KONCEPCJA PAMIĘCI

KONCEPCJA PAMIĘCI

PODRĘCZNEJ (CACHE)

PODRĘCZNEJ (CACHE)

Architektura komputera z pamięcią cache

Architektura komputera z pamięcią cache

Elementy systemu pamięci cache

Elementy systemu pamięci cache

Organizacja pamięci cache

Organizacja pamięci cache

Przypomnijmy:

Przypomnijmy:

•

pamięci statyczne są szybsze, droższe, pobierają więcej energii i

pamięci statyczne są szybsze, droższe, pobierają więcej energii i

są trudniejsze do scalania

są trudniejsze do scalania

•

pamięci dynamiczne są wolniejsze, tańsze, pobierają mniej

pamięci dynamiczne są wolniejsze, tańsze, pobierają mniej

energii i są łatwiejsze do scalania

energii i są łatwiejsze do scalania

Wniosek 1

Wniosek 1

: nie jest możliwe zbudowanie całej pamięci operacyjnej z

: nie jest możliwe zbudowanie całej pamięci operacyjnej z

pamięci statycznych, a pamięci dynamiczne są za wolne dla

pamięci statycznych, a pamięci dynamiczne są za wolne dla

współczesnych procesorów i częstotliwości zegara

współczesnych procesorów i częstotliwości zegara

Wniosek 2

Wniosek 2

: wprowadza się dużą pamięć operacyjną (rzędu kilka GB)

: wprowadza się dużą pamięć operacyjną (rzędu kilka GB)

zbudowaną z pamięci dynamicznych i małą (kilka kilkaset kB)

zbudowaną z pamięci dynamicznych i małą (kilka kilkaset kB)

pamięć podręczną - statyczną - znacznie szybszą (wraz ze

pamięć podręczną - statyczną - znacznie szybszą (wraz ze

sterownikiem)

sterownikiem)

Wniosek 3

Wniosek 3

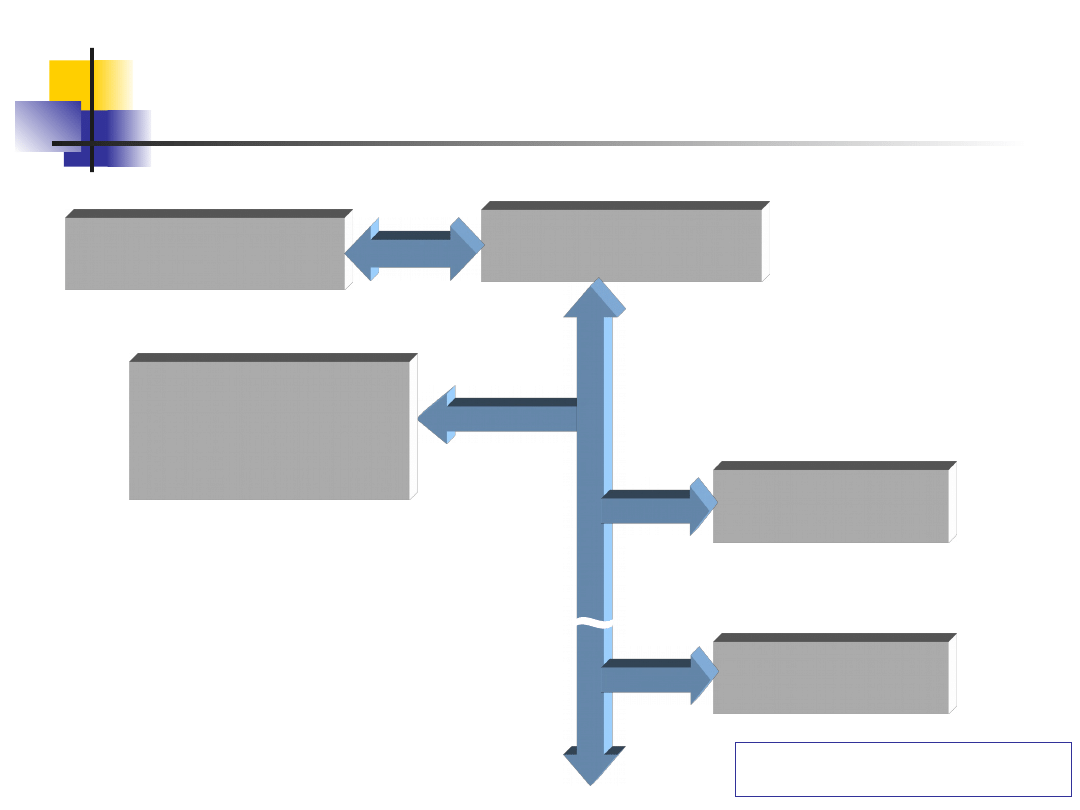

: dwa rodzaje architektury:

: dwa rodzaje architektury:

•

Look-trough („dostęp przez”)

Look-trough („dostęp przez”)

•

Look-aside

Look-aside

(„dostęp bezpośredni”)

(„dostęp bezpośredni”)

•

Back-side („dostęp od tyłu”)

Back-side („dostęp od tyłu”)

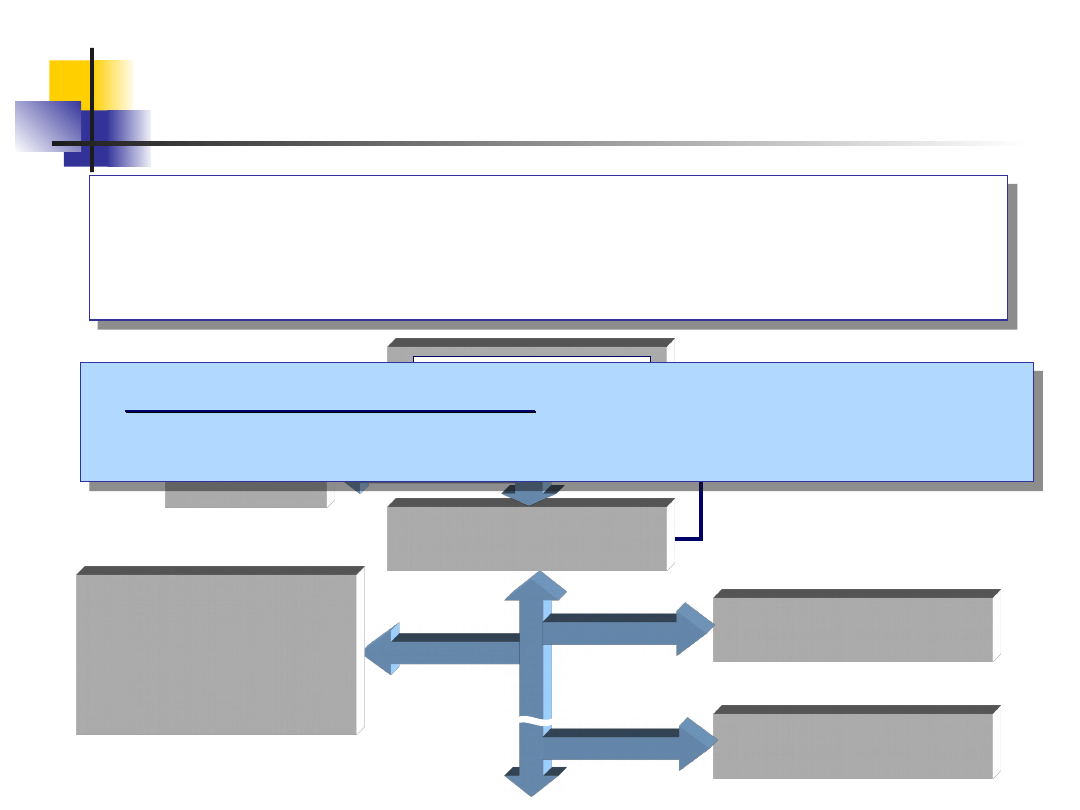

KONCEPCJA PAMIĘCI PODRĘCZNEJ

KONCEPCJA PAMIĘCI PODRĘCZNEJ

(CACHE)

(CACHE)

W przypadku „chybienia”

W przypadku „chybienia”

wykorzystywana

jest

wykorzystywana

jest

magistrala

główna

z

magistrala

główna

z

koniecznymi

stanami

koniecznymi

stanami

oczekiwania

oczekiwania

CACHE

CACHE

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

MIKROPROCESO

MIKROPROCESO

R

R

W przypadku „trafienia”

W przypadku „trafienia”

główna

magistrala

główna

magistrala

danych

nie

jest

danych

nie

jest

wykorzystywana

co

wykorzystywana

co

dodatkowo

przyspiesza

dodatkowo

przyspiesza

pracę

systemu

(z

pracę

systemu

(z

magistrali głównej mogą

magistrali głównej mogą

w tym czasie korzystać

w tym czasie korzystać

inni zarządcy).

inni zarządcy).

Magistrala

Magistrala

lokalna

lokalna

M

a

g

is

tr

a

la

M

a

g

is

tr

a

la

g

łó

w

n

a

g

łó

w

n

a

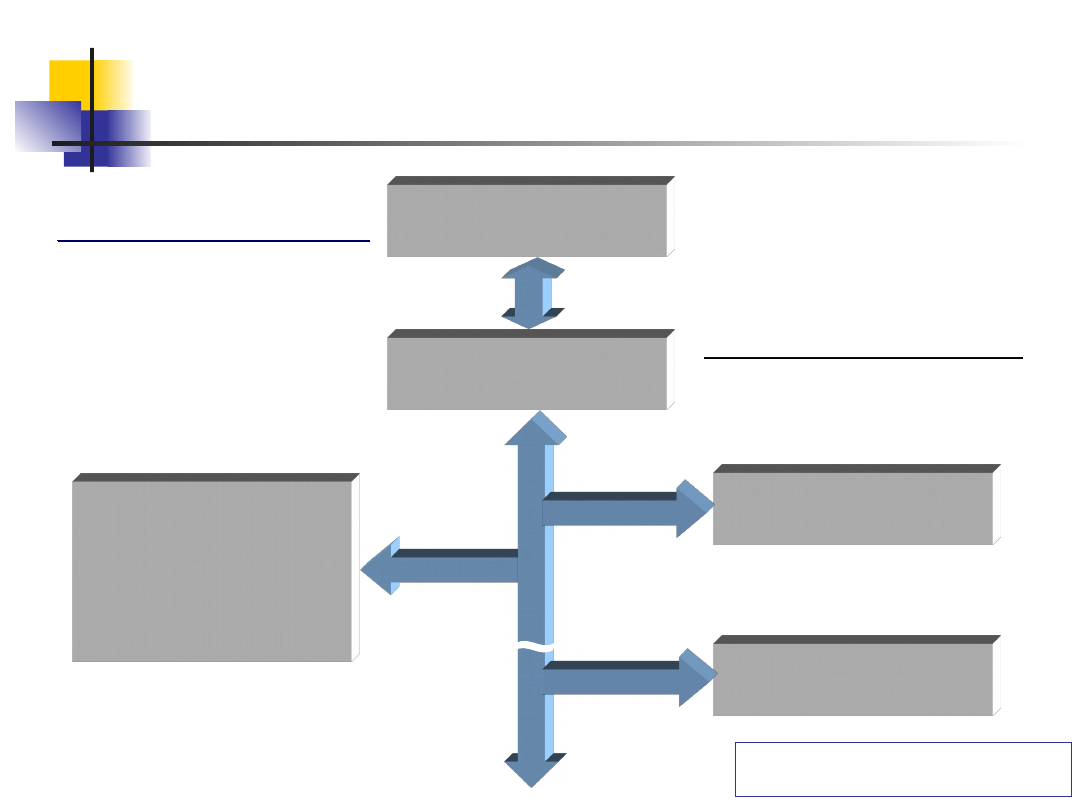

ARCHITEKTURA LOOK-THROUGH

ARCHITEKTURA LOOK-THROUGH

(„dostęp przez”)

(„dostęp przez”)

Wykorzystana w procesorach

Wykorzystana w procesorach

Intel Pentium II

Intel Pentium II

Zalety:

Zalety:

•

prostsza

prostsza

konstrukcja

konstrukcja

•

szybsza realizacja w

szybsza realizacja w

przypadku

przypadku

chybienia

chybienia

Wady:

Wady:

•

nawet przy trafieniu

nawet przy trafieniu

magistrala nie jest

magistrala nie jest

dostępna dla innych

dostępna dla innych

zarządców

zarządców

CACHE

CACHE

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

MIKROPROCESO

MIKROPROCESO

R

R

W przypadku „trafienia”

W przypadku „trafienia”

i

„chybienia”

i

„chybienia”

główna

główna

magistrala danych jest

magistrala danych jest

stale wykorzystywana.

stale wykorzystywana.

M

a

g

is

tr

a

la

M

a

g

is

tr

a

la

g

łó

w

n

a

g

łó

w

n

a

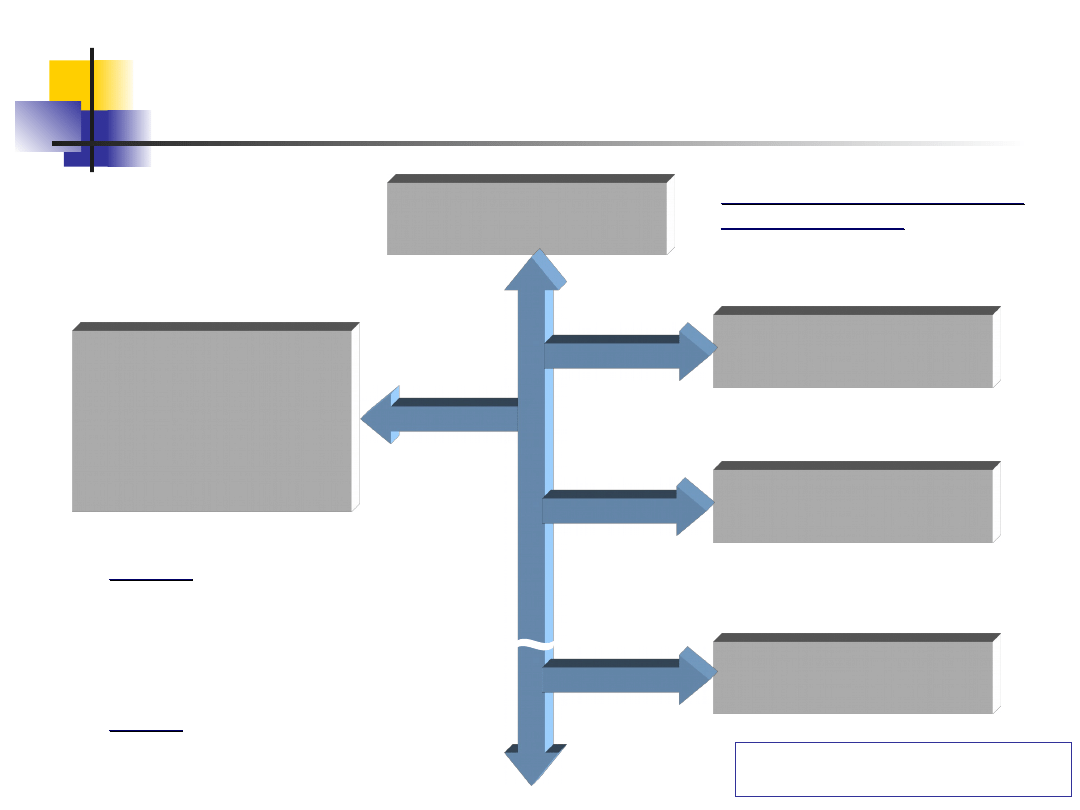

ARCHITEKTURA LOOK-ASIDE

ARCHITEKTURA LOOK-ASIDE

(„dostęp bezpośredni”)

(„dostęp bezpośredni”)

Wykorzystana w procesorach

Wykorzystana w procesorach

x86 i Pentium

x86 i Pentium

W czasie, kiedy procesor

W czasie, kiedy procesor

łączy się pamięcią cache,

łączy się pamięcią cache,

możliwe jest wykorzystanie

możliwe jest wykorzystanie

magistrali głównej przez

magistrali głównej przez

inne urządzenia

inne urządzenia

zapisujące/odczytujące do

zapisujące/odczytujące do

pamięci RAM. prostsza

pamięci RAM. prostsza

konstrukcja

konstrukcja

CACHE

CACHE

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

MIKROPROCESO

MIKROPROCESO

R

R

M

a

g

is

tr

a

la

M

a

g

is

tr

a

la

g

łó

w

n

a

g

łó

w

n

a

ARCHITEKTURA BACK-SIDE

ARCHITEKTURA BACK-SIDE

(„dostęp od tyłu”)

(„dostęp od tyłu”)

Magistra

Magistra

la

la

lokalna

lokalna

Wykorzystana w procesorach

Wykorzystana w procesorach

Intel Pentium Pro

Intel Pentium Pro

•

Bank danych pamięci cache

Bank danych pamięci cache

(pamięć danych)

(pamięć danych)

przechowuje, umożliwia zapisywanie i odczytywanie

przechowuje, umożliwia zapisywanie i odczytywanie

informacji

informacji

•

Katalog pamięci cache

Katalog pamięci cache

(zwany TAG-RAMem)

(zwany TAG-RAMem)

umożliwia szybkie sprawdzanie czy poszukiwana

umożliwia szybkie sprawdzanie czy poszukiwana

informacja znajduje się w pamięci danych cache

informacja znajduje się w pamięci danych cache

(konkretnie: czy dany adres jest odwzorowany w pamięci

(konkretnie: czy dany adres jest odwzorowany w pamięci

cache)

cache)

•

Sterownik pamięci cache

Sterownik pamięci cache

realizuje sprawdzenie adresu w katalogu pamięci cache,

realizuje sprawdzenie adresu w katalogu pamięci cache,

organizuje współpracę pamięci cache z systemem i

organizuje współpracę pamięci cache z systemem i

zapewnia zgodność zawartości pamięci cache z pamięcią

zapewnia zgodność zawartości pamięci cache z pamięcią

główną

główną

ELEMENTY SYSTEMU PAMIĘCI CACHE

ELEMENTY SYSTEMU PAMIĘCI CACHE

Zestaw 1

Zestaw 1

Strona 1

Strona 1

Strona 0

Strona 0

Strona 0

Strona 0

Zestaw 2

Zestaw 2

Zestaw 3

Zestaw 3

Zestaw 4

Zestaw 4

Zestaw 5

Zestaw 5

Zestaw 1

Zestaw 1

Zestaw 2

Zestaw 2

Zestaw 3

Zestaw 3

Zestaw 4

Zestaw 4

Zestaw 5

Zestaw 5

Zestaw 1

Zestaw 1

Zestaw 2

Zestaw 2

Zestaw 3

Zestaw 3

Zestaw 4

Zestaw 4

Zestaw 5

Zestaw 5

Zestaw 1

Zestaw 1

Zestaw 2

Zestaw 2

Zestaw 3

Zestaw 3

Zestaw 4

Zestaw 4

Zestaw 5

Zestaw 5

Strona 1

Strona 1

Strona 0

Strona 0

Strona 2

Strona 2

Dane 1

Dane 1

Dane 2

Dane 2

Dane 3

Dane 3

Dane 3

Dane 3

Dane 2

Dane 2

Dane 4

Dane 4

Dane 1

Dane 1

O1

O1

O2

O2

O3

O3

Katalog cache

Katalog cache

(TAG-RAM)

(TAG-RAM)

Bank cache

Bank cache

O4

O4

Dane 4

Dane 4

Strona

Strona

2

2

•

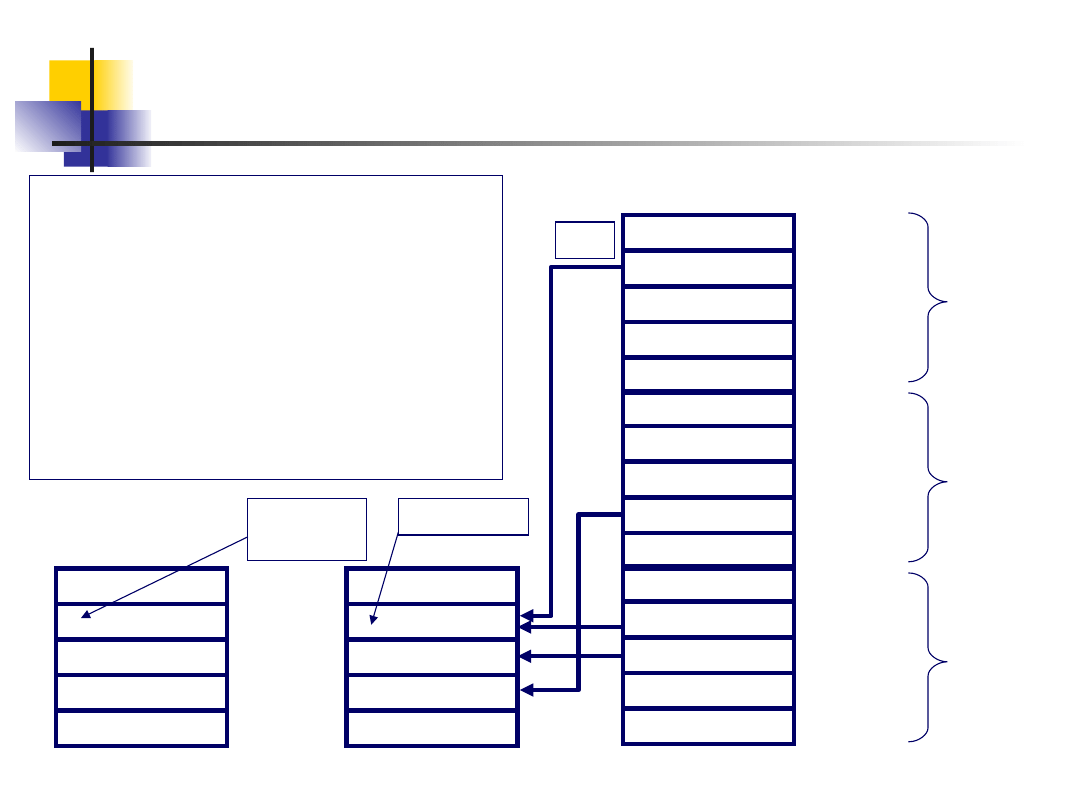

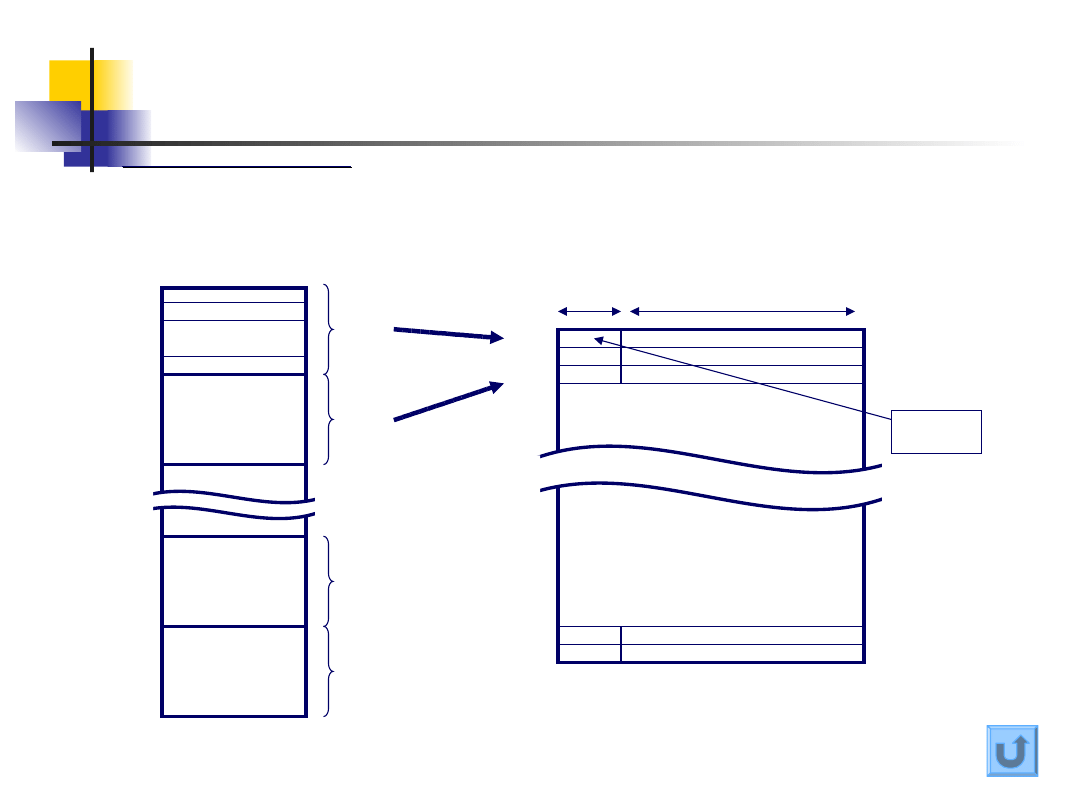

Bank danych i katalog pamięci cache (TAG-

Bank danych i katalog pamięci cache (TAG-

RAM) tworzą tzw. jednoblokową pamięć

RAM) tworzą tzw. jednoblokową pamięć

asocjacyjną

asocjacyjną

•

Pamięć

cache

stanowi

jeden

blok

Pamięć

cache

stanowi

jeden

blok

podzielony na zestawy

podzielony na zestawy

•

Pamięć główna dzielona jest na strony o

Pamięć główna dzielona jest na strony o

rozmiarze

równym

rozmiarowi

bloku

rozmiarze

równym

rozmiarowi

bloku

pamięci cache. Strony podobnie jak blok

pamięci cache. Strony podobnie jak blok

pamięci cache dzielone są na zestawy

pamięci cache dzielone są na zestawy

•

Każdy zestaw w pamięci cache ma swoją

Każdy zestaw w pamięci cache ma swoją

pozycję w katalogu (TAG-RAM) - zawiera

pozycję w katalogu (TAG-RAM) - zawiera

adres skąd pochodzi dany zestaw

adres skąd pochodzi dany zestaw

•

Każdy zestaw jest wpisywany na miejsce w

Każdy zestaw jest wpisywany na miejsce w

pamięci cache do zestawu o numerze

pamięci cache do zestawu o numerze

zgodnym z numerem zestawu w stronie

zgodnym z numerem zestawu w stronie

Pamięć

Pamięć

główna

główna

ORGANIZACJA PAMIĘCI CACHE

ORGANIZACJA PAMIĘCI CACHE

•

Bank danych i katalog pamięci cache (TAG-RAM) tworzą tzw.

Bank danych i katalog pamięci cache (TAG-RAM) tworzą tzw.

jednoblokową pamięć asocjacyjną

jednoblokową pamięć asocjacyjną

•

Pamięć cache stanowi jeden blok podzielony na zestawy

Pamięć cache stanowi jeden blok podzielony na zestawy

•

Pamięć główna dzielona jest na strony o rozmiarze równym

Pamięć główna dzielona jest na strony o rozmiarze równym

rozmiarowi bloku pamięci cache. Strony podobnie jak blok

rozmiarowi bloku pamięci cache. Strony podobnie jak blok

pamięci cache dzielone są na zestawy

pamięci cache dzielone są na zestawy

•

Każdy zestaw w pamięci cache ma swoją pozycję w katalogu

Każdy zestaw w pamięci cache ma swoją pozycję w katalogu

(TAG-RAM) - zawiera adres skąd pochodzi dany zestaw

(TAG-RAM) - zawiera adres skąd pochodzi dany zestaw

•

Każdy zestaw jest wpisywany na miejsce w pamięci cache do

Każdy zestaw jest wpisywany na miejsce w pamięci cache do

zestawu o numerze zgodnym z numerem zestawu w stronie

zestawu o numerze zgodnym z numerem zestawu w stronie

ORGANIZACJA PAMIĘCI CACHE

ORGANIZACJA PAMIĘCI CACHE

Podsumowanie

Przyczyny niezgodności:

Przyczyny niezgodności:

•

nastąpił zapis do pamięci cache bez zapisu do pamięci głównej (w

nastąpił zapis do pamięci cache bez zapisu do pamięci głównej (w

przypadku trafienia przy zapisie do pamięci)

przypadku trafienia przy zapisie do pamięci)

•

nastąpił zapis do pamięci głównej bez zapisu do pamięci cache (gdy z

nastąpił zapis do pamięci głównej bez zapisu do pamięci cache (gdy z

magistrali głównej korzystał inny zarządca magistrali niż procesor

magistrali głównej korzystał inny zarządca magistrali niż procesor

np. transmisja DMA do pamięci głównej)

np. transmisja DMA do pamięci głównej)

Strategie utrzymania zgodności:

Strategie utrzymania zgodności:

•

Write-through (zapis do pamięci cache powoduje jednoczesny zapis

Write-through (zapis do pamięci cache powoduje jednoczesny zapis

do pamięci głównej - proste ale zmniejsza szybkość, bo zpisuje się

do pamięci głównej - proste ale zmniejsza szybkość, bo zpisuje się

informacje do wolnej pamięci głównej)

informacje do wolnej pamięci głównej)

•

Buforowane (opóźnione) write-through (jak wyżej ale zapis do bufora

Buforowane (opóźnione) write-through (jak wyżej ale zapis do bufora

i dopiero później z bufora do pamięci głównej aby nie spowalniać

i dopiero później z bufora do pamięci głównej aby nie spowalniać

pracy)

pracy)

•

Write-back (zawartości obu pamięci są uzgadniane gdy zajdzie taka

Write-back (zawartości obu pamięci są uzgadniane gdy zajdzie taka

potrzeba - operacje bardzo skomplikowane)

potrzeba - operacje bardzo skomplikowane)

Pewne obszary w pamięci głównej nie mogą być odzwierciedlone w

Pewne obszary w pamięci głównej nie mogą być odzwierciedlone w

pamięci cache, gdyż nie jest możliwe zapewnienie zgodności, np. obszar

pamięci cache, gdyż nie jest możliwe zapewnienie zgodności, np. obszar

pamięci RAM karty sieciowej, gdzie zapis może realizować procesor przez

pamięci RAM karty sieciowej, gdzie zapis może realizować procesor przez

magistralę systemową jak i sterownik sieci (nie ma możliwości śledzenia

magistralę systemową jak i sterownik sieci (nie ma możliwości śledzenia

magistrali sieci). W systemie muszą więc istnieć układy NCA (

magistrali sieci). W systemie muszą więc istnieć układy NCA (

non-cachable

non-cachable

access

access

) uniemożliwiające niektóre zapisy do pamięci cache.

) uniemożliwiające niektóre zapisy do pamięci cache.

ZAPEWNIENIE ZGODNOŚCI PAMIĘCI

ZAPEWNIENIE ZGODNOŚCI PAMIĘCI

CACHE

CACHE

Pamięć cache (zwłaszcza typu Look-through) możer występować:

Pamięć cache (zwłaszcza typu Look-through) możer występować:

•

wewnątrz procesora - pamięć cache pierwszego poziomu (L1- lovel 1),

wewnątrz procesora - pamięć cache pierwszego poziomu (L1- lovel 1),

•

pamięć zewnętrzna - pamięć drugiego poziomu (L2).

pamięć zewnętrzna - pamięć drugiego poziomu (L2).

Pamięć tego typu pojawiła się po raz pierwszy w procesorach 80486.

Pamięć tego typu pojawiła się po raz pierwszy w procesorach 80486.

Pamięć L2 jest znacznie większa od L1, dzięki czemu jeśli nie nastąpiło

Pamięć L2 jest znacznie większa od L1, dzięki czemu jeśli nie nastąpiło

„trafienie” w pamięci L1 to istnieje duża szansa trafienia do L2 (oczywiście

„trafienie” w pamięci L1 to istnieje duża szansa trafienia do L2 (oczywiście

informacja z pamięci L1 znajduje się w pamięci L2) - przyspiesza to pracę

informacja z pamięci L1 znajduje się w pamięci L2) - przyspiesza to pracę

systemu.

systemu.

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

ZARZĄDCA

ZARZĄDCA

MAGISTRAL

MAGISTRAL

8048

8048

6

6

M

a

g

is

tr

a

la

M

a

g

is

tr

a

la

g

łó

w

n

a

g

łó

w

n

a

CACHE 1-go poziomu

CACHE 1-go poziomu

Blok sterowania

Blok sterowania

magistralą

magistralą

S

y

g

n

a

ły

s

te

ru

ją

c

e

S

y

g

n

a

ły

s

te

ru

ją

c

e

CACHE 2-go poziomu

CACHE 2-go poziomu

Magistrala lokalna

Magistrala lokalna

Układy

Układy

logiczne

logiczne

NCA

NCA

Sygnały sterujące

Sygnały sterujące

PAMIĘĆ CACHE DRUGIEGO POZIOMU

PAMIĘĆ CACHE DRUGIEGO POZIOMU

Pamięć L1 jest podzielona na dwa bloki:

Pamięć L1 jest podzielona na dwa bloki:

danych

danych

rozkazów,

rozkazów,

działa z częstotliwością pracy CPU, pojemności rzędu kilkudziesięciu

działa z częstotliwością pracy CPU, pojemności rzędu kilkudziesięciu

KB;

KB;

Pamięć trzeciego poziomu L3

Pamięć trzeciego poziomu L3

jest oddzielnym układem na płycie

jest oddzielnym układem na płycie

głównej.

głównej.

Stosowana jest zazwyczaj w serwerach i wydajnych stacjach roboczych.

Stosowana jest zazwyczaj w serwerach i wydajnych stacjach roboczych.

Jest wolniejsza od CPU, pojemność około kilku MB.

Jest wolniejsza od CPU, pojemność około kilku MB.

DZIĘKUJĘ ZA UWAGĘ !

DZIĘKUJĘ ZA UWAGĘ !

Zjawisko lokalności

Zjawisko lokalności

- procesor odwołuje się najczęściej do pamięci (

- procesor odwołuje się najczęściej do pamięci (

trafienie

trafienie

)

)

w pewnym niewielkim obszarze (w okolicach danego programu) - bardzo

w pewnym niewielkim obszarze (w okolicach danego programu) - bardzo

rzadko do obszarów odległych. Stąd stosowanie szybkich pamięci

rzadko do obszarów odległych. Stąd stosowanie szybkich pamięci

kieszeniowych (cache) zawierających właśnie taki lokalny obszar pamięci.

kieszeniowych (cache) zawierających właśnie taki lokalny obszar pamięci.

0

0

1

1

q-1

q-1

1 blok

1 blok

2 blok

2 blok

k-1 blok

k-1 blok

k-2 blok

k-2 blok

...

...

0

0

1

1

m-1

m-1

2

2

m-2

m-2

q słów

q słów

log

log

2

2

k

k

pamięć operacyjna

pamięć operacyjna

pamięć kieszeniowa

pamięć kieszeniowa

zawiera tylko

zawiera tylko

m

m

spośród

spośród

k

k

bloków

bloków

(k>>m)

(k>>m)

Gdy procesor zażąda dostępu do bloku, którego nie ma w pamięci cache

Gdy procesor zażąda dostępu do bloku, którego nie ma w pamięci cache

(

(

chybienie

chybienie

) to następuje wymiana zawartości jednej komórki pamięci

) to następuje wymiana zawartości jednej komórki pamięci

kieszeniowej.

kieszeniowej.

Nr

Nr

bloku

bloku

PAMIĘĆ KIESZENIOWA

PAMIĘĆ KIESZENIOWA

(przypomnienie)

(przypomnienie)

Document Outline

Wyszukiwarka

Podobne podstrony:

architektura sk 05

architektura sk 01

architektura sk 04

architektura sk 03

architektura sk 08

architektura sk 09

architektura sk 07

architektura sk 06

architektura sk 11

architektura sk 02

architektura sk 12

architektura sk 10

architektura sk 05

architektura sk 01

Egzamin SK?za 13

12 13 AiU pytania egzaminacyjne historia i teoria architekturyid 13704

URBANISTYKA 13 -18, Architektura i budownictwo, dyplom, jakies pytania i odp do dyplomu inz, urbanis

ST 13 specyfikacja techniczna wentylacja hybrydowa ETAP 1, TBS Wrocław Wojanowska, Etap I, ETAP I -

12-13---AiU---pytania-egzaminacyjne---historia-i-teoria-architektury

więcej podobnych podstron