PRACA PROCESORA W

PRACA PROCESORA W

TRYBIE

TRYBIE

RZECZYWISTYM I

RZECZYWISTYM I

CHRONIONYM

CHRONIONYM

Praca procesora w trybie rzeczywistym

Praca procesora w trybie rzeczywistym

Praca procesora w trybie chronionym

Praca procesora w trybie chronionym

Stronicowanie

Stronicowanie

Praca wielozadaniowa

Praca wielozadaniowa

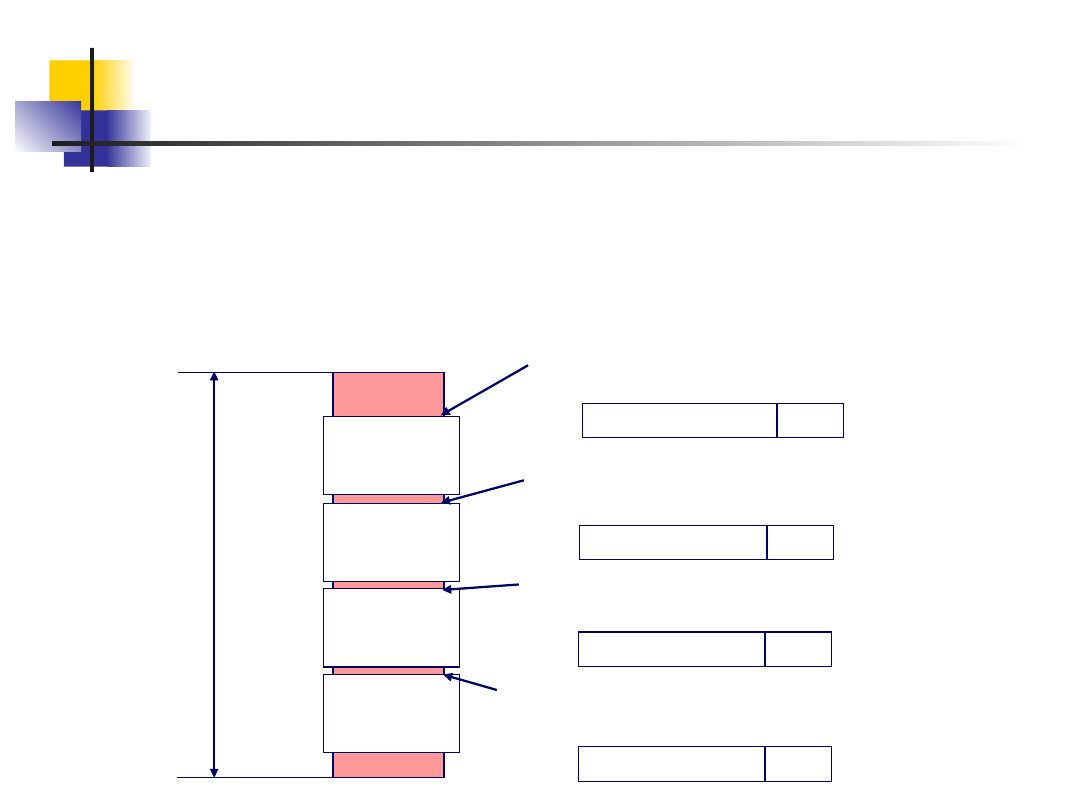

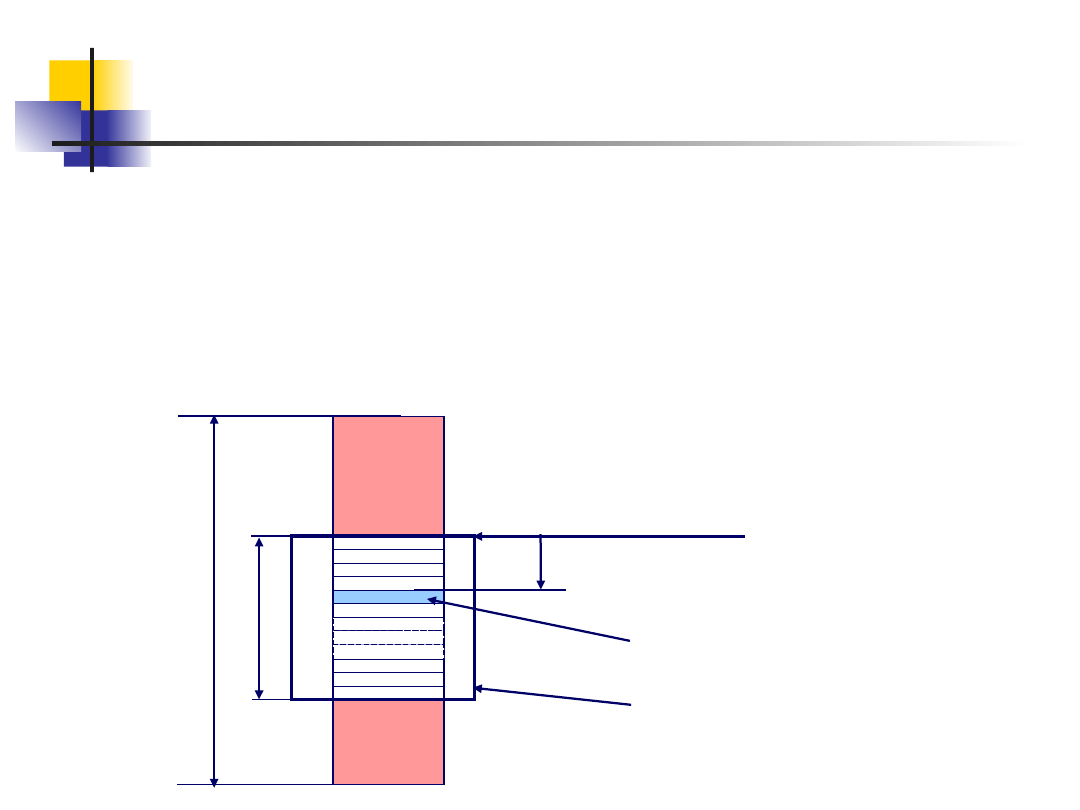

W typowym procesorze 16 bitowym (8086/88) mamy:

W typowym procesorze 16 bitowym (8086/88) mamy:

•

rejestry 16 bitowe

rejestry 16 bitowe

•

magistrala danych 16 bitowa

magistrala danych 16 bitowa

•

ale szyna adresowa 20 bitowa - adres 20 bitowy

ale szyna adresowa 20 bitowa - adres 20 bitowy

20 bitowy adres pozwala zaadresować 2

20 bitowy adres pozwala zaadresować 2

20

20

=1048576B=1MB pamięci operacyjnej

=1048576B=1MB pamięci operacyjnej

dzielonej na segmenty

dzielonej na segmenty

PAMIĘ

PAMIĘ

Ć

Ć

1M

1M

B

B

Segment

Segment

programu

programu

(kodu)

(kodu)

Segment

Segment

danych

danych

Segment

Segment

stosu

stosu

Segment

Segment

danych

danych

dodatkowy

dodatkowy

ch

ch

początek segmentu wyznacza

początek segmentu wyznacza

zawartość rejestru segmentu programu

zawartość rejestru segmentu programu

CS*16 czyli

CS*16 czyli

rejestr CS

rejestr CS

000

000

0

0

3

3

0

0

15

15

0

0

początek segmentu wyznacza

początek segmentu wyznacza

zawartość rejestru segmentu danych

zawartość rejestru segmentu danych

DS*16 czyli

DS*16 czyli

rejestr DS

rejestr DS

000

000

0

0

3

3

0

0

15

15

0

0

101100100110

101100100110

1101

1101

początek segmentu wyznacza

początek segmentu wyznacza

zawartość rejestru segmentu stosu

zawartość rejestru segmentu stosu

SS*16 czyli

SS*16 czyli

rejestr SS

rejestr SS

000

000

0

0

3

3

0

0

15

15

0

0

początek segmentu wyznaczają zawartości

początek segmentu wyznaczają zawartości

rejestrów dodatkowych segmentów danych

rejestrów dodatkowych segmentów danych

ES (GS, FS) *16 czyli

ES (GS, FS) *16 czyli

rejestr

rejestr

ES(GS,FS)

ES(GS,FS)

000

000

0

0

3

3

0

0

15

15

0

0

Adres

Adres

00000

00000

H

H

Adres

Adres

FFFFF

FFFFF

H

H

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

Część segmentowa adresu wyznacza adres segmentu, ale aby zaadresować

Część segmentowa adresu wyznacza adres segmentu, ale aby zaadresować

określoną komórkę należy posługiwać się adresem fizycznym.

określoną komórkę należy posługiwać się adresem fizycznym.

Adres fizyczny (20 bitowy) określa się według reguły:

Adres fizyczny (20 bitowy) określa się według reguły:

Adres fizyczny = część segmentowa *16 + przemieszczenie (tzw. adres

Adres fizyczny = część segmentowa *16 + przemieszczenie (tzw. adres

efektywny)

efektywny)

rejestr

rejestr

segmentowy

segmentowy

000

000

0

0

15

15

CS=1011001001101

CS=1011001001101

101

101

adres

adres

efektywny

efektywny

0

0

15

15

IP=0100011111110

IP=0100011111110

011

011

wskaźnik

wskaźnik

rozkazów

rozkazów

rejestr segmentu

rejestr segmentu

programu

programu

+

+

adres

adres

fizyczny

fizyczny

0

0

19

19

1011001001101101

1011001001101101

0000

0000

0100011111110

0100011111110

011

011

CS

CS

0000

0000

IP

IP

+

+

+

+

ADRES

ADRES

FIZYCZNY

FIZYCZNY

1011011011101100

1011011011101100

0011

0011

B2D60

B2D60

+

+

47F3

47F3

B6EC3

B6EC3

0

0

H

H

=000

=000

0

0

B

B

0 3

0 3

0

0

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

O tym, które pary rejestrów segmentowych i wskaźnikowych zostaną

O tym, które pary rejestrów segmentowych i wskaźnikowych zostaną

użyte do określania adresu fizycznego nie decyduje przypadek lecz

użyte do określania adresu fizycznego nie decyduje przypadek lecz

pewne reguły

pewne reguły

wskaźnik rozkazów

wskaźnik rozkazów

(IP)

(IP)

zawsze: rejestr segmentu programu (CS)

zawsze: rejestr segmentu programu (CS)

wskaźnik stosu (SP)

wskaźnik stosu (SP)

zawsze: rejestr segmentu stosu (SS)

zawsze: rejestr segmentu stosu (SS)

wskaźnik bazy (BP)

wskaźnik bazy (BP)

rejestr segmentu stosu (SS)

rejestr segmentu stosu (SS)

pozostałe rejestry

pozostałe rejestry

rejestr segmentu danych (DS)

rejestr segmentu danych (DS)

rejestr indeksowy

rejestr indeksowy

przeznaczenia (DI)

przeznaczenia (DI)

rejestr dodatkowy (ES)

rejestr dodatkowy (ES)

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

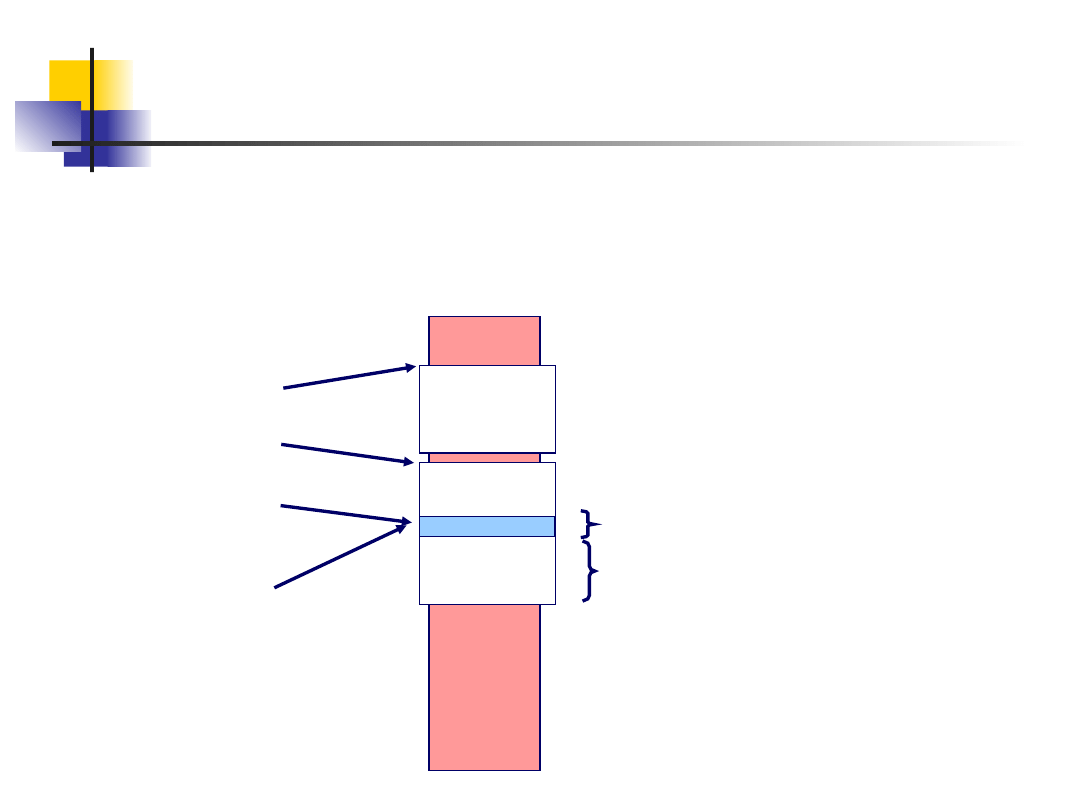

Interpretacja adresu fizycznego:

Interpretacja adresu fizycznego:

•

zawartość rejestru segmentowego *16 podaje adres początku

zawartość rejestru segmentowego *16 podaje adres początku

segmentu

segmentu

•

od tego początku odsuwamy się o liczbę komórek podaną w adresie

od tego początku odsuwamy się o liczbę komórek podaną w adresie

efektywnym

efektywnym

•

adres efektywny jest 16 bitowy to pozwala zaadresować

adres efektywny jest 16 bitowy to pozwala zaadresować

65536B=64kB

65536B=64kB

•

pamięć jest widziana przez procesor jako 64kB okno

pamięć jest widziana przez procesor jako 64kB okno

•

okno to można przesuwać przeładowując rejestry segmentowe (skok

okno to można przesuwać przeładowując rejestry segmentowe (skok

16B bo mnożymy przez 16)

16B bo mnożymy przez 16)

PAMIĘ

PAMIĘ

Ć

Ć

1MB

1MB

adresowana

adresowana

komórka

komórka

pamięci

pamięci

Adres

Adres

00000

00000

H

H

Adres

Adres

FFFFF

FFFFF

H

H

6

4

k

B

6

4

k

B

początek segmentu

początek segmentu

(zawartość rejestru

(zawartość rejestru

segmentowego*16)

segmentowego*16)

przesunięcie adres

przesunięcie adres

efektywny)

efektywny)

okno przez

okno przez

które widziana

które widziana

jest pamięć

jest pamięć

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

Segmenty mogą być rozłączne lub mogą się częściowo lub całkowicie

Segmenty mogą być rozłączne lub mogą się częściowo lub całkowicie

pokrywać.

pokrywać.

Jest to sytuacja niepożądana - przyjęcie za bliskich adresów

Jest to sytuacja niepożądana - przyjęcie za bliskich adresów

segmentowych może spowodować np. zamazanie kodu programu przez

segmentowych może spowodować np. zamazanie kodu programu przez

zapisywane dane

zapisywane dane

PAMIĘ

PAMIĘ

Ć

Ć

Segment

Segment

programu

programu

(kodu)

(kodu)

Segment

Segment

danych

danych

Segment stosu i

Segment stosu i

danych

danych

dodatkowych

dodatkowych

CS=2A00

CS=2A00

H

H

DS=41FF

DS=41FF

H

H

SS=4FFF

SS=4FFF

H

H

ES=4FFF

ES=4FFF

H

H

Obszar wspólny danych, stosu i

Obszar wspólny danych, stosu i

danych dodatkowych

danych dodatkowych

Obszar wspólny stosu i danych

Obszar wspólny stosu i danych

dodatkowych

dodatkowych

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

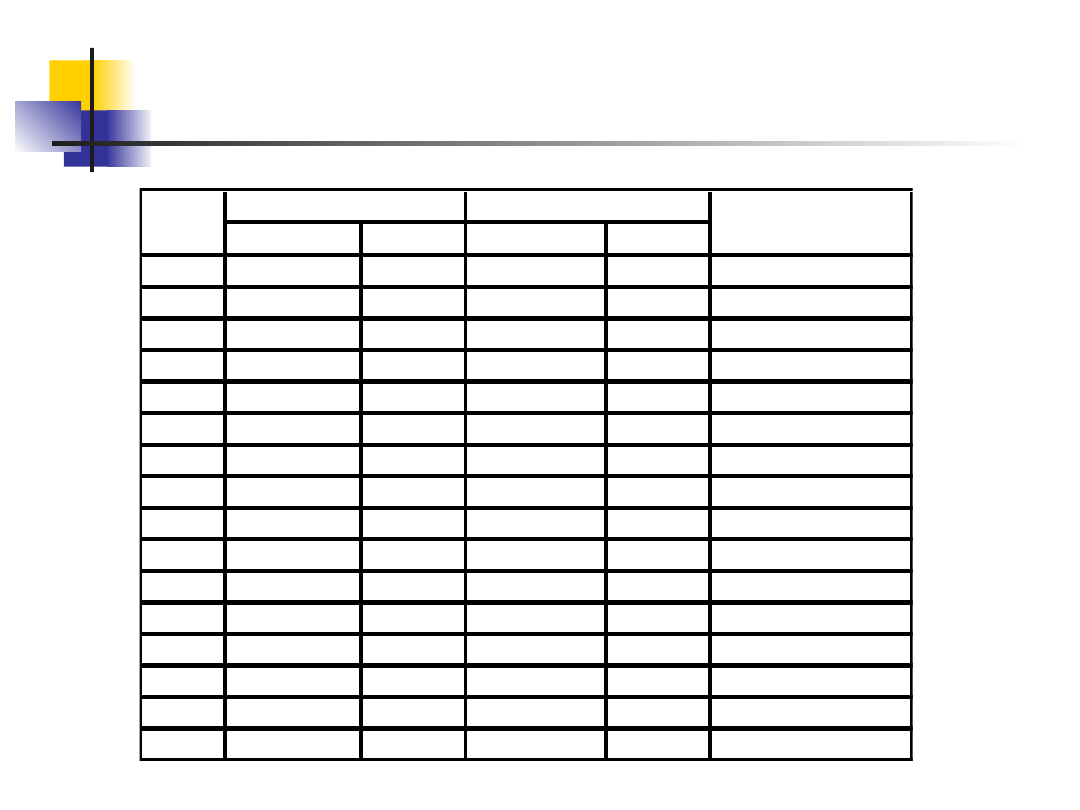

Segmenty pamięci komputera z procesorem 8086

Segmenty pamięci komputera z procesorem 8086

LOGICZNY FIZYCZNY LOGICZNY FIZYCZNY

0H

0000H:0000H 00000H 0000H:FFFFH 0FFFFH Programy użytkownika

1H

1000H:0000H 10000H 1000H:FFFFH 1FFFFH Programy użytkownika

2H

2000H:0000H 20000H 2000H:FFFFH 2FFFFH Programy użytkownika

3H

3000H:0000H 30000H 3000H:FFFFH 3FFFFH Programy użytkownika

4H

4000H:0000H 40000H 4000H:FFFFH 4FFFFH Programy użytkownika

5H

5000H:0000H 50000H 5000H:FFFFH 5FFFFH Programy użytkownika

6H

6000H:0000H 60000H 6000H:FFFFH 6FFFFH Programy użytkownika

7H

7000H:0000H 70000H 7000H:FFFFH 7FFFFH Programy użytkownika

8H

8000H:0000H 80000H 8000H:FFFFH 8FFFFH Programy użytkownika

9H

9000H:0000H 90000H 9000H:FFFFH 9FFFFH Programy użytkownika

AH

A000H:0000H A0000H A000H:FFFFH AFFFFH

Pamięć ekranu

BH

B000H:0000H B0000H B000H:FFFFH BFFFFH

Pamięć ekranu

CH

C000H:0000H C0000H C000H:FFFFH CFFFFH

BIOS-rozszerzenie

DH

D000H:0000H D0000H D000H:FFFFH DFFFFH

BIOS-rozszerzenie

EH

E000H:0000H E0000H E000H:FFFFH EFFFFH

BIOS

FH

F000H:0000H F0000H F000H:FFFFH FFFFFH

BIOS

ADRES POCZĄTKU

ADRES KOŃCA

NUMER

ZASTOSOWANIE

adres logiczny

adres logiczny

zawartość rejestru segmentowego: przesunięcie

zawartość rejestru segmentowego: przesunięcie

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

RZECZYWISTYM

RZECZYWISTYM

1. Gdyby szyna adresowa miała więcej bitów wówczas fizycznie można by zaadresować

1. Gdyby szyna adresowa miała więcej bitów wówczas fizycznie można by zaadresować

większy obszar pamięci. Np. przy 32 bitach do 2

większy obszar pamięci. Np. przy 32 bitach do 2

32

32

=4GB, przy 48 bitach 2

=4GB, przy 48 bitach 2

48

48

=256TB pamięci.

=256TB pamięci.

2. Tak duża pamięć operacyjna byłaby trudna do realizacji. Inaczej byłoby z pamięcią

2. Tak duża pamięć operacyjna byłaby trudna do realizacji. Inaczej byłoby z pamięcią

masową

masową

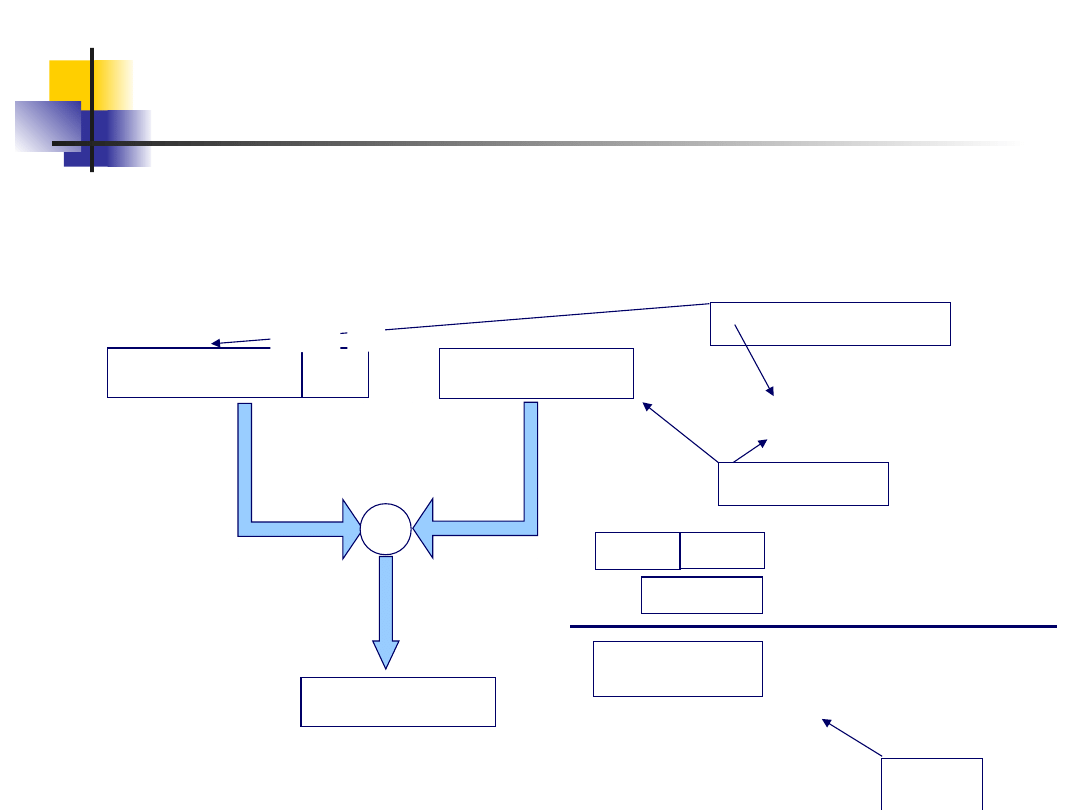

3. Dlatego stosuje się następujący mechanizm pamięci wirtualnej:

3. Dlatego stosuje się następujący mechanizm pamięci wirtualnej:

•

do pamięci operacyjnej przepisuje się segmenty informacji z pamięci masowej

do pamięci operacyjnej przepisuje się segmenty informacji z pamięci masowej

•

program żąda dostępu do informacji podając adres wirtualny (logiczny)

program żąda dostępu do informacji podając adres wirtualny (logiczny)

•

sprawdzana jest obecność poszukiwanej informacji w pamięci operacyjnej (informacja o

sprawdzana jest obecność poszukiwanej informacji w pamięci operacyjnej (informacja o

tym przechowywana jest w tablicy deskryptorów)

tym przechowywana jest w tablicy deskryptorów)

•

w przypadku braku poszukiwana informacja jest przepisywana z pamięci masowej (z

w przypadku braku poszukiwana informacja jest przepisywana z pamięci masowej (z

dysku) do pamięci operacyjnej (i z pamięci operacyjnej na dysk - wymiana informacji)

dysku) do pamięci operacyjnej (i z pamięci operacyjnej na dysk - wymiana informacji)

•

obliczany jest adres fizyczny potrzebnej informacji w pamięci operacyjnej - translacja

obliczany jest adres fizyczny potrzebnej informacji w pamięci operacyjnej - translacja

adresu wirtualnego na fizyczny (przy pomocy tablicy deskryptorów)

adresu wirtualnego na fizyczny (przy pomocy tablicy deskryptorów)

•

poszukiwana informacja jest dostępna dla procesora z pamięci operacyjnej

poszukiwana informacja jest dostępna dla procesora z pamięci operacyjnej

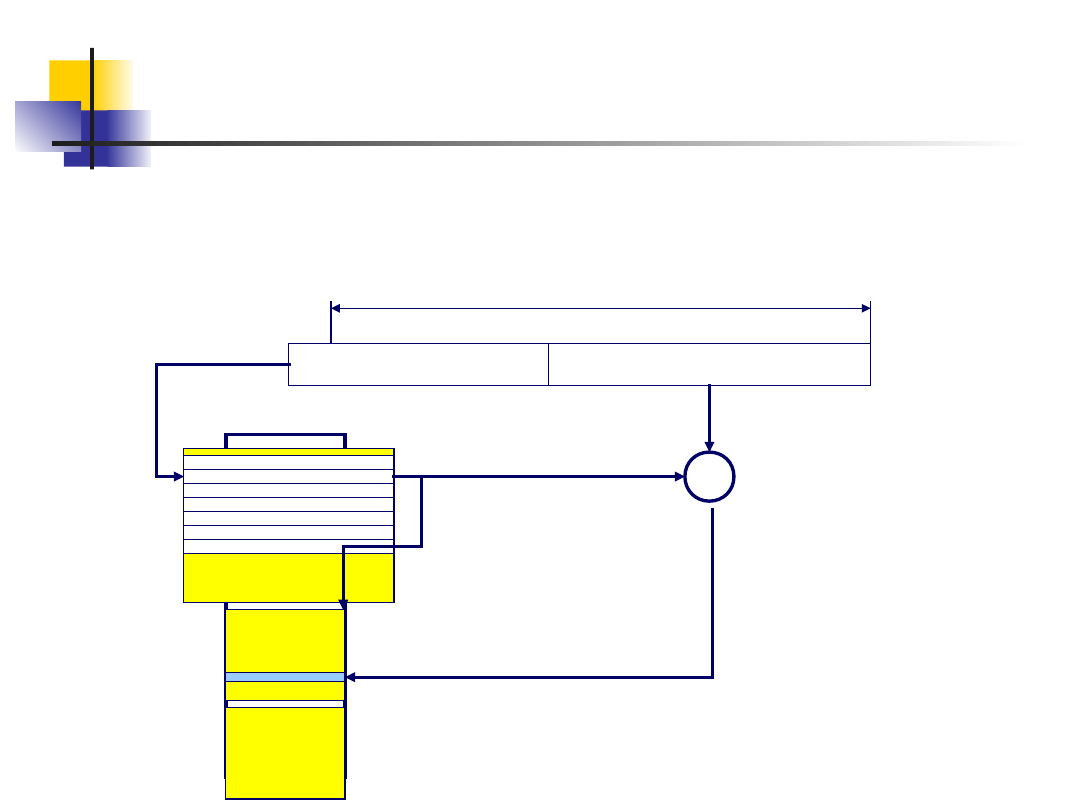

Przypomnijmy:

Przypomnijmy:

Pamięć masowa

Pamięć masowa

(PM)

(PM)

Pamięć operacyjna

Pamięć operacyjna

(PAO)

(PAO)

duża pojemność, wolne działanie, niski

duża pojemność, wolne działanie, niski

koszt

koszt

mała pojemność, szybkie działanie, wysoki

mała pojemność, szybkie działanie, wysoki

koszt

koszt

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

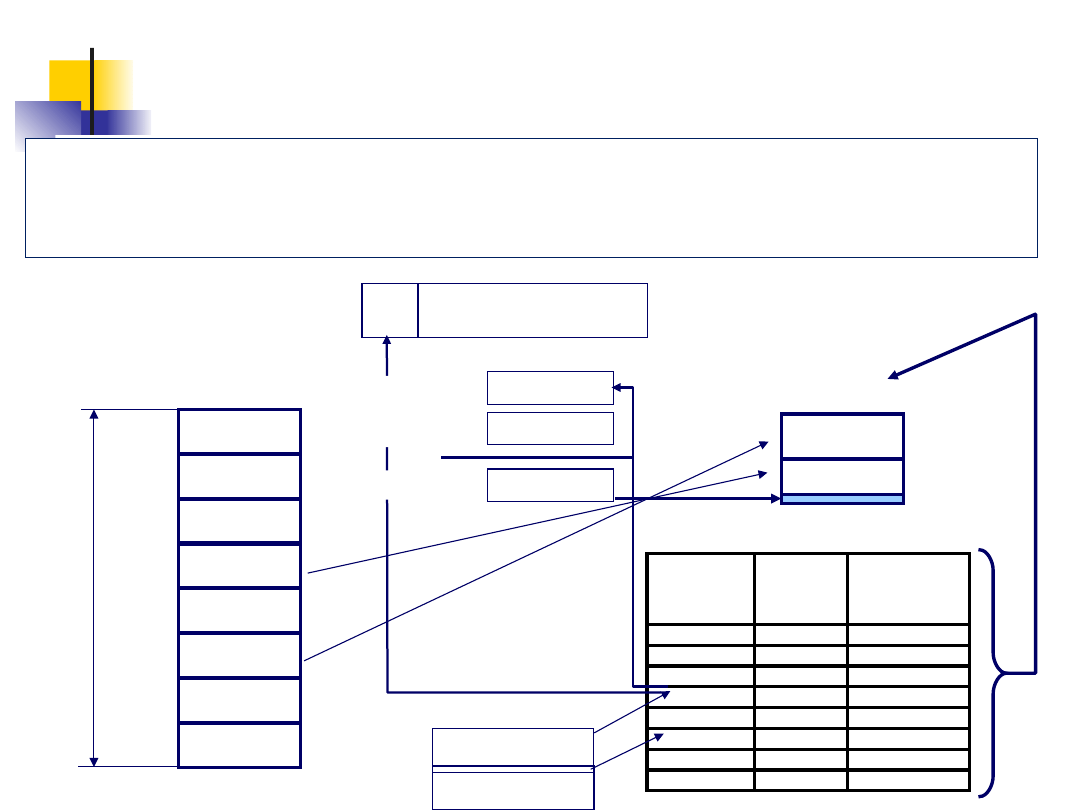

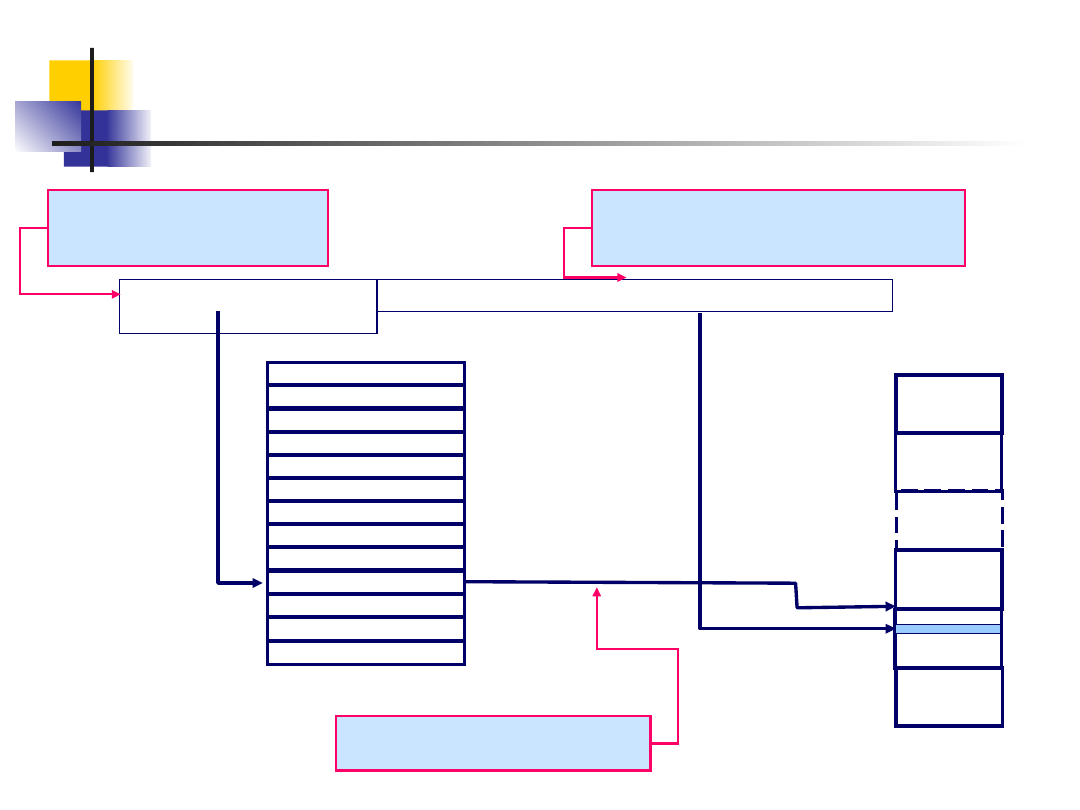

4. Adres wirtualny (logiczny) w trybie chronionym składa się z:

4. Adres wirtualny (logiczny) w trybie chronionym składa się z:

•

z części segmentowej (selektor segmentu)

z części segmentowej (selektor segmentu)

•

przemieszczenia (adres efektywny)

przemieszczenia (adres efektywny)

Dwuwymiarowa budowa adresu logicznego prowadzi do podziału pamięci na segmenty

Dwuwymiarowa budowa adresu logicznego prowadzi do podziału pamięci na segmenty

zwanego

zwanego

segmentacją przestrzeni logicznej

segmentacją przestrzeni logicznej

.

.

przykład dla procesora 80286 (najprostszy)

przykład dla procesora 80286 (najprostszy)

Adres logiczny (wirtualny) w trybie chronionym składa się z:

Adres logiczny (wirtualny) w trybie chronionym składa się z:

•

3 bitowej części segmentowej (selektor segmentu)

3 bitowej części segmentowej (selektor segmentu)

•

20 bitowego przemieszczenia (adres efektywny)

20 bitowego przemieszczenia (adres efektywny)

Pozwala to zaadresować 8 MB pamięci (2

Pozwala to zaadresować 8 MB pamięci (2

3

3

=8 segmentów po 2

=8 segmentów po 2

20

20

=1MB).

=1MB).

Adres logiczny (wirtualny) zamieniany jest na fizyczny 21 bitowy, więc pamięć operacyjna

Adres logiczny (wirtualny) zamieniany jest na fizyczny 21 bitowy, więc pamięć operacyjna

może mieć 2MB (pomijając obszar na system operacyjny i tablicę deskryptorów)

może mieć 2MB (pomijając obszar na system operacyjny i tablicę deskryptorów)

Numer

Numer

bloku

bloku

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

Deskryptor bloku

Deskryptor bloku

5

5

00

00

0

0

00

00

1

1

01

01

0

0

01

01

1

1

10

10

0

0

10

10

1

1

11

11

0

0

11

11

1

1

01

01

1

1

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

M

B

8

M

B

PAMIĘĆ

PAMIĘĆ

MASOWA

MASOWA

1MB

1MB

1MB

1MB

5

5

3

3

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

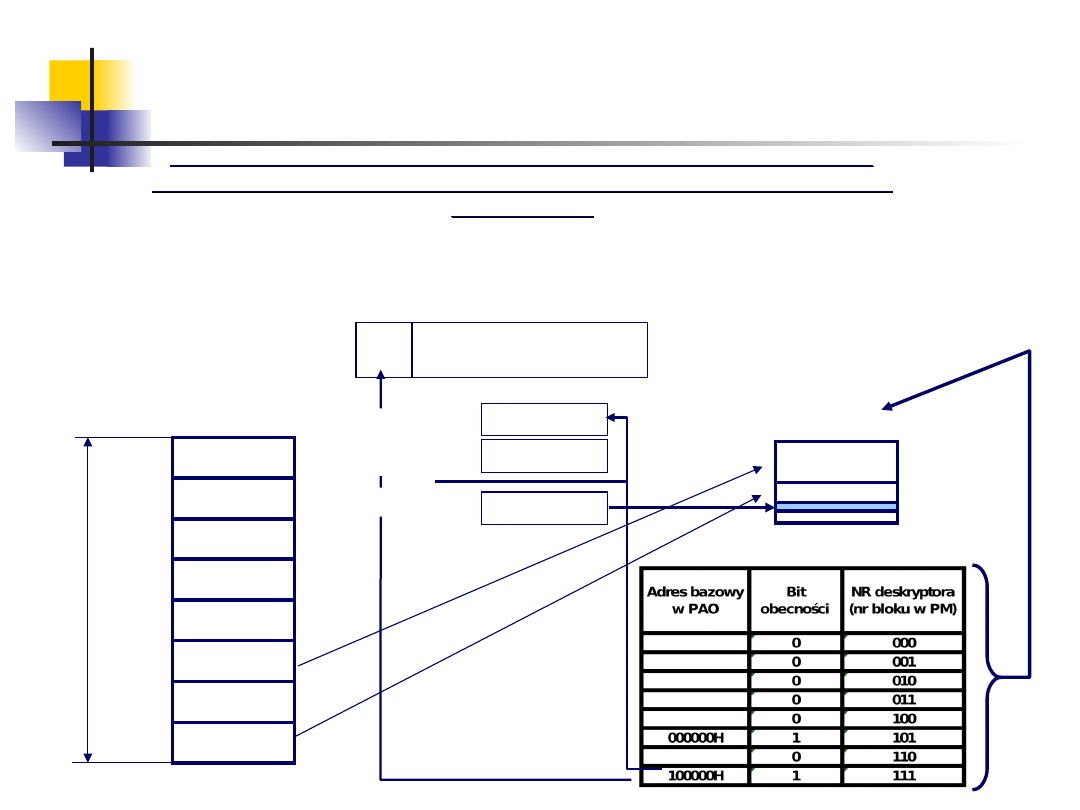

Adres bazowy

w PAO

Bit

obecności

NR deskryptora

(nr bloku w PM)

0

000

0

001

0

010

100000H

1

011

0

100

000000H

1

101

0

110

0

111

Deskryptor bloku

Deskryptor bloku

3

3

20

20

0

0

000000H

000000H

0FFFFFH

0FFFFFH

100000H

100000H

1FFFFFH

1FFFFFH

Adresy

Adresy

pamięci

pamięci

Tablica deskryptorów

Tablica deskryptorów

1111111111111111

1111111111111111

1111

1111

= 3FFFFFH

= 3FFFFFH

20

20

2

2

0

0

0

0

selektor

selektor

przesunięcie

przesunięcie

100000H

100000H

FFFFFH

FFFFFH

+

+

1FFFFFH

1FFFFFH

Adres fizyczny =

Adres fizyczny =

Adres bazowy w

Adres bazowy w

PAO

PAO

Przesunięcie

Przesunięcie

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

1.Program odwołuje się do adresu wirtualnego 3FFFFFH składającego się z:

1.Program odwołuje się do adresu wirtualnego 3FFFFFH składającego się z:

•

pola selektora: w którym bloku programu znajduje się informacja czyli którego

pola selektora: w którym bloku programu znajduje się informacja czyli którego

deskryptora użyć?

deskryptora użyć?

•

przesunięcia: jak daleko od początku bloku znajduje się informacja?

przesunięcia: jak daleko od początku bloku znajduje się informacja?

2. Selektor (w naszym przypadku) zawiera informację o bloku nr 3

2. Selektor (w naszym przypadku) zawiera informację o bloku nr 3

3. Czy blok nr 3 jest w PAO? Czy bit obecności jest równy „1”? - w tym przypadku jest !

3. Czy blok nr 3 jest w PAO? Czy bit obecności jest równy „1”? - w tym przypadku jest !

4. Odczytywany jest adres bazowy bloku w PAO

4. Odczytywany jest adres bazowy bloku w PAO

5. Do adresu bazowego dodawane jest przesunięcie z adresu wirtualnego

5. Do adresu bazowego dodawane jest przesunięcie z adresu wirtualnego

5. Otrzymany 21 bitowy adres jest adresem fizycznym w PAO, pod którym znajduje się

5. Otrzymany 21 bitowy adres jest adresem fizycznym w PAO, pod którym znajduje się

poszukiwana informacja

poszukiwana informacja

1. Program odwołuje się do adresu wirtualnego 3FFFFFH składającego

1. Program odwołuje się do adresu wirtualnego 3FFFFFH składającego

się z:

się z:

•

pola selektora: w którym bloku programu znajduje się

pola selektora: w którym bloku programu znajduje się

informacja czyli którego deskryptora użyć?

informacja czyli którego deskryptora użyć?

•

przesunięcia: jak daleko od początku bloku znajduje się

przesunięcia: jak daleko od początku bloku znajduje się

informacja?

informacja?

2. Selektor (w naszym przypadku) zawiera informację o bloku nr 3

2. Selektor (w naszym przypadku) zawiera informację o bloku nr 3

3. Czy blok nr 3 jest w PAO? Czy bit obecności jest równy „1”? - w tym

3. Czy blok nr 3 jest w PAO? Czy bit obecności jest równy „1”? - w tym

przypadku jest !

przypadku jest !

4. Odczytywany jest adres bazowy bloku w PAO

4. Odczytywany jest adres bazowy bloku w PAO

5. Do adresu bazowego dodawane jest przesunięcie z adresu

5. Do adresu bazowego dodawane jest przesunięcie z adresu

wirtualnego

wirtualnego

5. Otrzymany 21 bitowy adres jest adresem fizycznym w PAO, pod

5. Otrzymany 21 bitowy adres jest adresem fizycznym w PAO, pod

którym znajduje się poszukiwana informacja

którym znajduje się poszukiwana informacja

Algorytm tworzenia (obliczania) 21 bitowego adresu fizycznego

Algorytm tworzenia (obliczania) 21 bitowego adresu fizycznego

na podstawie 23 bitowego adresu wirtualnego

na podstawie 23 bitowego adresu wirtualnego

Gdy blok nie jest umieszczony w pamięci operacyjnej????

Gdy blok nie jest umieszczony w pamięci operacyjnej????

przykład dla procesora 80286 (najprostszy)

przykład dla procesora 80286 (najprostszy)

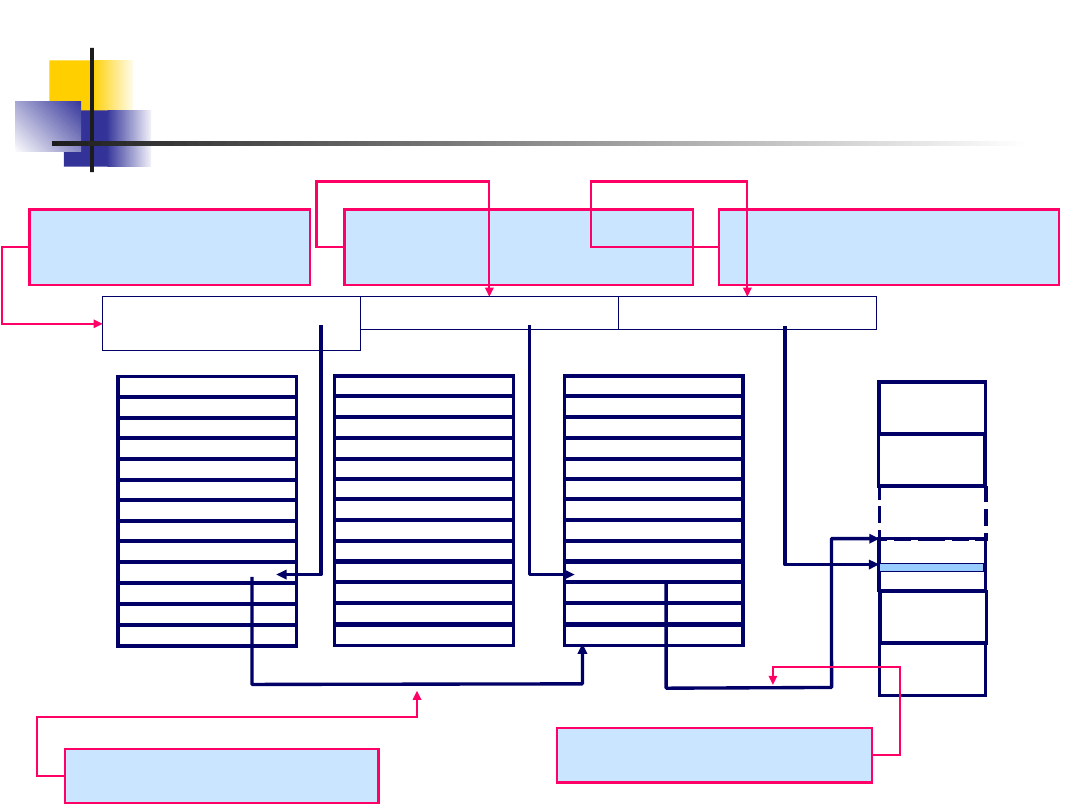

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

3.1. Bloku nr 7 nie ma w PAO

3.1. Bloku nr 7 nie ma w PAO

3.2. Blok nr 7 wczytany jest do PAO w miejsce np. bloku nr 3

3.2. Blok nr 7 wczytany jest do PAO w miejsce np. bloku nr 3

3.3. Modyfikowane są deskryptory usuniętego i załadowanego bloku

3.3. Modyfikowane są deskryptory usuniętego i załadowanego bloku

Algorytm dodatkowych czynności tworzenia (obliczania) 21

Algorytm dodatkowych czynności tworzenia (obliczania) 21

bitowego adresu fizycznego na podstawie 23 bitowego adresu

bitowego adresu fizycznego na podstawie 23 bitowego adresu

wirtualnego

wirtualnego

Numer

Numer

bloku

bloku

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

1MB

00

00

0

0

00

00

1

1

01

01

0

0

01

01

1

1

10

10

0

0

10

10

1

1

11

11

0

0

11

11

1

1

11

11

1

1

0

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

M

8

M

B

B

PAMIĘĆ

PAMIĘĆ

MASOWA

MASOWA

1MB

1MB

1MB

1MB

5

5

7

7

PAMIĘĆ

PAMIĘĆ

OPERACYJNA

OPERACYJNA

20

20

0

0

000000H

000000H

0FFFFFH

0FFFFFH

100000H

100000H

1FFFFFH

1FFFFFH

Adresy

Adresy

pamięci

pamięci

Tablica deskryptorów

Tablica deskryptorów

1111000000000000

1111000000000000

00000

00000

=

=

7F0000H

7F0000H

20

20

2

2

0

0

0

0

selektor

selektor

przesunięcie

przesunięcie

100000H

100000H

F0000H

F0000H

+

+

1F0000H

1F0000H

Adres fizyczny =

Adres fizyczny =

Adres bazowy w

Adres bazowy w

PAO

PAO

Przesunięcie

Przesunięcie

przykład dla procesora 80286 (najprostszy)

przykład dla procesora 80286 (najprostszy)

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

Adres logiczny w trybie chronionym składa się z:

Adres logiczny w trybie chronionym składa się z:

•

16 bitowej części segmentowej (selektor segmentu)

16 bitowej części segmentowej (selektor segmentu)

•

32 bitowego przemieszczenia (adres efektywny)

32 bitowego przemieszczenia (adres efektywny)

Teoretycznie możliwe jest więc adresowanie przestrzeni logicznej o pojemności 2

Teoretycznie możliwe jest więc adresowanie przestrzeni logicznej o pojemności 2

48

48

adresów tj. 256TB pamięci.

adresów tj. 256TB pamięci.

Nie wszystkie jednak bajty części segmentowej są wykorzystane do adresowania:

Nie wszystkie jednak bajty części segmentowej są wykorzystane do adresowania:

•

bajty 0 - 13 wyznaczają numer deskryptora segmentu (tak na prawdę jeden z

bajty 0 - 13 wyznaczają numer deskryptora segmentu (tak na prawdę jeden z

tych bitów określa typ tablicy deskryptorów - lokalny lub globalny) co pozwala na

tych bitów określa typ tablicy deskryptorów - lokalny lub globalny) co pozwala na

wybór 2

wybór 2

14

14

=16384=16k deskryptorów segmentu

=16384=16k deskryptorów segmentu

•

bajty 14 - 15 określają poziom ochronny zadania żądającego dostępu do pamięci

bajty 14 - 15 określają poziom ochronny zadania żądającego dostępu do pamięci

i przestrzeń adresów widzianych przez program wynosi 2

i przestrzeń adresów widzianych przez program wynosi 2

46

46

adresów czyli 64TB

adresów czyli 64TB

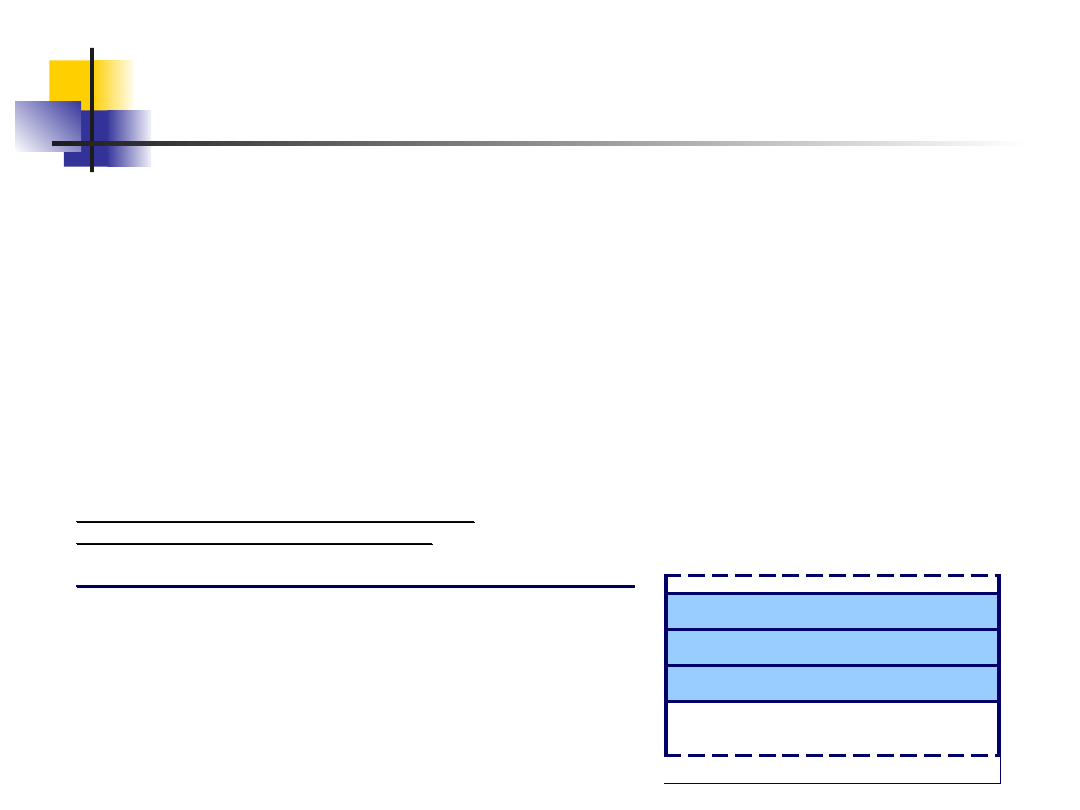

Tablica zajmuje jeden segment o objętości 64kB. W tablicy deskryptorów występuje

Tablica zajmuje jeden segment o objętości 64kB. W tablicy deskryptorów występuje

8192 pól (tzw. deskryptorów segmentów). Każdy deskryptor zawiera następujące

8192 pól (tzw. deskryptorów segmentów). Każdy deskryptor zawiera następujące

pola:

pola:

•

adres bazowy segmentu (32 bity)

adres bazowy segmentu (32 bity)

•

wielkość segmentu (20 bitów)

wielkość segmentu (20 bitów)

- segmenty nie muszą być jednakowe

- segmenty nie muszą być jednakowe

•

atrybuty

atrybuty

•

czy segment obecny fizycznie w pamięci (1 bit)

czy segment obecny fizycznie w pamięci (1 bit)

•

pole dostępne dla programu (1 bit)

pole dostępne dla programu (1 bit)

•

poziom ochronny (2 bity)

poziom ochronny (2 bity)

•

ziarnistość segmentu (1 bit)

ziarnistość segmentu (1 bit)

•

długość słowa (1 bit)

długość słowa (1 bit)

•

czy segment w pamięci (1 bit)

czy segment w pamięci (1 bit)

•

typ segmentu (3 bity)

typ segmentu (3 bity)

•

czy segment użyty (1 bit)

czy segment użyty (1 bit)

deskryptor segmentu

deskryptor segmentu

deskryptor segmentu

deskryptor segmentu

deskryptor segmentu

deskryptor segmentu

Tablica deskryptorów

Tablica deskryptorów

..

.

..

.

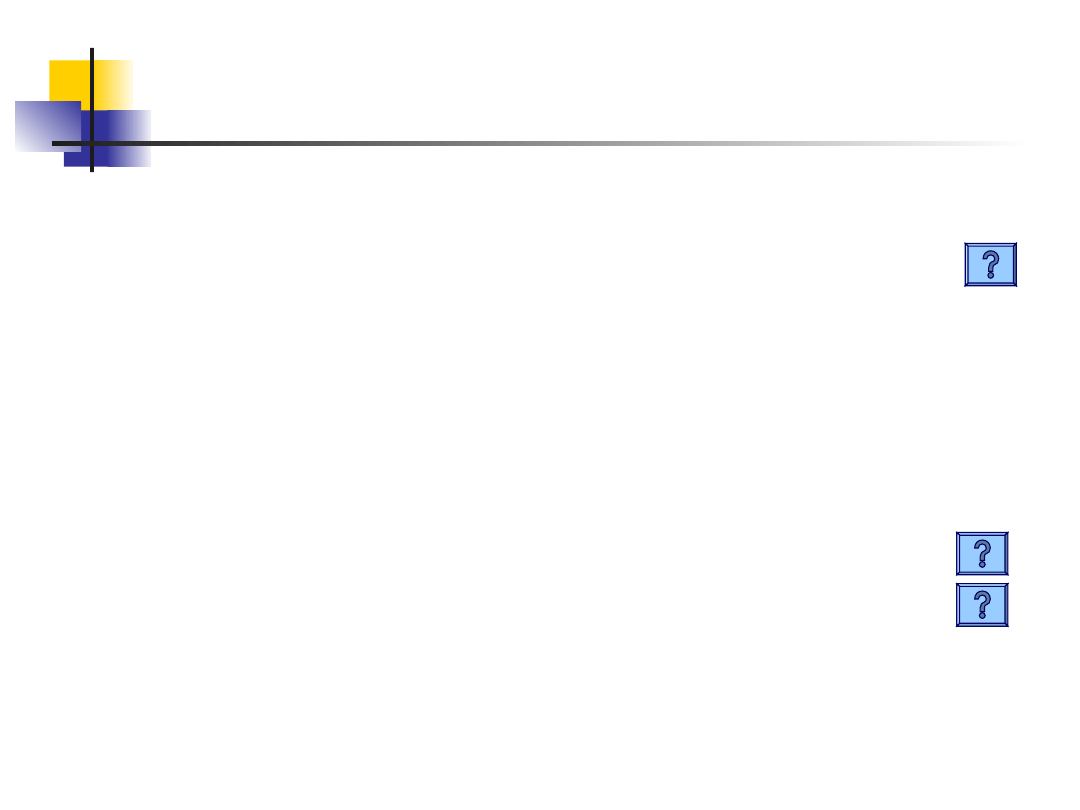

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

przykład dla procesora pentium (uproszczony)

przykład dla procesora pentium (uproszczony)

+

+

Selektor segmentu

Selektor segmentu

0

0

13

13

15

15

PAMIĘĆ

PAMIĘĆ

OPERACYJNA (PAO)

OPERACYJNA (PAO)

Tablica deskryptorów

Tablica deskryptorów

deskryptor

deskryptor

Adres efektywny (przemieszczenie)

Adres efektywny (przemieszczenie)

0

0

31

31

Adres bazowy

Adres bazowy

s

e

g

m

e

n

t

s

e

g

m

e

n

t

s

e

g

m

e

n

t

s

e

g

m

e

n

t

A

d

re

s

fi

zy

c

z

n

y

A

d

re

s

fi

zy

c

z

n

y

3

2

b

it

y

3

2

b

it

y

Jeśli w deskryptorze istnieje adnotacja, że

Jeśli w deskryptorze istnieje adnotacja, że

segmentu nie ma w PAO to segment jest

segmentu nie ma w PAO to segment jest

przenoszony z pamięci masowej do operacyjnej w

przenoszony z pamięci masowej do operacyjnej w

miejsce innego segmentu

miejsce innego segmentu

Adres logiczny - 46 bitów

Adres logiczny - 46 bitów

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

Selektorem wybierającym odpowiednią pozycję w tablicy deskryptorów jest zawartość

Selektorem wybierającym odpowiednią pozycję w tablicy deskryptorów jest zawartość

rejestru segmentowego (14 bitów bo 2 bity określają poziom ochrony). Umożliwia to wybór

rejestru segmentowego (14 bitów bo 2 bity określają poziom ochrony). Umożliwia to wybór

2

2

14

14

=16k segmentów.

=16k segmentów.

Przesunięcie stanowi 32 bity więc rozmiar segmentu wynosi 2

Przesunięcie stanowi 32 bity więc rozmiar segmentu wynosi 2

32

32

=4GB

=4GB

Tak więc wielkość przestrzeni pamięci wirtualnej wynosi 16k

Tak więc wielkość przestrzeni pamięci wirtualnej wynosi 16k

x

x

4GB=64TB

4GB=64TB

Algorytm tworzenia (obliczania) 32 bitowego adresu

Algorytm tworzenia (obliczania) 32 bitowego adresu

fizycznego na podstawie adresu logicznego

fizycznego na podstawie adresu logicznego

1. Program odwołuje się do adresu logicznego składającego się z:

1. Program odwołuje się do adresu logicznego składającego się z:

•

selektora segmentu

selektora segmentu

•

adresu efektywnego (przemieszczenia)

adresu efektywnego (przemieszczenia)

2. Selektor wskazuje określony deskryptor segmentu w tablicy

2. Selektor wskazuje określony deskryptor segmentu w tablicy

deskryptorów

deskryptorów

3. Jedno z pól deskryptora określa czy segment jest obecny w PAO.

3. Jedno z pól deskryptora określa czy segment jest obecny w PAO.

Jeśli nie to następuje wczytanie segmentu do PAO z pamięci

Jeśli nie to następuje wczytanie segmentu do PAO z pamięci

masowej.

masowej.

Z deskryptora można określić również:

Z deskryptora można określić również:

•

adres początku segmentu = adres bazowy

adres początku segmentu = adres bazowy

•

adres końca segmentu = adres bazowy + wielkość segmentu

adres końca segmentu = adres bazowy + wielkość segmentu

Jeśli przemieszczenie będzie większe od wielkości segmentu to

Jeśli przemieszczenie będzie większe od wielkości segmentu to

procesor nie dopuści do zamazania sąsiednich segmentów

procesor nie dopuści do zamazania sąsiednich segmentów

przechodząc w tryb obsługi błędu (tzw. wyjątek) - to jest przewaga

przechodząc w tryb obsługi błędu (tzw. wyjątek) - to jest przewaga

trybu wirtualnego nad rzeczywistym

trybu wirtualnego nad rzeczywistym

4. Odczytanie z deskryptora adresu bazowego i dodanie do niego

4. Odczytanie z deskryptora adresu bazowego i dodanie do niego

przemieszczenia (adresu efektywnego) w celu określenia adresu

przemieszczenia (adresu efektywnego) w celu określenia adresu

fizycznego poszukiwanej komórki pamięci.

fizycznego poszukiwanej komórki pamięci.

PRACA PROCESORA W TRYBIE

PRACA PROCESORA W TRYBIE

WIRTUALNYM CHRONIONYM

WIRTUALNYM CHRONIONYM

Mechanizm pamięci wirtualnej polega na tym, że nie cała przestrzeń

Mechanizm pamięci wirtualnej polega na tym, że nie cała przestrzeń

adresów logicznych widzianych przez zadanie ma swoje oparcie w pamięci

adresów logicznych widzianych przez zadanie ma swoje oparcie w pamięci

fizycznej.

fizycznej.

Przestrzeń adresów logicznych (selektor segmentu: przemieszczenie)

Przestrzeń adresów logicznych (selektor segmentu: przemieszczenie)

odwołujących się do potrzebnych zadaniu segmentów kodu, danych i stosu

odwołujących się do potrzebnych zadaniu segmentów kodu, danych i stosu

jest odwzorowywana na 4GB przestrzeń 32 bitowych adresów liniowych, z

jest odwzorowywana na 4GB przestrzeń 32 bitowych adresów liniowych, z

których wszystkie mogą być użyte w zadaniu.

których wszystkie mogą być użyte w zadaniu.

Jednak ta przestrzeń nie może być cała zrealizowana w fizycznej pamięci

Jednak ta przestrzeń nie może być cała zrealizowana w fizycznej pamięci

operacyjnej komputera. Dlatego w praktyce zostaje podzielona na

operacyjnej komputera. Dlatego w praktyce zostaje podzielona na

segmenty i tylko część spośród nich jest jednocześnie przechowywana w

segmenty i tylko część spośród nich jest jednocześnie przechowywana w

pamięci fizycznej (operacyjnej).

pamięci fizycznej (operacyjnej).

Zarządzaniem przeładowywaniem segmentów pomiędzy dyskiem i

Zarządzaniem przeładowywaniem segmentów pomiędzy dyskiem i

pamięcią operacyjną zajmuje się system operacyjny za pomocą funkcji

pamięcią operacyjną zajmuje się system operacyjny za pomocą funkcji

wykonywanych przez procesor w trybie tzw. wyjątku procesora (tzn.

wykonywanych przez procesor w trybie tzw. wyjątku procesora (tzn.

przerwania generowanego przez sam procesor).

przerwania generowanego przez sam procesor).

MECHANIZM PAMIĘCI WIRTUALNEJ

MECHANIZM PAMIĘCI WIRTUALNEJ

PODSUMOWANIE

PODSUMOWANIE

W procesorze Pentium pracującym w trybie wirtualnym, oprócz mechanizmu

W procesorze Pentium pracującym w trybie wirtualnym, oprócz mechanizmu

segmentacji, dostępny jest także mechanizm stronicowania.

segmentacji, dostępny jest także mechanizm stronicowania.

Mechanizm stronicowania pozwala na podział pamięci wirtualnej na strony o stałej

Mechanizm stronicowania pozwala na podział pamięci wirtualnej na strony o stałej

wielkości (4kB lub 4MB)

wielkości (4kB lub 4MB)

STRONICOWANIE

STRONICOWANIE

ADRES LINIOWY

ADRES FIZYCZNY

S

E

G

M

E

N

T

A

C

JA

S

T

R

O

N

IC

O

W

A

N

IE

wyłączanie

stronicowania

0

3

1

Selektor segmentu

Selektor segmentu

0

0

13

13

15

15

Adres efektywny (przemieszczenie)

Adres efektywny (przemieszczenie)

0

0

31

31

Adres logiczny - 46 bitów

Adres logiczny - 46 bitów

0

3

1

Mechanizm stronicowania jest wspomagany przez pamięć CACHE

Mechanizm stronicowania jest wspomagany przez pamięć CACHE

pozycja w katalogu

pozycja w katalogu

stron

stron

pozycja na stronie

pozycja na stronie

0

0

21

21

22

22

31

31

adres strony w

adres strony w

pamięci

pamięci

wybiera stronę w pamięci

wybiera stronę w pamięci

katalog stron

katalog stron

4MB strony w

4MB strony w

pamięci

pamięci

1

1

1024

1024

1

1

2

2

1k

1k

STRONICOWANIE

STRONICOWANIE

Strony 4MB

Strony 4MB

10 bitów wybiera 1 z

1024 pozycji katalogu

stron

Wskazuje na adres początku

wybranej strony

Wskazuje na 1 z 2

22

(4194304)

komórek pamięci na wybranej

stronie

Mechanizm stronicowania ustawia się przy pomocy bitu PG w rejestrze

Mechanizm stronicowania ustawia się przy pomocy bitu PG w rejestrze

sterującym CR0

sterującym CR0

Strony 4kB

Strony 4kB

pozycja w katalogu

pozycja w katalogu

stron

stron

pozycja w tablicy stron

pozycja w tablicy stron

pozycja na stronie

pozycja na stronie

11

11

12

12

0

0

21

21

22

22

31

31

adres tablicy

adres tablicy

stron

stron

adres strony w

adres strony w

pamięci

pamięci

adres strony w

adres strony w

pamięci

pamięci

wybiera tabelę stron

wybiera tabelę stron

wybiera stronę w pamięci

wybiera stronę w pamięci

katalog stron

katalog stron

tabele stron

tabele stron

4kB strony w

4kB strony w

pamięci

pamięci

...

...

1

1

1024

1024

1

1

1024

1024

1

1

1024

1024

1

1

1024

1024

1

1

2

2

1

1

M

M

STRONICOWANIE

STRONICOWANIE

10 bitów wybiera 1 z

1024 pozycji katalogu

stron

10 bitów wybiera 1 z 1024

adresów stron w wybranej

tabeli stron

Wskazuje na 1 z 2

12

(4096)

komórek pamięci na wybranej

stronie

Wskazuje na 1 z 1024 tabel

stron

Wskazuje na adres początku

wybranej strony

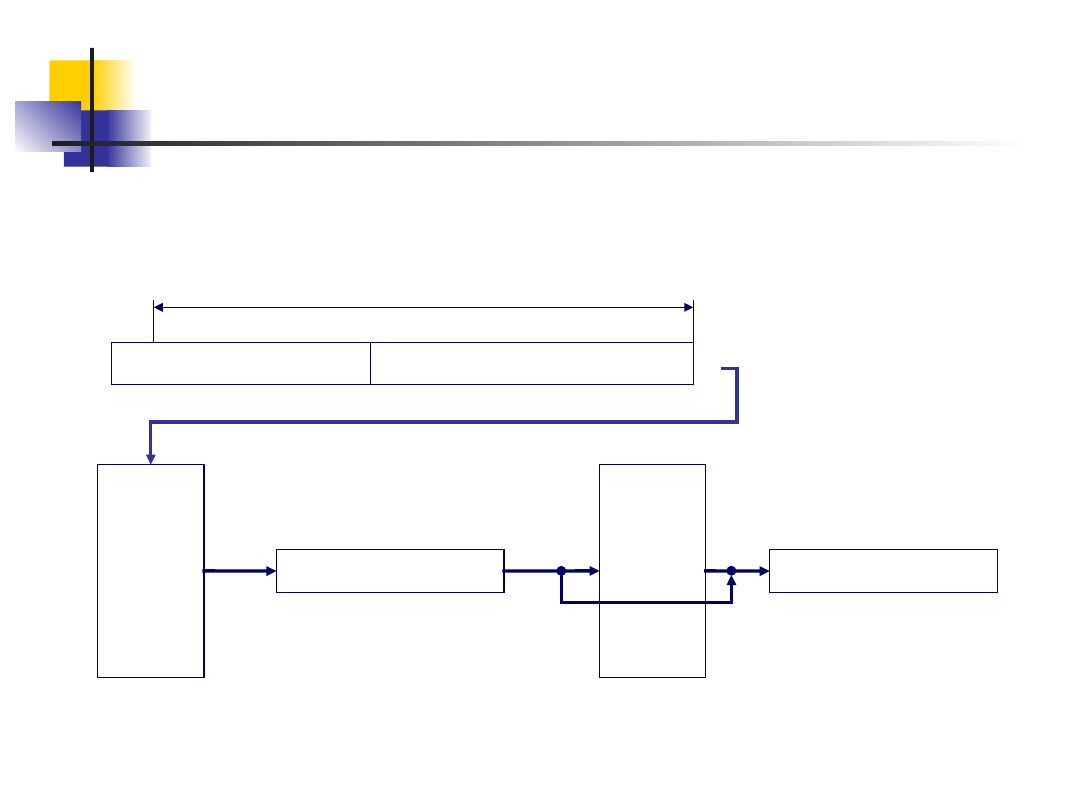

Praca wielozadaniowa polega na przełączaniu zadań.

Praca wielozadaniowa polega na przełączaniu zadań.

1. Procesor realizuje zadanie do momentu:

1. Procesor realizuje zadanie do momentu:

•

upływu czas przeznaczonego na realizację zadania

upływu czas przeznaczonego na realizację zadania

lub pojawieniu się zadania o wyższym priorytecie

lub pojawieniu się zadania o wyższym priorytecie

•

w którym chwilowo brak określonych informacji

w którym chwilowo brak określonych informacji

•

żądania zmiany zadania przez użytkownika

żądania zmiany zadania przez użytkownika

2. Zapamiętanie stanu realizacji zadania

2. Zapamiętanie stanu realizacji zadania

3. Zmiana wykonywanego zadania

3. Zmiana wykonywanego zadania

itd.....

itd.....

Istnieje konieczność kontroli dostępu poszczególnych

Istnieje konieczność kontroli dostępu poszczególnych

zadań do:

zadań do:

•

informacji

informacji

•

zasobów systemu

zasobów systemu

Wielozadaniowość może być realizowana programowo, ale

Wielozadaniowość może być realizowana programowo, ale

procesor Pentium realizuje to sprzętowo wykorzystując

procesor Pentium realizuje to sprzętowo wykorzystując

•

systemowe segmenty stanu zadania (TSS)

systemowe segmenty stanu zadania (TSS)

•

rejestr zadań (TR)

rejestr zadań (TR)

PRACA WIELOZADANIOWA W

PRACA WIELOZADANIOWA W

SYSTEMIE JEDNOPROCESOROWYM

SYSTEMIE JEDNOPROCESOROWYM

DZIĘKUJĘ ZA UWAGĘ !

DZIĘKUJĘ ZA UWAGĘ !

PRACA WIELOZADANIOWA W

PRACA WIELOZADANIOWA W

SYSTEMIE JEDNOPROCESOROWYM

SYSTEMIE JEDNOPROCESOROWYM

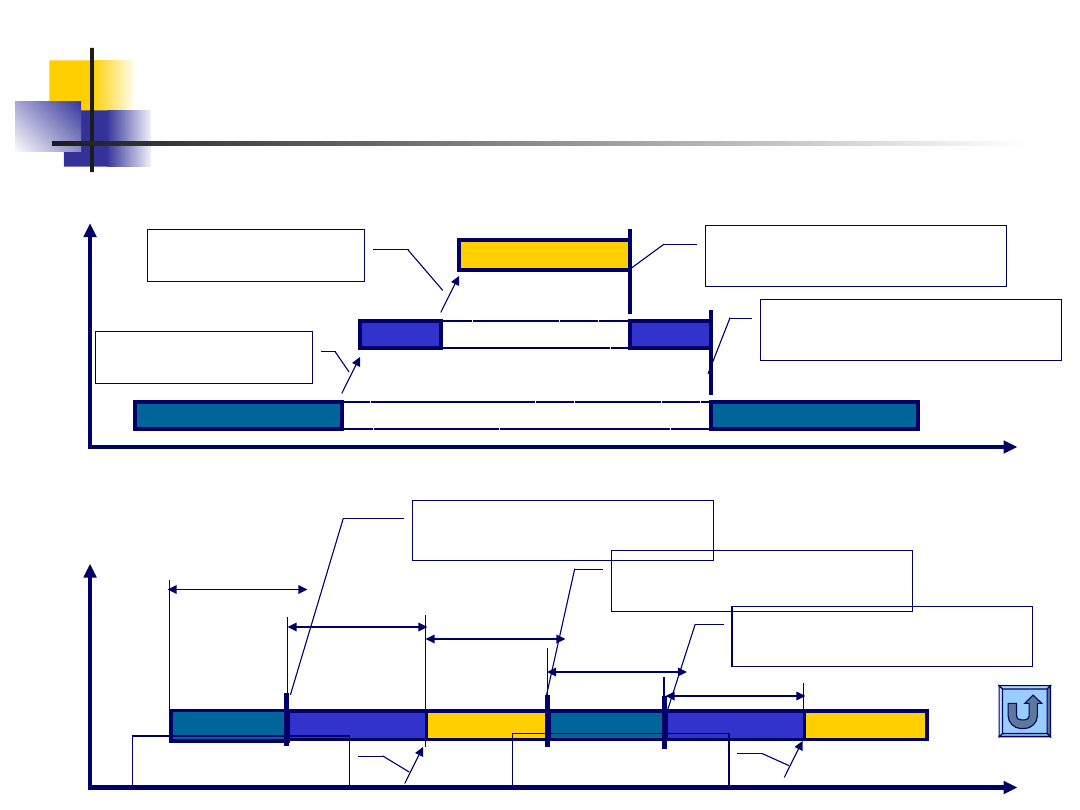

•

obsługa priorytetowa zadań z wywłaszczaniem

•

obsługa cykliczna zadań z wywłaszczaniem (ten sam priorytet i

limit czasu na obsługę zadania)

2

3

1

1

2

czas

1

p

ri

o

ry

te

t

za

d

a

n

ia

czas

p

ri

o

ry

te

t

z

a

d

a

n

ia

2

3

1

2 (cd.)

maksymaln

y czas

obsługi

zadania

3

zakończenie obsługi zadania

w danym cyklu

obliczeniowym

zakończenie obsługi zadania

w danym cyklu

obliczeniowym

zakończenie obsługi zadania

w danym cyklu

obliczeniowym

wywłaszczenie

zadania

wywłaszczenie

zadania

zakończenie obsługi zadania

w danym cyklu

obliczeniowym

zakończenie obsługi zadania

w danym cyklu

obliczeniowym

wywłaszczenie

zadania

wywłaszczenie

zadania

maksymaln

y czas

obsługi

zadania

maksymaln

y czas

obsługi

zadania

maksymaln

y czas

obsługi

zadania

maksymaln

y czas

obsługi

zadania

PRACA WIELOZADANIOWA W

PRACA WIELOZADANIOWA W

SYSTEMIE JEDNOPROCESOROWYM

SYSTEMIE JEDNOPROCESOROWYM

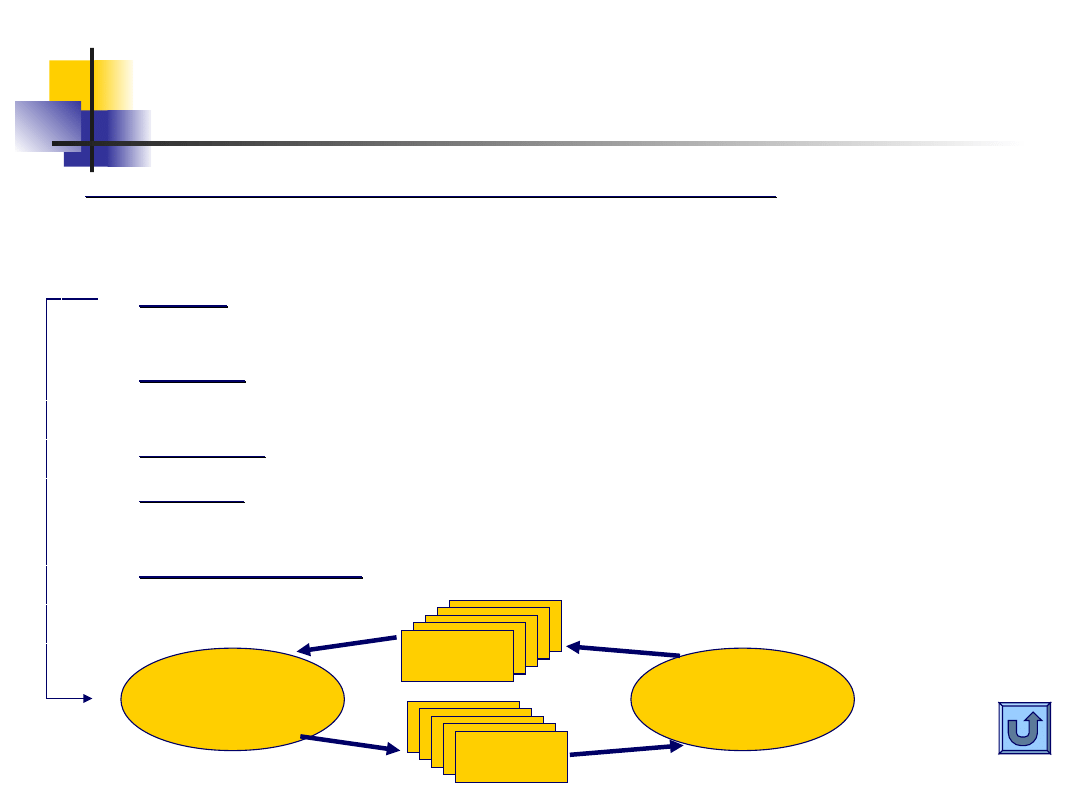

Typowe mechanizmy jądra RTOS:

Typowe mechanizmy jądra RTOS:

•

kolejki

kolejki

do wymiany informacji między zadaniami za pomocą

do wymiany informacji między zadaniami za pomocą

komunikatów

komunikatów

•

gniazda

gniazda

do wymiany informacji między zadaniami a systemami

do wymiany informacji między zadaniami a systemami

zewnętrznymi za pomocą standardowych protokołów

zewnętrznymi za pomocą standardowych protokołów

•

semafory

semafory

do synchronizacji pracy zadań

do synchronizacji pracy zadań

•

sygnały

sygnały

do

wymiany

informacji

między

zdarzeniami

do

wymiany

informacji

między

zdarzeniami

zewnętrznymi a zadaniami (np. do obsługi przerwań)

zewnętrznymi a zadaniami (np. do obsługi przerwań)

•

wspólna pamięć

wspólna pamięć

do korzystania ze wspólnych struktur danych

do korzystania ze wspólnych struktur danych

przez wiele zadań

przez wiele zadań

Mechanizmy wymiany informacji między zadaniami

Mechanizmy wymiany informacji między zadaniami

są niezbędne ze

są niezbędne ze

względu na komunikację między zadaniami.

względu na komunikację między zadaniami.

Zadanie

Zadanie

1

1

Zadanie

Zadanie

2

2

komunikat

komunikat

Kolejka

Kolejka

komunikatów 1

komunikatów 1

Kolejka

Kolejka

komunikatów 2

komunikatów 2

Po

d

st

a

w

o

w

y

m

e

ch

a

n

iz

m

Po

d

st

a

w

o

w

y

m

e

ch

a

n

iz

m

PRACA WIELOZADANIOWA W

PRACA WIELOZADANIOWA W

SYSTEMIE JEDNOPROCESOROWYM

SYSTEMIE JEDNOPROCESOROWYM

W

celu

ułatwienia

przenoszenia

fragmentów

programów

W

celu

ułatwienia

przenoszenia

fragmentów

programów

sterujących urządzeniami peryferyjnymi, dostęp do specyficznych

sterujących urządzeniami peryferyjnymi, dostęp do specyficznych

dla danego programu układów peryferyjnych będzie się odbywał

dla danego programu układów peryferyjnych będzie się odbywał

przez wydzielone fragmenty oprogramowania (sterowniki urządzeń)

przez wydzielone fragmenty oprogramowania (sterowniki urządzeń)

kontaktujące się z zadaniami za pośrednictwem systemu

kontaktujące się z zadaniami za pośrednictwem systemu

operacyjnego. System wykorzystuje najczęściej do tego celu

operacyjnego. System wykorzystuje najczęściej do tego celu

specyficzne funkcje:

specyficzne funkcje:

Mechanizmy dostępu do specyficznych układów peryferyjnych :

Mechanizmy dostępu do specyficznych układów peryferyjnych :

create( )

create( )

zdefiniowanie określonej klasy układów peryferyjnych

zdefiniowanie określonej klasy układów peryferyjnych

delete( )

delete( )

usunięcie zdefiniowanej uprzednio klasy układów

usunięcie zdefiniowanej uprzednio klasy układów

peryferyjnych

peryferyjnych

open( )

open( )

otwarcie dostępu do danego układu peryferyjnego

otwarcie dostępu do danego układu peryferyjnego

należącego do uprzednio zdefiniowanej klasy

należącego do uprzednio zdefiniowanej klasy

close( )

close( )

zamknięcie dostępu do danego układu peryferyjnego

zamknięcie dostępu do danego układu peryferyjnego

należącego do uprzednio zdefiniowanej klasy

należącego do uprzednio zdefiniowanej klasy

read( )

read( )

czytanie z danego układu peryferyjnego, do którego

czytanie z danego układu peryferyjnego, do którego

dostęp został uprzednio otwarty

dostęp został uprzednio otwarty

write( )

write( )

wpisanie do danego układu peryferyjnego, do którego

wpisanie do danego układu peryferyjnego, do którego

dostęp został uprzednio otwarty

dostęp został uprzednio otwarty

ioctl( )

ioctl( )

konfigurowanie danego układu peryferyjnego, do

konfigurowanie danego układu peryferyjnego, do

którego dostęp został uprzednio otwarty

którego dostęp został uprzednio otwarty

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

Wyszukiwarka

Podobne podstrony:

architektura sk 05

Md10 2, GDA?SK 12

STR TYT, GDA?SK 12

architektura sk 01

architektura sk 04

architektura sk 03

architektura sk 08

kolo projektowanie, ARCHITEKTURA KRAJOBRAZU(12)

architektura sk 09

architektura sk 07

architektura sk 13

architektura sk 06

sk 12, Psychoogia

architektura sk 11

architektura sk 02

architektura sk 10

projektowanie Wykłady-1, ARCHITEKTURA KRAJOBRAZU(12)

architektura sk 05

architektura sk 01

więcej podobnych podstron