Języki Opisu Sprzętu

Wykład 3

III rok kierunek Elektronika

J.Kasperek P.J.Rajda

1. VHDL – po co?

2. VHDL – co to jest?

3. VHDL – jak, gdzie, kiedy?

4. VHDL – i co z tego?

5. VHDL – wczoraj, dziś i jutro

6. VHDL – standardy

7. VHDL – literatura, źródła, firmy

8. VHDL – podstawowe deklaracje

9. VHDL – jednostki projektowe

10. VHDL – przykłady kodu

Program wykładu – DEKALOG

Kontakt z prowadzącymi:

C-3 p.502 tel. (617)3980

mgr inż. Jerzy Kasperek kasperek@uci.agh.edu.pl

mgr inż. Paweł J.Rajda pjrajda@uci.agh.edu.pl

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

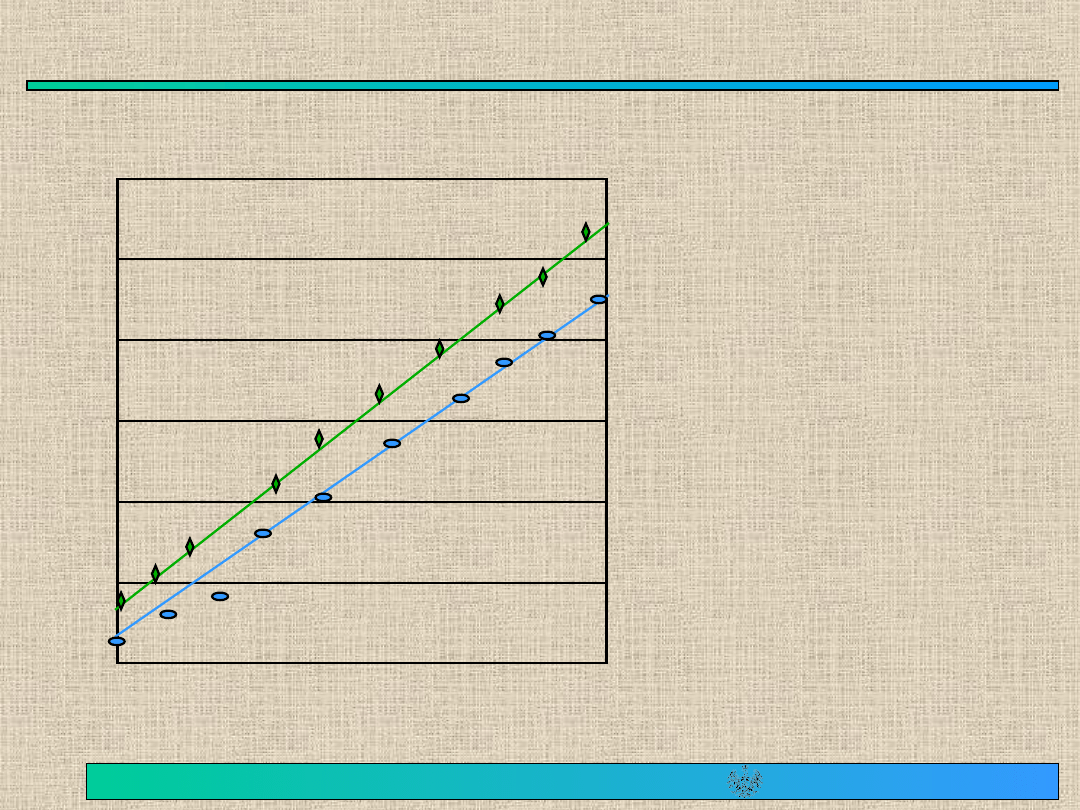

VHDL – po co? Złożoność

projektów

i ???

1K

10K

100K

1M

10M

100M

1G

1970

1980

1990

1998

4004

8080

8085

8086

80286

80386

80486

Pentium

i ???

4K

16K

64K

256K

1M

4M

16M

64M

256M

Wymogi pamięci:

1.50 na rok

Wymogi CPU

1.35 na rok

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Potrzeba narzędzia:

• 1970 - INTEL 4004 4 projektantów 1 tys.

tranzystorów

• 1982 - INTEL 80286

20 projektantów 100 tys.

tranzystorów

• 1992 - INTEL PENTIUM 100 projektantów 3 mln

tranzystorów

• 2002 - ???

1000 projektantów 150

mln tranzystorów

Współczesne wymagania:

hardware-software codesign !!!

VHDL – po co? Złożoność

projektów

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Project: | 10K FPGA | 100K ASIC |800K 4ASICs

Activity | SS SE BA | SS SE BA | SS SE BA

--------------------------------------------+------------+-----------

Requirements Development | 0 5 2 | 0 7 5 | 0 8 6

Top-level design | 5 15 5 | 7 16 7 | 8 18 8

Detail design | 15 30 10 | 16 28 13 | 18 32 15

Implementation and Timing Est. | 30 45 15 | 28 40 9 | 32 45 10

Component verification | 35 50 15 | 30 43 9 | 35 48 9

Component integration | 45 60 15 | 43 53 8 | 48 60 10

Device verification | 60 80 15 | 53 61 5 | 60 67 4

System verification preparation| - - - | 43 61 6 | 48 67 5

System verification | - - - | 61 70 6 | 67 75 5

Synthesis & timing checks | 60 80 8 | 53 70 12 | 60 75 11

Place & Route, Timing Verified | 80 85 5 | 70 80 7 | 75 82 5

Fabrication | - - - | 80 90 - | 82 90 -

System integration | 85 100 6 | 90 100 7 | 90 100 6

Ancillary functions | - - 4 | - - 6 | - - 6

--------------------------------------------+------------+-----------

Project estimates | | |

Time: (weeks) | 20 | 40 | 60

Manpower: (man-weeks) | 20 | 120 | 1200

Productivity: (gates/man week) | 500 | 833 | 667

VHDL – po co?

Przykłady

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

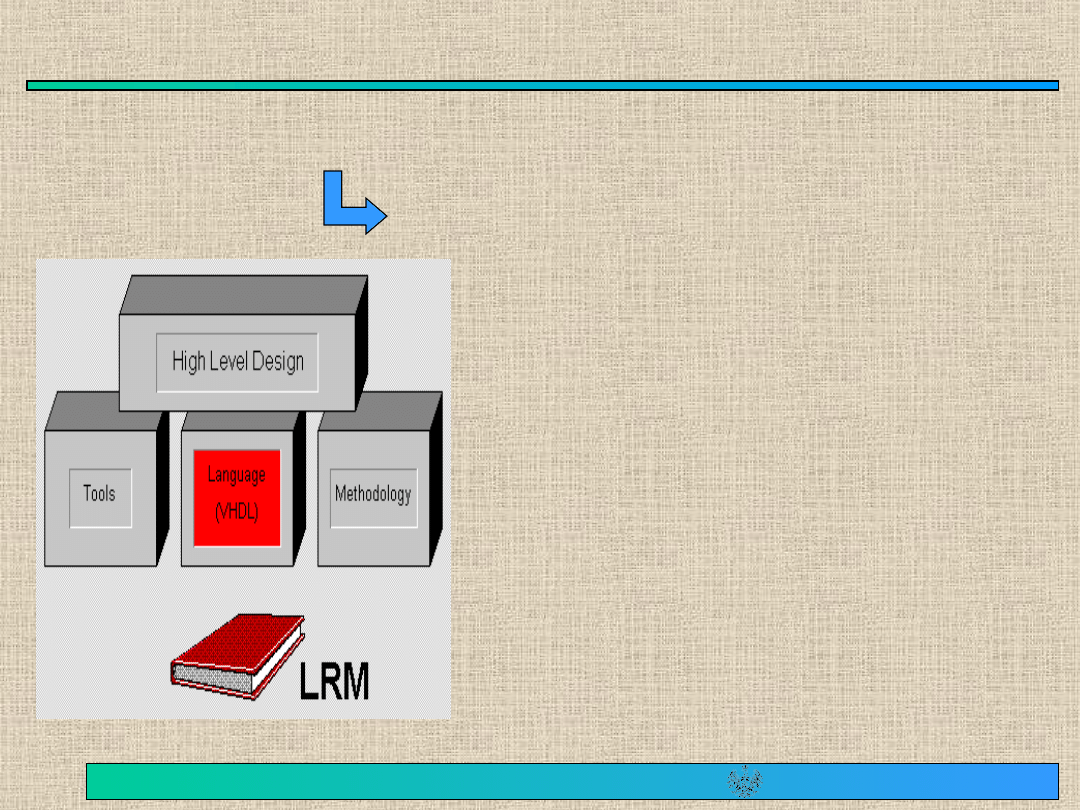

VHDL – co to jest?

Definicja

It is "a formal notation

intended for use in all

phases of the creation of

electronic systems. ... it

supports the development,

verification, synthesis, and

testing of hardware

designs, the

communication of

hardware design data ..."

[IEEE Standard VHDL Language

Reference Manual]

VHDL

-

V

HSIC

H

ardware

D

escription

L

anguage

V

ery

H

igh

S

peed

I

ntegrated

C

ircuit

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

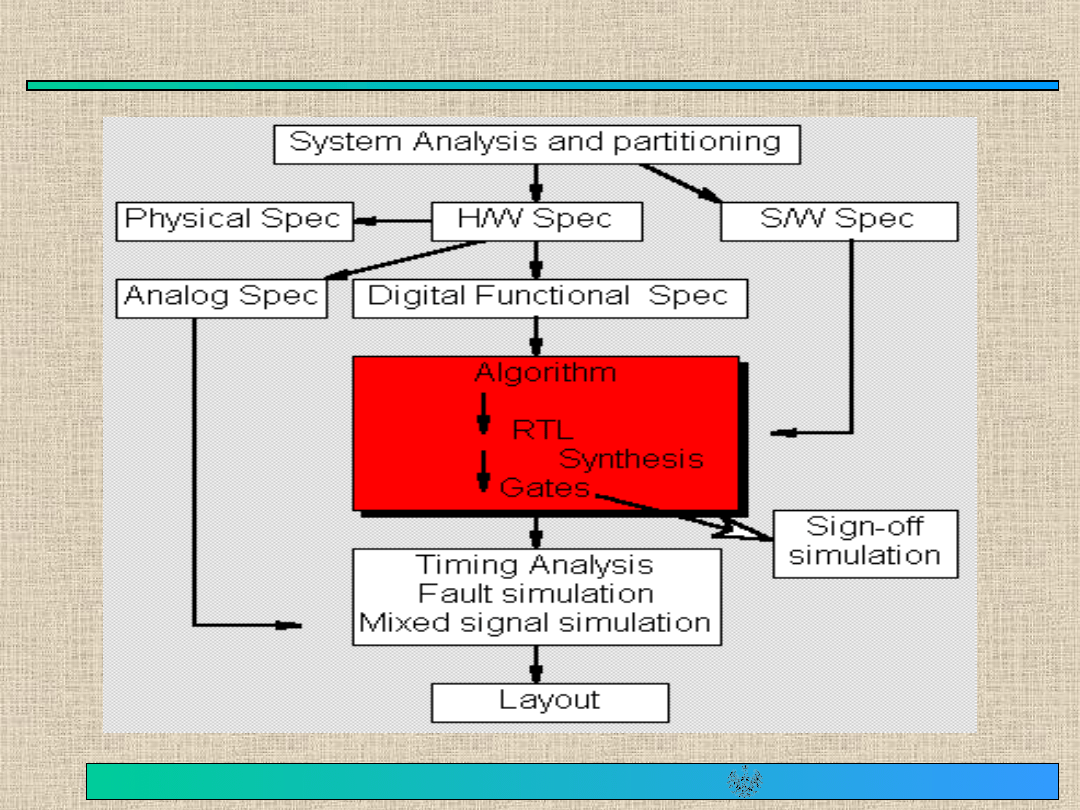

VHDL – jak? Zakres

stosowania

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

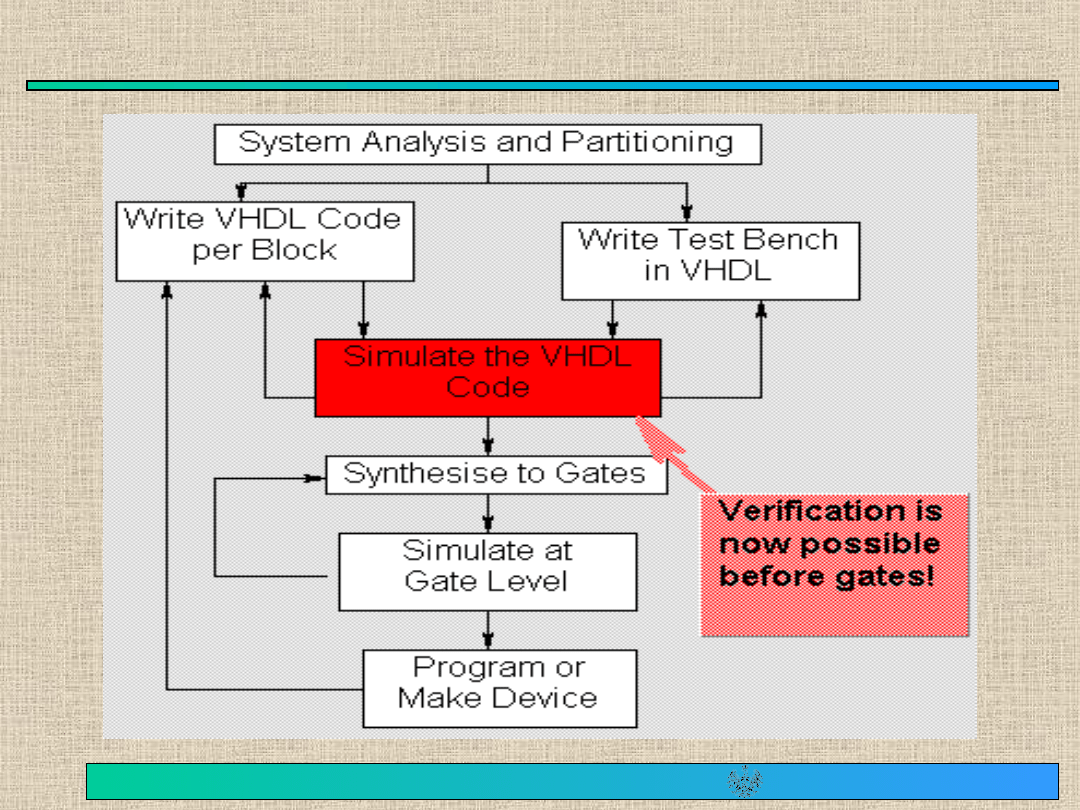

VHDL – jak? Proces

projektowania

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL – i co z tego?

Zalety

• Specyfikacja projektu niezależna od technologii

• możliwość współpracy z wieloma

producentami

• uniknięcie problemów z wycofywanymi

technologiami

• łatwe ulepszenie i poprawy

• Automatyzacja projektowania niskiego poziomu

• krótszy czas projektowania

• redukcja kosztów

• eliminacja błędów niskiego poziomu

• Poprawa jakości projektu

• łatwe sprawdzanie opcjonalnych technologii

• weryfikacja działania na wysokim poziomie

• łatwa weryfikacja implementacji

• modularność projektu – łatwa wymiana do

innych celów

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL - wczoraj

1980 DoD USA – początek programu rozwijania

technologii

układów VHSIC (Very High Speed Integrated

Circuits)

1981 Woods Hole, Massachusetts - konferencja na

temat założeń

przyszłego standardu HDL

1983 DoD ustala założenia VHDL: VHSIC Hardware

Description

Language – kontrakt otrzymują : Intermetrics, TI

i IBM

1984 gotowa wersja 6.0

1985 zwolnienie z restrykcji ITAR (US Interntional

Traffic and Arm

Regulation), VHDL 7.2 wraz z referencjami

przekazany do

IEEE celem standaryzacji i dalszego rozwoju

1987 wydany opis IEEE Std 1076

1993 wydana nowelizacja IEEE Std 1076-1993

2000 wydana errata IEEE Std 1076a-1993

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

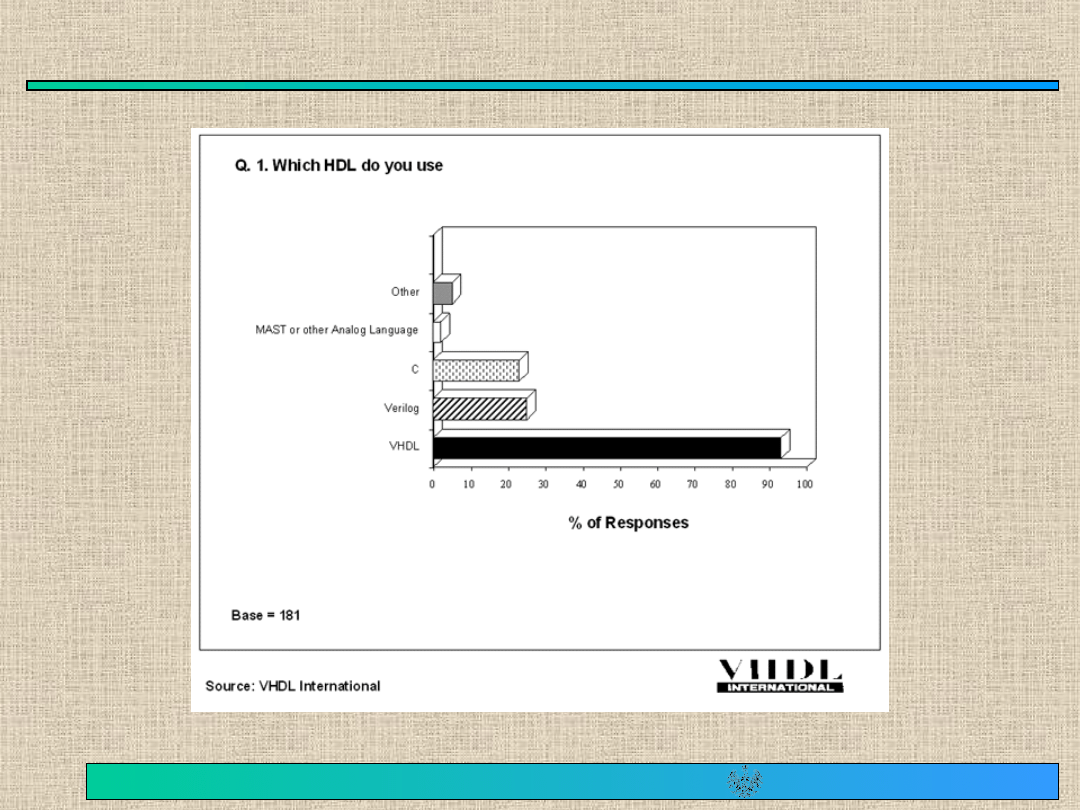

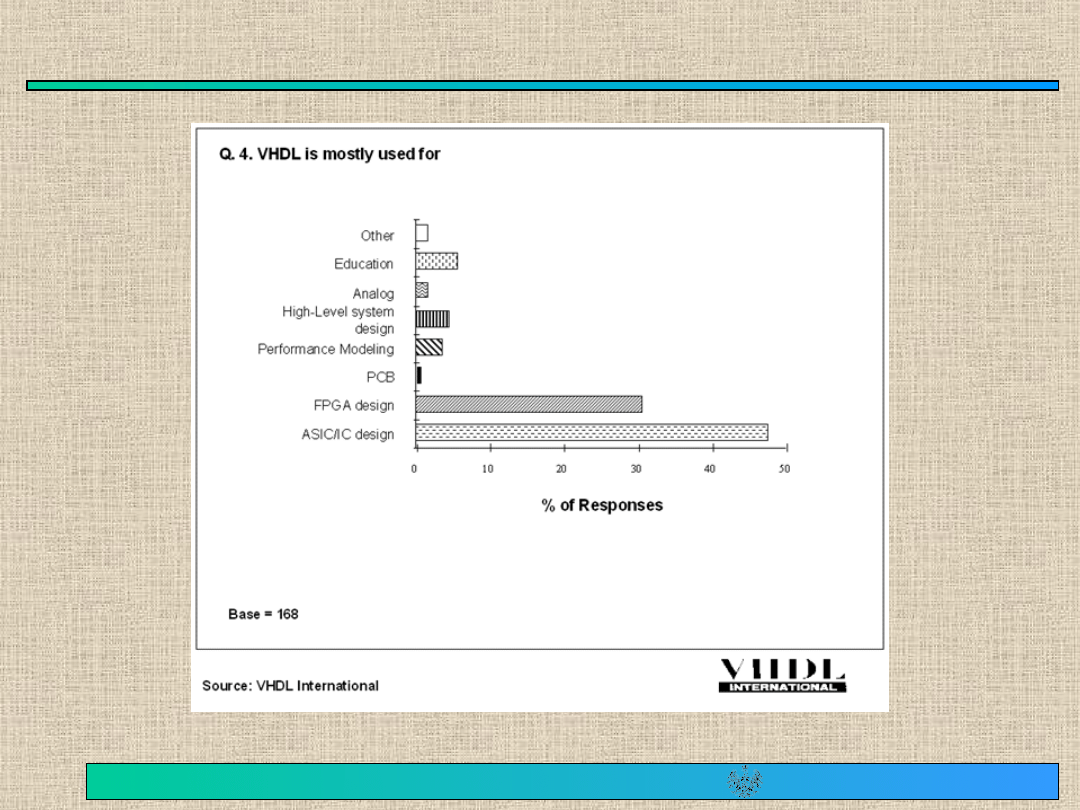

VHDL - dziś

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

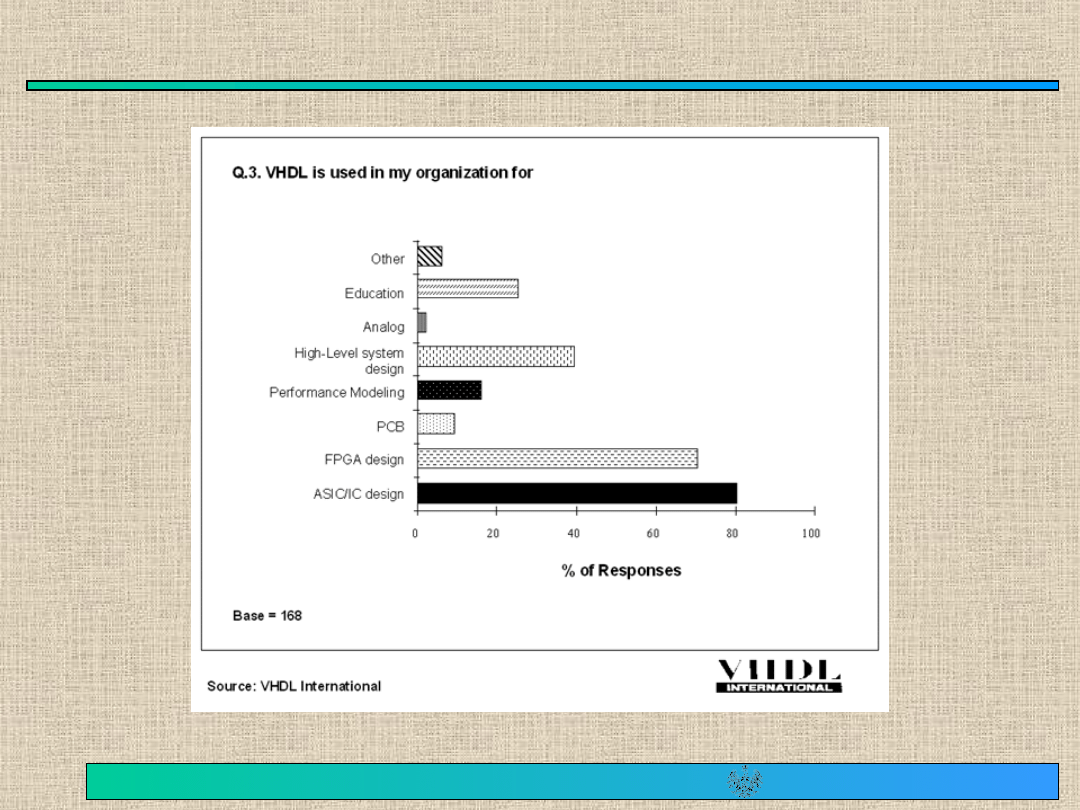

VHDL - dziś

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

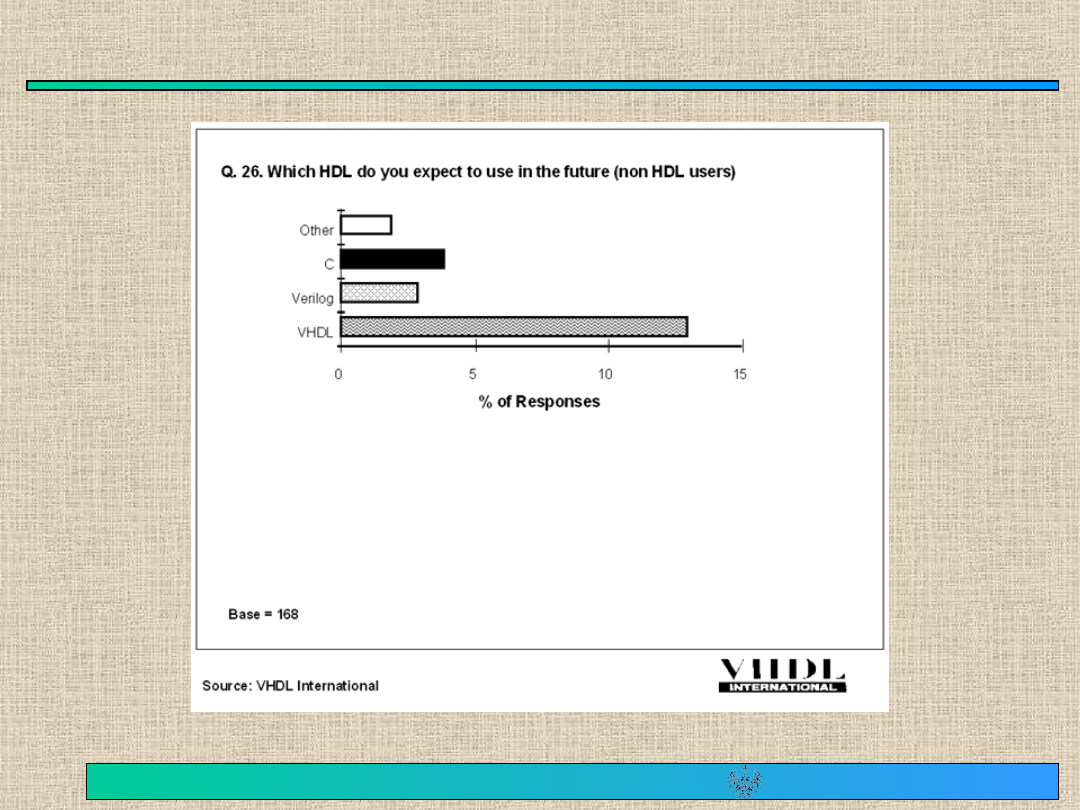

VHDL - dziś

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL - jutro

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL - standardy

• IEEE Std 1029.1-1998, IEEE Standard for VHDL Waveform and Vector Exchange

(WAVES)

to Support Design and Test Verification

• IEEE Std 1076-1993, IEEE Standard VHDL Language Reference Manual

• IEEE Std 1076a-2000, Amendment to IEEE Std 1076-1993

• IEEE Std 1076/INT-1991, IEEE Standards Interpretations: IEEE Std 1076-1987 IEEE

Standard VHDL

Language Reference Manual

• IEEE Std 1076.1-1999, IEEE Standard VHDL Analog and Mixed-Signal Extensions

• IEEE Std 1076.2-1996, IEEE Standard VHDL Mathematical Packages

• IEEE Std 1076.3-1997, IEEE Standard VHDL Synthesis Packages

• IEEE Std 1076.4-1995, IEEE Standard for VITAL Application-Specific Integrated

Circuit (ASIC)

Modeling Specification

• Approved draft of IEEE Std 1076.6-1999, IEEE Standard for VHDL Register Transfer

Level Synthesis

• IEEE Std 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan

Architecture

• IEEE Std 1149.1b-1994, Supplement to IEEE Std 1149.1-1990, IEEE Standard Test

Access Port

and Boundary-Scan Architecture

• IEEE Std 1164-1993, IEEE Standard Multivalue Logic System for VHDL Model

Interoperability

(Std_logic_1164)

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL – literatura

„A Guide to VHDL”, S. Mazor, P. Langstraat

„VHDL Analysis and Modelling of Digital Systems”, Z.

Navabi

„VHDL Hardware Description and Design”,

R. Lipsett, C. Schaefer, C. Ussery

„The VHDL Cookbook”, P. J. Ashenden

„VHDL programming: with advanced topics”, L. Baker

„VHDL starter's guide”, S. Yalamanchili

„VHDL for designers”, S. Sjoholm, L. Lindh

„VHDL made easy!”, D. Pellerin, D. Taylor

„VHDL answers to frequently asked questions”, B. Cohen

„VHDL and AHDL digital systems implementation”, F. A.

Scarpino

„VHDL: język opisu i projektowania układów cyfrowych”,

W. Wrona

„Active-VHDL Series BOOK#2 – EVITA Interactive Tutorial”,

J. Mirkowski, M. Kapustka, Z. Skowroński, A.

Biniszkiewicz

„VHDL: a logic synthesis approach”, D. Naylor, S. Jones

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL – źródła

• VHDL International:

http://www.vhdl.org/vhdl_intl/

• VHDL International Users' Forum (VIUF) internet service

machine:

http://vhdl.org/

• The Hamburg VHDL archive:

http://tech-www.informatik.uni-

hamburg.de/vhdl/vhdl.html

• Doulos High Level Design Web site:

http://www.doulos.co.uk/

• RASSP WWW site:

http://rassp.scra.org/

• University of Strasbourg:

http://erm1.u-strasbg.fr/db/ or ftp://erm1.u-strasbg.fr/

• ESA (European Space Agency):

http://www.estec.esa.nl/wsmwww/vhdl/vhdlpage.html

• Programmable Logic Jump Station:

http://www.optimagic.com/

• VHDL-online, University of Erlangen-Nürnberg:

http://www.vhdl-online.de/

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL – firmy (produkty)

• Accolade Design Automation, (PeakFPGA)

• Aldec, (Active-HDL)

• Cadence Design Systems

• Cypress Semiconductor (Warp)

• Data I/O Corporation (Synario)

• Green Mountain Computing Systems,

(VHDL Studio)

• Model Technology, (V-System)

• Exemplar (LeonardoSpectrum)

• Synplicity (SynplifyPro)

• Model Technology (ModelSim)

• Synopsys (FPGA Compiler, FPGA Express)

• InnovEDA, (dawniej: Viewlogic Systems)

• Xilinx, (ISE – Minc+Synario)

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

VHDL – przykład: licznik

entity

Counter

is

port

( CLK:

in

STD_LOGIC;

RESET:

in

STD_LOGIC;

Q:

out

STD_LOGIC_VECTOR (3

downto

0) );

end

Counter;

architecture

Counter_Arch

of

Counter

is

begin

process

(CLK, RESET)

variable

Qint: STD_LOGIC_VECTOR (3

downto

0);

begin

if

RESET='1'

then

Qint := "0000";

elsif

CLK'event

and

CLK='1'

then

if

Qint<9

then

Qint:=Qint+1;

else

Qint:="0000";

end if

;

end if

;

Q <= Qint;

end process

;

end

Counter_Arch ;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Deklaracje entity i architecture

-- deklaracja entity definiuje komponent

-- i jego połączenie ze światem zewnętrznym

entity

ENTITY_NAME

is

port

(

< PORT_NAME: <mode> <type_spec>; >

);

end

ENTITY_NAME;

-- deklaracja architecture definiuje sposób

działania

-- komponentu, do którego się odwołuje

architecture

ARCH_NAME

of

ENTITY_NAME

is

begin

<statements>

end

ARCH_NAME;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

entity

xyz

architecture

beh

of

xyz

(behavioral)

architecture

str

of

xyz

(structural)

architecture

dat

of

xyz

(dataflow)

-- Przykład komparator

entity

COMPARE

is

port

(A,B:

in

bit;

C:

out

bit);

end

COMPARE;

Deklaracje entity i architecture

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

-- deklaracja architecture (behavioral style)

architecture

arch_behavioral

of

COMPARE

is

begin

-- współbieżne operatory przypisań

process

(A,B)

-- A,B - zmienne “aktywne” w

process

begin

-- sekwencyjne operatory przypisań

if

(A=B)

then

C <=‘1’

after

1 ns;

else

C <=‘0’

after

1 ns;

end

if

;

end process

;

end

arch_behavioral;

Deklaracja architecture – behavioral

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

-- deklaracja architecture (dataflow

style)

architecture

arch_dataflow

of

COMPARE

is

begin

C <=

not

(A

xor

B)

after

1 ns;

end

arch_dataflow

Deklaracja architecture – dataflow

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

-- deklaracja architecture (structural style)

architecture

arch_structural

of

COMPARE

is

signal

I: bit;

component

XOR2

port

(x,y:

in

bit; z:

out

bit);

end component

;

component

INV

port

(x:

in

bit; z:

out

bit);

end component

;

begin

U0: XOR2

port map

(A,B,I);

U1: INV

port map

(I,C);

end

arch_structural;

Deklaracja architecture – structural

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

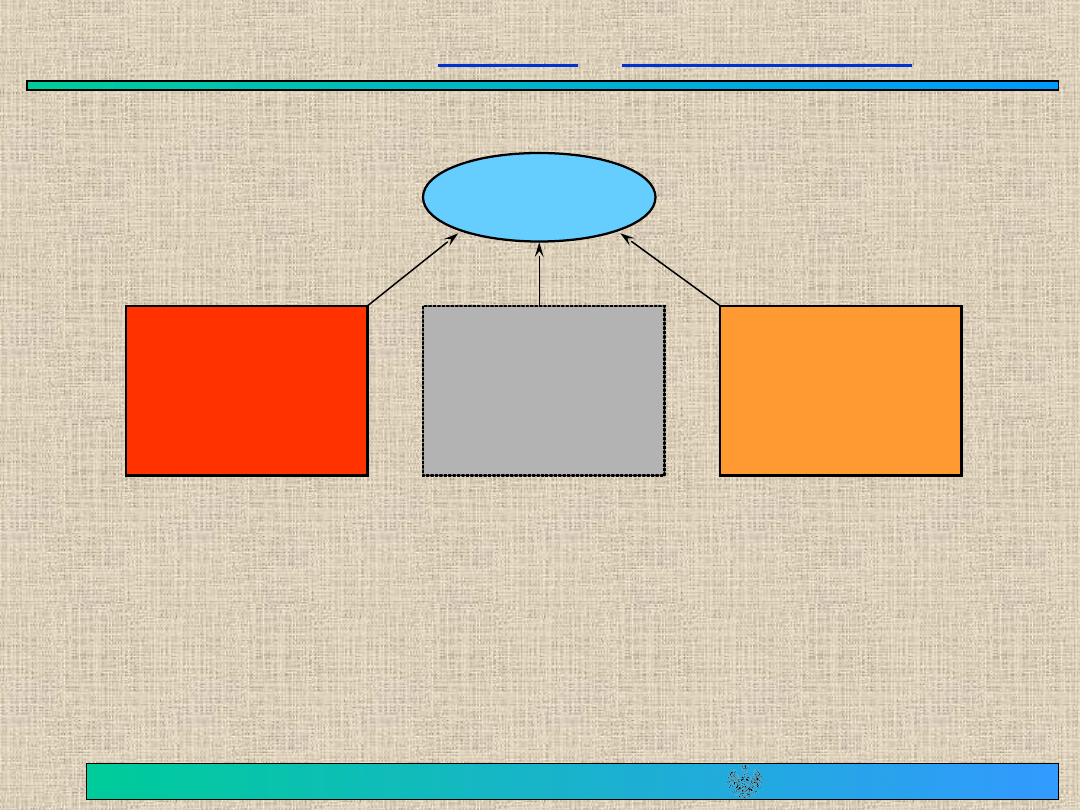

VHDL – jednostki projektowe

kompilator

VHDL

Jednostki

projektowe

Biblioteki

entity

architecture

configuration

package

entity

architecture

configuration

package

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

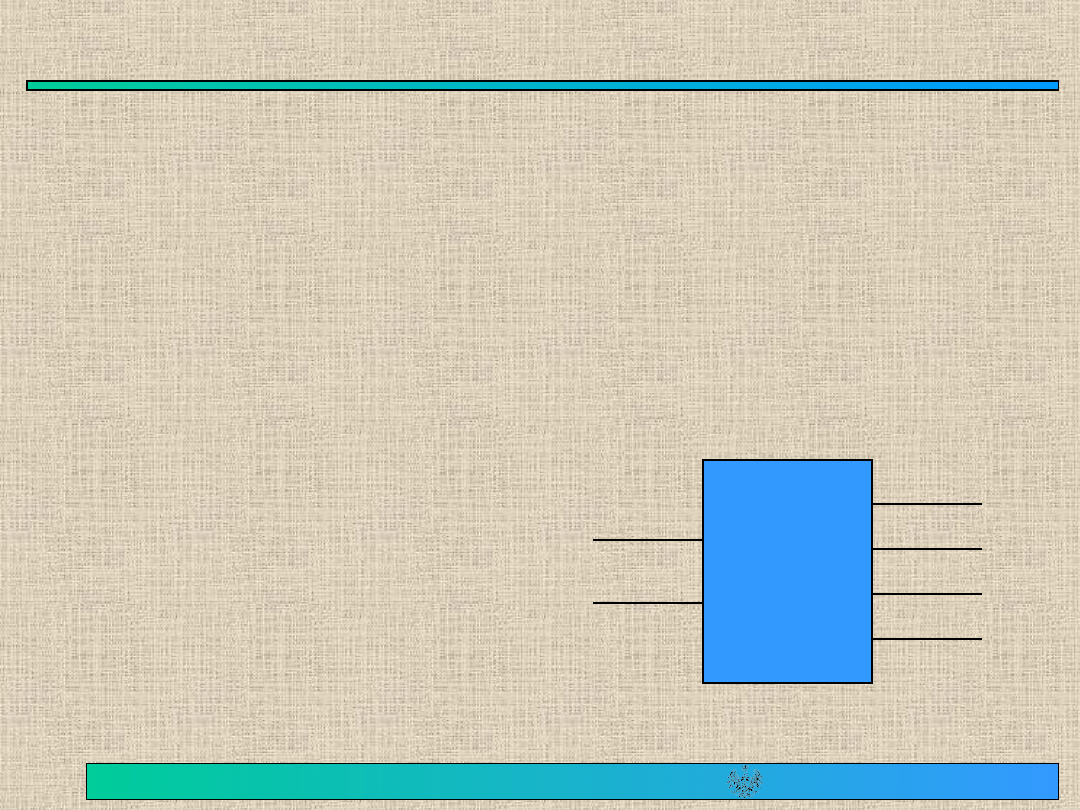

PRZYKŁAD – zespół czterech

komparatorów

entity

COMPARE

is

port

(A,B:

EQL: );

end

COMPARE;

architecture

MY_FIRST

of

COMPARE

is

begin

end

MY_FIRST;

A 4bity

B 4bity

EQL(0)

EQL(1)

EQL(3)

EQL(2)

COMPARE

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

entity

COMPARE

is

port

(A,B:

in

bit_vector (3

downto

0);

EQL:

out

bit_vector (3

downto

0) );

end

COMPARE;

architecture

MY_FIRST

of

COMPARE

is

begin

EQL <=

not

(A

xor

B);

end

MY_FIRST;

A 4bity

B 4bity

EQL(0)

EQL(1)

EQL(3)

EQL(2)

COMPARE

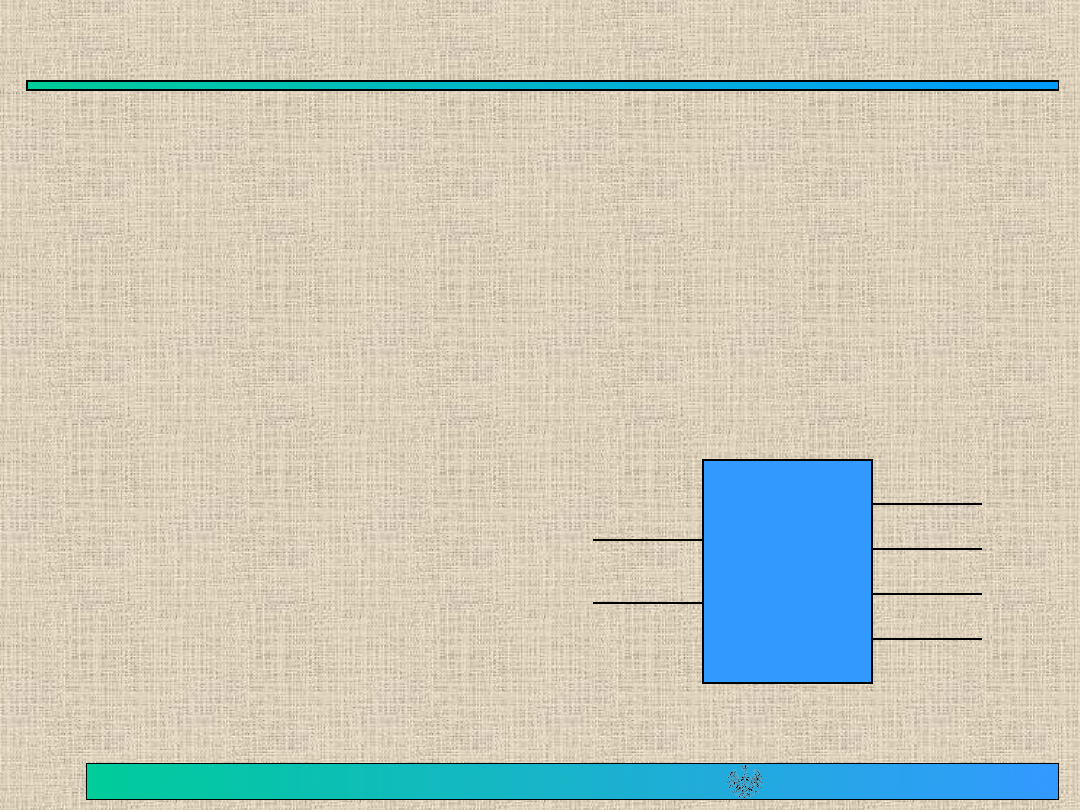

PRZYKŁAD – zespół czterech

komparatorów

entity

BCD_DECODER

is

port

(D:

NINE,EIGHT,ONE,ZERO: );

end

BCD_DECODER;

architecture

MY_FIRST

of

BCD_DECODER

is

begin

end

MY_FIRST;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

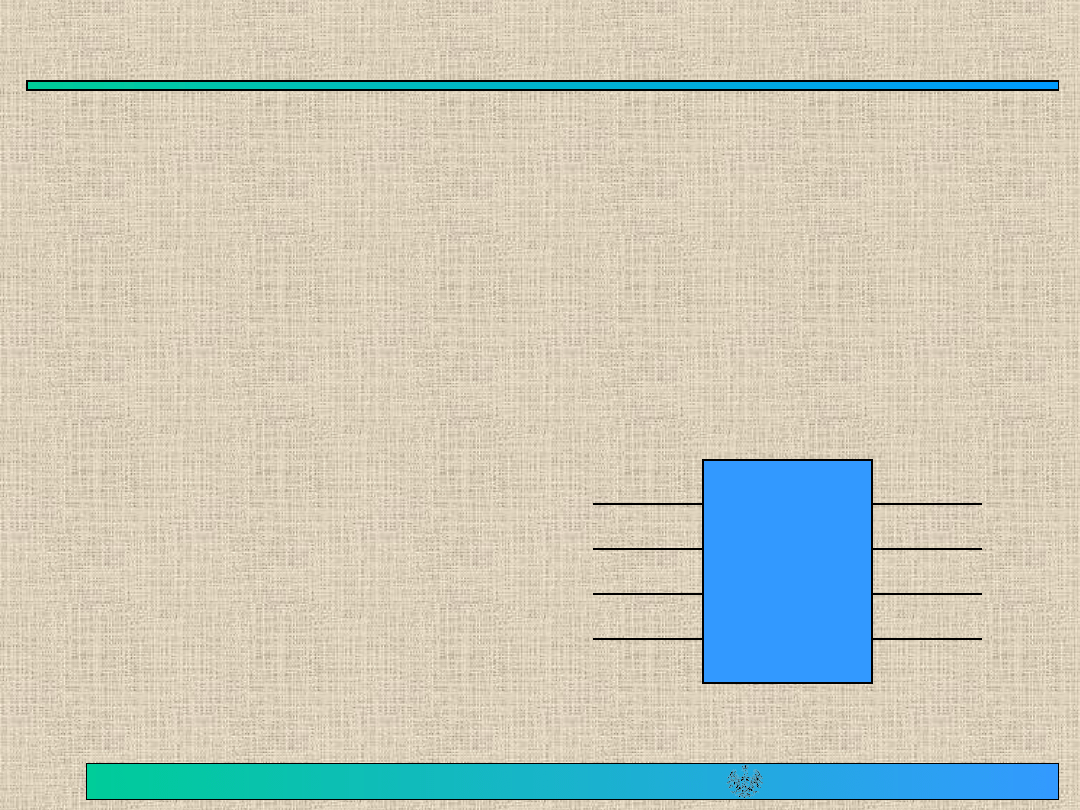

DECODER

NINE

EIGHT

ZERO

ONE

D(3)

D(2)

D(0)

D(1)

PRZYKŁAD – dekoder kodu BCD

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

PRZYKŁAD – dekoder kodu BCD

entity

BCD_DECODER

is

port

(D:

in

bit_vector (3

downto

0);

NINE,EIGHT,ONE,ZERO:

out

boolean);

end

BCD_DECODER;

architecture

MY_FIRST

of

BCD_DECODER

is

begin

NINE <= (D=“1001”);

EIGHT <= (D=“1000”);

ONE <= (D=“0001”);

ZERO <= (D=“0000”);

end

MY_FIRST;

DECODER

NINE

EIGHT

ZERO

ONE

D(3)

D(2)

D(0)

D(1)

Ciąg dalszy

nastąpi...

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

Wyszukiwarka

Podobne podstrony:

J zyki Opisu Sprz tu 4 dzienne

J zyki Opisu Sprz tu 5 dzienne

Po katastrofie nawiązano połączenie z telefonem w Tu 154 Nasz Dziennik

Telefon ofiary katastrofy Tu 154 był aktywny po tragedii Nasz Dziennik

Dzienniki mowy

SP dzienni w2

Wyklad1 bilans BK dzienne zaoczne cr (1)

RIWKS dzienne W 1

Gatunki dziennikarskie

Wykład XI Metody opisu układów cyfrowych

SP dzienni w1

IK dzienne 1

Gatunki dziennikarskie licencjat PAT czesc 2

RIWKS dzienne W 11

RIWKS dzienne W 2

RIWKS dzienne W 6

więcej podobnych podstron