Języki Opisu Sprzętu

Wykład 4

III rok kierunek Elektronika

J.Kasperek P.J.Rajda

• VHDL – jednostki projektowe

• VHDL – pojęcia leksykalne

• VHDL – instrukcje sekwencyjne

• VHDL – instrukcje współbieżne

Program wykładu

Kontakt z prowadzącymi:

C-3 p.502 tel. (617)3980

mgr inż. Jerzy Kasperek kasperek@uci.agh.edu.pl

mgr inż. Paweł J.Rajda pjrajda@uci.agh.edu.pl

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

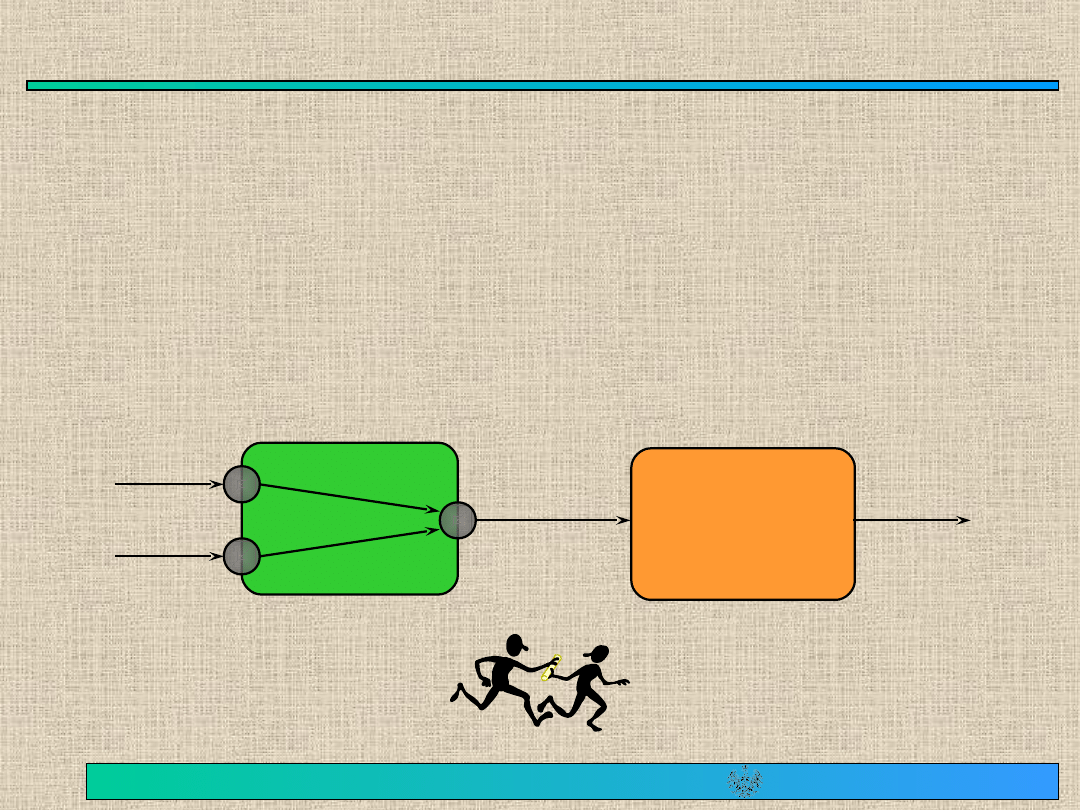

VHDL – jednostki projektowe

kompilator

VHDL

Jednostki

projektowe

Biblioteki

entity

architecture

configuration

package

entity

architecture

configuration

package

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Jednostki projektowe: entity i architecture

-- deklaracja entity definiuje komponent

-- i jego połączenie ze światem zewnętrznym

entity

ENTITY_NAME

is

port

(

< PORT_NAME: <mode> <type_spec>; >

);

end

ENTITY_NAME;

-- deklaracja architecture definiuje sposób

działania

-- komponentu, do którego się odwołuje

architecture

ARCH_NAME

of

ENTITY_NAME

is

begin

<statements>

end

ARCH_NAME;

Deklaracja

configuration

• pozwala na wybranie jednej z architektur dla danej

entity

.

• stanowi wygodny sposób dokumentowania wersji

projektu.

• likwiduje konieczność rekompilacji całego projektu gdy

wymagana jest

zmiana tylko kilku komponentów.

configuration

MY

of

ALGORITHM

is

for

STRUCT

for

U0:COMPARE

use

entity

WORK.COMPARE(arch_dataflow);

end for

;

end for

;

end

MY;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Jednostki projektowe: configuration

nazwa

konfiguracji

konfigurowana

entity

konfigurowana

architektura

wybrana

architektura

nazwa

biblioteki

konfigurowany

komponent

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Deklaracja

package

Grupuje używane wspólnie deklaracje stałych,

podprogramów

czy typów zmiennych.

package

my_constans

is

constant

unit_delay: time := 1ns;

end

my_constans;

...

after

work.my_constans.unit_delay;

package

STANDARD

W każdym pakiecie VHDL - definiuje m.in. typy danych,

jak :

bit, boolean, bit_vector itp.

Jednostki projektowe: package

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Pojęcia leksykalne

• literały

napisy reprezentujące dane; ze sposobu ich

zapisu

wynikają ich wszystkie właściwości, w tym ich

wartości

• identyfikatory (nazwy)

ciągi liter i cyfr, rozpoczynające się od litery

• obiekty

stałe, zmienne, sygnały

• wyrażenia

wzory ujmujące operatory i argumenty,

określające sposób

obliczenia lub określenia

wartości

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Literały pojedyncze (skalary)

character

- pojedynczy znak objęty apostrofami, np:

‘A’

lub

‘a’

bit

- reprezentuje wartość binarną

‘1’

lub

‘0’

std_logic

- reprezentuje wartość sygnałów wg. IEEE

1164:

U

niezainicjalizowany

X

nieznany (forcing an unknown)

0

silne zero (forcing 0)

1

silne jeden (forcing 1)

Z

wysoka impedancja

W

słaby nieznany (weak unknown)

L

słabe zero (weak 0)

H

słabe jeden (weak 1)

-

nieistotny (don’t care)

Pojęcia leksykalne - literały

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Pojęcia leksykalne - literały

boolean

- reprezentuje dwie dyskretne wartości:

true

TRUE

True

false FALSE False

real

- reprezentuje wartość zmiennoprzecinkową, np:

1.3

lub

-344.0E+23

, typowo od

-1.0E+38

do

1.0E+38

z precyzją co najmniej sześciu cyfr po przecinku

integer

- reprezentuje wartość całkowitą, n.p.:

+1

,

862

lub

-257

,

+123_456

,

16#00FF#

, typowo od

-2,147,483,647

do

+ 2,147,483,647

time

- reprezentuję jedyną zdefiniowaną wielkość fizyczną,

to jest czas:

62

fs

, (

ps

,

ns

,

us

,

ms

,

sec

,

min

,

hr

)

Literały wielokrotne (tablice)

string

- ciąg znaków objęty cudzysłowami, n.p.:

“x”

,

“hold time”

bit_vector

-

”0001_1100”

,

x”00FF”

std_logic_vector

-

”101Z”

,

”UUUUUU”

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Literały dziesiętne:

Literały typu based:

14

16#FE#

-- 254

7755

2#1111_1110#

-- 254

156E7

8#376#

-- 254

188.993

16#D#E1

-- 208

88_670_551.453_909

16#F.01#E+2

-- 3841.00

44.99E-22

2#10.1111_0001#E9

-- 1506.00

Literały wielkości fizycznych:

60 sec

100 m

5 kohm

177 A

b"11111110"

- reprezentacja binarna

B"1111_1110"

- równoważna reprezentacja binarna

x"FE"

- równoważna reprezentacja szesnastkowa

O"376"

- równoważna reprezentacja ósemkowa

Pojęcia leksykalne - literały

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Identyfikatory

Muszą zaczynać się od litery. Potem mogą następować

litery, cyfry lub

podkreślnik (underscore _ ):

XYZ

,

S(3)

,

S(1 to 4)

,

X3

,

my_defs

.

VHDL nie rozróżnia wielkości (not case sensitive):

XyZ

<=>

xyz

.

Identyfikatory nie mogą być takie jak słowa kluczowe

(około 100).

Deklaracje

Deklaracje obiektów (ich nazwy i typu) są to deklaracje

stałych, zmiennych, sygnałów lub plików.

Zakres sygnałów i zmiennych można ograniczać:

range

{low_val

to

high_val | high_val

downto

low_val}

np:

integer

range

1

to

10

;

real

range

1.0

to

10.0

;

Pojęcia leksykalne – identyfikatory,

deklaracje

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Deklaracje stałych

• skalarnych:

constant

name: type := expression;

• tablicowych:

constant

name: array_type [(index)] := expression;

np:

constant

Vcc: real :=

5.0

;

constant

Cycle: time :=

50

ns;

constant

five: bit_vector :=

“0101”

;

constant

SIX: std_logic_vector (8

to

11):=

“0110”

;

Deklaracje sygnałów

• skalarnych:

signal

name(s): type[range][:=

expression];

• tablicowych:

signal

name(s): array_type [(index)][:=

expression];

• entity:

port

(name(s): direction type [range][:=

expression]);

Pojęcia leksykalne – deklaracje

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Deklaracje zmiennych (w zakresie procesu)

• skalarnych:

variable

name(s): type[(range)][:= expression];

• tablicowych:

variable

name(s): array_type [(range)][:=

expression];

np:

variable

Index: integer

range

1

to

50;

variable

Cycle: time

range

10 ns

to

50 ns :=

10ns;

variable

MEMORY: bit_vector (0

to

7);

variable

x,y: integer;

Pojęcia leksykalne – deklaracje

W VHDL’92 wprowadzono zmienne

globalne do komunikacji pomiędzy

procesami.

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

W języku VHDL argumenty wyrażeń muszą być tego samego typu

Konwersje typów:

integer (

3.0

)

integer

real (

3

)

real

integer * time

time

nanos + picos

time

nanos / picos

integer

variable

My_Data, My_Sample: integer;

...

My_Data := integer(

74.94

* real(My_Sample ));

Pojęcia leksykalne – wyrażenia

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Operatory wyrażeń:

logiczne

and

or

nand

nor

xor

not

relacji

=

/=

<

<=

>

>=

połączenia &

arytmetyczne

+

-

*

/

**

mod

rem

abs

VHDL’92

sll

srl

sla

sra

rol

ror

xnor

Typy argumentów:

takie same :

and or nand nor xor not

= /= < <= > >= + - * /

integer

:

mod rem

integer exp : **

numeryczny :

abs

Pojęcia leksykalne – wyrażenia

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

•

process

• instrukcje

przypisania

•

wait

•

if

•

case

•

loop

•

next

•

exit

•

assert

• podprogramy

Instrukcje sekwencyjne

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

[etykieta:]

process

[(lista zmiennych aktywujących)]

[podprogram]

[typ]

[stała]

[zmienna]

[inne deklaracje]

begin

instrukcje sekwencyjne

end process

[etykieta];

Instrukcja przypisania wartości dla zmiennych

zmienna := wyrażenie;

Instrukcja przypisania wartości dla sygnałów

sygnał <= wyrażenie [

after

delay];

Instrukcje sekwencyjne - process

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

• zawiera wyłącznie instrukcje sekwencyjne,

• definiuje część architektury, gdzie instrukcje

wykonywane są sekwencyjnie,

• musi zawierać albo listę sygnałów aktywujących albo

instrukcję WAIT,

• zapewnia możliwość “programowego” definiowania

działania,

• ma możliwość zmian sygnałów zdefiniowanych

w

archtecture

i / lub

entity

Instrukcje sekwencyjne - process

sygnał

sygnał

Proces M

czekaj na

zmianę

sygnału

wejściowego

sygnał

Sygnał

Proces N

zmienna

zmienna

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

W ciele instrukcji

process

może wystąpić

instrukcja

wait

.

Składnia:

wait

[

on

sygnały]

[

until

warunek]

[

for

wyrażenie_czas]

Przykłady:

wait on

a,b;

wait until

x > 10;

wait for

10 ns;

wait

;

-- waits forever

Poniższe zapisy są równoważne:

wait on

a,b; <=>

process

(a,b);

Instrukcje sekwencyjne - wait

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

if

warunek

then

instrukcje_sekwencyjne;

[

elsif

warunek

then

instrukcje_sekwencyjne] ;

[

else

instrukcje_sekwencyjne];

end if

;

Przykład:

process

(CLK,R,DATAB)

begin

if

(R = '0')

then

operand2(9

downto

0) <=

"0000000000";

elsif

(CLK = '1'

and

CLK'event)

then

operand2(9

downto

0) <= DATAB;

end if

;

end process

;

Instrukcje sekwencyjne - if

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Szczególnie wygodna do dekodowania kodów lub

stanu magistral.

Składnia:

case

wyrażenie

is

when

val

=>

instrukcje_sekwencyjne;

[

when

val1 | val2 =>

instrukcje_sekwencyjne;]

[

when

val2

to

val3

=>

instrukcje_sekwencyjne;]

[

when others

=>

instrukcje_sekwencyjne;]

end case

;

Przykład:

case

bit_index

is

when

‘0’ => ix := 0;

when

‘1’ => ix := 1;

end case

;

Instrukcje sekwencyjne - case

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

[etykieta:]

[

while

warunek |

for

index

in

valA

to

valZ]

loop

instrukcje sekwencyjne;

end loop

;

Przykłady:

L:

for

i

in

1

to

10

loop

instrukcje sekwencyjne;

end loop

;

M:

while

(i<11)

loop

instrukcje sekwencyjne;

i := i + 1;

end loop

;

Instrukcje sekwencyjne - loop

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

next

[etykieta] [

when

warunek];

Przykłady:

for

i

in

0

to

max_limit

loop

if

(a(i) = 0)

then next

;

end if

;

g(i) := a(i);

end loop

;

L1:

while

i < 5

loop

L2:

while

j < 5

loop

...

next

L2

when

i=j;

...

end loop

L2;

end loop

L1;

Instrukcje sekwencyjne - next

Natychmiast

owe

przejście do

kolejnej

iteracji

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

exit

[etykieta] [

when

warunek];

Przykład:

for

i

in

0

to

max_limit

loop

if

(a(i) = 0)

then exit

;

end if

;

g(i) := a(i);

end loop

;

...

Instrukcje sekwencyjne - exit

Natychmiast

owe

opuszczenie

pętli

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Drukuje komunikat podczas symulacji.

Składnia:

assert

warunek [

report

string] [

severity

level];

level: FAILURE | ERROR | WARNING | NOTE

Przykład:

assert

(Machine_Code = ”0000”)

report

“Illegal Opcode”

severity

FAILURE;

W VHDL’92 umożliwiono używanie

report

bez

assert

.

Instrukcje sekwencyjne - assert

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Funkcje zwracają jedną wartość.

Składnia:

function

nazwa [parametry]

return

typ

is

deklaracje

begin

instrukcje sekwencyjne;

end

[nazwa ]

Przykład:

function

INCREMENT (COUNT: INTEGER)

return

INTEGER

is

variable

TEMP: INTEGER;

begin

if

COUNT >= 255

then

TEMP := 0;

else

TEMP := COUNT + 1;

end if

;

return

TEMP;

end

;

Instrukcje sekwencyjne - function

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Procedury mogą zwracać więcej niż jedną wartość.

Składnia:

procedure

nazwa [parametry]

is

deklaracje

begin

instrukcje sekwencyjne;

end

[nazwa ]

parametry

{[

variable

] nazwy [

in

|

out

|

inout

] typ [:=wyrażenie];

|

|

signal

nazwy [

in

|

out

|

inout

] typ;}

Przekazanie parametrów do procedury :

in inout

Przekazanie parametrów z procedury :

out inout

Instrukcje sekwencyjne - procedure

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Przykład:

procedure

vect_to_int (z:

in

bit_vector (1

to

8);

zero_flag:

out

boolean;

q:

inout

integer)

is

begin

q:=0;

zero_flag:=

true

;

for

i

in

1

to

8

loop

q := q * 2;

if

(z(i) = ‘1’)

then

q:=q +1;

zero_flag :=

false

;

end if

;

end loop

;

return

;

end

vect_to_int;

Wywołanie: vect_to_int (s,t,u);

Instrukcje sekwencyjne - procedure

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

• przypisania wartości

sygnałom

• współbieżne

(cuncurent)

• warunkowe

(conditonal)

• decyzyjne (selected)

• podprogramy

•

block

Instrukcje współbieżne

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Współbieżne przypisanie wartości

sygnałom

W obydwu poniższych przykładach skutek

jest ten sam:

architecture

example_1

of

EXAMPLE

is

begin

OUTPUT <= A (INDEX);

end

example_1 ;

architecture

example_2

of

EXAMPLE

is

begin

process

(A,INDEX)

begin

OUTPUT <= A (INDEX);

end process

;

end

example_2;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

sygnał <= {wyrażenie

when

warunek

else

} wyrażenie;

Przykład:

Z <= A

when

(x > 3)

else

B

when

(x < 3)

else

C;

Analogiczne do sekwencyjnej instrukcji

if

, ale:

• wykonują się bez uwzględnienia kolejności,

• używane w opisach typu dataflow i structural,

• syntezują się do logiki kombinacyjnej.

Uwaga! Nie można przypisana jak wyżej użyć wewnątrz

process

.

Współbieżne przypisanie warunkowe

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Składnia:

with

wyrażenie

select

sygnał <= {wyrażenie

when

wartości,};

Przykład:

with

digit

select

out <= ‘1’

when

0 | 1 | 8 | 9,

‘0’

when

2 to 7,

‘Z’

when

others

;

Analogiczne do sekwencyjnej instrukcji

case

.

Uwaga! Nie można przypisana jak wyżej użyć wewnątrz

process

.

Współbieżne przypisanie decyzyjne

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Współbieżne wywołanie podprogramu

W obydwu poniższych przykładach skutek jest ten

sam:

architecture

example_3

of

EXAMPLE

is

begin

vector_to_int (bitstuff, flag, number);

end

example_3;

architecture

example_4

of

EXAMPLE

is

begin

process

begin

vector_to_int (bitstuff, flag, number);

wait on

bitstuff, number;

end process

;

end

example_4;

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Instrukcje współbieżne - block

Grupuje instrukcje współbieżne.

Bloki można zagnieżdżać, tworząc hierarchię.

Składnia:

[etykieta:]

block

[(wyrażenie_typu_boolean)];

[deklaracje]

begin

instrukcje współbieżne;

end block

[etykieta];

deklaracje:

• stałych,typów,sygnałów

• podprogramów

• klauzula

use

• komponentów

J.Kasperek P.J.Rajda © 2001 Katedra Elektroniki AGH

Kraków

Języki Opisu Sprzętu

Instrukcje współbieżne – block (guarded)

Wyrażenie_typu_boolean automatycznie generuje sygnał

guard, który może warunkować przypisania wartości

sygnałom przez klauzulę

guarded

.

Przykład:

B1:

block

(control)

begin

s <=

guarded

‘1’;

end block

B1;

Przypisanie s <= ‘1’ zajdzie, jeżeli control jest równe true.

Uwaga !!! Nie wszystkie narzędzia dopuszczają korzystanie

z tej opcji.

Ciąg dalszy

nastąpi...

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

Wyszukiwarka

Podobne podstrony:

J zyki Opisu Sprz tu 5 dzienne

J zyki Opisu Sprz tu 3 dzienne

Po katastrofie nawiązano połączenie z telefonem w Tu 154 Nasz Dziennik

Telefon ofiary katastrofy Tu 154 był aktywny po tragedii Nasz Dziennik

Dzienniki mowy

SP dzienni w2

Wyklad1 bilans BK dzienne zaoczne cr (1)

RIWKS dzienne W 1

Gatunki dziennikarskie

Wykład XI Metody opisu układów cyfrowych

SP dzienni w1

IK dzienne 1

Gatunki dziennikarskie licencjat PAT czesc 2

RIWKS dzienne W 11

RIWKS dzienne W 2

RIWKS dzienne W 6

więcej podobnych podstron