Charakterystyka systemów cyfrowych

Charakterystyka systemów cyfrowych

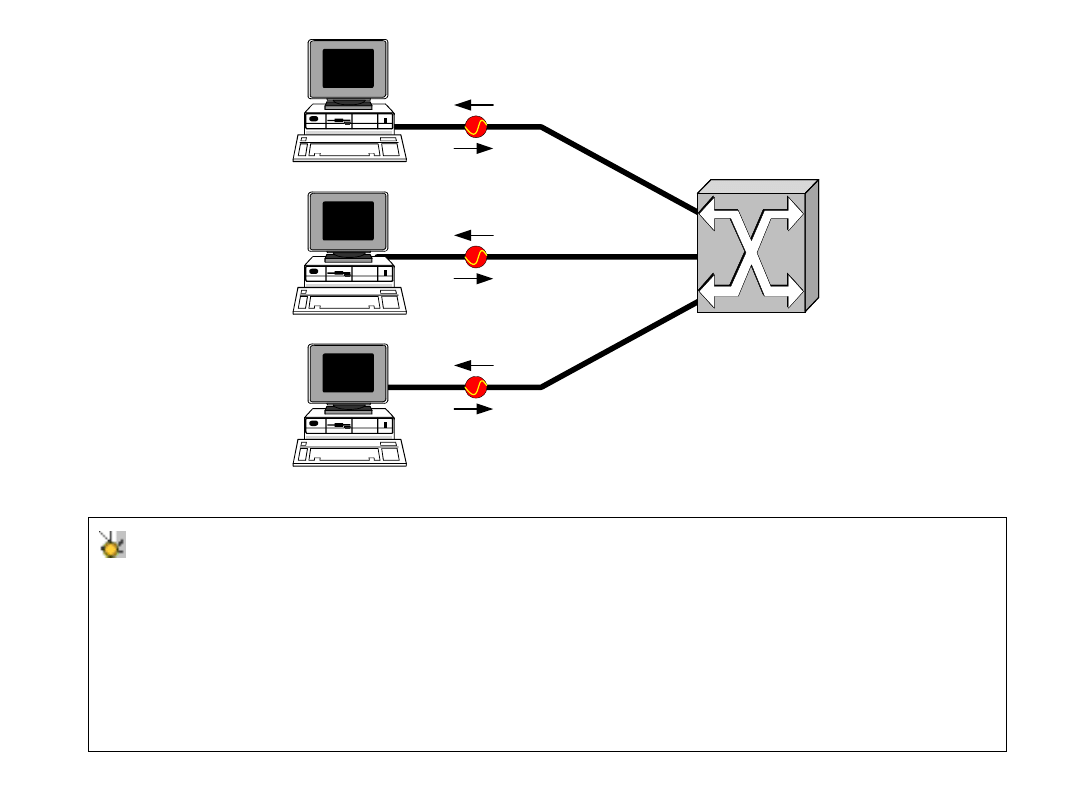

1. Komunikują się ze światem analogowym

korzystając

z przetworników A/C oraz C/A.

2. Przesyłają informacje cyfrowe z dowolnych

źródeł

(

zarówno sygnały foniczne jak i dane

).

3. W prosty sposób przesyłają informacje

sygnalizacyjne.

4. Łatwa jest realizacja zwielokrotnienia.

5. Korzystają z najnowszych rozwiązań

technologicznych.

6. Korzystają z różnych mediów transmisyjnych.

7. Pozwalają na tworzenie pól komutacyjnych o

dużych

pojemnościach i małych rozmiarach

Charakterystyka systemów cyfrowych

Charakterystyka systemów cyfrowych

8. Jakość transmisji nie zależy od liczby węzłów ani liczby

kanałów, przez które przechodzi sygnał.

9. Szum w kanale transmisyjnym nie wpływa na jakość

sygnału odbieranego.

10. Źródłem szumu w systemie jest przetwornik A/C.

11. Wzmacnianie sygnału w torze zastąpione regeneracją.

12. Możliwe jest tworzenie systemów odpornych na

niepowołany dostęp.

13. Wymagają szerszego pasma kanału transmisyjnego.

14. Wymagają synchronizacji zegarów oraz ramek.

Created with an unregistered version of Advanced Grapher - http:/ / www.serpik.com/ agrapher/

Created with an unregistered version of Advanced Grapher - http:/ / www.serpik.com/ agrapher/

Created with an unregistered version of Advanced Grapher - http:/ / www.serpik.com/ agrapher/

Sygnał # 1

Sygnał # 2

Czas

Amplituda

Czas

Czas

Amplituda

Amplituda

Amplituda

Czas

Sygnał # N

...

...

...

Ramka i - 1

Ramka i

Ramka i + 1

S

2

S

1

S

N

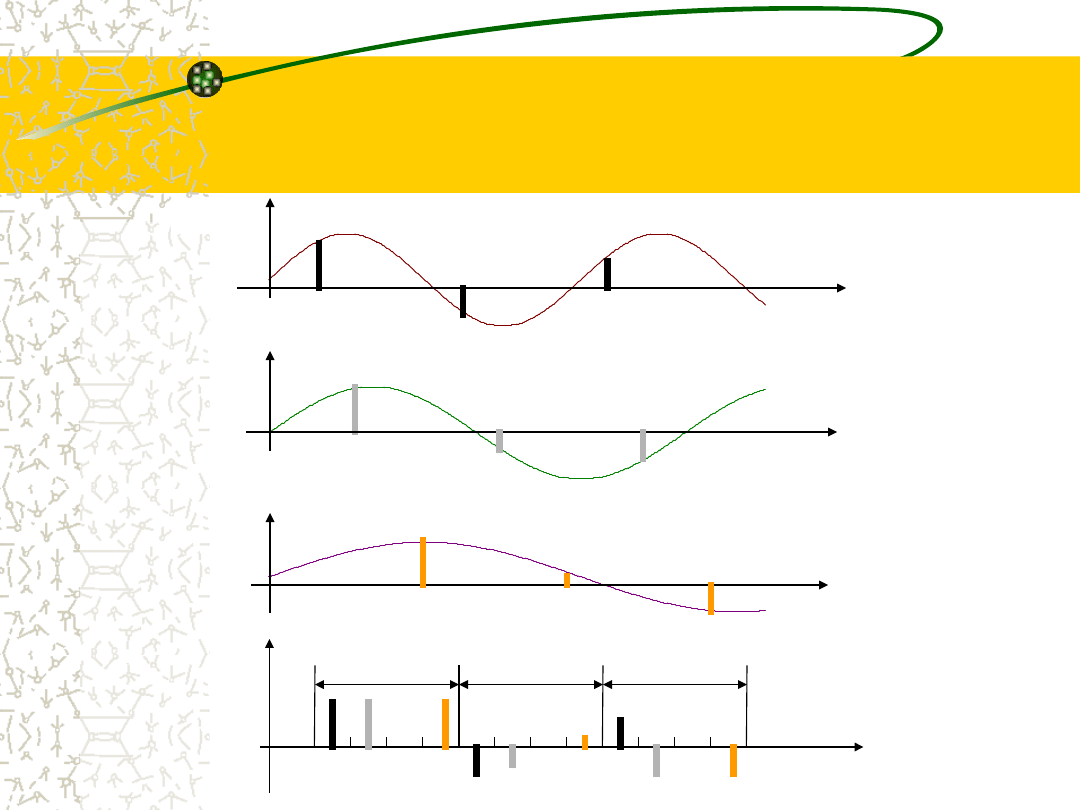

Przebiegi czasowe TDM

Przebiegi czasowe TDM

Zwielokrotnienie w

Zwielokrotnienie w

dziedzinie czasu

dziedzinie czasu

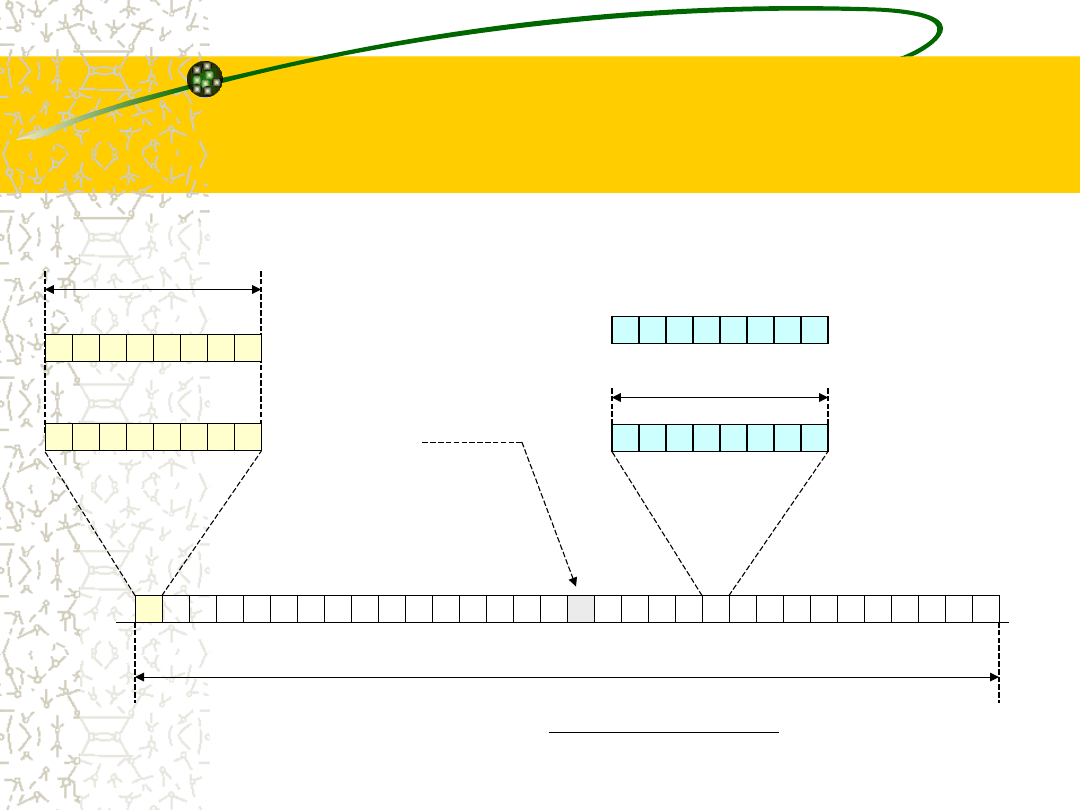

Zwielokrotnienie w dziedzinie czasu polega na

ustaleniu stałego odcinka czasu nazywanego

ramką

,

która

jest synchronicznie przesyłana w kanale.

Ramkę dzieli się na mniejsze odcinki zwane

szczelinami

, w których przesyła się wartości

chwilowe

przenoszonego sygnału.

0

Ramka

16

31

30

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15

17 18 19 20 21 22 23 24 25 26 27 28 29

Szczelina 0

- synchronizacyjna

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

Szczelina kanałowa

R

0

0

1

1

0

1

1

S

Nr. segm. Nr. przedziału

Szczelina sygnalizacyjna

Czas ramki =

125s

( T = 1/f

p

= 1/8.000);

Czas szczeliny = 125 / 32 =

3.9 s

;

1 bit = 3.9 s / 8 – 488 ns;

Przepływność binarna:

8.000 * 32 * 8 = 2.048.000 b/s =

2.048 kb/s = 2,048 Mb/s.

R

1

A

X

X

X

X

X

Ramka systemu PCM

Ramka systemu PCM

32/30

32/30

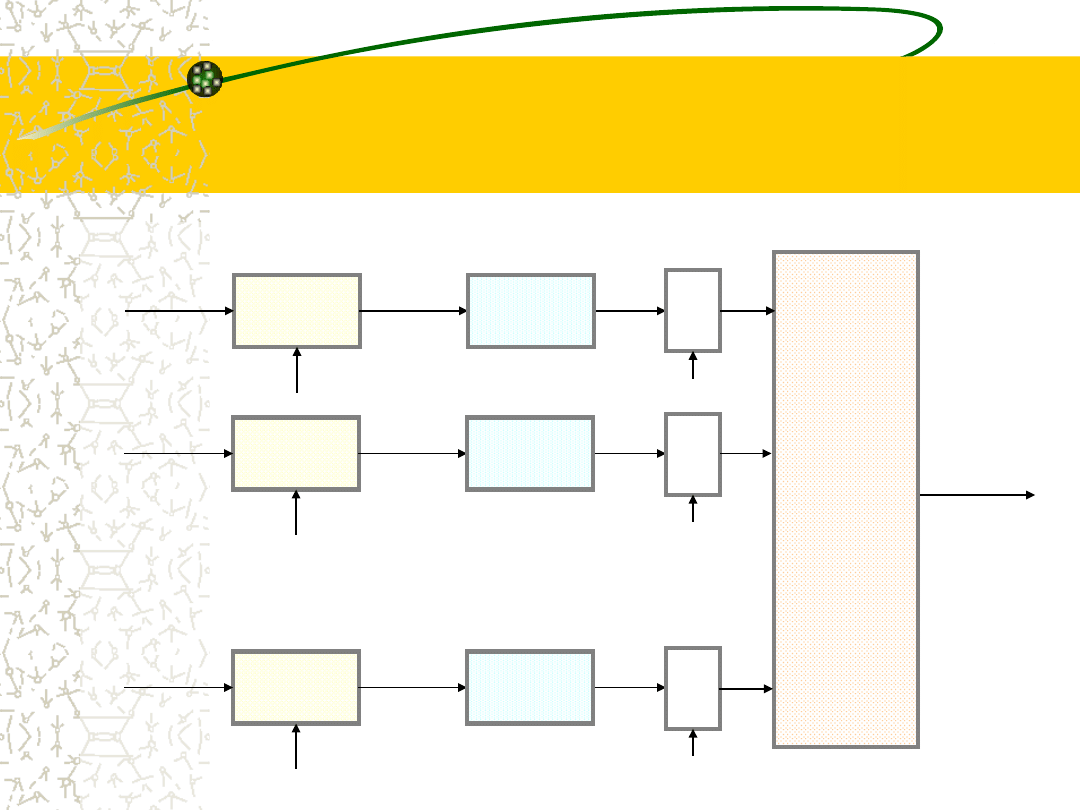

Zasada zwielokrotnienia

Zasada zwielokrotnienia

TDM

TDM

Układ

próbkujący

Sygnał wej. 1

KT

Pamięć

Układ

próbkujący

Sygnał wej. 2

KT + T

Pamięć

Układ

próbkujący

Sygnał wej. n

Pamięć

S

U

M

A

T

O

R

.

.

.

.

.

.

KT + (n-1)T

B

B

B

S

y

g

n

a

ł

zw

ie

lo

k

ro

tn

io

n

y

T = T / n

0 1 2 3 4 5 6 7

Szczelina 0

Szczelina 1

Szczelina 2

Szczelina 31

Ramka zawierająca 32 szczeliny

Szczelina 0

1 0 1 1 0 0 1 0

A

C

A

C

.

.

.

M

u

lt

ip

le

k

s

e

r

.

.

.

0

31

N

a

d

a

jn

ik

i

Przetwornik

liniowy

Przetwornik

liniowy

D

e

m

u

lt

ip

le

k

s

e

r

C

A

C

A

.

.

.

.

.

.

0

31

O

d

b

io

rn

ik

i

Zegary,

synchronizacja

Zegary,

synchronizacja

1 0 1 1 0 0 1 0

Przetworniki

analogowo-cyfrowe

Przetworniki

cyfrowo-analogowo

t

Uwe

Created with an unregistered version of Advanced Grapher - http:/ / www.serpik.com/ agrapher/

t

Uwy

t

U

wy

t

U

we

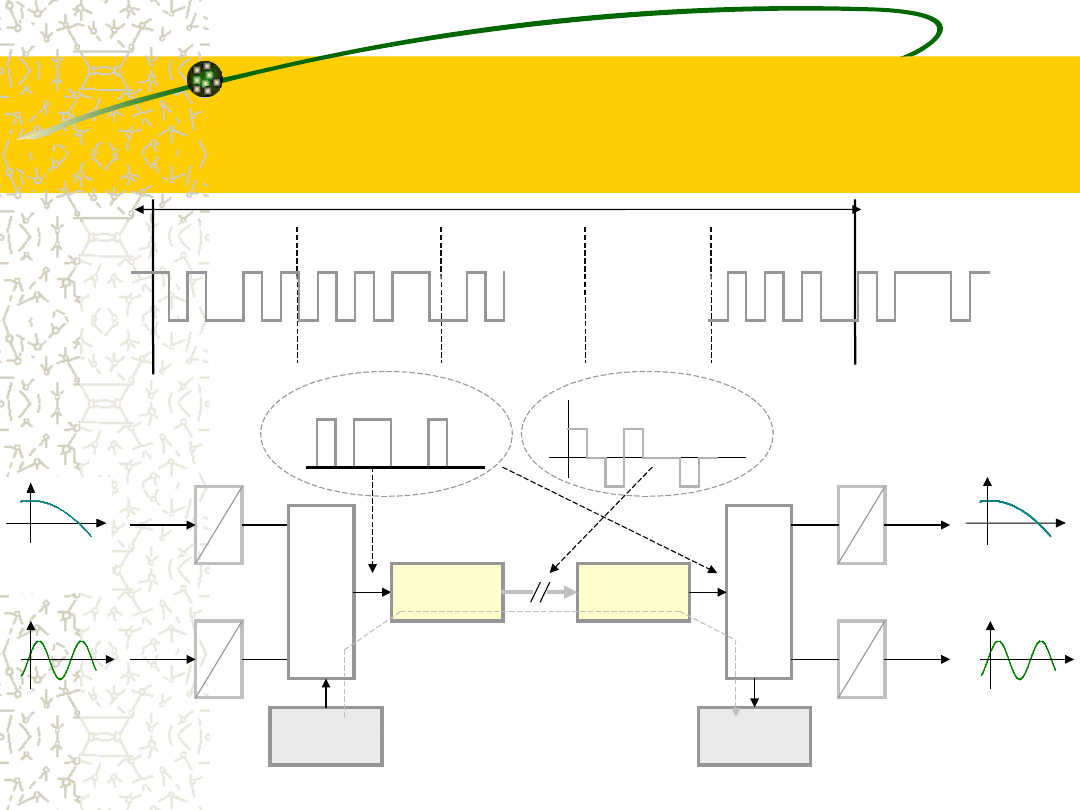

Zwielokrotniony system

Zwielokrotniony system

PCM

PCM

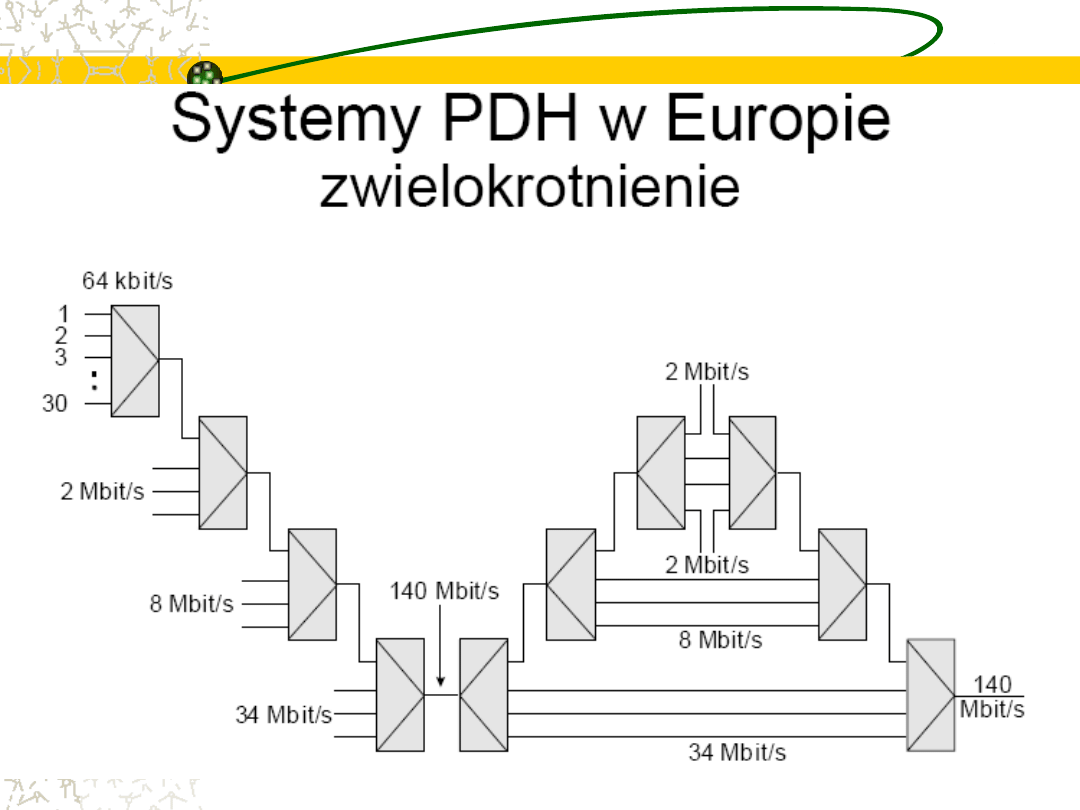

Systemy PCM hierarchii PDH

Systemy PCM hierarchii PDH

Hierarchia plesjochroniczna PDH (

P

lesjochronous

D

igital

H

ierarchy) zawiera następujące grupy:

1. Grupa pierwotna: 32 szczeliny

-

2,048

Mb/s;

2. Grupa wtórna: 128 szczelin -

8,448 Mb/s;

3. Grupa trójna: 512 szczelin -

34,368 Mb/s;

4. Grupa czwórna:2 048 szczelin

-

139,264

Mb/s.

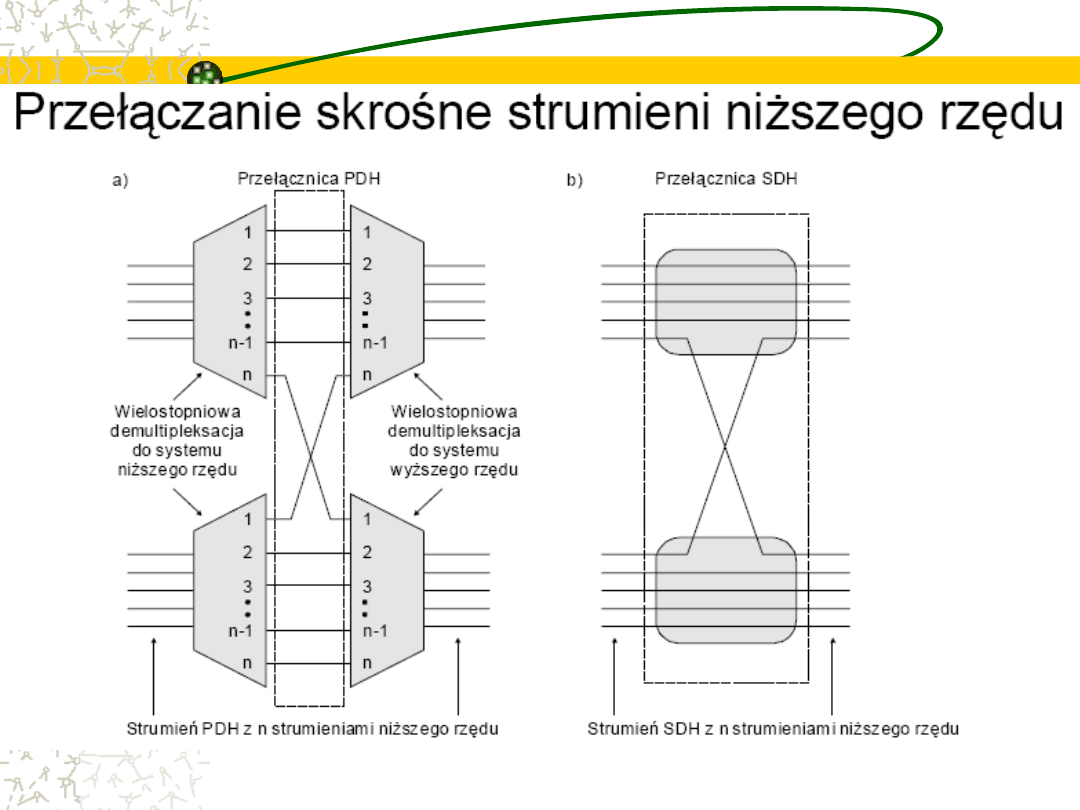

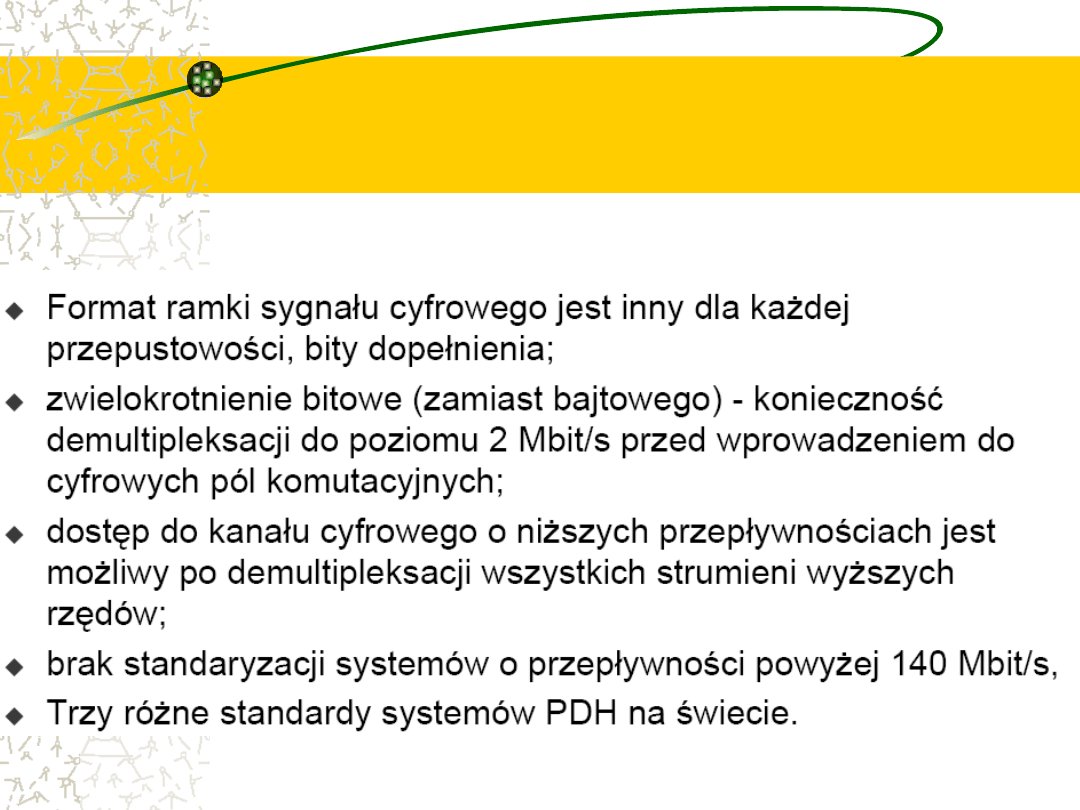

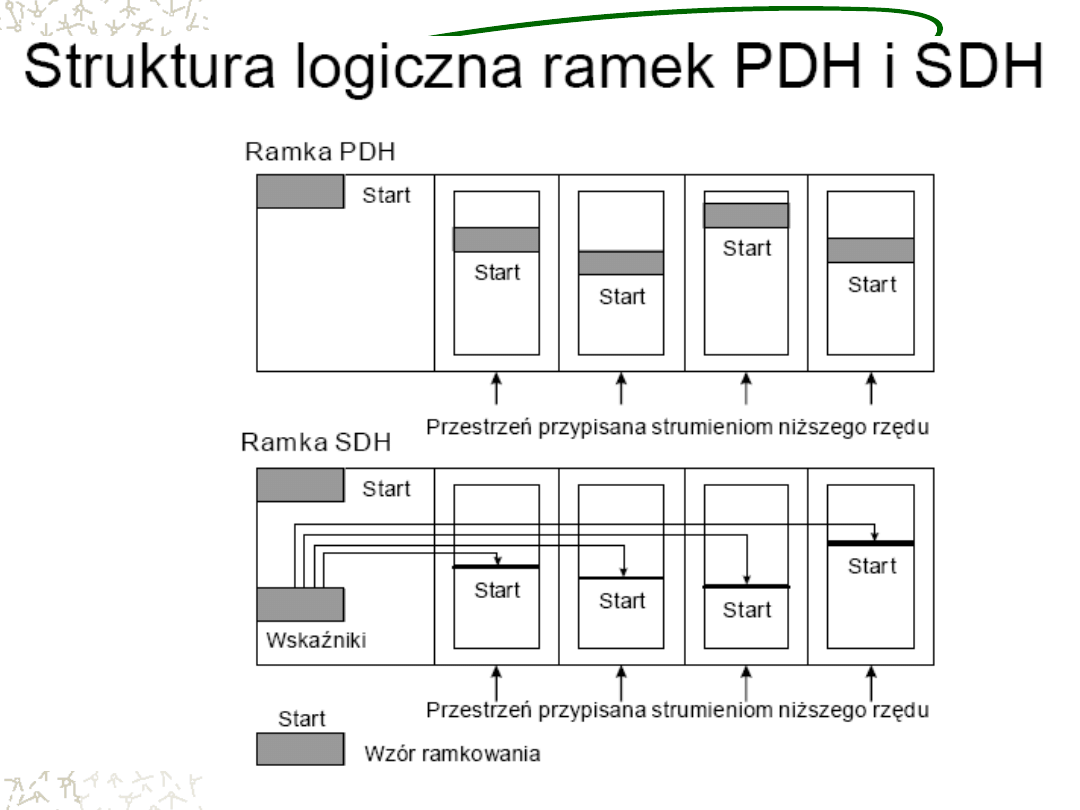

Wady systemów PDH

Wady systemów PDH

ATM

Switch

ATM

Switch

ATM

Switch

Server

Server

ATM

Switch

ATM Ethernet

Switch

ATM Router

10BaseT Hub

Ethernet

LAN

NSAP

Address

NSAP

Address

NSAP

Address

NSAP

Address

NSAP

Address

NSAP

Address

ATM

WAN

Przyjrzyjmy się najpierw procesowi rejestracji

adresów. Wiadomo, że każde urządzenie musi

być unikalnie identyfikowane w sieci ATM.

Każde urządzenie końcowe posiada swój adres

w formacie NSAP.

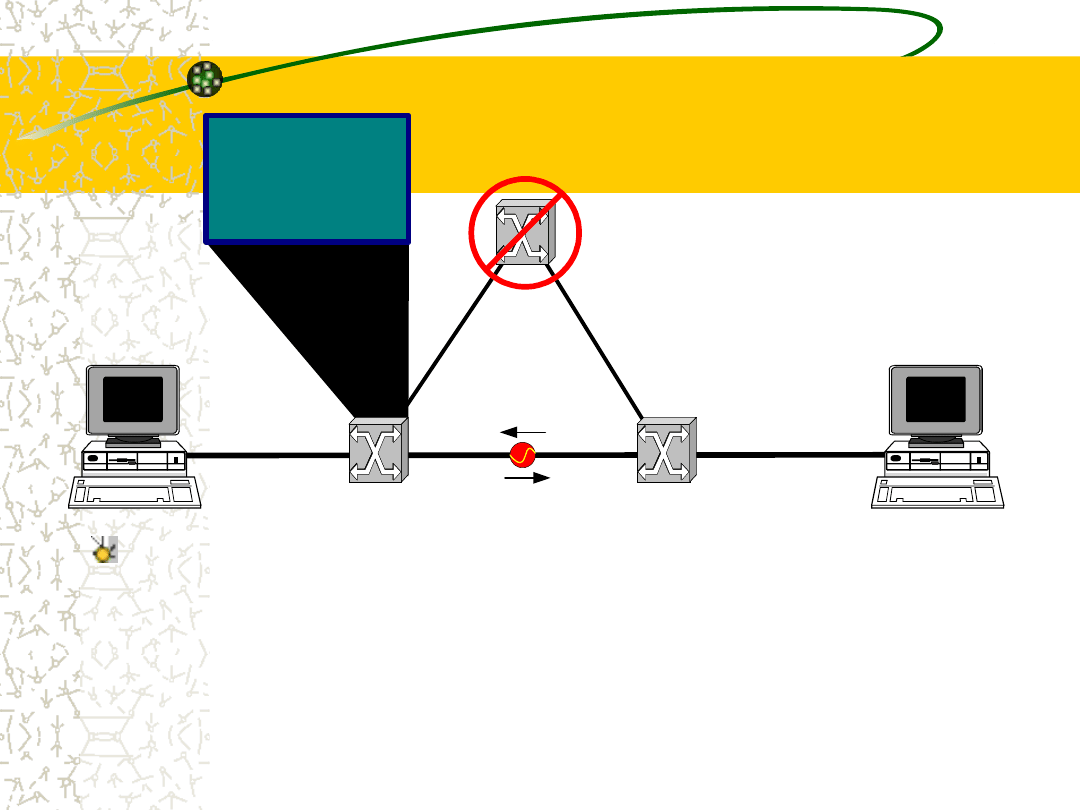

Switch A

Switch C

Endsystem

Endsystem

Switch B

Address Table

Switch B is inactive

Switch C is active

Elementy sieci ATM muszą przeprowadzić

proces rejestracji adresu zawsze wtedy gdy są

przyłączane do sieci oraz wtedy gdy zmienia

się ich status – czyli stają się aktywne lub

nieaktywne. Aktualny status urządzeń jest

kontrolowany

na

bieżąco

za

pomocą

sygnalizacji.

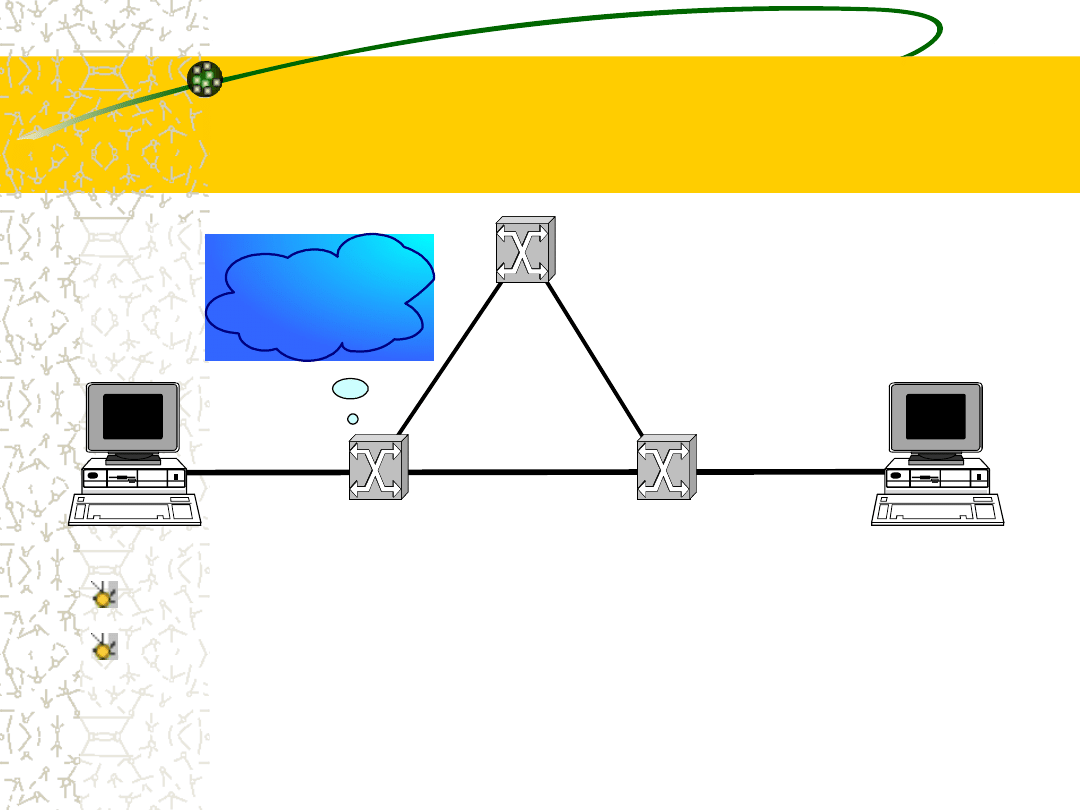

Switch A

Switch C

Endsystem

Endsystem

Switch B

Muszę przeprowadzić

proces

rejestracji adresu

Rozpocznijmy analizę rejestracji adresu.

Załóżmy, że przełącznik A zostaje włączony do

sieci.

.

Network Topology Table

xxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxx

Network Topology Table

xxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxx

Przełączniki

ATM

muszą

w

tej

fazie

zaktualizować dwie tablice. Jedna zawiera

informacje o topologii w sieciowej, druga

natomiast

posiada

adresy

urządzeń

końcowych.

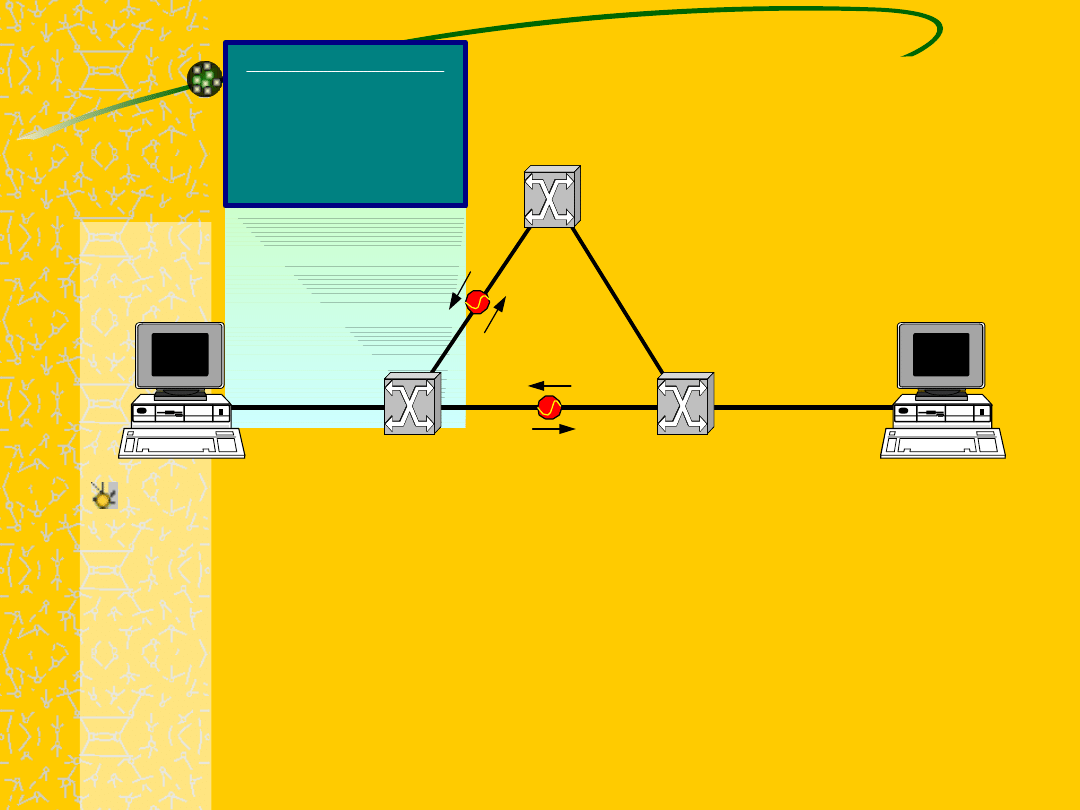

Switch A

Switch C

Endsystem

Endsystem

Switch B

Network Topology Table

Switch B's Prefix

xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

Switch C's Prefix

xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxxxx

Wymiana informacji o topologii następuje

dzięki zastosowaniu sygnalizacji PNNI. Komórki

sygnalizacyjne zostają przesłane pomiędzy

przełącznikami ATM za pomocą kanału 18,

dzięki czemu następuje wymiana między nimi

prefiksów NSAP. Na rysunku widać, że

przełącznik A buduje swoja tablice zapełniając

ją prefiksami innych przełączników, które

odpowiedziały na jego zapytanie

.

.

Device C

Device B

Device A

Także podczas tego procesu, wykorzystując

sygnalizacje ILMI, przełącznik uzyskuje wiedzę

o

wszystkich

podłączonych

do

niego

urządzeniach. Ta dwukierunkowa wymiana

odbywa się na kanale 16 po którym

przemieszczają się komórki sygnalizacyjne ILMI

pomiędzy przełącznikiem a urządzeniami

końcowymi w interfejsie UNI.

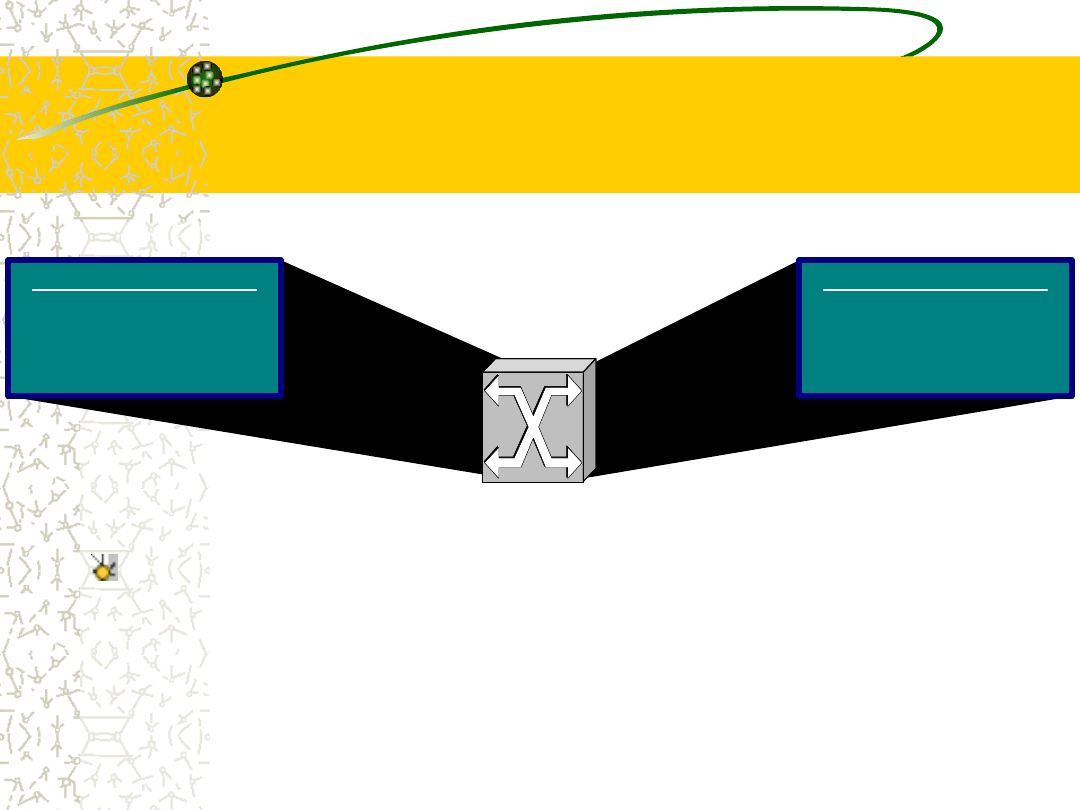

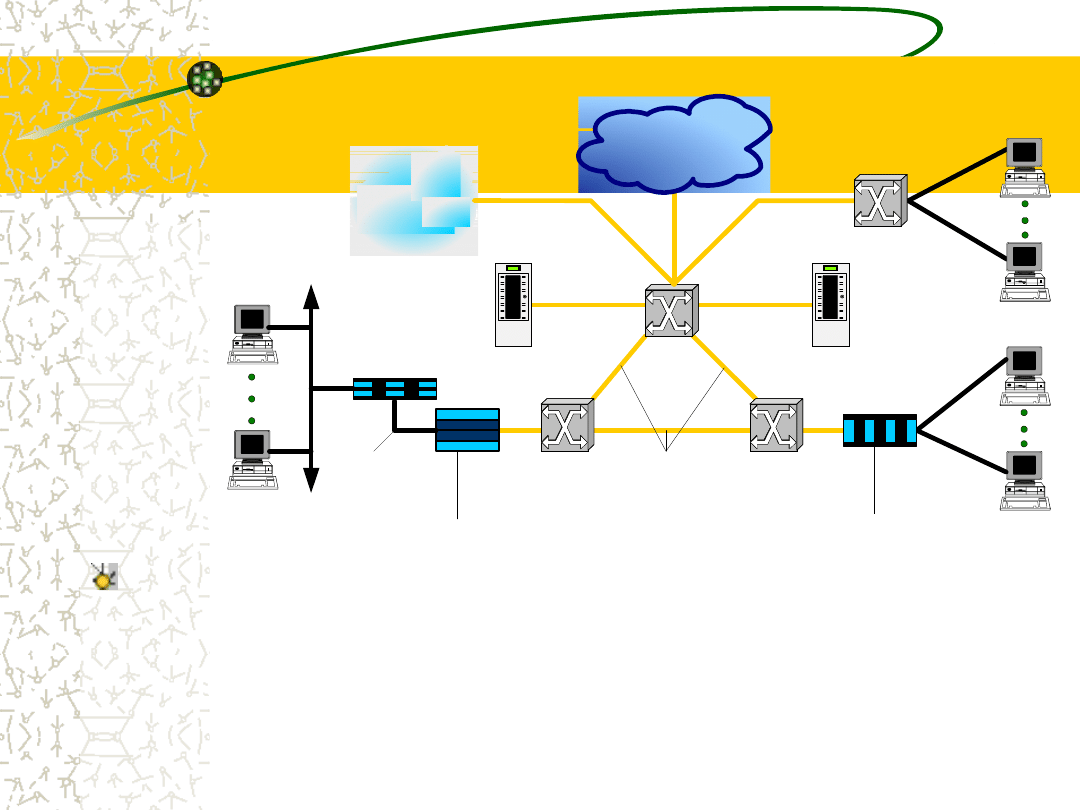

Przełącznik

ATM

Przełącznik

ATM

Przełącznik

ATM

ATM WAN

Serwer

Serwer

Przełącznik ATM

Workgroup

Przełącznik

ATM Ethernet

Urządzenie brzegowe

ATM Router

10BaseT Hub

Ethernet

LAN

Urządzenie brzegowe

Publiczna sieć

telefoniczna

10BaseT

E1

STM-1

STM-1

STM-1

OC3

STM-1

STM-1

STM-4

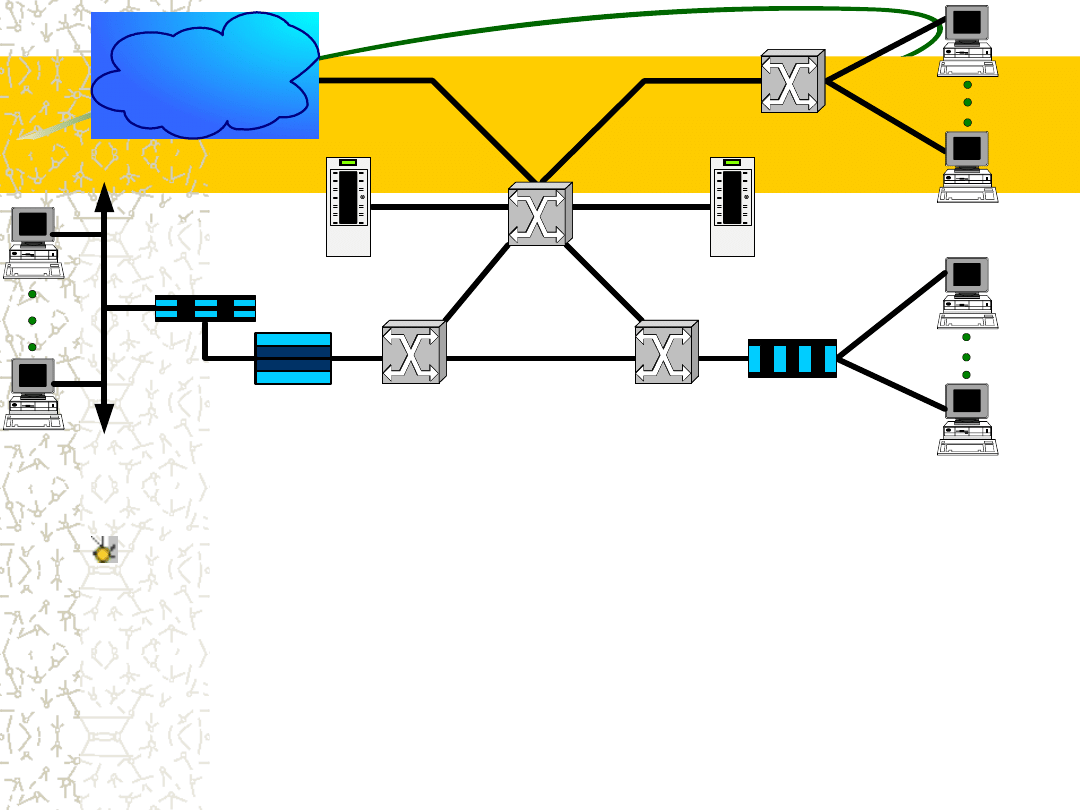

W połączeniach sieci ATM wykorzystuje się

głównie łączy światłowodowych oraz kabli

miedzianych – par symetrycznych.

.

Rozproszona architektura

central

Sterowanie

R. S. U.

Sterowanie

R. S. U.

PCM 2 Mb/s

20 km

Sterowanie

R. S. U.

Sterowanie

R. S. U.

PCM 2 Mb/s

30 km

Moduł końcowy

Moduł końcowy

Moduł pośredniczący

Moduł pośredniczący

Sterowanie

C

za

so

w

e

p

o

le

k

o

m

u

ta

c

y

jn

e

Procesor

centralny

HOST

PCM 2 Mb/s

PCM 2 Mb/s

60 km

Sterowanie

L. S. U.

20 km

Rozproszona architektura

central

Czynniki wpływające na rozproszoną architekturę

centrali.

1. tanie i wydajne układy mikroprocesorowe

pozwalające

implementować wiele funkcji sterowania w

modułach;

2. tanie oraz dostępne komutatory dla realizacji

funkcji

komutacyjnych w modułach (np. koncentracja);

3. tanie oraz inteligentne systemy transmisyjne

PCM

(dotyczy to w szczególności systemów SDH).

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

Wyszukiwarka

Podobne podstrony:

PDH,SDH,Centrale

Plezjochroniczna hierarchia cyfrowa PDH i SDH synchronizacja

Wykład6 systemy PDH i SDH

Wykład7 Optyczne techniki w PDH i SDH

wyk ad 4b systemy transmisyjne pdh sdh

Systemy i sieci SDH i PDH

BANK CENTRALNY I JEGO FUNKCJE

Bank centralny 5

Magazyny i centra logistyczne

Europejski Bank Centralny

Bank centralny

Centralne ogrzewanie id 109800 Nieznany

Kaniulacja żył obwodowych i centralnych u noworodków

BANK T02 S Bank Centralny

PDH, Broadband ISDN, ATM and all that

Zalety systemów SDH, SPRAWOZDANIA czyjeś

więcej podobnych podstron