Wojskowa Akademia

Techniczna

im. Jarosława Dąbrowskiego

Modulacja ∑-∆

w przetwornikach

Agnieszka Zalewska

E2C1N1

Plan

prezentacji

Zasada działania modulatora delta sigma

Zasada przetwarzania sygnału w 3

krokach

Przebiegi sygnałów modulatora ∑-∆

Szum kwantyzacji modulatora sigma –

delta w dziedzinie częstotliwości

Zależność SNR od współczynnika

nadpróbkowania

Przetwornik CDC

Modulacja Sigma – Delta w przetwornikach

2

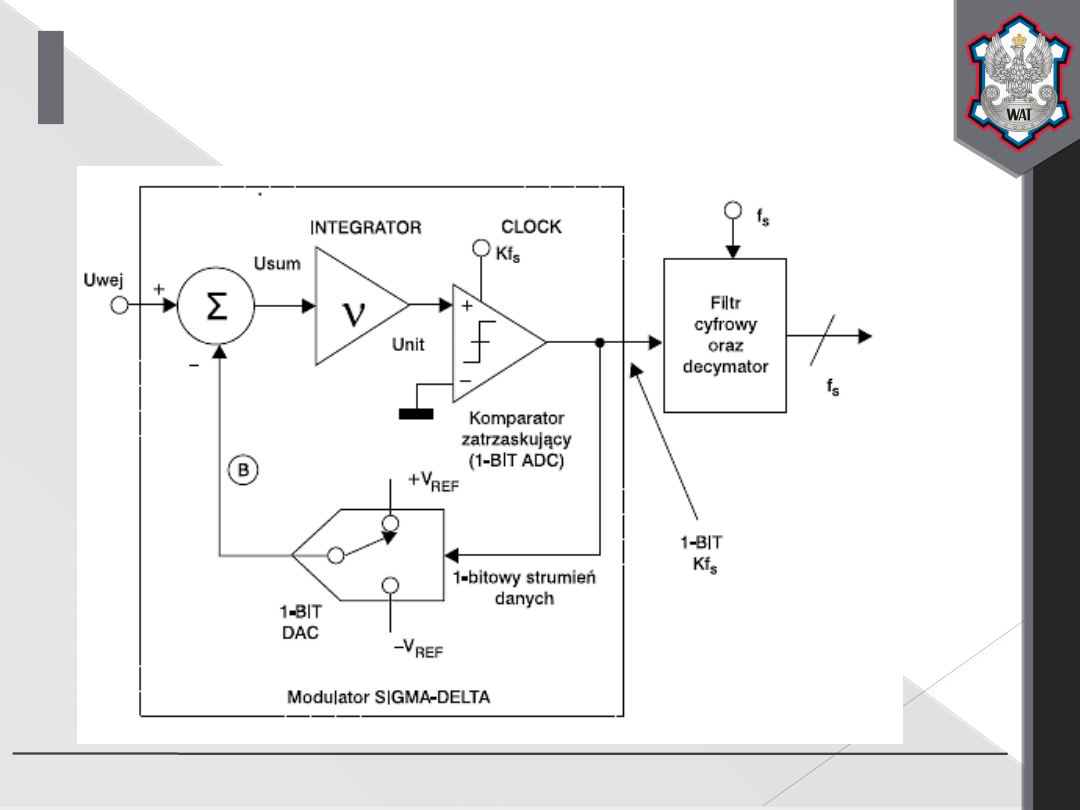

Zasada działania modulatora

delta sigma

Modulacja Sigma – Delta w przetwornikach

3

Zasada przetwarzania sygnału

Zasada przetwarzania wejściowego napięcia (U

wej

) na

wyjściowe słowo cyfrowe (DIG)

Zał.: U

wyj

=1,2 V, U

ref+

=5 V, U

ref-

=-5 V oraz po włączeniu

układu zasilania napięcia DIG=U

sum

=U

int

=0 V.

Krok 1

Napięcie wejściowe (U

we

j=1,2 V) jest sumowane z

napięciem wyjściowym (U

wyj

=0 V), czego wynikiem jest

napięcie sumacyjne (U

sum

=1,2 V) podane na wejście układu

całkującego. Po całkowaniu napięcie wyjściowe układu

całkującego (U

int

=1,2 V) podawane jest na komparator;

ponieważ napięcie wejściowe jest większe od potencjału

masy (U

int

>0) komparator wystawia na wyjściu dodatnie

napięcie referencyjne (Uwyj=5 V) odpowiada to stanowi

„1” na wyjściu.

Modulacja Sigma – Delta w przetwornikach

4

Zasada przetwarzania sygnału

Krok 2

Napięcie wejściowe (

Uwej

=1,2 V) sumowane jest z napięciem

wyjściowym komparatora (U

wyj

=5 V), czego wynikiem jest

napięcie sumacyjne(U

sum

=1,2 V–5 V=–3,8 V) podane na

wejście układu całkującego. Po całkowaniu wyjściowe

napięcie (U

int

=1,2 V–3,8 V=–2,6 V) podawane jest na

komparator, ponieważ wejściowe napięcie jest mniejsze od

potencjału masy (U

int

<0) komparator wystawia na wyjściu

potencjał masy (U

wy

j=0 V) odpowiada to stanowi „0” na

wyjściu.

Modulacja Sigma – Delta w przetwornikach

5

Zasada przetwarzania sygnału

Krok 3

Napięcie wejściowe (U

wej

=1,2 V) sumowane jest z napięciem

wyjściowym (U

wyj

=0 V), czego wynikiem jest napięcie

sumacyjne (U

sum

=1,2 V) podane na wejście układu

całkującego. Po całkowaniu wyjściowe napięcie(U

int

=-2,6 V+1,2

V=-1,4 V) podawane jest na komparator; ponieważ wejściowe

napięcie jest mniejsze od potencjału masy (U

int

<0) komparator

wystawia na wyjściu potencjał masy (U

wyj

=0 V) odpowiada to

stanowi „0” na wyjściu.

Powtarzając wyżej przedstawiony algorytm uzyskamy strumień

bitowy na wyjściu komparatora DIG = ”01000100010001...”,

uśredniając w filtrze cyfrowym otrzymamy wartość 24% z

napięcia zasilania komparatora U

ref+

=5 V, czyli dokładnie 1,2 V.

Modulacja Sigma – Delta w przetwornikach

6

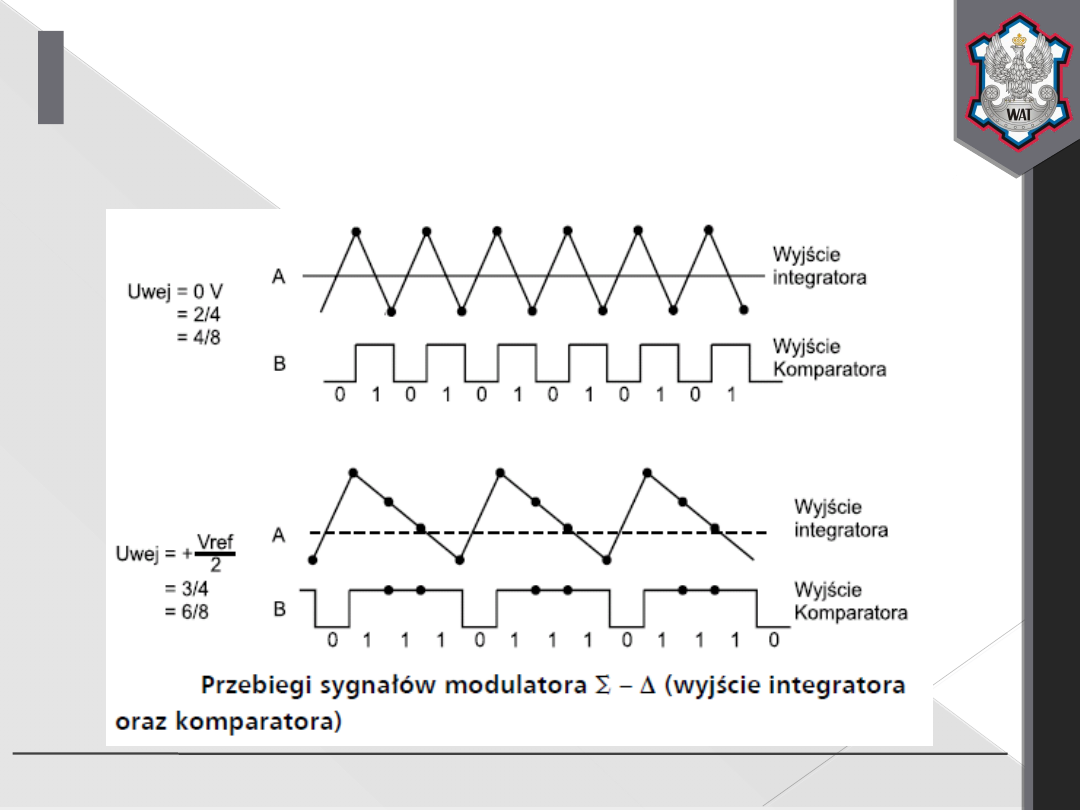

Przebiegi sygnałów

modulatora ∑-∆

Modulacja Sigma – Delta w przetwornikach

7

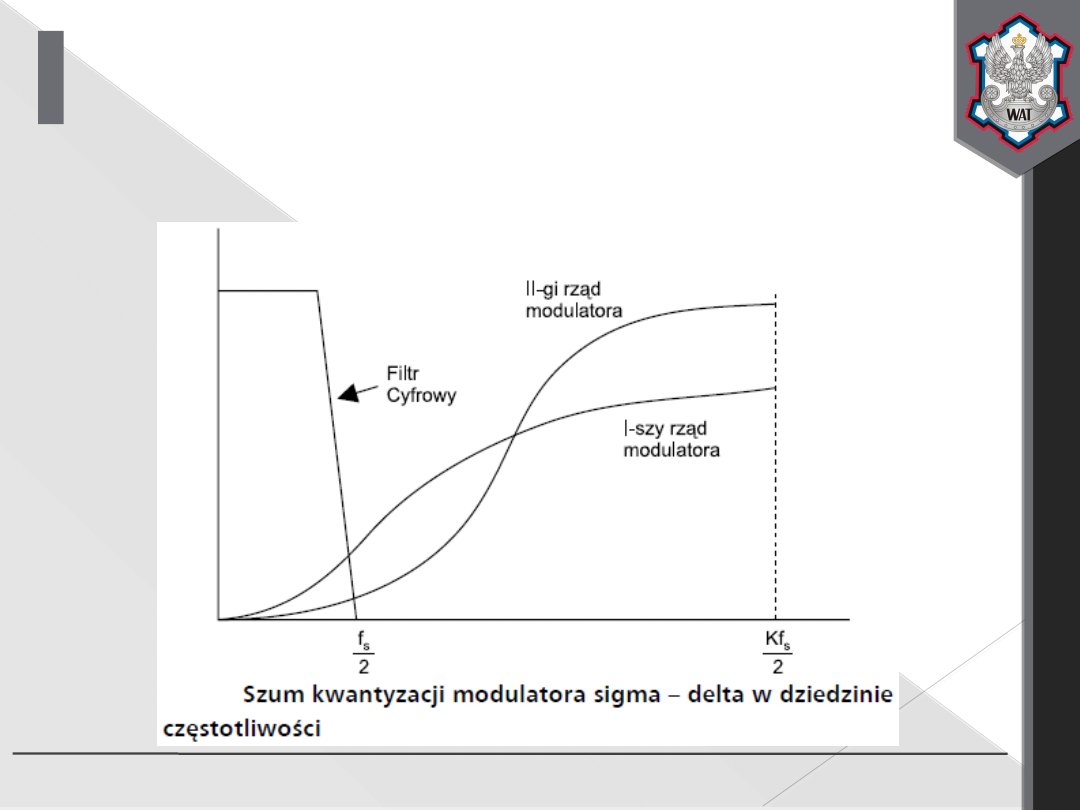

Szum kwantyzacji modulatora

sigma – delta w dziedzinie

częstotliwości

Modulacja Sigma – Delta w przetwornikach

8

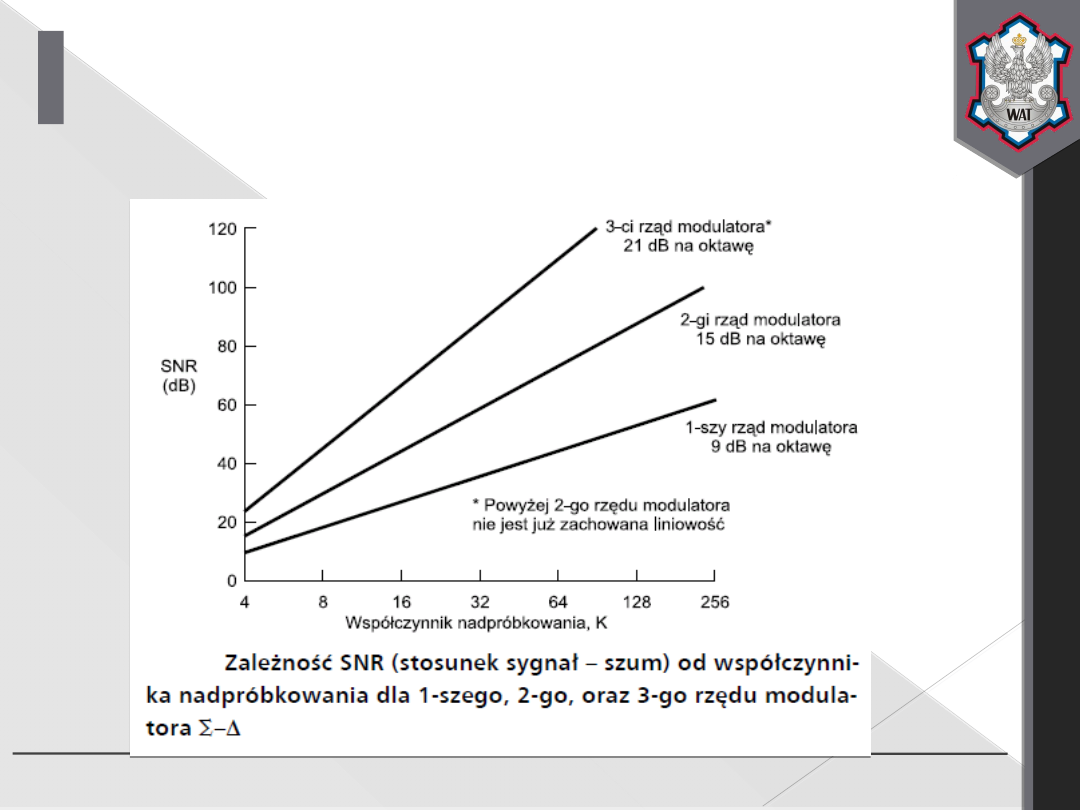

Zależność SNR od

współczynnika nadpróbkowania

Modulacja Sigma – Delta w przetwornikach

9

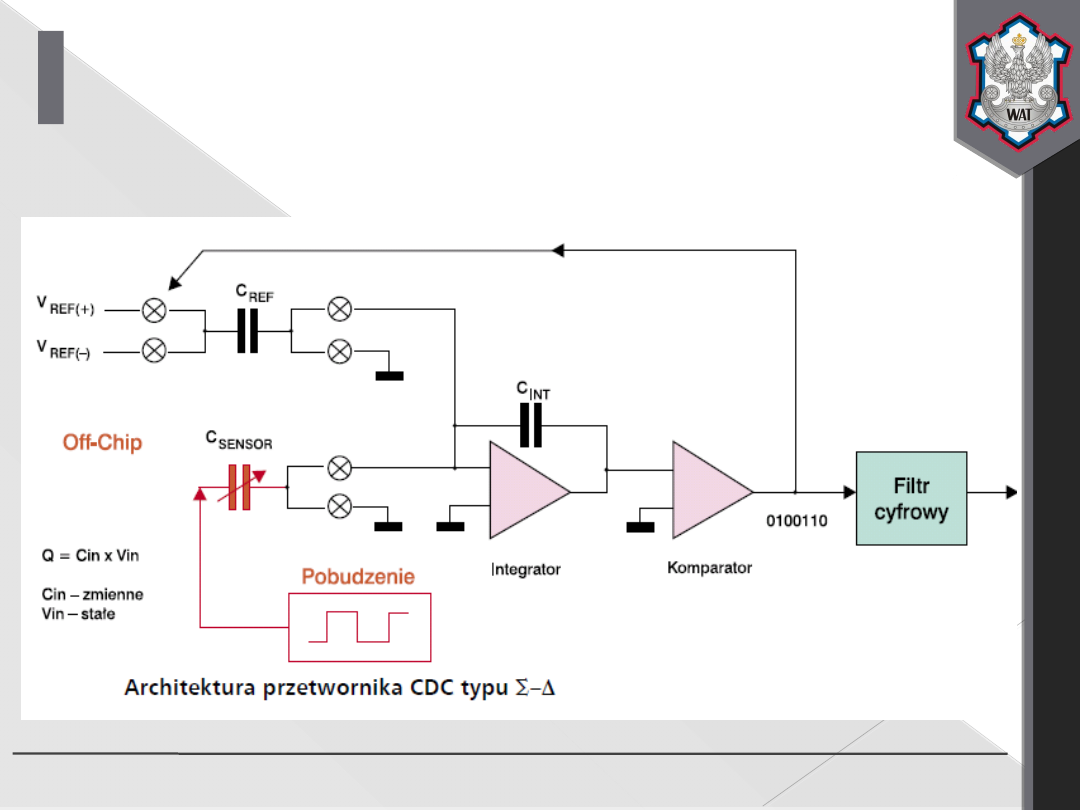

Przetwornik CDC

(Capacitance-to-Digital Converter)

Pojemności Cin oraz Cref ładowane są w fazie f1 i

całkowane w fazie f2. Sprzężenie zwrotne utrzymuje

ładunek referencyjny Cref równy ładunkowi wejściowemu

Cin. Ładunek referencyjny jest ładowany proporcjonalnie

do cyfrowego wyjścia komparatora, skutkiem tego cyfrowe

wyjście jest proporcjonalne do ładunku wejściowego.

Ewolucją zaprezentowanego układu jest przetwornik

pojemnościowo – cyfrowy (CDC).

Modulacja Sigma – Delta w przetwornikach

10

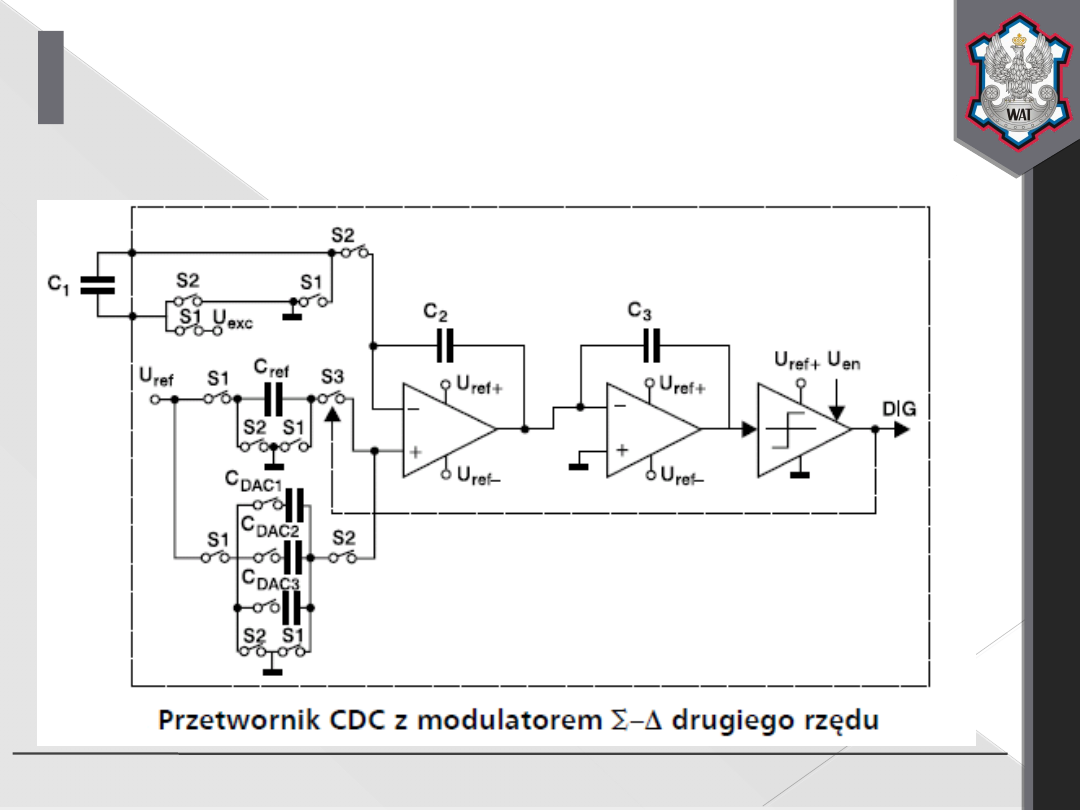

Przetwornik CDC

Modulacja Sigma – Delta w przetwornikach

11

Przetwornik CDC

Modulacja Sigma – Delta w przetwornikach

12

Dziękuję za uwagę

Bibliografia: ELEKTRONIKA PRAKTYCZNA 3/2009 Przetworniki

CDC (1) Modulacja Sigma – Delta w przetwornikach pojemność –

cyfra P. Pietrzyk

Modulacja Sigma – Delta w przetwornikach

13

Document Outline

- Slide 1

- Plan prezentacji

- Zasada działania modulatora delta sigma

- Zasada przetwarzania sygnału

- Zasada przetwarzania sygnału

- Zasada przetwarzania sygnału

- Przebiegi sygnałów modulatora ∑-∆

- Slide 8

- Zależność SNR od współczynnika nadpróbkowania

- Przetwornik CDC (Capacitance-to-Digital Converter)

- Przetwornik CDC

- Przetwornik CDC

- Slide 13

Wyszukiwarka

Podobne podstrony:

Przetwornik analogowo cyfrowy typu sigma delta

Wykład 1 2 przetworniki sigma delta

Principles of Sigma Delta Conversion for Analog to Digital Converters

Applications of polyphase filters for bandpass sigma delta analog to digital conversion

Principles of Sigma Delta Conversion for Analog to Digital Converters

Applications of polyphase filters for bandpass sigma delta analog to digital conversion

Principles of Sigma Delta Conversion for Analog to Digital Converters

delta sigma

Modulacja DELTA id 305917 Nieznany

Metrologia-lab-Mostek Thomsona, MOSTEK~1, δσ

Błąd Pośredni, OCENAB~1, δσ Wydział Transportu

Delta Call Plus i Sigma katalog

Modulacja DELTA

przetworniki indukcyjne

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

Przetworstwo produktow rolniczych

MLEKO I PRZETWORY MLECZNE (2)

Ceny detaliczne i spożycie warzyw i ich przetworów

więcej podobnych podstron