Technika Cyfrowa- Laboratorium |

|||

Skład zespołu:

|

Temat ćwiczenia Bramki TTL |

||

Kierunek |

Data wykonania ćwiczenia |

Data złożenia sprawozdania |

Ocena |

2 ET-DI |

16.04.2009r |

30.04.2009r |

|

Uwagi

|

|||

Układy TTL (Transistor-Transistor Logic) są układami stosowanymi w praktyce od lat sześćdziesiątych, kiedy to wprowadzone zostały na rynek przez firmę Texas Instruments.

W okresie największej popularności układów TTL, przypadającym na lata 70. i 80., seria ta obejmowała ponad 300 pozycji katalogowych. W późniejszych czasach część układów oryginalnej serii 74xx pojawiła się w seriach pochodnych, wykonywanych w technologiach TTL-LS (o obniżonym poborze mocy) oraz S (o podwyższonej szybkości), opartych o tranzystory Schottky'ego. W latach 90. układy bipolarne TTL zaczęły ustępować miejsca układom CMOS (Complementary MOS). Częściowo kompatybilne z układami serii 74xx są produkowane do dziś odpowiedniki tych układów serii HC i HCT .

Serie pochodne:

L - o małym poborze mocy (ze względu na niską częstotliwość pracy szybko zastąpiona przez LS), co uzyskano poprzez zwiększenie wartości rezystancji o około rząd wielkości, ale bramki te przełączały się wolniej

H - High speed (zastąpiona przez AS), o około dwukrotnie mniejszych wartościach rezystancji niż w standardowych bramkach, bramki przełączały się szybciej, ale pobierały większą moc.

S - szybkie bramki z diodami Schottky'ego (zastąpiona przez LS i AS)

LS - szybkie bramki z diodami Schottky'ego o małym poborze mocy (najważniejsza obecnie seria - wyparła pozostałe)

AS - Advanced Schottky

ALS - Advanced Low Power Schottky

F - Fast (zbliżona szybkością do AS)

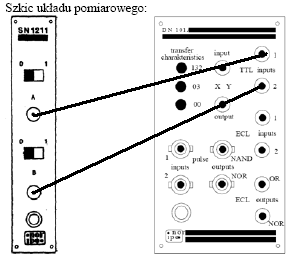

Bramki badane w ćwiczeniu:

7400

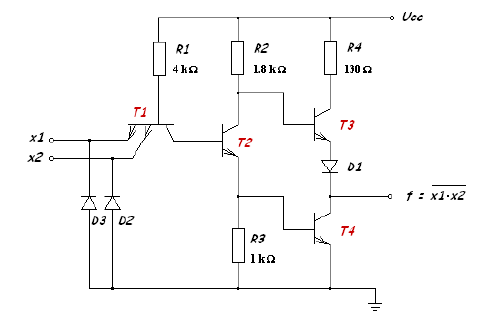

Układ SN7400 zawiera w swojej obudowie cztery dwuwejściowe bramki NAND. Stopień wejściowy bramki stanowi tranzystor wieloemiterowy T1 (odpowiednik diodowej bramki AND), zaś tranzystor T2 działa dwojako: jako wtórnik emiterowy i inwerter ( jest podstawowym elementem wzmacniacza pośredniczącego). Tranzystory T3 i T4 stopnia wyjściowego (tzw. wzmacniacza przeciwsobnego) zapewniają mała impedancje wyjściowa zarówno przy poziomie L, jak i H na wyjściu.

Podanie stanu niskiego na którekolwiek z wejść (A lub B) spowoduje przejście tranzystora T1 w stan aktywny. Powoduje to zatkanie tranzystora T2 przez co przez T2 nie płynie prąd. W takim przypadku na bazie tranzystora Q3 pojawia się napięcie, a przez co przez ten tranzystor płynie prąd. Przez rezystor R1 nie płynie prąd więc tranzystor Q2 jest zatkany. Na wyjściu bramki panuje wtedy stan wysoki.Z powyższego schematu wynika, że pozostawienie wejścia A lub B wiszącego jest traktowane tak jakby był podany stan wysoki. Napięcie to pochodzi ze złącza Baza-Emiter (przez rezystor w bazie nie płynie prąd więc napięcie to jest o 0,7V niższe od zasilania).

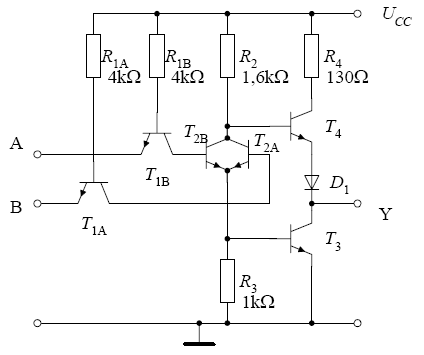

7402

Układ SN7400 zawiera w swojej obudowie cztery dwuwejściowe bramki NOR. Aby na wyjściu uzyskać stan wysoki T3 musi być odcięty, a T4 i D muszą przewodzić, co mam miejsce przy odciętych równocześnie T2A i T2B, tzn. gdy na wejściach panuje stan niski. Gdy na jednym z wejść jest stan wysoki, to przynajmniej jeden z tranzystorów wejściowych jest w inwersji i albo T2A albo T2B jest nasycony, co powoduje nasycenie T3 i odcięcie T4, a na wejściu stan niski

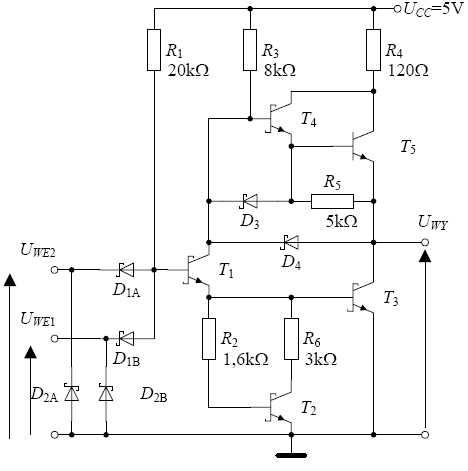

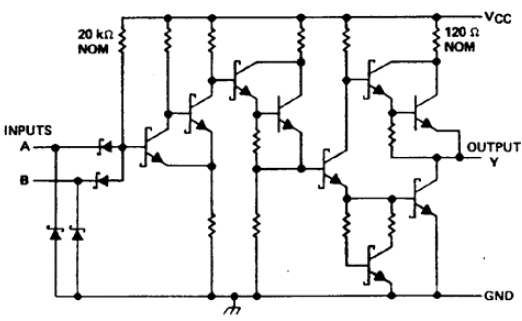

LS00

Układy z serii LS umożliwiają w znacznej mierze osiągniecie zarówno małej mocy strat, jak i dużej szybkości działania.

Wejściowy układ AND jest zrealizowany jako diodowy. Przy zastosowaniu diod Schottky'ego jest to układ szybszy niż klasyczna struktura wieloemiterowa. Ponadto zaleta układu diodowego jest większe dopuszczalne napięcie wejściowe (równe co najmniej 7V), gdyż typowe napięcie przebicia diod wejściowych wynosi 15V. Wada tej konfiguracji jest natomiast obniżona wartość napięcia progowego (1.1V).

Układ zawiera w odróżnieniu od bramki 7400:

- Większe rezystancje R1 i R3 w celu obniżenia poboru mocy w stanie statycznym

- Tranzystory z zintegrowaną diodą Schottky'ego w celu zapobiegania głębokiemu nasycania tranzystorów, oraz diody Schottky'ego D3 i D4 w celu redukcji czasów przełączania bramki.

- Układ Darlingtona T4 i T5 w celu zwiększenia rezystancji wejściowej

74137

Jest to bramka z wbudowanym przerzutnikiem Schmitta. Przerzutnik ten charakteryzuje się tym, że wartości napięć wejściowych przy których następują przełączenia są różne zależnie od kierunku zmian napięcia wejściowego.

Jeżeli napięcie wejściowe rośnie to napięcie rzełączania jest wyższe a jeżeli maleje to niższe. Różnica napięć włączenia i wyłączenia nazywa się napięciem histerezy. Bramka tego typu jest stosowana przeważnie w celu zwiększenia odporności układu na zakłócenia, generatorach lub miejscach gdzie sygnał wejściowy jest wolnozmienny (lub czas jego narastania lub/i opadania są wolniejsze niż zalecane dla poprawnej pracy danej rodziny układów logicznych).

1) Określenie tablicy prawdy bramek

|

|

Wyjścia |

|

Wejście 1 |

Wejście 2 |

7400 |

7402 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

Funkcja |

NAND |

NOR |

|

2) Obserwacja przebiegów czasowych na wyjściach bramek sterujących impulsowo

|

7400 |

7402 |

Częstotliwość pomiarowa |

61,728 kHz |

61,7 kHz |

Minimalne napięcie sygnału wyjściowego Umin, V |

58mV |

119mV |

Maksymalne napięcie sygnału wyjściowego Umax, V |

3,68V |

3,73V |

Amplituda logiczna sygnału wyjściowego bramki TTL Upp, V |

3,625V |

3,61V |

Obserwacja przebiegów czasowych czasowych na wyjściu bramek sterowanych impulsowo:

1 - wejście A (kolor pomarańczowy)

2 - wejście B (kolor zielony)

3 - wyjście NAND (kolor fioletowy)

4 - wyjście NOR (kolor czerwony)

3) Obserwacja charakterystyk przejściowych

|

Badana Bramka |

Badana Bramka |

Badana Bramka |

Badana Bramka |

Badana Bramka |

|

74132 |

7400 |

7403 |

LS00 |

7437 |

Napięcie zasilania UCC, V |

5,1 |

5,1 |

5,1 |

5,1 |

5,1 |

UIL, V |

59,27m |

118m |

83m |

194m |

52m |

UIH, V |

3,79 |

4,9 |

3,64 |

3,72 |

3,62 |

UOH, V |

3,79 |

4,91 |

3,65 |

3,75 |

3,65 |

UOL, V |

58m |

95m |

133m |

209m |

57m |

UT, V (Jeśli nie ma histerezy) |

- |

1,35 |

1,43 |

1,11 |

1,42 |

UT-, V(Jeśli jest histereza) |

826m |

- |

- |

- |

- |

UT+, V (Jeśli jest histereza) |

1,74 |

- |

- |

- |

- |

NML, V |

1,68 |

1,23 |

1,34 |

0,91 |

1,36 |

NMH, V |

2,96 |

3,55 |

2,22 |

2,61 |

2,2 |

// Bramki z otwartym kolektorem umożliwiają równoległe łączenie wyjść w celu utworzenia sumy montażowej , sterowani przekaźników, wskaźników,

Wyszukiwarka

Podobne podstrony:

[SPR] Modelowanie doc

Badanie bramek NAND TTL doc

Wera spr fluidyzacja doc

SPR 1DLA DOC

SPR 51 (2) DOC

SPR 85 (2) DOC

SPR 2MAC DOC

SPR C910 DOC

SPR 2DAR DOC

[SPR] Modelowanie (2) doc

SPR 76 (2) DOC

spr ściąga doc

SPR 52 (2) DOC

SPR 1DAR DOC

spr 5 marcin doc

wahadlo fizyczne spr doc

Spr 4?a bom doc

spr (9) doc

więcej podobnych podstron