Laboratorium Układów Cyfrowych

Ćwiczenie 8: Układy asynchroniczne.

Jarosław Sadowski, Michał Wilkowski,

Telekomunikacja, semestr 5, grupa dziekańska 4

Data wykonania ćwiczenia: 3.11.1999r.

Do wykonania następujące zadania:

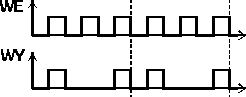

1. Zaprojektować układ asynchroniczny działający zgodnie z poniższymi wykresami.

2. Zaprojektować przerzutnik typu T Master-Slave.

1. Wstępnie można wyróżnić sześć stanów, w których może znajdować się projektowany układ asynchroniczny. Stany te następują kolejno po sobie, najlepiej jest je więc ponumerować jako kolejne liczby w kodzie Graya. Przyjęto numerację stanów taką jak na poniższym rysunku.

Tabela przejść między stanami oraz przyjęta reprezentacja binarna stanów wygląda następująco:

Stan |

Reprezentacja |

Przejście dla 0 |

Przejście dla 1 |

Wyjście |

A |

000 |

A |

B |

0 |

B |

001 |

C |

B |

1 |

C |

011 |

C |

D |

0 |

D |

010 |

E |

D |

0 |

E |

110 |

E |

F |

0 |

F |

100 |

A |

F |

1 |

Pośród tych stanów żadne dwa nie są stanami niesprzecznymi: wszystkie różnią się albo stanem wyjścia albo kolejnymi przejściami. Oznaczając bity określające stan układu jako Q2, Q1 i Q0 otrzymujemy następującą tabelę opisującą działanie układu:

WE |

Q2 |

Q1 |

Q0 |

Q2' |

Q1' |

Q0' |

WY |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

X |

X |

X |

X |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

X |

X |

X |

X |

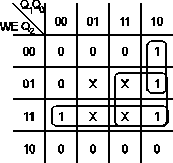

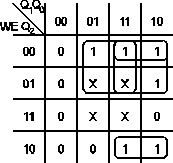

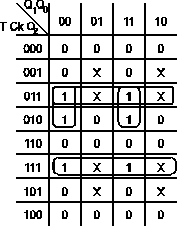

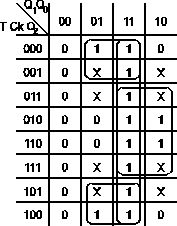

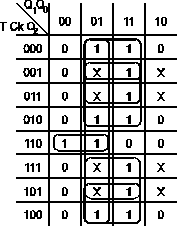

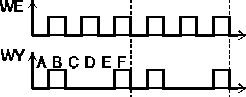

Tablice minimalizacji poszczególnych funkcji wyglądają następująco:

|

|

|

|

Wszystkie funkcje zostały zminimalizowane w ten sposób, by wyeliminować możliwość wystąpienia hazardów. Pełen schemat układu zamieszczono na następnej stronie.

Układ nie wymaga żadnych sekwencji do przetestowania - konieczny jest tylko sygnał zegarowy.

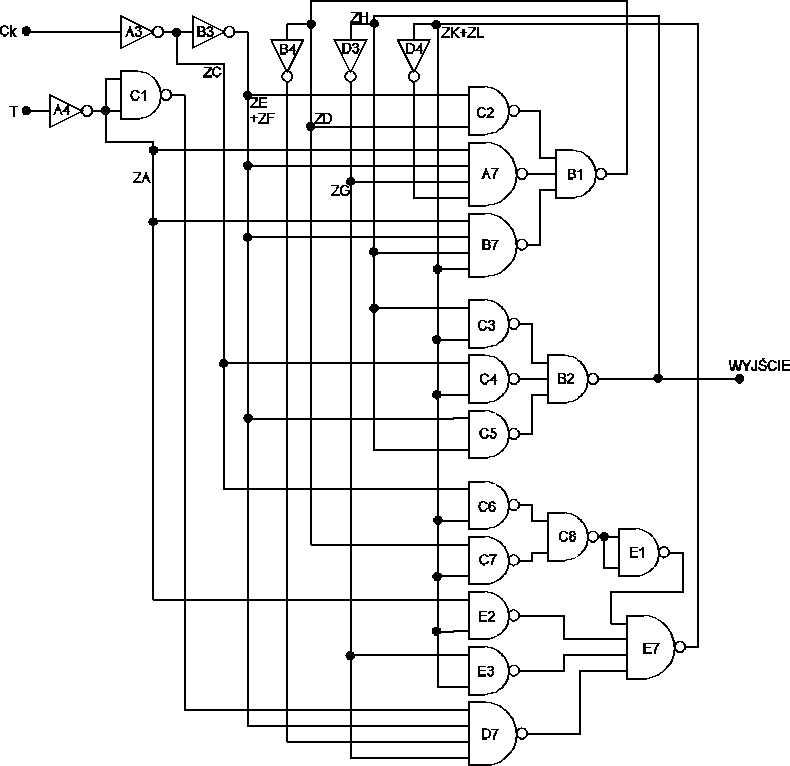

2. Zaprojektować przerzutnik typu T Master-Slave.

Układ ma testować stan wejścia T przy narastającym zboczu sygnału zegarowego i w zależności od tego ma zmienić stan wyjścia na przeciwny przy opadającym zboczu sygnału zegarowego lub nie podejmować żadnej akcji aż do następnego zbocza narastającego. Konieczne jest sześć stanów, tabela przejść wygląda następująco.

Stan |

Reprezentacja |

Wejścia: T - Ck |

Wyjście |

|||

|

|

00 |

01 |

10 |

11 |

|

A |

000 |

A |

B |

A |

C |

0 |

B |

100 |

A |

B |

A |

B |

0 |

C |

001 |

D |

C |

D |

C |

0 |

D |

011 |

D |

E |

D |

F |

1 |

E |

111 |

D |

E |

D |

E |

1 |

F |

010 |

A |

F |

A |

F |

1 |

Przyjęta reprezentacja binarna stanów może się wydawać dość nietypowa, ale wynika ona stąd, że stany te nie są ułożone w jedną pętlę. Pętlę tworzą stany ACDF, natomiast jeśli układ przejdzie np. ze stanu A do B to może tylko wrócić ze stanu B do stanu A. Taka reprezentacja stanów zapewnia, że w każdym przejściu zmienia się stan tylko jednego bitu.

Stany A i D odpowiadają poziomowi niskiemu na wejściu zegarowym, stany B i E są odpowiedzialne za pamiętanie, że wejście T było w stanie niskim przy narastającym zboczu sygnału zegarowego, stany C i F odpowiadają za pamiętanie, że wejście T było w stanie wysokim przy narastającym zboczu sygnału zegarowego. Nie istnieje możliwość zmniejszenia ilości stanów układu.

Każdy bit reprezentujący stan układu jest funkcją pięciu zmiennych wejściowych:

T |

Ck |

Q2 |

Q1 |

Q0 |

Q2' |

Q1' |

Q0' |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

X |

X |

X |

0 |

0 |

1 |

1 |

0 |

X |

X |

X |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

X |

X |

X |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

X |

X |

X |

1 |

0 |

1 |

1 |

0 |

X |

X |

X |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

X |

X |

X |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

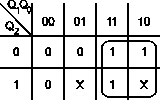

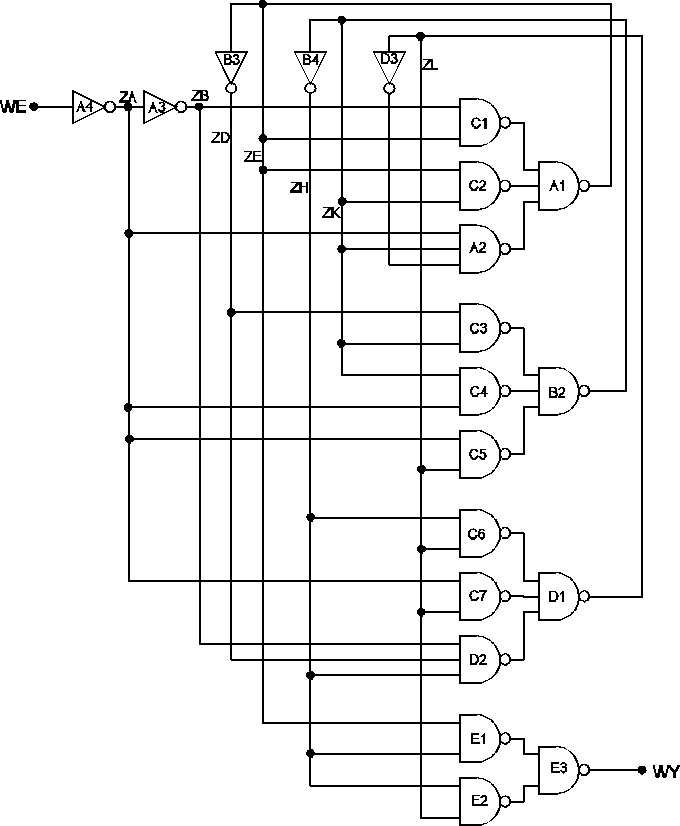

W tabeli tej nie ujęto stanu wyjścia, gdyż jest on funkcją tylko stanów układu, nie zaś stanów wejść, jest to więc funkcja tylko trzech zmiennych. Po zminimalizowaniu wszystkich funkcji otrzymujemy:

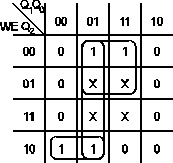

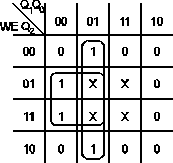

|

|

|

|

Schemat układu został zamieszczony na następnej stronie.

1

5

Wyszukiwarka

Podobne podstrony:

[090121] Alicja Przytomska Pokolenie epoki cyfrowej doc

~$Podstawy techniki cyfrowej doc

Elementy układów cyfrowych doc

Elektronika- Przetworniki cyfrowo-analogowe.DOC, Wydz. E i A Grupa I_

Lustrzanka cyfrowa-czyszczenie matrycy, ZACHOMIKOWANE#, Doc, FOTO, Instrukcja - aparaty fotograficzn

Miernictwo PRZETWORNIK CYFROWO ANALOGOWY DOC

Cyfrowy pomiar czasu DOC

NOTAKI Z TECHNIKI CYFROWEJ

europejski system energetyczny doc

Wykład XI Metody opisu układów cyfrowych

Cyfrowy system rejestracji obrazu

Ortofotomapa cyfrowa i Numeryczny Model Terenu

Dźwięk cyfrowy plik cyfrowy

CYFROWA PRZYSZŁOŚĆ

3 osiowy cyfrowy kompas (magnet Honeywell HMC5883L id 34381 (2)

aparaty cyfrowe praktyczny przewodnik r 14 trudne zdjecia stan sitwe helion 56GBUFHXJXG6NRFSKVYCN

więcej podobnych podstron