1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A

A

B

B

C

C

D

D

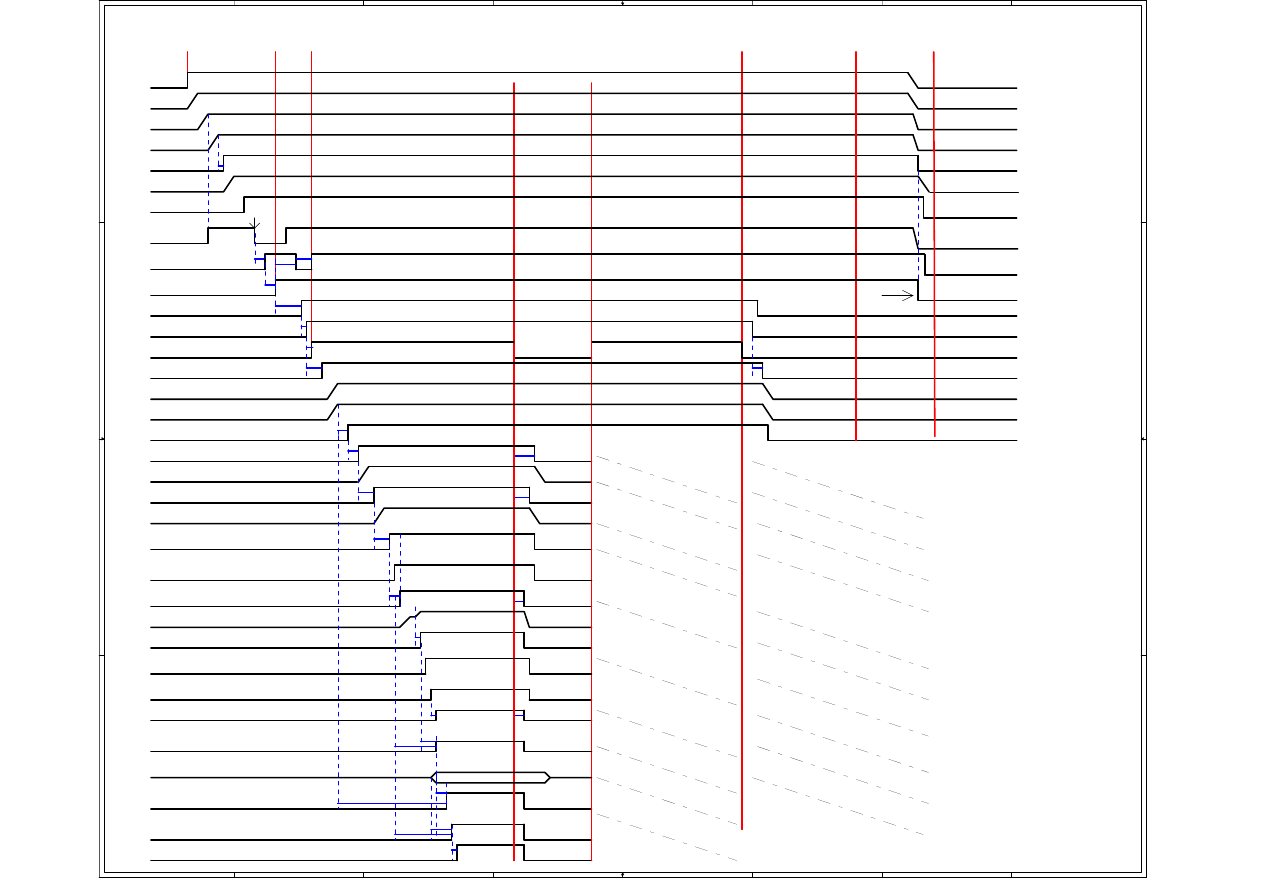

VHCORE

CLK_PWRGD

CLK_CPU_BCLK

IMVP_PWRGD

T24

PM_DRAM_PWRGD

H_CPUPWRGD

PLT_RST#

(From EC to PCH)

(From EC to PCH)

(From PCH to EC)

(From PCH to EC)

(From PCH to EC)

(0V to1.5V ->Max.2ms for DDR3)

(1ms)

(5ms)

(max.110ms)

(Min 30us)

(Min 30us)

(1ms)

(Delay Min 99ms)

(5ms)

( Min 1ms )

(From +1_1V_VTT VR PGOOD to EC)

(From EC to IMVP6)

(1ms)

(1ms)

(5ms)

(From Clock Gen TO CPU)

For battery mode(ACIN_EC inactive):

PM_RSMRST# follow ACIN_EC

& PM_SLP_S5# &PM_SLP_S4#)

(From PCH to CPU)

(From PCH to CPU)

G3

G3 --> S5

S0

T15

(2ms)

T12

T13

T16

S3

(Min. 5 ms)

S0

Te

(~1.8ms)

Td

(~0.3ms)

Repeat Previous

S0 Sequence

DCBATOUT

DC_IN

+ECVCC

ECRST#

ALW_ON

+3VALW/+5VALW

Repeat Previous

S3 Sequence

ALW_PWRGD

Power

Switch

Press

S4/S5

T17

(1ms)

PWRSW#

S5

( Form EC to PCH)

EC[O]

EC[I]

EC[O]

EC[O]

EC[O]

EC[O]

EC[O]

EC[I]

EC[I]

EC[I]

EC[O]

EC[I]

EC[I]

EC[I]

EC[I]

T01

PM_RSMRST#

S4(S5)-->G3

G3

PWRBTN#

DC_IN+

DCBATOUT

+ECVCC

ECRST#

ALW_ON

+3VALW/+5VALW

ALW_PWRGD

PWRSW#

PWRBTN#

PM_RSMRST#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

SUS_ON

+3V_SUS/+5V_SUS

+1_5VSUS/DDRDIMM_VREF(DDR2)

SUS_PWRGD

T03

T02

PM_SLP_S5#

Ta

(700ms)

T8

(5ms)

PM_SLP_S4#

T9

T04

(150ms)

T05

(50ms)

PM_SLP_S3#

SUS_ON

T06

+3VSUS/+5VSUS

+1_5VSUS/DDRDIMM_VREF

SUS_PWRGD

T07

RUN_ON

+3VRUN/+5VRUN

T08

RUN_ON1

PEX_VDD/NV_VDD/+1_05VRUN/+1_5VRUN/+1_1V_VTT/+1_8VRUN/+0_75VRUN

T09

RUN_PWRGD

T16

IMVP_VR_ON

(Form PCH to CPU)

T32

(Min 1ms)

PCH will wait for 4-5 seconds before de-asserting SLP_S5#

T20

( From 3ms to 20ms )

T18

BCLK, SRCCLK, PCICLK

Running

SYS_PWROK/PWROK/MEPWROK/LAN_RST#

VTTPWRGOOD

(TO CPU)

T23

( Min 1ms )

T24

( Min 1ms )

( From 1ms to 100ms )

T26

T21

T22

T25

(From 10 to 100us )

( Min 5ms )

( Min 100ns )

( Min 1ms )

EC[I]

EC[O]

IMVP_OK

Wyszukiwarka

Podobne podstrony:

Power Up Your Traffic

Pulse controlled inverter with variable operating sequence and wind power plant having such an inver

shiba power sequence

JM5B power sequence

prezentacja power media

S up prezentacja 1 dobˇr przekroju

05 DFC 4 1 Sequence and Interation of Key QMS Processes Rev 3 1 03

Power D, zebranie zarządu

karty płatnicze (power point)

elastyczność popytu (power point)

kryptologia w bankowości (power point)

europejski system nagród (power point)

TQM zarządzanie jakością (power point)

V80 Power Management 11May04

Popular Mechanics Repairing Power Antennas

[ebook renewable energy] Home Power Magazine 'Correct Solar Panel Tilt Angle to Sun'

Iron Maiden Power Slave

McMartin LT2000D Power Amplifier

All Flesh Must Be Eaten Two Rotted Thumbs Up

więcej podobnych podstron