Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514, Kraków 1998

15. Projektowanie oprogramowania dla sterowników PLC

Wiele systemów jest sterowanych za pomocą prostych algorytmów tylko poprzez wejścia

binarne (0 - 1). Wyjściami tych systemów też są przeważnie sygnały binarne. Do sterowania takich

układów projektowane są proste układy elektroniczne. Coraz większe zastosowanie znajdują

elektroniczne układy typu ASIC, umożliwiające zaprogramowanie złożonych algorytmów.

Mikrokomputery nazywane sterownikami programowalnymi lub programowalnymi sterownikami

logicznymi PLC (Programmable Logic Controllers) stosowane są do sterowania systemów, dla

których nie istnieje potrzeba archiwizacji i wizualizacji danych.

15.1. Zastosowanie modeli automatowych w projektowaniu systemów cyfrowych

Do

opisu

układów przełączających stosujemy metody algebry Boole’a. Rozpatrzmy funkcję

y= f(x1, x2, ... xn), której argumenty i wartość należą do zbioru { 0, 1}. Funkcje takie nazywamy

funkcjami przełączającymi. Funkcję określoną na zbiorze symboli nazywamy funkcją kombinacyjną.

Funkcje kombinacyjne opisują automat bez pamięci.

Etapy syntezy automatu bez pamięci:

1. Podanie zbioru warunków.

2. Uzupełnienie zmiennych w poszczególnych warunkach.

3. Określenie funkcji przełączających dla poszczególnych warunków.

4. Minimalizacja formalna funkcji.

5. Deminimalizacja techniczna, końcowa postać funkcji.

6. Schemat logiczny struktury.

Przykład 15.1.

W systemie zainstalowane są 3 sygnalizatory dwupołożeniowe. Mamy uzyskać sygnał w dwóch

przypadkach:

1) gdy wszystkie zbiorniki osiągną określony poziom,

2) gdy co najmniej dwa dowolne osiągną określony poziom.

Rozwiązanie:

1. Zbiór warunków

Sygnał wyjściowy ma być ustawiony dla następujących warunków:

abc, ab, ac, bc.

2. Uzupełnienie zmiennych w poszczególnych warunkach:

ab

ab c c

abc abc

ac

a b b c abc abc

ab

a a bc abc abc

⋅ =

+

=

+

⋅ =

+

=

+

⋅ =

+

=

+

1

1

1

(

)

(

)

(

)

3. Określenie funkcji. Zestawiając wszystkie iloczyny przy eliminacji powtarzających się otrzymamy:

y

=

+

+

+

abc abc ab c abc

4. Dokonujemy minimalizację stosując jedną z metod, uzyskamy:

y= ab + ac + bc

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-2

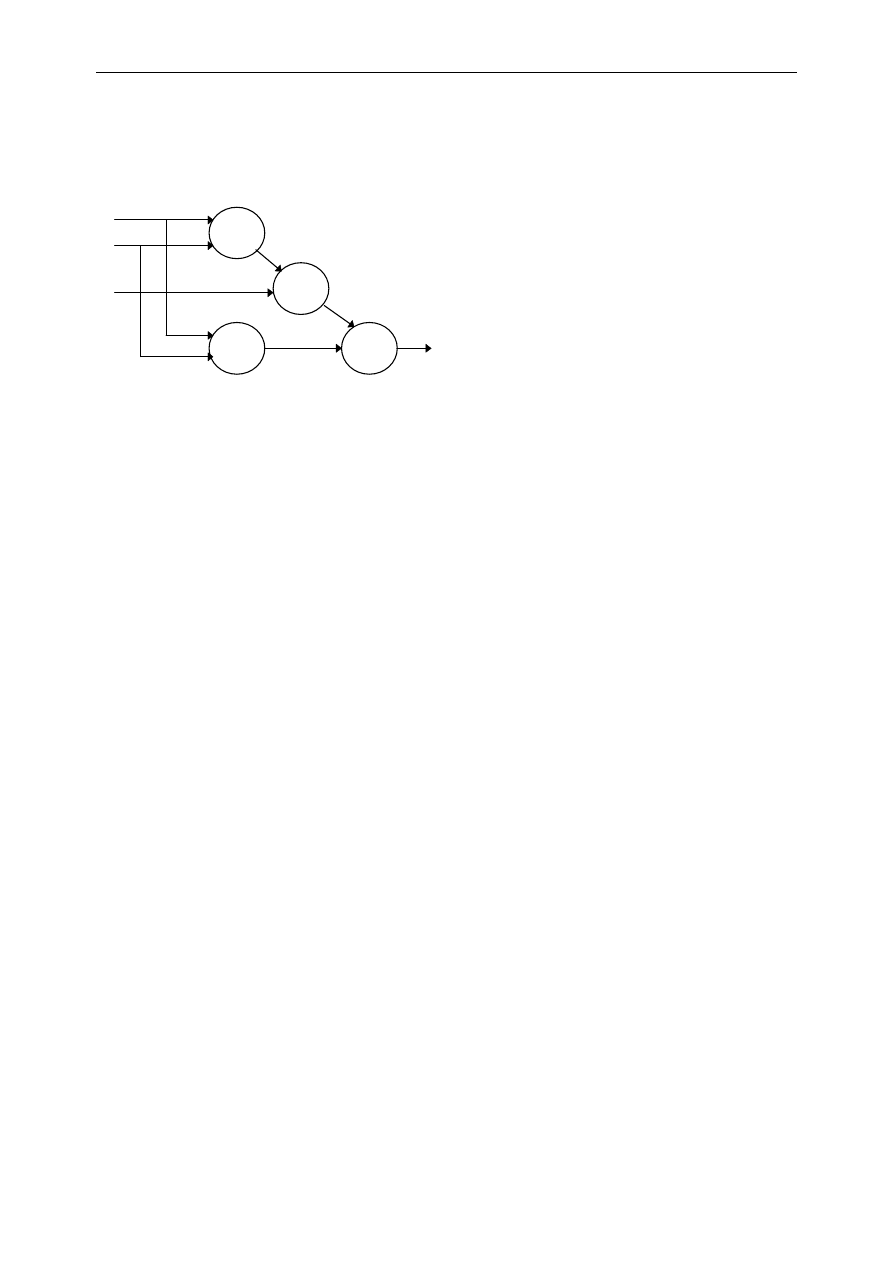

5. Minimalizacja techniczna. Tworzymy taki zapis, by każdy układ sumujący lub mnożący miał dwa

wejścia. Istnieją trzy rozwiązania jednym z nich jest y= c(a+b) +bc.

6. Schemat logiczny układu przedstawia rysunek 15.1.

+

&

+

&

a

b

c

y

Rys. 15.1. Schemat logiczny przykładowego układu

Układy kombinacyjne mają ograniczone możliwości, gdyż wiele układów wymaga

uwzględnienia stanu systemu. Dla takich układów stosuje się automaty z pamięcią.

Rozpowszechnienie znalazły automaty Meale'go i Moore'a.

Automat Meale'go:

S(t+1)=

α

( X(t), S(t) )

Y(t)=

λ

( X(t), S(t) )

Automat Moore'a:

S(t+1)=

α

( X(t), S(t) )

Y(t+1)=

λ

( S(t) )

S jest wektorem stanu automatu, X - wektorem wejść, a Y - wektorem wyjść. Zmiana stanu i wyjść

obu automatów ( wyznaczane są przez funkcje

α

i

β

) dokonywana jest w dyskretnych chwilach

czasu.

Techniki projektowania systemów cyfrowych opisane są w wielu podręcznikach, np. [4].

15.2. Sprzętowa realizacja sterowania logicznego

Istnieją rozwinięte techniki szybkiego wytwarzania układów elektronicznych, realizujących określony

program sformułowany przez użytkownika [4]. Program ten jest odwzorowywany w na pewien

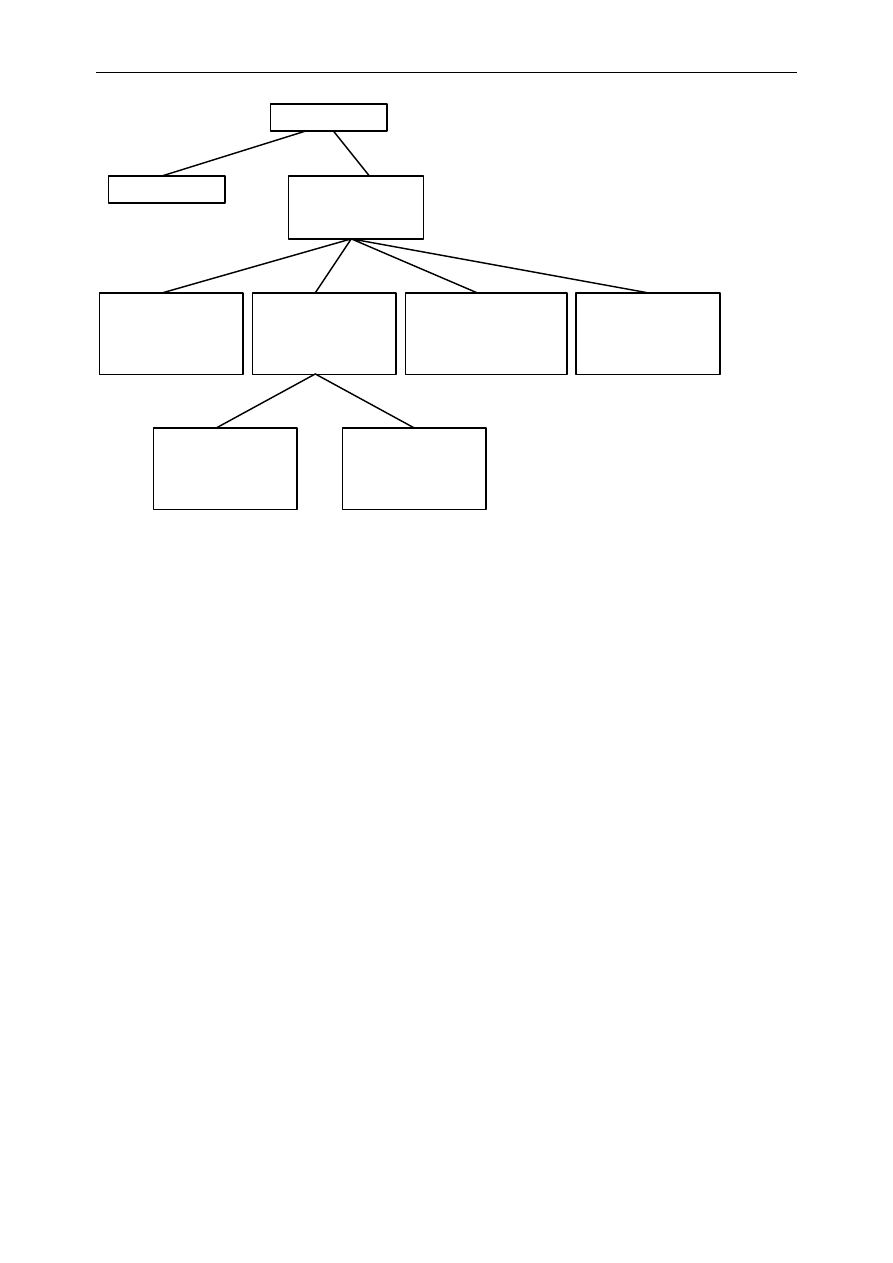

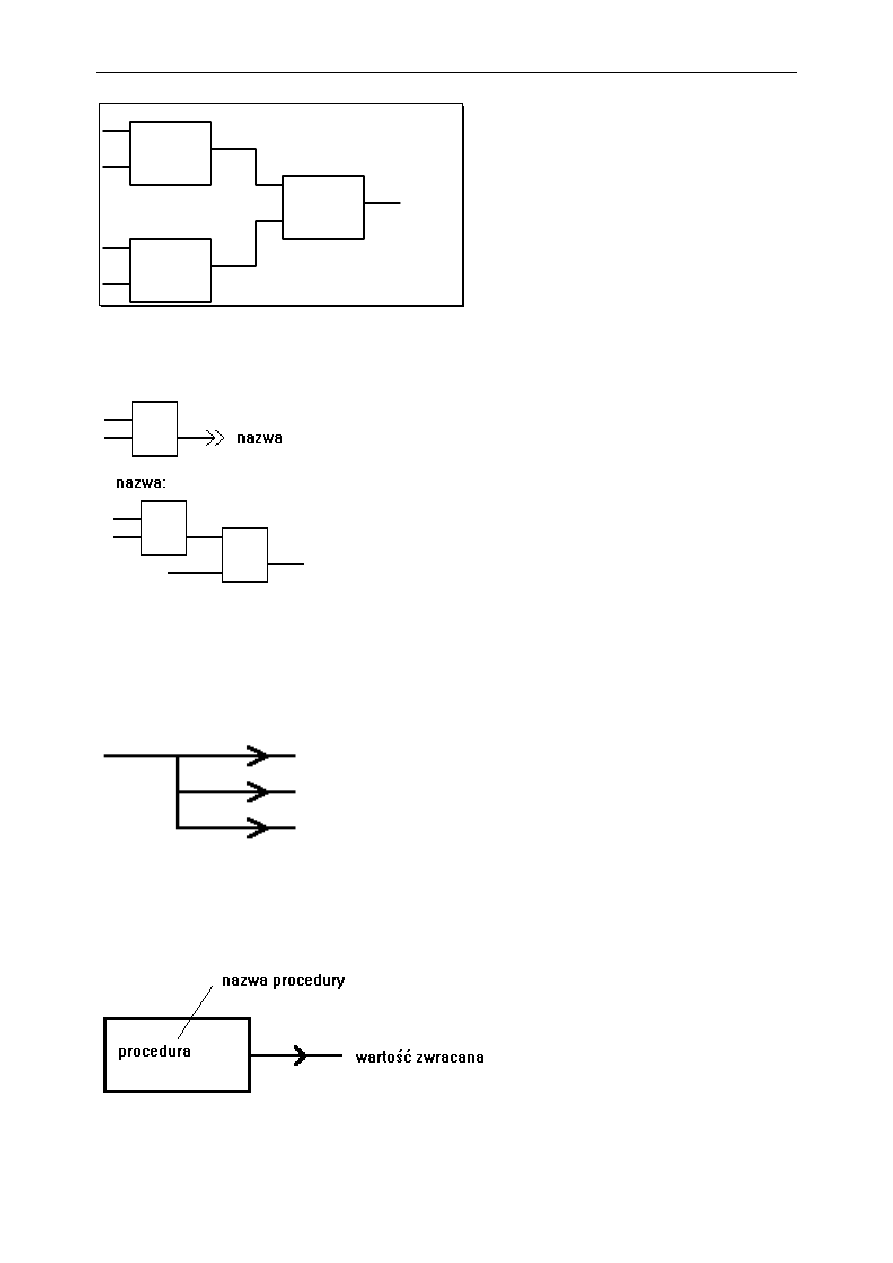

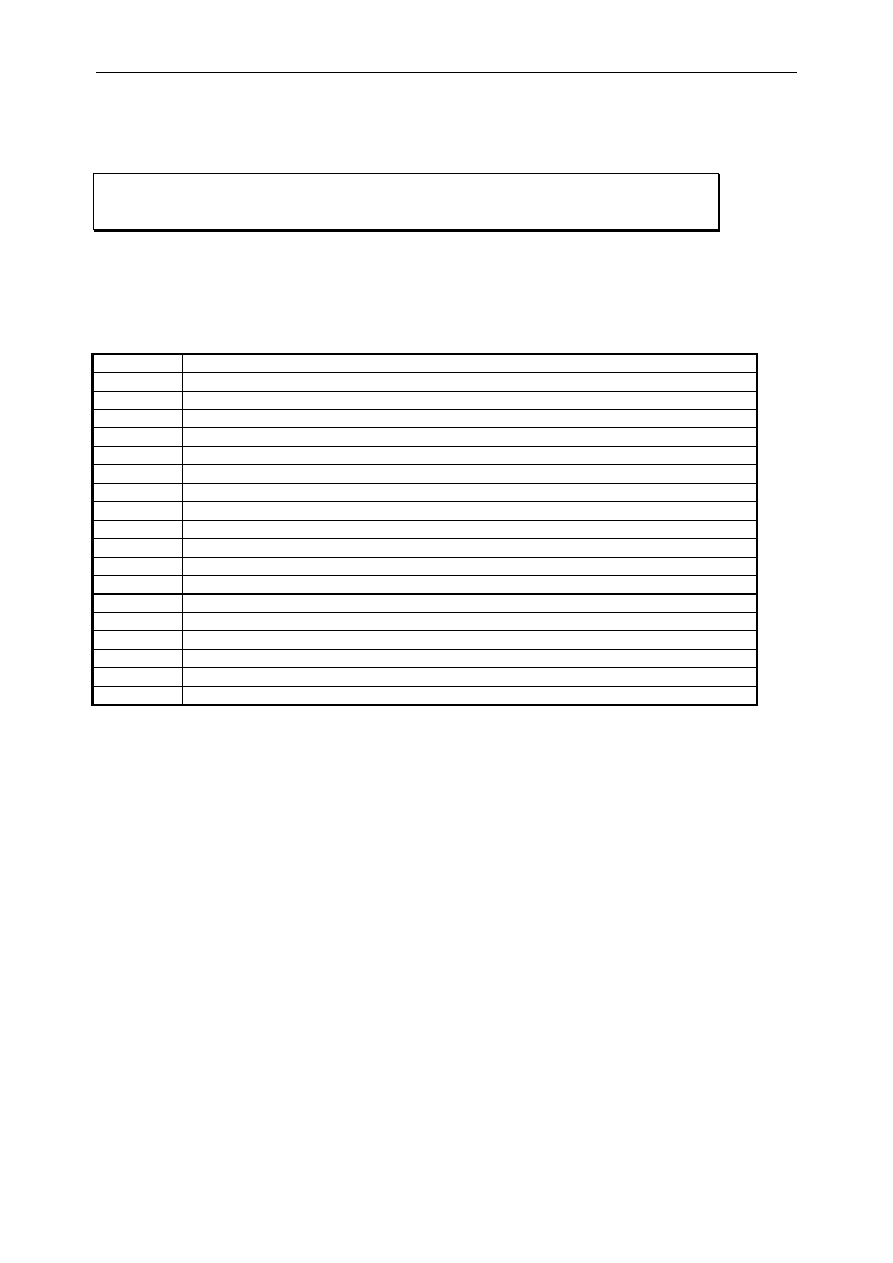

uniwersalny moduł elektroniczny. Przekrój tych układów przedstawia rysunek 15.2.

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-3

Układy scalone

Wielkie standardy

ASIC

Application Specific

Integrated Circuits

Full Custom

Układy na zamówienie

z pełnym cyklem

projektowania

Semi Custom

Układy z

ograniczonym cyklem

projektowania

PLD

Układy programowalne

przez użytkownika

Programmable Logic Devices

FPGA

Field Programmable

Gate Array

Standard Cells

Układy

wykorzystujące

komórki standardowe

Gate Arrays

Układy na płytkach

wstępnie

przygotowanych

Rys. 15.2. Podział układów scalonych

Określenie ASIC (ang. Application Specific Integrated Circuit) stosuje się ogólnie do wszelkich

układów, projektowanych i konstruowanych specjalnie do zastosowania w jakiejś konkretnej aplikacji.

Koncepcja takich układów pojawiła się wraz z rozwojem technologii VLSI, która pozwala

użytkownikom modyfikować (przykroić) powstający projekt układu scalonego odpowiednio do potrzeb.

Złożoność układu ASIC może się mieścić w szerokim zakresie, od prostej logiki interfejsu aż do

pełnego procesora DSP, RISC, sieci neuronowej czy kontrolera z rozmytą logiką.

Technologia ASIC

Osiągnięte postępy w procesie wytwarzania układów wielkiej skali integracji umożliwiły opracowanie

dwóch zasadniczych technologii ASIC, a mianowacie CMOS i BiCMOS, w których osiągnięto

szerokość ścieżki 0.5

µ

m. W procesie CMOS można wytwarzać układy ASIC zawierające 250000

bramek lub więcej (generalnie bramkę określa się jako pojedynczą bramkę NAND). Z drugiej strony

tablice bramek BiCMOS (zawierające układy bipolarne i CMOS) umożliwiają większą szybkość

działania kosztem bardziej złożonego procesu wytwarzania i mniejszej gęstości upakowania.

Układy ASIC w technologii CMOS są oferowane w postaci macierzy standardowych komórek i

bramek. Wraz ze standardowymi komórkami rdzenie procesorów mogą być łączone z rozmaitymi

blokami pamięci i modułami logicznymi, zapewniając wielką elastyczność. Jednak koszt wytworzenia

prototypu jest znacznie wyższy. Z drugiej strony na macierzach bramek można również projektować

bloki pamięciowe i logiczne. Układ ASIC w technologii CMOS 0.8

µ

m może zawierać do 250000

bramek. W technologii CMOS 0.5

µ

m możliwe jest upakowanie do 600000 użytecznych bramek na

jednej strukturze.

Układ ASIC w technologii BiCMOS zawiera zarówno tranzystory CMOS jak i tranzystory

bipolarne wykorzystując technologię "sea of gates". Robocza częstotliwość przyrządów BiCMOS jest

stosunkowo wysoka (100 MHz) ze względu na (drive) pojemność tranzystorów bipolarnych. Jednak

gęstość upakowania jest mniejsza, przykładowo BiCMOS ASIC może zawierać tylko do 150000

bramek. W technologii BiCMOS 0.5

µ

m można otrzymać układ scalony, zawierający do 300000

użytecznych bramek.

Cyfrowo-analogowe

układy ASIC (mixed-signal ASIC) zawierają na tej samej strukturze

zarówno elementy analogowe, jak i cyfrowe, i są ostatnio oferowane przez kilku producentów. Układy

takie dają większe możliwości połączenia w całość złożonego systemu. Te utworzone na poziomie

struktury układu scalonego systemy mogą realizować mieszane zadania analogowo - cyfrowe, które

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-4

przedtem mogły być realizowane dopiero na poziomie płytek drukowanych. Elementy analogowe

obejmują wzmacniacze operacyjne, komparatory, przetworniki A/C i C/A, wzmacniacze próbkujące

(sample-and-hold), wzorce napięcia oraz aktywne filtry RC. Elementy logiczne obejmują bramki,

liczniki, rejestry, mikrosekwentery, programowalne macierze logiczne PLA, pamięci RAM i ROM.

Elementy pośredniczące obejmują 8-mio i 16-to bitowe, równoległe porty wejścia/wyjścia oraz

synchroniczne porty szeregowe i układy UART.

Rdzenie RISC i DSP są oferowane przez kilku wytwórców i pozwalają projektować

zindywidualizowane, zaawansowane procesory według metodologii ASIC. Na pojedynczym układzie

scalonym użytkownik może składać jak z klocków kompletne moduły z rdzeni procesorów DSP, RISC,

pamięci oraz modułów logicznych, korzystając z narzędzi CAD. Przykładowo Texas Instruments

oferuje rdzenie DSP w układach rodzin C1x, C2x, C3x i C5x w postaci elementów ASIC. Każdy rdzeń

zaopatrzony jest w schemat, symulacyjny wykres czasowy, schematy rozmieszczenia elementów na

strukturze, oraz w zbiór przebiegów testowych.

Projektowanie układów ASIC

Proces projektowania układu ASIC składa się z trzech zasadniczych etapów:

a) projektu logicznego i symulacji,

b) rozmieszczenia elementów, poprowadzenia i sprawdzenia połączeń, oraz

c) opracowania maski rozkładu i wyprodukowanie prototypu.

Końcowy użytkownik może włączyć się do procesu projektowania wg. różnych schematów,

zwanych "semistandard", „semicustom" oraz "full-custom", zależnie od wymagań konkretnego

zastosowania. W schemacie "semistandard" użytkownik przekazuje swoje propozycje projektowe

producentowi ASIC. Producent modyfikuje projekt układu scalonego zgodnie z przyjętymi

uzgodnieniami.

15.3. Sterowniki programowalne - PLC

W systemach sterowania stosowany jest różny sprzęt komputerowy. Zwykle najniższy poziom struktury

sterowania bazuje na sterownikach programowalnych. W krajach wysoko uprzemysłowionych

programowalne sterowniki logiczne PLC (Programmable Logic Controllers) są podstawowym środkiem

sterowania i automatyzacji wszelkiego typu maszyn i urządzeń technologicznych o binarnej strukturze

funkcjonowania, takich jak obrabiarki, prasy, wtryskarki tworzyw sztucznych, linie zgrzewania,

urządzenia do transportu technologicznego, urządzenia malarskie i galwanizerskie, urządzenia

mieszająco-dozujące, sortujące, ważące itp. Stosuje się je także do automatyzacji całych procesów

technologicznych w hutnictwie, energetyce, przemyśle spożywczym, chemicznym, materiałów

budowlanych itp.

Rozwój systemów programowalnych sterowników logicznych rozpoczął się na początku lat

siedemdziesiątych i trwa do dziś. Na świecie istnieje ponad 100 liczących się firm produkujących kilkaset

modeli sterowników PLC. Największe znaczenie w produkcji i zastosowaniu mają USA, Niemcy, Japonia

i Francja. Większość firm produkuje sterowniki we wszystkich klasach wielkości, z bogatym

wyposażeniem wspomagającym programowanie, testowanie i uruchamianie systemów. Istotnym

zagadnieniem jest szybkie uzyskiwanie prawidłowo działających programów.

Sterowniki

spełniają szereg dodatkowych wymagań, których nie spełniają komputery biurowe.

Obostrzone wymagania dotyczą zakresu temperatury pracy, wilgotności, odporności na drgania i

wstrząsy, zapylenie, itp.

Zasada działania sterowników programowalnych

Programowalne sterowniki logiczne, najogólniej definiując, mają strukturę komputerów uniwersalnych,

lecz zorientowane są na procesy sterowania logicznego. Wynikają stąd dwie podstawowe ich

właściwości: programowanie zadań odbywa się z wykorzystaniem specjalnych języków zorientowanych

na zapis funkcji logicznych, a ich budowa jest dostosowana do bezpośredniego połączenia ze

sterowanym obiektem. Wykonywanie programu sterowania polega na szeregowo-cyklicznym

przetwarzaniu rozkazów programu. Kolejne rozkazy są wykonywane szeregowo jeden po drugim, a po

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-5

wykonaniu wszystkich cykl jest powtarzany, niezależnie od przebiegu sterowanego procesu

technologicznego. Cykl powtarzania programu jest na tyle szybki, że sterowany obiekt reaguje na

związki logiczne pomiędzy jego wejściami a wyjściami, wynikające z algorytmu jego pracy, tak jakby były

one realizowane równolegle w czasie rzeczywistym.

Bloki

układów wejścia/wyjścia służą do elektrycznego dopasowania sygnałów dwustanowych,

pochodzących ze sterowanego obiektu i wysyłanych przez sterownik do obiektu sterowanego. Bloki te

realizują również separację galwaniczną sterownika od obiektu sterowanego, zmniejszając zagrożenie

przed uszkodzeniem i przed zakłóceniami elektrycznymi systemu sterowania. Układy wejścia/wyjścia

umożliwiają bezpośrednie podłączenie sterownika do obiektu sterowanego.

Parametry sterowników programowalnych

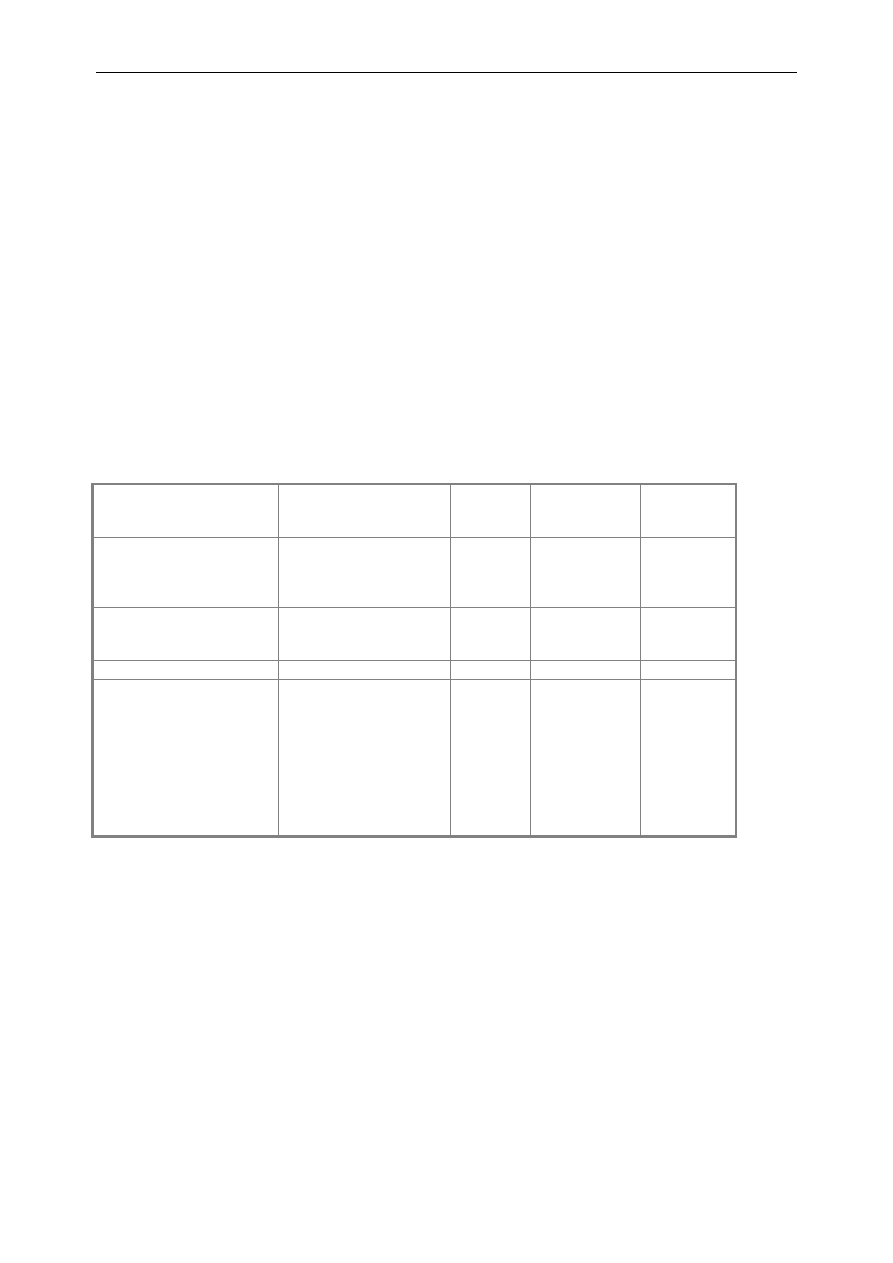

W tabeli 15.1. zawarto charakterystyczne parametry [3] niektórych producentów sterowników

programowalnych. Jedną z charakterystycznych cech sterowników jest liczba wejść i wyjść cyfrowych. W

większości zastosowań wystarcza niewielka liczba takich wejść i wyjść. Ponieważ program typowego

sterownika polega na cyklicznym wykonaniu tego samego ciągu instrukcji, dlatego szybkość sterownika

programowalnego określana jest przez czas wykonania tysiąca instrukcji. Proste programy sterownika

nie zajmują zbyt dużo miejsca w pamięci, dlatego typowe sterowniki wyposażane są w mniejszą pamięć

RAM niż komputery osobiste.

Tab. 15.1. Podstawowe parametry wybranych sterowników PLC

Firma

Typ

I/O

Szybkość

czas dla 1000

instrukcji

RAM

Allen-Bradley

Micrologix 1000

SLC 500

PLC-5

PLC-5/250

16-32

20-960

128-3072

do 4.1K

do 2ms

0.5-8ms

<1ms

<1ms

do 1Kb

1K-24Kb

8K-100Kb

do 8Mb

GE Fanuc Automation

90 Micro

Seria 90-30

Seria 90-70

14

1K

12K

1ms

0.18ms

0.4ms

6Kb

80Kb

512Kb

PEP Modular Computers Smart I/O

8-88

3Mb

Siemens

Simatic S5-90U

Simatic S5-95U

Simatic S5-100U

Simatic S5-115U

Simatic S5-135U/155U

Simatic TI500/TI505

Simatic S7-200

Simatic S7-300

Simatic S7-400

14-208

32-480

do 448

do 2K

32.8K

8.2K

64

1024

128K

2ms

2ms

0.8ms

0.1ms

0.18ms

0.06ms

0.8ms

0.3ms

0.08ms

4Kb

20Kb

20Kb

384Kb

1664Kb

1920Kb

4Kb

48Kb

512Kb

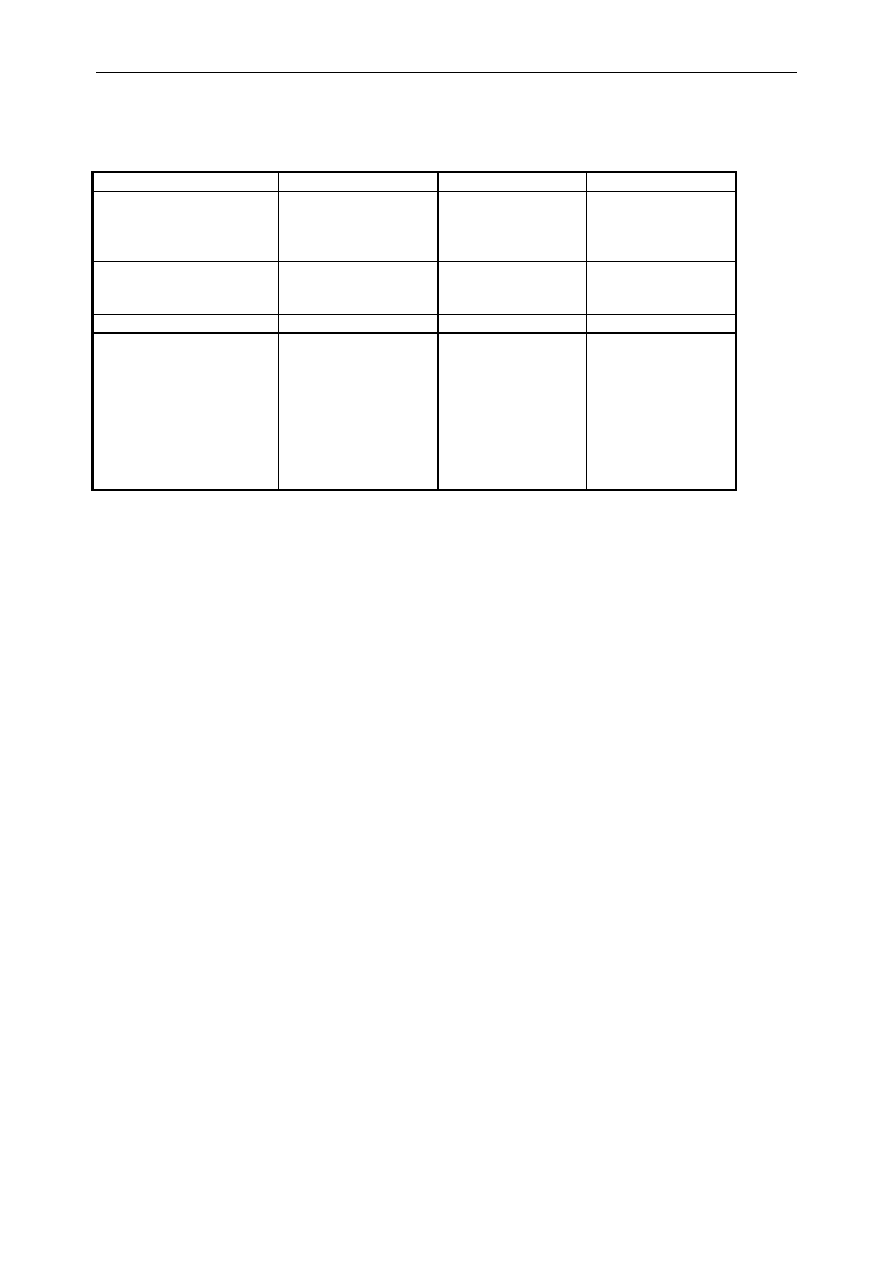

Sterowniki

mogą być przeznaczone nie tylko do wykonywania prostych operacji. Tabela 15.2

podaje różne rodzaje operacji, które mogą być realizowane przez sterowniki: r - zadania czasu

rzeczywistego, m - wielozadaniowość, II - moduły do obliczeń równoległych, f - obliczenia

zmiennoprzecinkowe, pid - sterowanie typu PID, fz - logika fuzzy.

Programowanie sterowników nie musi być realizowane na poziomie bliskim maszynie. Świadczy

o tym coraz bogatsze oprogramowanie oferowane dla sterowników programowalnych. W tab. 15.2

podawane są następujące typy oprogramowania: tr - pakiety treningowe, pc - oprogramowanie

komputerów osobistych (PC), iec- zgodność z IEC1131 dla wszystkich wariantów, f - bloki funkcyjne, i -

schematy drabinkowe, l - lista instrukcji, s - schematy przebiegu sekwencji instrukcji, h - programator

przenośny.

Coraz

większe wymagania związane są integracją sterownika z otoczeniem. Sterowniki

wyposażone są w różne sprzęgi umożliwiające transmisję danych. W tabeli 15.2 podano typy łączy

komunikacyjnych: e - Ethernet i jego odmiany, a - ARCnet, f -FIP, c - CAN, p-Profibus, l - LONWorks, m -

Modbus, m+ - Modbus+, s - Interbus-S, d - DeviceNet, as - ASInet, fo - światłowody (fibre optics), r - fale

radiowe.

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-6

Stosowane

są rozwiązania bazujące na języku naturalnym, przykładem może być narzędzie

CASE firmy Siemens o nazwie APT, którego celem jest zapewnienie prostoty programowania

sterowników.

Typ Operacje

Programowanie

Transmisja

Micrologix 1000

SLC 500

PLC-5

PLC-5/250

r

r,f,pid

r,f,pid,dmr

r,m,II,f,pid,dmr

pc, l, h

tr,pc,l,s,h

tr,pc,l,i,s,h

pc,l,s

m,d,fo,r

e,p,m,f,fo,r

e,m,d,fo,r

90 Micro

Seria 90-30

Seria 90-70

r,pid

r,pid,II

r,m,II,f,fz,pid,d/tmr

tr,pc,iec,l,i,h

tr,pc,iec,l,i,s,h

tr,pc,iec,l,s

m

e,f,c,m,d,s,d,r

e,f,p,m,s,d,sd,fo,r

Smart I/O

r,m

tr,pc,iec

p,m,d

Simatic S5-90U

Simatic S5-95U

Simatic S5-100U

Simatic S5-115U

Simatic S5-135U/155U

Simatic TI500/TI505

Simatic S7-200

Simatic S7-300

Simatic S7-400

r

r,fz

r,fz

r,f,pid,d,fz

r,f,II,pid,d,fz

r,f,pid,d

r

r,f,pid,fz

r,II,f,pid,fz

tr,pc,f,l,i,s,h

pc,f,l,i,s,h

pc,f,l,i,s,h

p,c,f,l,i,s,h

pc’C’,f,l,i,s,h

pc,l,i,APT

tr,pc,iec,l,i

tr,pc,iec,f,l,i,s

pc,iec,fl,is

as,m

p,m,as

as,m

e,p,m,m+,as,fo

e,p,m,m+,as,fo

a,p,m,m+,as,fo

RS485,ascii

p,as,fo,m+,RS485

e,p,as,fo,m,RS485

Tab. 15.2. Parametry wybranych sterowników PLC

Metody programowania sterowników

Dla języków programowania sterowników PLC opracowano standardy IEC (International

Electrotecnical Comission). Istnieje pięć podstawowych metod konstrukcji oprogramowania

sterowników w standardzie IEC 1131-3. Przykładem takiego zaawansowanego systemu jest pakiet

ISaGRAF, który uruchamiany jest pod Windows, natomiast aplikacje programowe uruchamiane są

na rodzinie sterowników PLC typu PEP 9000 w środowisku systemu operacyjnego czasu

rzeczywistego OS9. Funkcje pakietu są dostępne w dwóch trybach pracy, normalnym służącym do

konstruowania programu oraz drugim, służącym do kontroli działania programu. Program posiada

procedury testujące oraz możliwości podglądu wykonania programu w trybie symulacyjnym i na

systemie docelowym.

ISaGRAPH posiada pięć języków programowania zgodnych ze standardem IEC 1131-3, z których

można korzystać na raz w jednym programie. Są to:

- sekwencyjne schematy funkcyjne (SFC - Sequential Function Chart),

- bloki funkcyjne (FBD - Function Block Diagramm ),

- schematy drabinkowe (LD - Ladder Diagram ),

- lista instrukcji (IL - Instruction List),

- tekst strukturalny (ST - Structured Text ).

15.4. ISaGRAF Środowisko programowe sterowników

15.4.1. Opis własności środowiska ISaGRAF

ISaGRAF WDS jest bazującym na Windows, zintegrowanym środowiskiem programowym CASE

(Computer Aided Software Engineering) [1, 2, 5]. Cechuje go zgodność z IEC1131-3, nowym

międzynarodowym standardem językowym PLC. Aplikacje programowe uruchamiane są na rodzinie

kontrolerów PEP 9000 pod środowiskiem czasu rzeczywistego OS-9/68K. ISaGRAF WDS jest osadzony

w środowisku OS-9 jako w systemie nośnym. Wykonanie programu odbywa się przez wczytanie wejść,

wykonanie kodu oraz ustawienie wyjść. Po każdym takim cyklu wykonywane są inne zadania należące

do OS-9. Pod systemem RTOS-9 ISaGRAF kernel (ISaKER) jest wykonywany równolegle z innymi

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-7

zadaniami komunikacyjnymi (ISATST). Struktura ta umożliwia klientowi uruchomić więcej niż jedną

aplikację ISaGRAFu oraz swoje własne zadanie OS-9 w tle.

Oprogramowanie posiada procedury testujące, funkcje symulacyjne i podglądu wykonania

zadania w systemie docelowym. Podgląd w programie umożliwiają te same okna, które służą do edycji

ale ze statusem procesu. Funkcje programu są dostępne w dwóch trybach pracy: normalnym, służącym

do konstruowania projektu i symulacyjnym, służącym do kontroli działania programu.

W trybie normalnym można wyróżnić składowe:

• edytory graficzne dla języków: schemat sekwencji funkcji (SFC - Sequential Function Chart),

schemat bloku funkcji (FBD - Function Block Diagram), schemat drabinkowy (LD - Ladder Diagram);

• edytory tekstowe dla języków: lista instrukcji (IL - Instruction List), tekst strukturalny (ST - Structured

Text), kodu C (opcjonalny);

• dodatkowe edytory dla deklaracji zmiennych, definicji, konfiguracji wejścia/wyjścia.

• zarządzanie projektem;

• zarządzanie bibliotekami: kart wejścia/wyjścia, procedur użytkownika w C, konwersji funkcji;

• zarządzaniem archiwizacją projektów i bibliotek;

• informacja (help).

W

oknie

środowiska, ISaGRAF Projects Management, podawany jest wykaz dostępnych

programów użytkownika. Wybieramy jeden z nich lub tworzymy nowy. Ukazuje się ISaGRAF Project, w

którym przedstawiony jest układ programu. W oknie podane są opcje służące do:

• wprowadzania poszczególnych elementów językowych lub segmentów w zależności od potrzeb

użytkownika,

• definiowania zmiennych binarnych, analogowych, czasowych oraz komunikatowych, ich adresów i

możliwych stanów,

• ustawiania list zmiennych, szczególnie przydatnych w dużych projektach,

• tablic konwersji zmiennych,

• ustawiania konfiguracji kart podpiętych do programowanego urządzenia,

• weryfikacji poprawności programu,

• kompilacji do postaci wykonywalnych,

• symulacji programu.

Jeżeli program został napisany zgodnie z zasadami programowania w dostępnych językach,

przeprowadzana jest weryfikacja i kompilacja programu. Po uruchamieniu symulacji ukazuje się okno

Debuggera oraz okno Kernela przedstawiające stan wejść/wyjść, które można dowolnie zmieniać.

Możliwe jest również otwarcie okien dowolnych zmiennych zarówno lokalnych jak i globalnych, a także

można stale obserwować dowolną zmienną, jak również nadawać jej żądane wartości. Możemy ponadto

obserwować przebieg procesu w edytorach poszczególnych języków. W tym przypadku nie jest możliwa

żadna zmiana wewnątrz struktury programu. Mając do dyspozycji sterownik możemy załadować

program, dokonując wcześniej połączenia za pośrednictwem opcji Debug. Okno dialogowe informuje o

trybie pracy i aktualnej aplikacji znajdującej się w sterowniku. Przed załadowaniem nowej aplikacji,

należy zatrzymać wykonanie aplikacji poprzednio załadowanej. Po umieszczeniu nowego programu za

pomocą opcji Download podawany jest komunikat o aktywności aplikacji i status pracy RUN. W czasie

pracy można obserwować wartości zmiennych lub uruchomić przygotowaną wcześniej wizualizację

procesu.

15.4.2. Symulacja wykonania aplikacji

Symulator kernela umożliwia symulację pracy sterownika. Karty wejścia/wyjścia są graficznie

uwidocznione w oknie systemu Windows. W tym przypadku karty wejścia/wyjścia definiowane są jako

karty wirtualne (virtual board). Oprócz okna zmiennych wirtualnych wejść/wyjść możliwy jest też podgląd

wszystkich zmiennych wewnętrznych lokalnych i globalnych za pośrednictwem okien: zmiennych

binarnych, zmiennych analogowych, zmiennych czasowych, komunikatów, bloków funkcyjnych.

Symulator kernela zawsze pracuje z aktualną aplikacją. Ważne jest, aby przed użyciem symulatora

wybrać opcję przygotuj program do symulacji (prepare code for simulation).

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-8

Symulator pracy sterownika znacznie ułatwia sprawdzenie poprawności działania programu

użytkownika. Wygodna, graficzna obsługa wejść/wyjść daje możliwość przetestowania wszelkich

możliwych sytuacji stanu systemu, co jest utrudnione na urządzeniach rzeczywistych.

Wizualizacja graficzna tworzona przez użytkownika za pomocą opcji "Graphics" umożliwia

przedstawienie projektu w sposób obrazowy i przejrzysty. Użytkownik ma do wyboru następujące

elementy tworzące kompletny obraz:

• tło rysunkowe - stworzony np. pod PaintBrusch plik formatu BMP pomaga we wzrokowym

usytuowaniu i przejrzystości zastosowanych elementów,

• binarna ikona graficzna - obrazuje stany logiczne prawdy i fałszu. Stosuje się do tego celu

standardowe ikony systemu Windows,

• pole graficzne - element w kształcie prostokąta, wypełniany dowolnym kolorem w dowolnym kierunku.

Obrazuje stopień wypełnienia lub wykorzystania zmiennej w deklarowanych granicach,

• pole numeryczne - zmienna jest przedstawiana za pomocą cyfr dziesiętnych.

Tablice

konwersji

stanowią wygodny dla użytkownika blok służący, do przeliczania poziomu

sygnałów elektrycznych (przychodzących z karty zewnętrznej) na wielkości fizyczne. W zależności od

ilości punktów charakterystycznych, zostają automatycznie stworzone wykresy funkcji zależności.

Blok kontroli aplikacji stanowi rozbudowaną częścią programu, służącą do pełnej kontroli

aplikacji uruchomionej na urządzeniu wykonawczym. Do dyspozycji mamy te same okna, które służą do

projektowania, jednak bez możliwości zmian. Umożliwia to pełny podgląd: zmiennych wszystkich

dostępnych typów, wykonania programu w dowolnej jego części w dowolnym języku, stanu wejść/wyjść

poszczególnych modułów. Celem tego bloku jest zarządzanie aplikacją, polegające na: załadowaniu

kodu programu na urządzenie, jego uruchomienie bądź zatrzymanie, śledzenie wykonania krok po

kroku, zmianę czasu wykonania pętli programowej i pełną komunikację błędów. Zamknięcie tego okna

powoduje zakończenie śledzenia wykonywanego programu.

Biblioteki

zawierają sterowniki poszczególnych modułów, umożliwiające poprawne ich

wykorzystanie, deklaruje się je potem w czasie łączenia poszczególnych wejść/wyjść. Oprócz tego

zawierają elementy napisane w języku C: procedury - funkcje C, bloki funkcyjne, funkcje konwersji.

Archiwizacja

dokonywana jest przy użyciu programu Archive, który umożliwia pakowanie i

archiwizacje projektów, sterowników modułów, funkcji, bloków języka C.

15.5. Opis języków programowania systemu ISaGRAF

Cały program użytkownika jest podzielony na trzy główne segmenty:

- BEGIN program wykonywany na początku każdego cyklu, służy do obsługi zmiennych wejściowych;

- SEQUENTIAL program wykonywany według kodu języka SFC, używany do opisu właściwej części

programu;

- END program wykonywany na końcu każdego cyklu, służy do obsługi zmiennych wyjściowych.

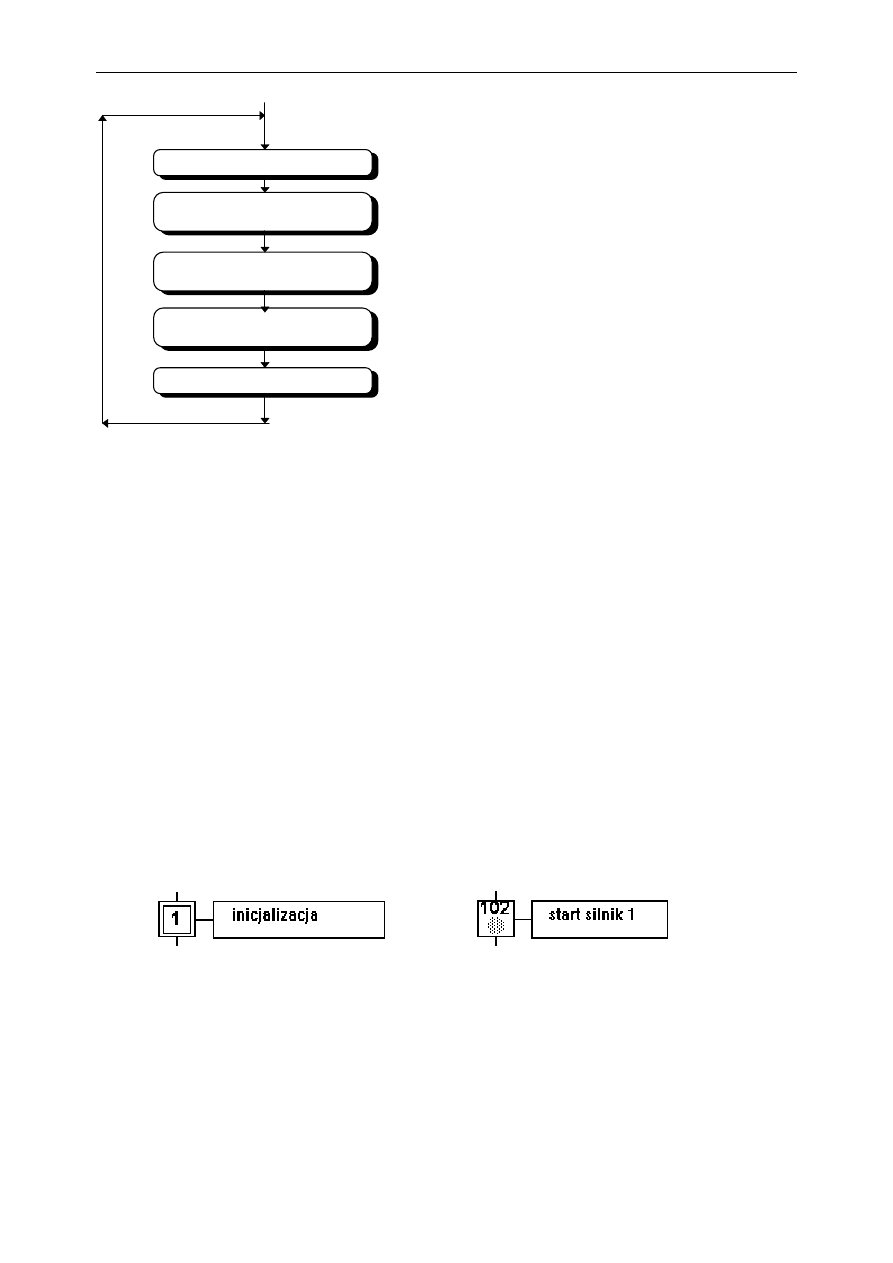

Cykl wykonania instrukcji sterownika programowalnego przedstawia rysunek 15.3.

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-9

Pobierz dane wejściowe

Przetwarzaj sekcję BEGIN

programu

Przetwarzaj sekcję

sekwencyjną programu

Przetwarzaj sekcję END

programu

Wyprowadź dane wyjściowe

Rys. 15.3. Zasada cyklicznego wykonywania programu PLC

Program główny oraz akcje zawarte w sekcji sekwencyjnej muszą być przedstawione w SFC. Natomiast

procedury mogą być pisane przy pomocy innych dostępnych języków. Również w samym edytorze SFC

znajdują się okna pokrewne z innymi językami programowania. Możliwa jest też współpraca z

procedurami napisanymi w języku C.

15.5.1. Sekwencyjne schematy funkcyjne

Sekwencyjne schematy funkcyjne SFC (Sequential Function Chart) tworzą język graficzny, służący do

opisu operacji wykonywanych sekwencyjnie. Proces jest reprezentowany przez definiowane bloki,

łączone również definiowalnymi przejściami. Definicja bloków może być dokonana przez użycie

pozostałych języków (ST, IL, LD, FDB), natomiast przejście musi zawierać warunek logiczny.

Składowe języka:

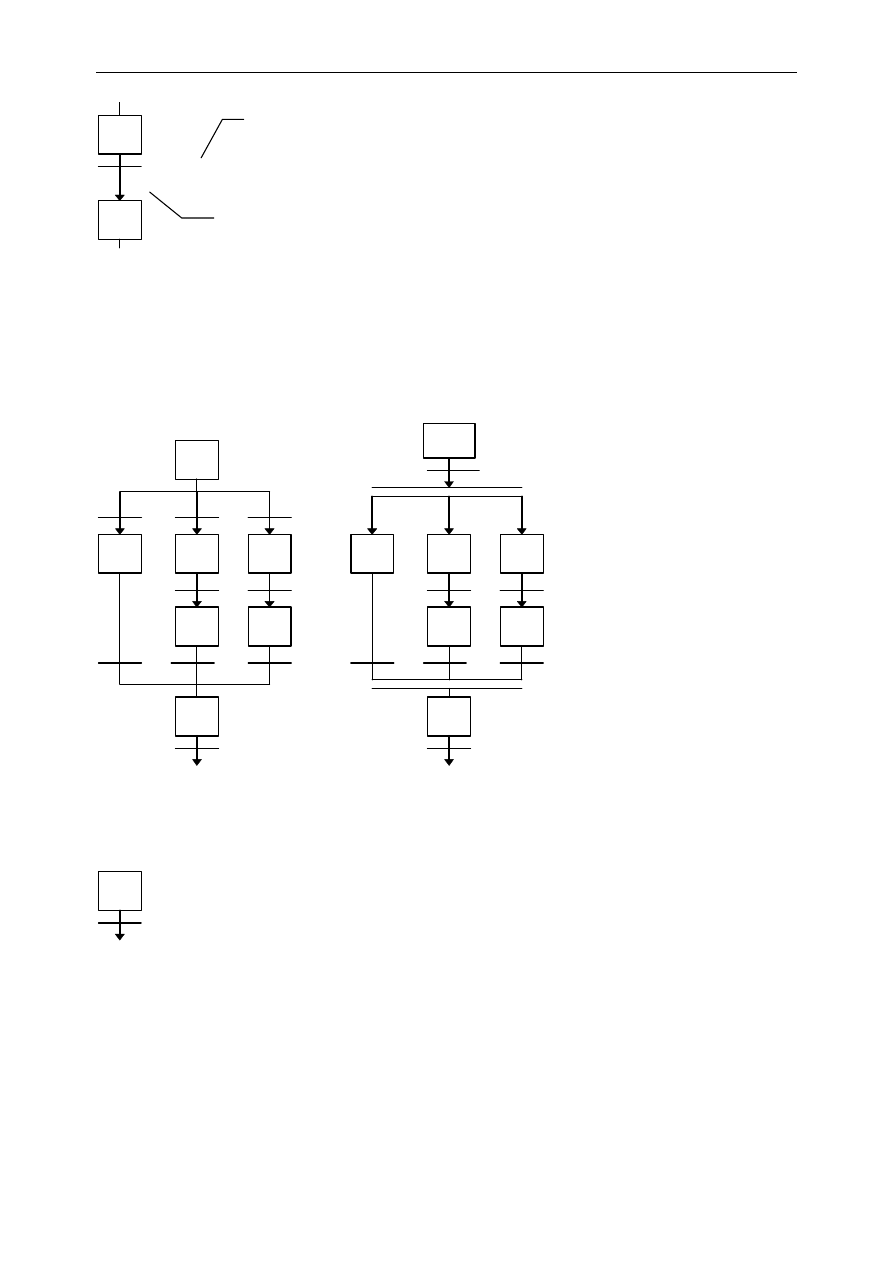

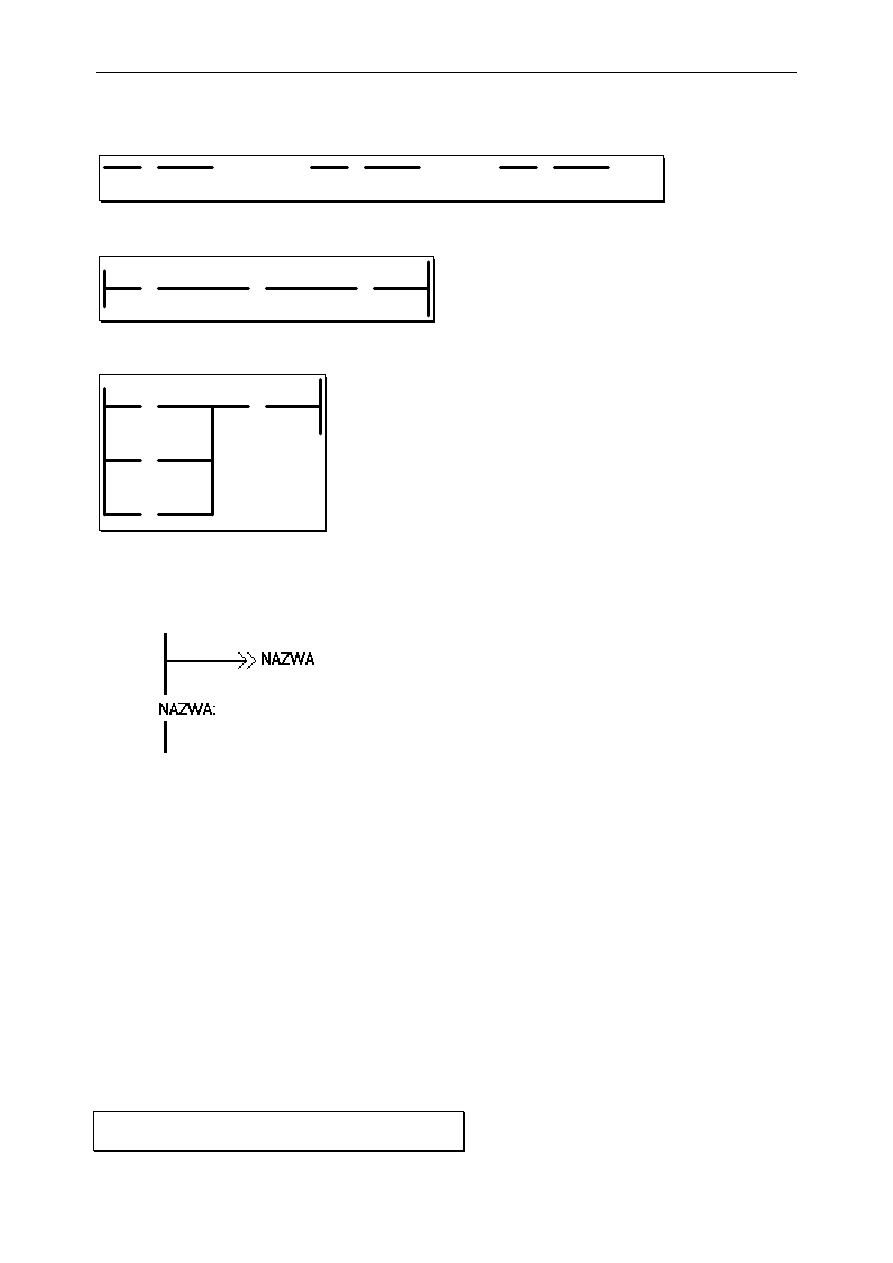

Bloki i bloki inicjalizacyjne - reprezentowane są jako pojedyncze prostokąty (rys. 15.4). Każdy blok jest

oznaczony numerem automatycznie nadawanym przez program lub definiowanym przez użytkownika.

Oprócz numeru blok może mieć nadany identyfikator znakowy - krótki opis, nie będący kodem

programu. Aktywność bloku w czasie działania programu sygnalizuje podświetlenie bloku szarym

okręgiem. Atrybutem bloku, służącym do reprezentacji bloku w innych językach lub do identyfikacji bloku

podczas kompilacji i przyporządkowaniu błędów, jest symbol: GSnnn.x (zmienna logiczna), GSnnn.t

(zmienna czasowa). Gdzie nnn oznacza numer bloku.

Rys. 15.4. Przykłady bloków

Przejścia - reprezentowane przez grubszą linię umieszczoną w poprzek linii łączących elementy (rys.

15.5). Każde przejście opisane jest przez numer identyfikacyjny, umieszczony obok przejścia. Przejściu

można również nadać komentarz - krótki opis nie będący kodem programu.

Pojedyncze linie łączące - służą do łączenia bloków i przejść. Symbolizują przechodzenie punktu pracy

programu przez elementy składowe.

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-10

102

Zezwolenie na Start

numer

przejścia

komentarz

Rys. 15.5. Opis przejścia

Pojedyncze linie rozgałęzione - służą do połączenia jednego bloku z wieloma przejściami (rys. 15.6.a).

Praktyczne umożliwia to wybór jednej z dróg dla której spełniony jest warunek przejścia.

Podwójne linie łączące - służą do połączenia jednego przejścia z kilkoma blokami (rys. 15.6.b), których

instrukcje wykonywane są dalej równolegle.

Metoda ta może być traktowana jako zastosowanie pojęć sieci Petriego. Miejsca sieci

Petriego odpowiadają krokom SFC, natomiast przejścia sieci Petriego odpowiadają przejściom SFC.

Przejścia definiują warunki przejścia z jednego kroku, do następnego.

1

4

e

3

c

6

h

7

i

5

f

8

k

d

g

j

1

a

4

3

6

7

i

5

f

8

k

d

g

j

Rys 15.6. Sekwencja kroków z: (a) alternatywnymi gałęziami, (b) równoległymi gałęziami

Skoki do bloków - mogą być użyte do przeniesienia punktu pracy z przejścia do bloku. Skok

symbolizuje strzałka z numerem bloku, do którego skok jest skierowany (rys. 15.7).

102

Rys. 15.7. Zapis skoku

Blok makra - zawiera bloki i przejścia łączone w standardowy sposób, lecz traktowane jako odrębna

część zamknięta w jednym bloku makra (rys. 15.8).

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-11

Rys. 15.8. Blok makra

Wywołanie procedury - powoduje przejście wykonywania instrukcji do procedury zawartej w ramce.

Funkcja zwraca wartość będącą rezultatem poprawności jej wykonania.

<rezultat> := <procedura> ();

Konwersja IL - bloki SFC można opisać także za pomocą IL. Tą część kodu należy umieścić w ramach

ograniczonych rozkazami: #info=IL .................... #endinfo

Reguły układu i wykonania programu: bloki i przejścia łączone są liniami pojedynczymi lub złożonymi,

poszczególne części programu mogą być grupowane i wywoływane jako makra, blok nie może

następować bezpośrednio po bloku, przejście nie może następować po przejściu, to samo makro nie

może być użyte więcej niż jeden raz w programie, program FSC nie mający programu nadrzędnego jest

nazywany main, program ten jest uruchamiany przy starcie aplikacji, podprogram może mieć tylko

jednego właściciela, podprogram może być kontrolowany tylko przez jego właściciela, właściciel nie ma

wpływu na podprogram wywoływany w podprogramie, jeżeli przejście nie posiada instrukcji, to jego

wartość logiczna wynosi 1.

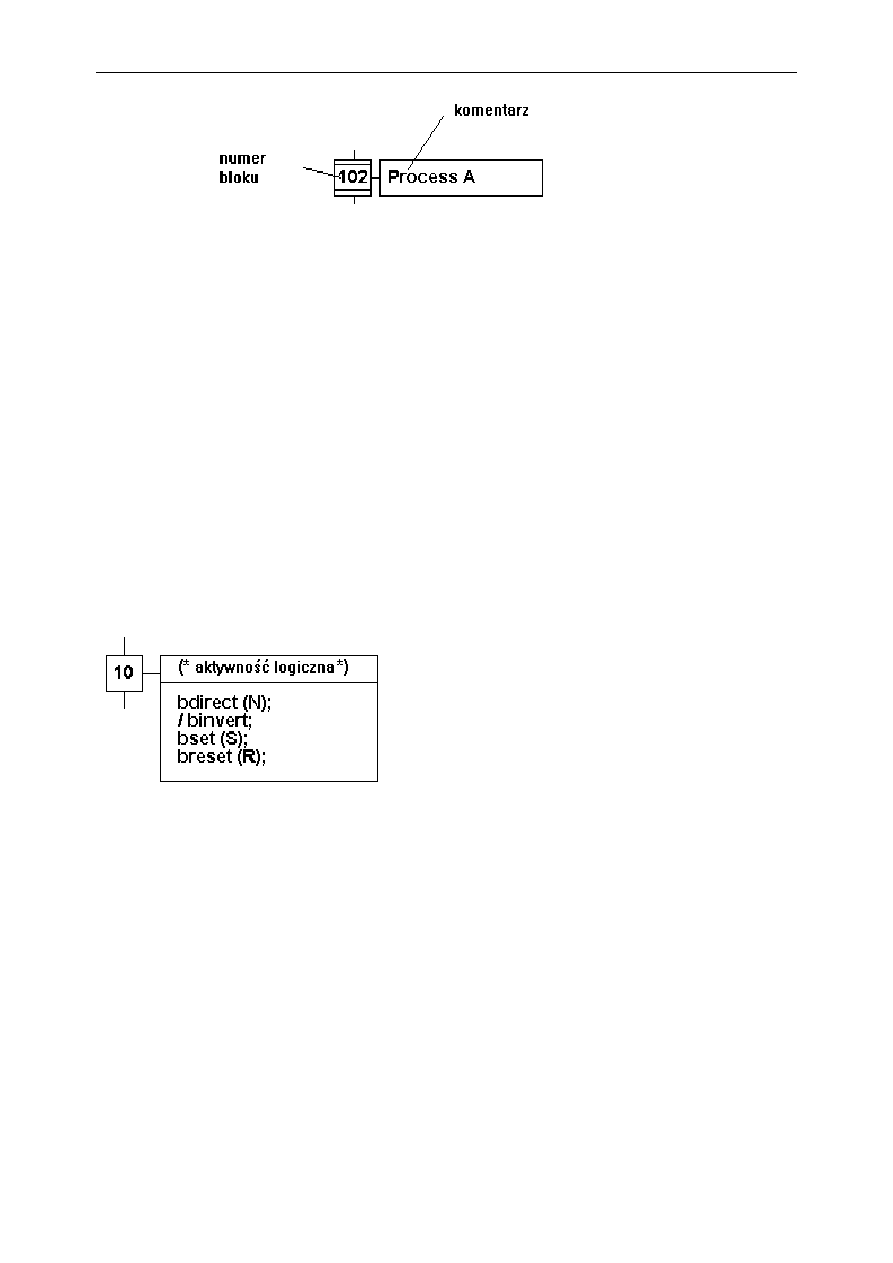

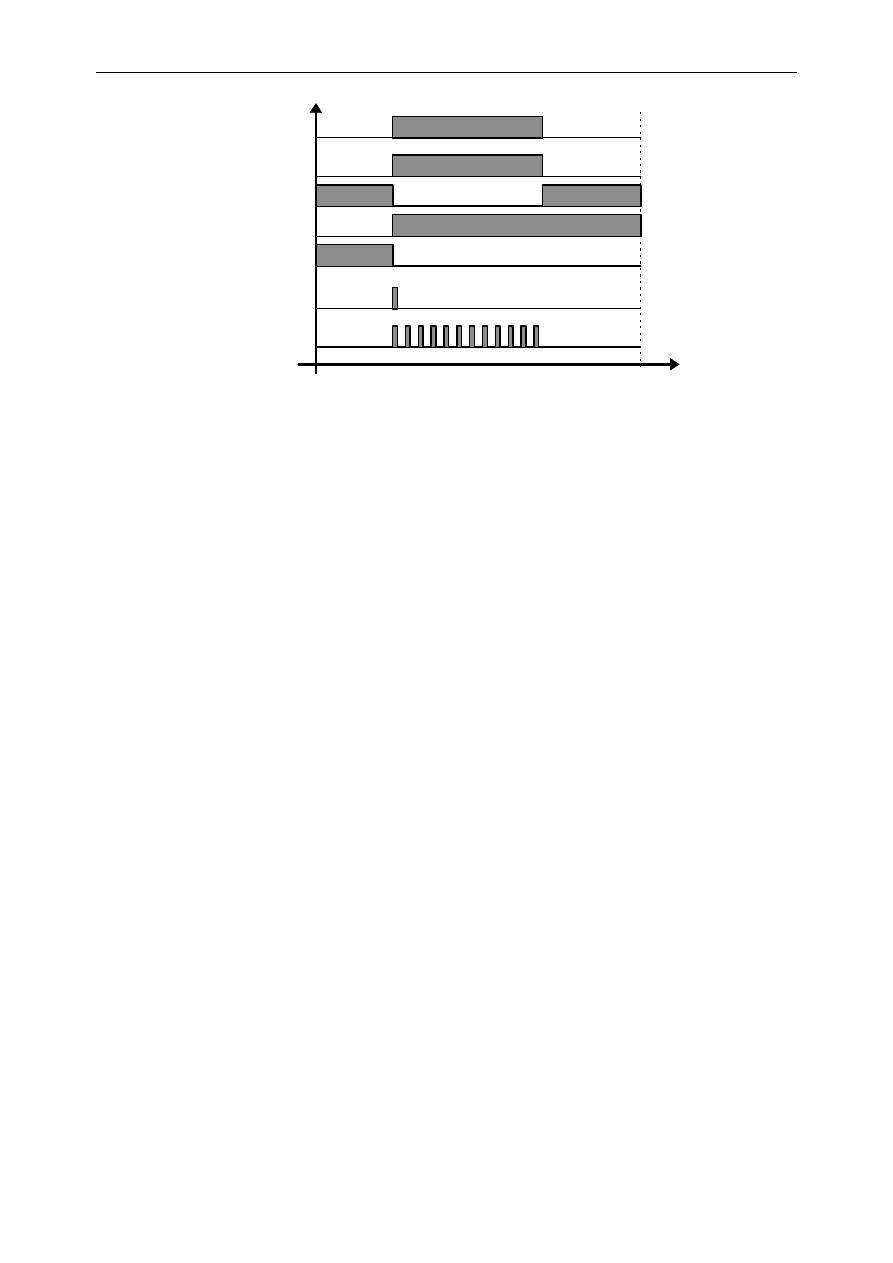

Typy aktywności bloków

Aktywność logiczna - przypisuje aktywność zmiennym logicznym przy aktywności bloku. Działanie to

ilustruje rysunek 15.9. Przy czym zmienna logiczna musi być zmienną wewnętrzną lub wyjściową.

Rys. 15.9. Zapis aktywności logicznej

Aktywność pulsacyjna - powoduje, że instrukcja wykonywana jest tylko raz w przypadku aktywności

bloku (rys. 15.10). Ten rodzaj aktywności uzyskiwany jest przez umieszczenie instrukcji w części

ograniczonej rozkazami ACTION (P) i END_ACTION;

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-12

aktywność bloku

aktywność logiczna - bidirect

aktywność logiczna - binvert

aktywność logiczna - bset

aktywność logiczna - breset

aktywność pulsacyjna

aktywność bez pamięci

t

Rys. 15.10. Typy aktywności

Aktywność bez pamięci

- instrukcje są wykonywane w każdym cyklu podczas aktywności bloku (rys.

15.10). Ten rodzaj pracy uzyskuje się przez zamknięcie w klamry rozkazów ACTION (N) i

END_ACTION;

Aktywność SFC

- umożliwia zarządzanie podprogramami na podobnych zasadach, jak akcja

zmiennych logicznych. Jej uruchomienie następuje przez podanie nazwy podprogramu i parametru:

<pod_program> (N) - uruchamia podprogram, gdy blok jest aktywny oraz kończy wraz z

dezaktywacją bloku. (N) jest parametrem opcjonalnym;

<pod_program> (S) - startuje podprogram;

<pod_program> (R) - zatrzymuje podprogram.

Przyporządkowanie warunków do przejść

Konwersja

języka ST

- przejście osiąga stan prawdy, gdy wyrażenie napisane w języku ST jest

prawdziwe. Konwersja języka IL - jeżeli aktualna wartość akumulatora jest równa 0, przejście nie jest

aktywne. Uaktywni się wówczas, gdy wartość akumulatora będzie się różnić od zera. Wywołanie

procedury

- wywołana przy przejściu procedura musi po wykonaniu zwrócić wartość różną od zera, aby

uaktywnić przejście.

Sterowanie podprogramem przez program nadrzędny

realizowane jest przez instrukcje:

Gstart - uruchamia podprogram, Gkill - zatrzymuje podprogram wraz z jego podprogramami, Gfreeze -

zawiesza wykonanie podprogramu, Grst - ponownie restartuje zawieszony podprogram, Gstatus -

pobiera aktualny status podprogramu.

15.5.2. Bloki funkcyjne

Bloki funkcyjne FBD (Functional Block Diagram) są graficznym językiem, umożliwiającym budowę

całościowych procedur przez pobieranie bloków funkcyjnych z bibliotek i ich łączenie. Elementy języka

FBD opisują zależność funkcyjną pomiędzy zmiennym wejściowymi a wyjściowymi.

Bloki funkcyjne

Bloki funkcyjne wywodzą się ze schematów obwodów cyfrowych. W standardzie IEC wyróżnia się

funkcje i bloki funkcyjne. Zakłada się, że obiekt typu funkcja posiada tylko jedne wyjście i dla tych

samych wejść wydaje tą samą wartość wyjścia. Bloki funkcyjne posiadają kilka wyjść i dla tych

samych wartości wejść mogą posiadać różne wartości wyjść, ze względu na wewnętrzne sprzężenia

zwrotne i pamięć. Funkcje i bloki funkcyjne mogą być zdefiniowane hierarchicznie.

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-13

>=1

>=1

&

a

b

c

d

k

k= (a+b)*(c+d)

Rys 15.11. Przykład użycia prostych bloków funkcyjnych

Funkcje lub bloki funkcji mogą realizować przetwarzanie binarne, numeryczne, analogowe lub

znakowe. Rysunek 15.11 przedstawia użycie prostych bloków funkcyjnych.

Rys. 15.12. Sposoby łączenia bloków

Bloki

funkcyjne

łączone są liniami, przy czym ważne jest, aby lewy koniec linii nie znajdował się

wyżej niż prawy, gdyż diagram programu rozpatrywany jest kolejno z góry w dół. Pojedyncza linia może

łączyć: zmienną wejściową z wejściem funkcji, wyjście funkcji ze zmienną wyjściową, wyjście funkcji z

wejściem innej funkcji. Linie rozgałęziającą tworzymy na tych samych zasadach pamiętając również aby

prawy koniec nie przewyższał lewego (Rys. 15.12 i 15.13).

Rys. 15.13. Rozgałęzienie linii

W przypadku, gdy linia jest zakończona kółkiem, oznacza to logiczne zaprzeczenie

przenoszonego sygnału. Wywołanie procedury przeprowadza się przez wstawienie bloku, który ją

obrazuje ( rys. 15.14). Nazwa procedury widnieje wewnątrz bloku. Natomiast wyjściem z procedury jest

zwracana przez nią wartość.

Rys. 15.14. Zapis bloku procedury

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-14

Standardowe bloki funkcyjne

Biblioteka ST

posiada podprogramy umożliwiające operacje: manipulacji na zmiennych

(przyporządkowanie), logiczne (AND, OR, EXOR), operacje arytmetyczne (dodawanie, odejmowanie,

mnożenie, dzielenie), operacje na bitach (maska z użyciem AND, OR, EXOR), operacje porównania,

operacje konwersji, operacje na znakach, operacje systemowe (łączność z systemem).

Biblioteka bloków funkcji C

zawiera:

• manipulacje danymi logicznymi: ustawialny przerzutnik bistabilny, kasujący przerzutnik bistabilny,

wykrywanie powstania brzegu, wykrycie opadania brzegu, semafor,

• liczniki: licznik w górę, licznik w dół, licznik w górę i w dół,

• zegary: opóźnienie przy sygnale 1, opóźnienie przy sygnale 0, zegar pulsacyjny,

• manipulacje danymi całkowitymi: pełne porównanie bloku funkcyjnego, stos,

• procesy dotyczące sygnałów analogowych: przepełnienie, histereza, alarm z ograniczeniem,

połączenie z czasem, różnice czasu,

• regulator PID,

• generacje sygnału: generator sygnału logicznego.

Biblioteka funkcji C

zawiera funkcje matematyczne, trygonometryczne, kontroli rejestrów (przesunięcia,

przeniesienia), manipulacji danymi (minimum, maksimum, modulo, multiplekser 4 lub 8 wejść,

parzystość, generator liczb losowych, selektor logiczny 0), konwersji danych, realizujące operacje na

łańcuchach znaków i tablicach.

15.5.3. Schematy drabinkowe

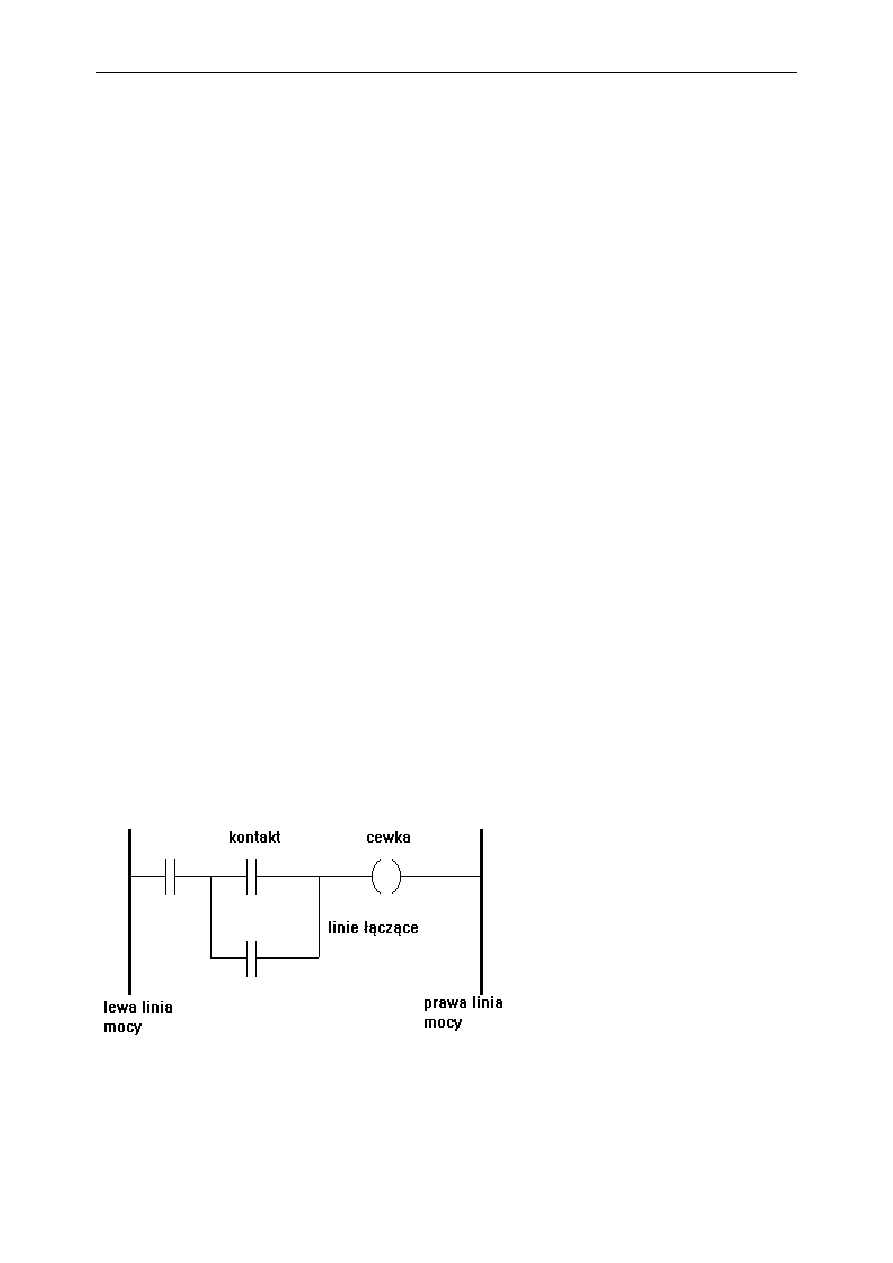

Schematy drabinkowe LD (Ladder Diagram) są graficzną reprezentacją logicznych równań przez układ

graficznych symboli. Diagram LD zawiera się pomiędzy lewą i prawą szyną mocy, do których jest

dołączony (rys. 15.15). Elementy mogą być łączone liniami pojedynczymi lub grupowymi. Lewa szyna

mocy, jak również wszystkie linie połączone z nią, posiadają stan logiczny prawdy. Stan ten jest

przenoszony przez kontakt w przypadku, gdy jest zamknięty. Każdy kontakt jest przyporządkowany

zmiennej wejściowej lub wewnętrznej. Gdy zmienna przyjmuje stan 1, kontakt ulega zamknięciu. Gdy

linia połączona z cewką posiada "moc", to cewka jak również przyporządkowana do niej zmienna

wyjściowa zostają uaktywnione (przyjmują wartość 1).

Kontakt

może występować w różnych modyfikacjach: standardowy, zanegowany - (/),

uaktywniany zboczem narastającym - (P), uaktywniany zboczem opadającym - (N). Z kolei cewki mogą

mieć postać: standardową, zanegowaną - (/), ustawialną - (S), kasowalną - (R).

Rys. 15.15. Przykład schematu drabinkowego

Schematy drabinkowe reprezentują formalizm elektrycznych diagramów połączeń stosując

sterowanie bazujące na przełącznikach binarnych. Wadą tych schematów jest to, że jeżeli mają być

zaprogramowane nie tylko operacje binarne, to schematy te muszą być rozszerzone o dodatkowe

elementy. Rysunek 15.16 podaje podstawowe elementy schematów drabinkowych, natomiast

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-15

rysunki 15.17 i 15.18 przedstawiają sposób użycia elementów dla połączenia szeregowego i

równoległego.

] [

( )

]/ [

Włączone

Wyłączone

Ustawienie

Rys 15.16. Podstawowe elementy schematów drabinkowych

] [

( )

]/ [

A

B

P

Rys 15.17. Połączenie szeregowe

P

A

B

=

*

_

] [

( )

]/ [

] [

A

B

C

P

Rys 15.18. Połączenie równoległe

P

A

B

C

=

+

+

_

Elementami łączonymi tylko z lewej strony do linii sygnałowych są: instrukcja powrotu - RETURN -

powodująca przerwanie wykonywania programu i instrukcja skoku - umożliwiająca przejście

wykonywania programu do miejsca oznaczonego etykietą (rys. 15.19).

Rys. 15.19. Przykład zapisu instrukcji skoku

15.5.4. Tekst strukturalny

Tekst strukturalny ST (Structured Text) ma składnię podobną do języka Pascal. W języku ST

zdefiniowane są instrukcje podstawiania, wyboru IF i CASE, iteracyjne FOR, WHILE, REPEAT,

wywołanie funkcji lub bloku funkcji oraz przerwania wykonania funkcji. Język ST stanowi główne

narzędzie do budowy złożonych procedur, dlatego nie może być przedstawiony jako język graficzny.

Domyślnie używa się go przy opisie akcji w blokach i przejściach SFC. Program ST jest listą wyrażeń

zakończonych średnikiem, będącym separatorem instrukcji.

Typy wyrażeń języka ST:

-

przyporządkowanie: zmienna := wyrażenie;

-

wywołanie podprogramu lub funkcji C:

zmienna := podprogram (par1,par2,...);

- wywołanie bloku funkcji C: nazwabloku (par1,par2,...); rezultat := nazwabloku.par1;

- wyrażenie wyboru:

IF

wyr_logiczne THEN wyrażenie;

ELSE

wyrażenie; END_IF;

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-16

- pętle:

FOR

ind:=min TO max BY krok

DO

wyrażenie; END_FOR;

WHILE

wyr_logiczne DO

wyrażenie; END_WHILE;

REPEAT

wyrażenie; UNTIL

war_logiczny; END_REPEAT;

- powrotu:

RETURN;

Operatory języka:

- nawiasy (maksymalnie 8 w wyrażeniu),

- funkcje konwersji:

zmienna

:=

BOO

(wyrażenie); zmienna := ANA (wyrażenie); zmienna:=REAL(wyrażenie);

zmienna

:=

TMR

(wyrażenie); zmienna := MSG (wyrażenie);

- operatory logiczne:

zm_logiczna

:= NOT (wyr_logiczne);

rez_logiczny := wyr_log1 AND wyr_log2;

rez_logiczny := wyr_log1 OR wyr_log2;

rez_logiczny := wyr_log1 XOR wyr_log2;

brzeg

:=

REDGE

(wyr_logiczne,zm_pam);

brzeg := FEDGE (wyr_logiczne,zm_pam);

- operatory arytmetyczne:

wynik := wyr1 * wyr2; wynik := wyr1 / wyr2; wynik := wyr1 + wyr2; wynik := wyr1 - wyr2;

- porównania,

wynik := wyr1 < wyr2; wynik := wyr1 > wyr2; wynik := wyr1 <= wyr2;

wynik := wyr1 >= wyr2; wynik := wyr1 = wyr2; wynik := wyr1 <> wyr2;

Rozszerzenia języka ST:

- sterowanie zegarem (zmienne zegarowe): TSTART, TSTOP;

- zarządzanie programami (podprogramy): GSTART, GKILL, GFREEZE, GRST, GSTATUS;

- wyrażenie systemowe:

zm_analog

:=

SYSTEM

(rozkaz, argument);

- wyrażenie akcji:

zm_analog

:=

OPERATE

(zm_we_wy, rozkaz, argument);

15.5.5. Lista instrukcji

Lista instrukcji IL (Instruction List) jest językiem niskiego poziomu, podobnym do języka asemblera.

Język ten jest efektywny dla małych aplikacji lub służy dla optymalizacji części aplikacji. Instrukcje

odnoszą się zawsze do aktualnego wyniku (rejestru). Operator wskazuje, jakiego typu operacja

będzie wykonywana. Wynik jest ponownie zapisywany do rejestru i traktowany jako aktualny wynik.

Większość operacji standardowego języka IL ma postać:

wynik := wynik OP operand

Program IL jest listą instrukcji, z których każda musi zaczynać się od nowej linii, zawierać

operator z kompletnymi modyfikacjami i ewentualnie jeden lub więcej operandów oddzielonych

separatorem ",". Etykieta zawsze poprzedza znak ":" i może być umieszczona przed instrukcją lub w

wolnej linii. Nazwa nie może przekraczać 16 znaków, pierwszy znak musi być literą, następne literą,

liczbą bądź znakiem "_". Może być definiowana tylko raz w programie. Wykaz operatorów oraz ich

Opublikowano w: WEREWKA J..: Programowanie sprzętu komputerowego dla automatyków. Skrypt AGH Nr 1514 15-17

podstawowe zastosowanie przedstawia tabela 15.3. Rozmieszczenie elementów w programie ma

postać:

ETYKIETA

OPERATOR

OPERAND

KOMENTARZ

Start

LD

zm1

(*wczytanie

zm1*)

AND

zm2

(*koniunkcja

z

zm2*)

ST

wynik

(*wynik

operacji

zapisany

do

wynik*)

W

języku IL nie ma możliwości operowania na zmiennych typu rzeczywistego i zmiennych

będących komunikatem. Maksymalna ilość modyfikatorów służących do grupowania wynosi 32.

Tab. 15.3. Operacje z listy instrukcji.

Operator Opis

LD

ładuje wartość do aktualnego rejestru wynikowego

ST zapamiętuje aktualny wynik z rejestru wynikowego w zmiennej

S wpisuje

wartość TRUE do zmiennej, jeżeli aktualny wynik jest TRUE

R wpisuje

wartość FALSE do zmiennej, jeżeli aktualny wynik jest TRUE

AND

operacja logiczna AND pomiędzy aktualnym wynikiem a operandem

OR

operacja logiczna OR pomiędzy aktualnym wynikiem a operandem

XOR

operacja logiczna XOR pomiędzy aktualnym wynikiem a operandem

ADD

operacja arytmetyczna dodawania pomiędzy aktualnym wynikiem a operandem

SUB

operacja arytmetyczna odejmowania pomiędzy aktualnym wynikiem a operandem

MUL

operacja arytmetyczna mnożenia pomiędzy aktualnym wynikiem a operandem

DIV

operacja arytmetyczna dzielenia pomiędzy aktualnym wynikiem a operandem

GT

operacja porównania >, wynikiem operacji jest TRUE albo FALSE

GE

operacja porównania >=, wynikiem operacji jest TRUE albo FALSE

EQ

operacja przyrównania, wynikiem operacji jest TRUE albo FALSE

LE

operacja porównania <=, wynikiem operacji jest TRUE albo FALSE

LT

operacja porównania <, wynikiem operacji jest TRUE albo FALSE

JMP

operacja skoku do określonej etykiety

RET

operacja powrotu z podprogramu

Literatura

[1] ISaGRAPH Version 2.10, User's Guide, CJ International, 1994

[2] ISaGRAPH Version 2.10, Target user's Guide, CJ International, 1994

[3] Programmable Logic Controllers Survey. Control and Instrumentation. January 1996, pp. 21-23

[4] Skomorowski M.: Wstęp do projektowania systemów cyfrowych. Skrypt Uczelniany UJ, 1994, nr 701,

p. 122

[5] Werewka J., Kich Z. R.: Dobór sterowników analogowo-cyfrowych oraz ich oprogramowania

ze

względu na ich przydatność w wybranych systemach sterowania układów elektromechanicznych.

Opracowanie ZBPE MPH i PAN IE Warszawa, Kraków 1994

[6]

Werewka J., Raczyński A.: Szybkie projektowanie oprogramowania dla sterowników

programowalnych (PLC). Komputerowe wspomaganie inżynierskich prac projektowych. Redakcja. M.

Szymkat i T. Uhl, Cracow Centre for Advanced Training in Information Technology (CCATIE), Kraków

1995, pp. 110-124

Document Outline

Wyszukiwarka

Podobne podstrony:

Sterowniki PLC projekt

Sterowniki PLC

BALANCED SCORECARD PROJEKTU pusty dla studentów

Realizacja układu sterowania logicznego na?zie sterownika PLC sprawozdanie

Sterownik PLC

PROJEKT?UKACJI EKOLOGICZNEJ DLA PRZEDSZKOLA

Projektowanie oprogramowania Wstep do programowania i techniki komputerowej

projekt socjalny dla Pani Ewy K. 92l - OŚ, Projekt socjalny

2 Architektura sterowników PLC materiały wykładowe

sterownik PLC, Automatyka

Labolatorium projektowania układów i systemów sterowania, Narzędzia komputerowego wspomagania projek

praca dyplomowa sterowniki plc(1) AXJZC2BHVTOB2W4Y25CUGW5NAMFE5TU2LJ73JCY

PROJEKT DACHU DLA BUDYNKU RODZINNEGO prezentacja

4 Sterowniki PLC wejściawyjścia analogowe

PL CP1E sterownik PLC Broszura

Podstawy programowania sterowników PLC (2)

Programowanie sterowników PLC u

Projekt geologia 2 dla starszych wersji Worda, Geologia inżynierska

więcej podobnych podstron