1998 Dec 09

DISCRETE SEMICONDUCTORS

Thermal Considerations

Power Diodes

Valid for:

SC11

General Section Module

Thermal Considerations

Module: THC00X

1998 Dec 09

2

Philips Semiconductors

Power Diodes

Thermal Considerations

THERMAL CONSIDERATIONS

Thermal resistance

Circuit performance and long-term reliability are affected

by the temperature of the chip. Normally, both are

improved by keeping the chip temperature (junction

temperature) low.

Electrical power dissipated in any semiconductor device is

a source of heat. This increases the temperature of the

chip with regard to some reference point, normally an

ambient temperature of 25

°

C in still air. The increase in

temperature depends on the amount of power dissipated

in the device and the net thermal resistance between the

heat source and the reference point. This can be

expressed as:

∆

T

j

= P

tot

×

R

th j-a

where:

∆

T

j

is the increase in junction temperature

P

tot

is the total power generated in the device

R

th j-a

is the thermal resistance from junction to ambient.

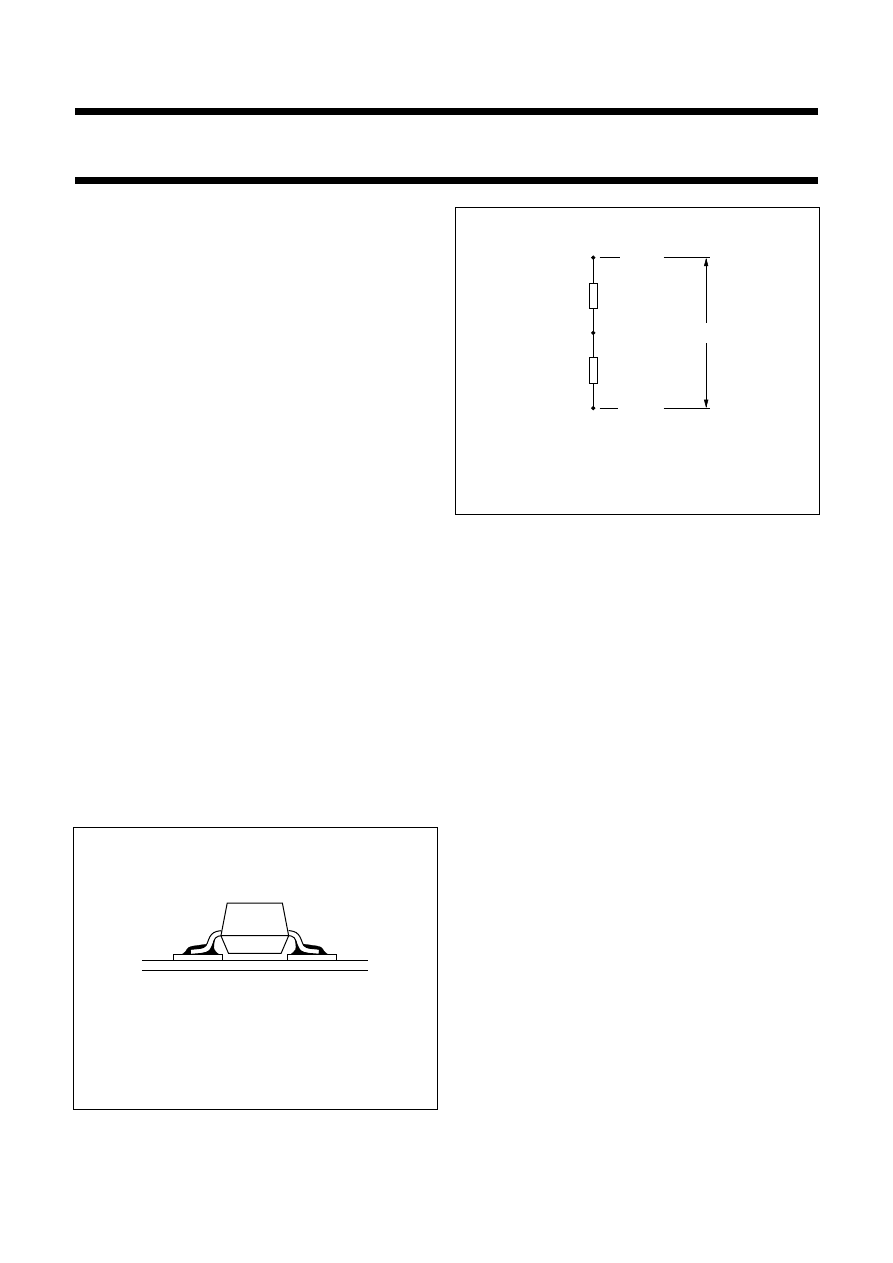

Surface mounted devices

Heat transfer can occur by radiation, conduction and

convention. Surface mounted devices lose most of their

heat by conduction when mounted on a substrate.

Referring to Fig.1, heat conducts from its source (the

junction) via the package leads and soldered connections

to the substrate. Some heat radiates from the package into

the surrounding air, where it is dispersed by convection or

by forced cooling air. Heat that radiates from the substrate

is dispersed in the same way.

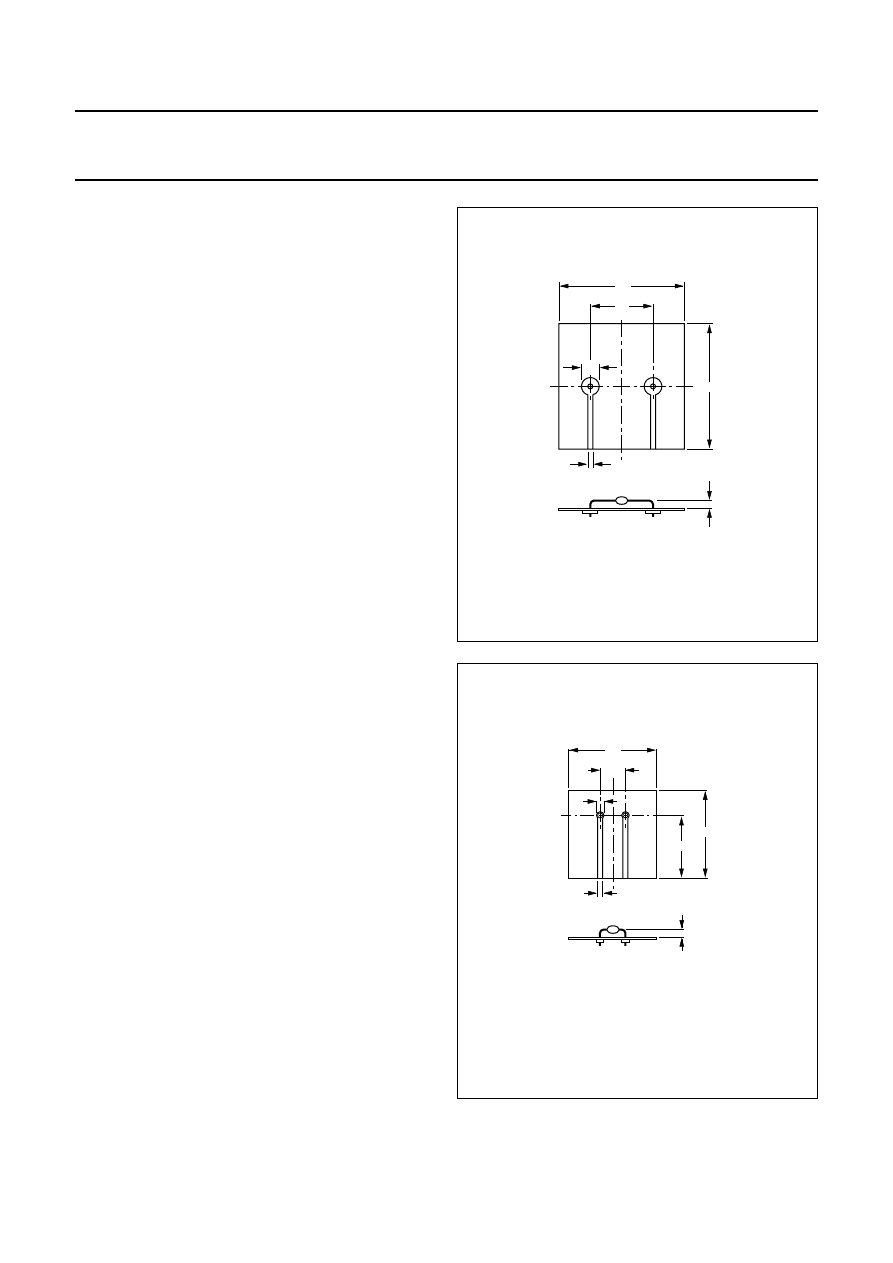

handbook, halfpage

,

,

,

MBB438

,

,

,,

,,

1

2

3

2

3

4

Fig.1 Heat losses.

Heat radiates from the package ‘1’ to ambient.

Heat conducts via leads ‘2’, solder joints ‘3’ to the substrate ‘4’.

The thermal resistance for surface mounted devices

therefore, can be expressed as:

R

th j-a

= R

th j-tp

+ R

th tp-a

(see Fig.2)

where:

R

th j-a

is the thermal resistance from junction to ambient

R

th j-tp

is the thermal resistance from junction to tie-point

R

th tp-a

is the thermal resistance from tie-point to ambient.

The R

th j-tp

value is essentially independent of external

mounting method and cooling air, but is sensitive to the

materials used in the package construction, the chip

bonding method and the chip area, all of which are fixed.

The R

th tp-a

value depends on the shape and material of

the tracks and substrate. For all package types these

values are given in Table 1 for mounting on (FR4)

printed-circuit board with small pad area. For other pad

areas and printed-circuit board configurations see Fig.3

and “Appendix A”.

The maximum power handling capability (P

tot max

) is given

by:

where:

T

j max

is the maximum junction temperature

T

amb

is the ambient temperature.

Calculating this maximum power handling capability we

have to take into account the maximum junction

temperature of the particular device, the maximum

temperature of the solder joints (110

°

C for long time

Fig.2

Representation of thermal resistance for a

surface mounted diode.

handbook, halfpage

MBH560

ambient

junction

tie

−

point

Rth j

−

a

Rth j

−

tp

Rth tp

−

a

P

tot max

T

j max

T

amb

–

(

)

R

th j-a

-----------------------------------------

=

1998 Dec 09

3

Philips Semiconductors

Power Diodes

Thermal Considerations

reliability) and the ambient temperature. Dependent on the

ratio of the component parts of the thermal resistance, it

will be possible that the junction temperature or the

temperature of the solder joints (T

tp

) will be the limiting

factor. This can be shown in the following examples for

SOT23 and SOD87 packages mounted on FR4

printed-circuit board.

E

XAMPLE FOR THE SOT

23

PACKAGE

This is below 110

°

C, so T

j max

is the limiting factor.

E

XAMPLE FOR THE SOD

87

PACKAGE

This is above 110

°

C, so the P

tot max

will be limited by T

tp

,

therefore:

The P

tot max

values given in Table 1 are based on:

T

amb

= 25

°

C; T

j

= T

j

max; T

tp

≤

110

°

C.

150

°

C

25

°

C

)

–

(

500 K/W

-------------------------------------------------

=

0.25 W

=

P

tot max

T

j max

T

amb

)

–

(

R

th j-a

--------------------------------------------

=

T

tp

T

amb

P

tot max

R

th tp-a

×

+

=

25

°

C

0.25 W

150 K/W

×

62.5

°

C

=

+

=

P

tot max

T

j max

T

amb

)

–

(

R

th j-a

--------------------------------------------

=

175

°

C

25

°

C

)

–

(

150 K/W

-------------------------------------------------

=

1 W

=

T

tp

T

amb

P

tot max

R

th tp-a

×

+

=

25

°

C

1 W

120 K/W

×

145

°

C

=

+

=

P

tot max

T

tp

T

amb

)

–

(

R

th tp-a

-------------------------------------

=

110

°

C

25

°

C

)

–

(

120 K/W

-------------------------------------------------

=

0.71 W

=

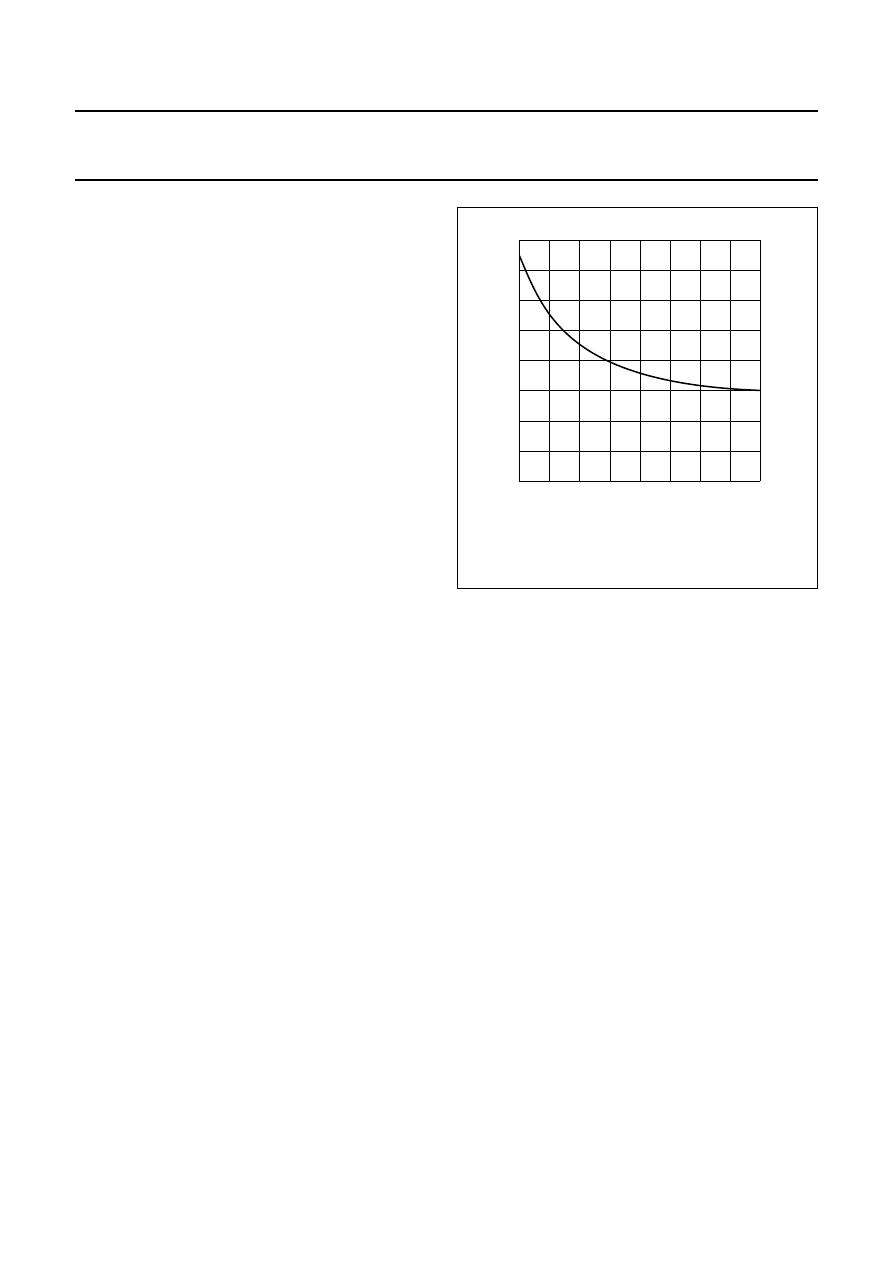

Fig.3

Thermal resistance (R

th tp-a

) as a function of

FR4 printed-circuit board pad area.

handbook, halfpage

0

100

200

400

pad area (mm

2

)

Rth tp

−

a

(K/W)

160

120

40

0

80

300

MBH561

1998 Dec 09

4

Philips Semiconductors

Power Diodes

Thermal Considerations

Table 1

Thermal resistance values and maximum power handling capability of surface mounted packages; typical

values

PACKAGE

R

th j-a

(K/W)

R

th j-tp

(K/W)

R

th tp-a

(K/W)

P

tot max

(W)

SOD87

150

30

120

0.71

SOD106(A)

150

25

125

0.68

SOT23

500

330

170

0.25

SOT89

125

15

100

0.85

SOT223

85

15

70

1.21

SOT323 (SC70-3)

625

300

325

0.20

SOT363 (SC70-6)

415

200

215

0.30

SOT457 (TSOP6)

300

150

150

0.42

SO8 (SOT96-1)

155

35

115

0.74

SO20 (SOT163-1)

100

30

70

1.21

SSOP16 (SOT338-1)

145

75

70

0.86

SSOP24 (SOT340-1)

105

35

70

1.19

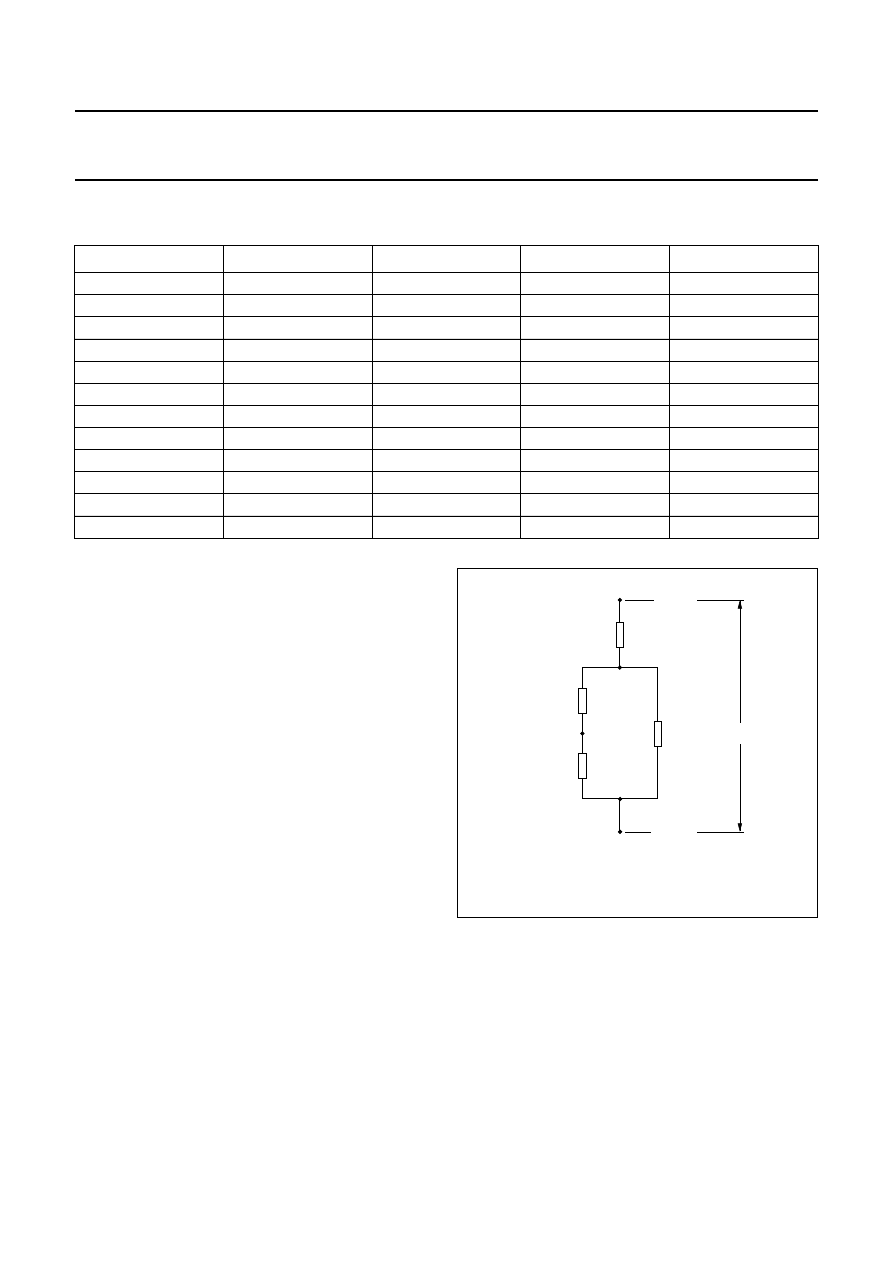

Leaded devices

Figure 4 illustrates the various components of thermal

resistance for an axial leaded diode mounted with

symmetrical, equal length leads. The thermal resistance

from junction to ambient (R

th j-a

) comprises the following

thermal resistances:

R

th j-p

is the thermal resistance from junction to package

R

th p-tp

is the thermal resistance from package to tie-point

R

th tp-a

is the thermal resistance from tie-point to ambient

R

th p-a

is the thermal resistance from package to ambient.

The values of the thermal components depend on the

diode package type, the lead length and the mounting

method used.

Using the model in Fig.4 and referring to Table 2, values

for the thermal resistance from junction to ambient can be

calculated using the formula:

The maximum power handling capability (P

tot max

) is given

by:

R

th j-a

R

th j-p

R

th p-a

R

th p-tp

R

th tp-a

)

+

(

R

th p-a

R

th p-tp

R

th tp-a

+

+

---------------------------------------------------------------------

+

=

P

tot max

T

j max

T

amb

–

(

)

R

th j-a

-----------------------------------------

=

Fig.4

Representation of thermal

resistance paths for a leaded device.

handbook, halfpage

MBH563

ambient

package

junction

tie

−

point

Rth j

−

a

Rth p

−

tp

Rth tp

−

a

Rth p

−

a

Rth j

−

p

where:

T

j max

is the maximum junction temperature and

T

amb

is the ambient temperature.

Calculating this maximum power handling capability we

have to take into account the maximum junction

temperature of the particular device, the maximum

temperature of the solder joints (110

°

C for long time

reliability) and the ambient temperature. Depending on the

ratio of the component parts of the thermal resistance it is

possible that the junction temperature or the temperature

1998 Dec 09

5

Philips Semiconductors

Power Diodes

Thermal Considerations

of the solder joints (T

tp

) will be the limiting factor. This can

be shown in the following examples for a SOD57 device

mounted on an FR4 printed-circuit board, as shown in

Fig.5:

and

Using values in Table 2:

is simplified to:

Using T

tp

= 110

°

C and T

amb

= 60

°

C the equation

becomes:

This is lower than P

tot max

= 1.15 W (for T

j max

= 175

°

C),

so in this particular case T

tp

= 110

°

C is limiting the

P

tot max

.

R

th j-a

14 K/W

=

429 K/W 38 K/W

70 K/W

+

(

)

429 K/W

38 K/W

70 K/W

+

+

-----------------------------------------------------------------------------

+

100 K/W

=

P

tot max

T

j max

T

amb

–

(

)

R

th j-a

-----------------------------------------

=

175

°

C

60

°

C

)

–

(

100 K/W

-----------------------------------------------

=

1.15 W

=

T

tp

T

amb

R

th p-a

R

th tp-a

×

R

th p-a

R

th p-tp

R

+

+

---------------------------------------------------

th tp-a

P

tot

×

+

=

T

tp

T

amb

=

429 K/W

70 K/W

×

429 K/W

38 K/W

70 K/W

+

+

----------------------------------------------------------------------------

P

tot

×

+

T

tp

T

amb

=

56 K/W

P

tot

×

+

P

tot

T

tp

T

amb

–

(

)

56 K/W

----------------------------------

=

110

°

C

60

°

C

–

(

)

56 K/W

--------------------------------------------

=

0.89 W

=

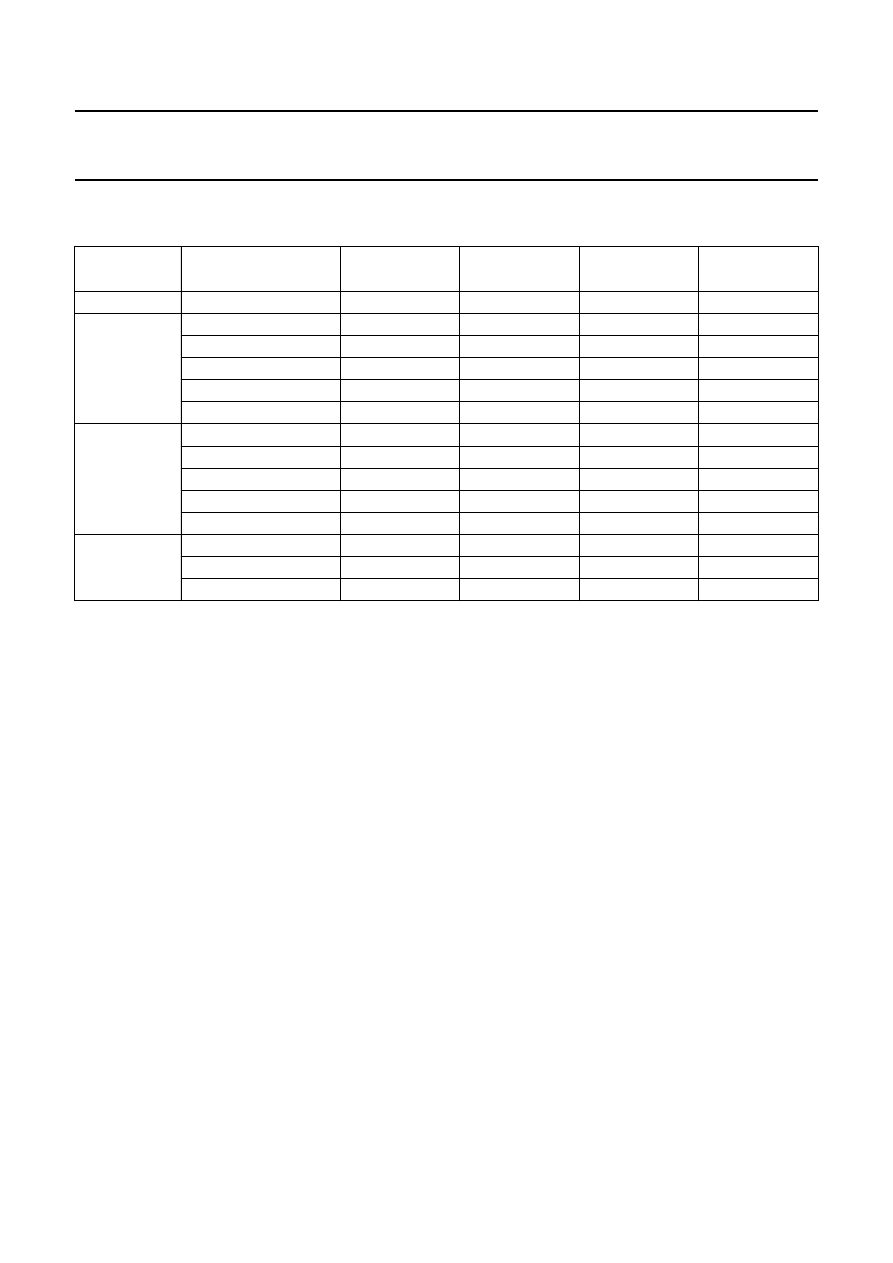

handbook, halfpage

MGA200

3

2

7

50

25

50

Fig.5

Leaded device mounted on printed-circuit

board 50

×

50 mm.

Dimensions in mm.

Fig.6

Leaded device mounted on printed-circuit

board 35

×

35 mm.

handbook, halfpage

MBH562

3

2

3

35

10

25

35

Dimensions in mm.

1998 Dec 09

6

Philips Semiconductors

Power Diodes

Thermal Considerations

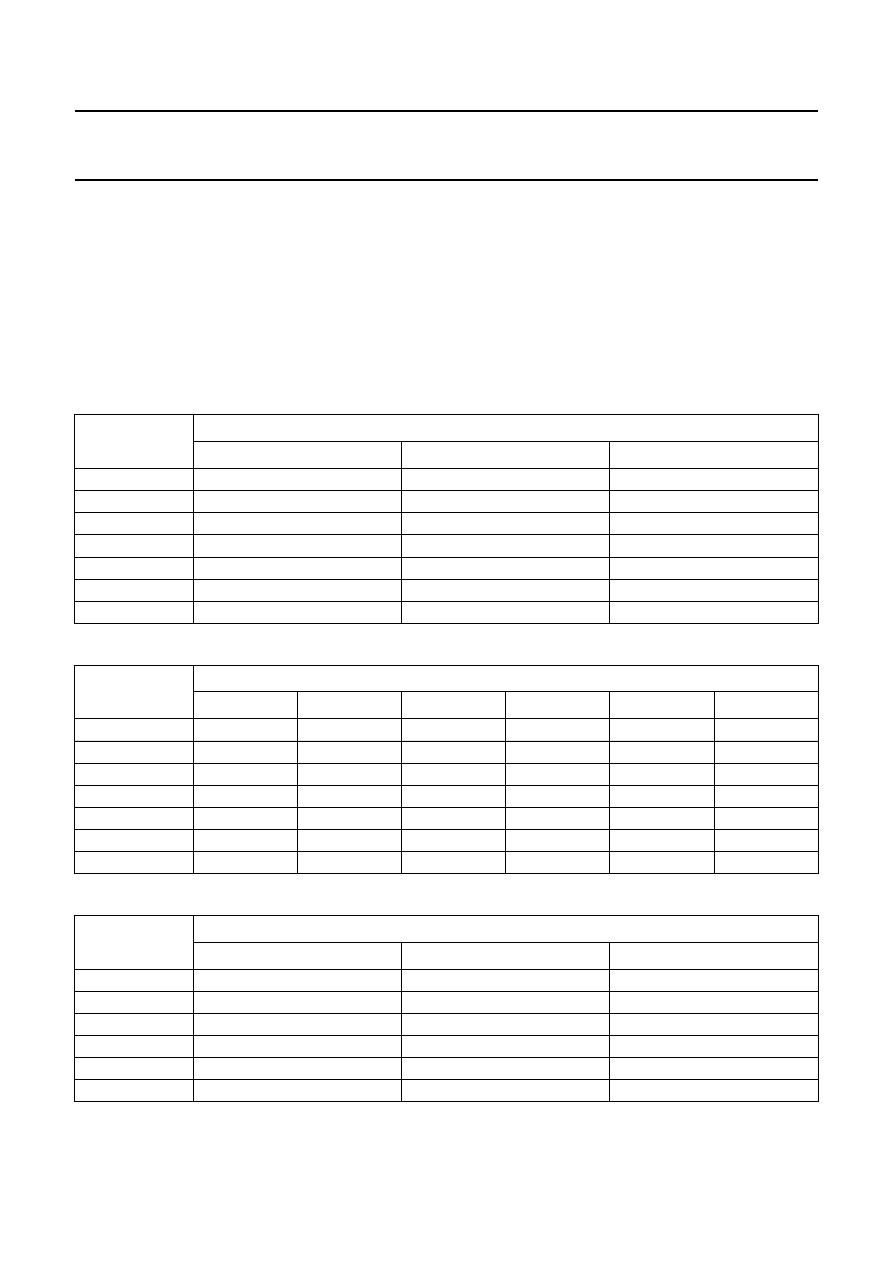

Table 2

Thermal resistance values for leaded packages

All values expressed in K/W, unless otherwise specified.

Notes

1. Device mounted on a 1.5 mm thick epoxy-glass printed circuit board with a copper thickness

≥

40

µ

m.

2. Mounted as in Fig.5.

3. Mounted with copper laminate per lead of 1 cm

2

.

4. Mounted with copper laminate per lead of 2.25 cm

2

.

THERMAL

RESISTANCE

CONDITIONS

SOD57

SOD88A

SOD61

SOD64

SOD83A

SOD81

R

th j-p

14

60

10

28

R

th p-tp

lead length = 5 mm

19

48

7

19

lead length = 10 mm

38

96

14

38

lead length = 15 mm

57

144

21

57

lead length = 20 mm

76

192

28

76

lead length = 25 mm

95

240

35

95

R

th p-a

lead length = 5 mm

586

1261

417

787

lead length = 10 mm

429

843

293

527

lead length = 15 mm

338

633

225

396

lead length = 20 mm

279

507

183

317

lead length = 25 mm

237

423

154

264

R

th tp-a

notes 1 and 2

70

70

70

70

notes 1 and 3

55

55

55

55

notes 1 and 4

45

45

45

45

1998 Dec 09

7

Philips Semiconductors

Power Diodes

Thermal Considerations

APPENDIX A

Additional thermal resistance data for SMD packages

All values are expressed in K/W, unless otherwise specified. The data included in Tables 3 to 5 are the results of

laboratory investigation into the effect of FR4 printed-circuit board pad area and power dissipation on thermal resistance.

Measurements were made with the test samples positioned vertically in still air.

It can be seen that with increased power dissipation, thermal resistance decreases slightly. This is because, as the power

dissipation increases, the resulting higher junction temperature causes increased losses due to radiation and natural

convection.

Table 3

SOT223 package (Thermal resistance junction to ambient)

Table 4

SOT428 package (Thermal resistance junction to ambient}

Table 5

SOT404 package (Thermal resistance junction to ambient)

PCB PAD AREA

(mm

2

)

R

th j-a

(K/W) @ POWER DISSIPATION P

P = 0.5 W

P = 1 W

P = 1.5 W

20

110

110

−

49

99

98

−

81

91

90

90

144

88

87

86

256

78

79

78

484

73

74

73

900

68

69

69

PCB PAD AREA

(mm

2

)

R

th j-a

(K/W) @ POWER DISSIPATION P

P = 0.5 W

P = 1 W

P = 1.5 W

P = 2 W

P = 2.5 W

P = 3 W

20

90

85

−

−

−

−

49

77

75

73

72

−

−

81

71

69

66

65

−

−

144

64

62

60

59

58

−

256

58

56

54

53

52

−

484

54

50

48

47

46

45

900

46

45

43

43

42

41

PCB PAD AREA

(mm

2

)

R

th j-a

(K/W) @ POWER DISSIPATION P

P = 1 W

P = 2 W

P = 3 W

103.5

60

55

−

192

52

47

−

300

47

43

41

475

41

39

37

825

39

36

34

1200

36

34

32

Wyszukiwarka

Podobne podstrony:

SC11 MARKING 1998 1

SC11 REPLACEMENT 1998 1

SC11 THERMAL CONSIDERATIONS

SC11 PACKAGES 1998 2

SC11 XREF GUIDE 1998 1

Kodeks pracy Dziennik Ustaw poz 94 nr 21 z 1998 roku

1998(1)

Microwaves in organic synthesis Thermal and non thermal microwave

1998 01 str 10 Egzotyczne mezony

1998 (101)

1998 09 09 1917

1998 10 03 prawdopodobie stwo i statystykaid 18585

1998 08 str 56 61 Gradientometria grawitacyjna

1998 Bustillo Surface Micromach Nieznany (2)

May 1998 Mathematics HL P1$

NISSAN FRONTIER 1998 2004

ARCH MED SĄD KRYM 1998, XLVII, 27 34

więcej podobnych podstron