Elektor

2/98

Wenn es wie so oft um einen einzelnen

Schaltungsaufbau geht, der möglichst

optimal funktionierten soll, kann man

mit einem FET-Tester entweder die am

besten zur Schaltungsdimensionierung

passenden FETs selektieren oder umge-

kehrt die Schaltungsdimensionierung

an den verwendeten FET anpassen,

um beispielsweise den optimalen

Arbeitspunkt einzustellen und damit

den maximalen Aussteuerbereich zu

erhalten. Bei Differenzstufen und

anderen Schaltungen, bei denen es auf

gute Übereinstimmung der Parameter

zweier oder mehrerer FETs ankommt,

bietet der Tester die Möglichkeit, die

geeignetsten Exemplare aus einem

größeren Posten auszuwählen. Die hier

vorgestellte Schaltung ist für die häu-

fig verwendeten N-Kanal-Junction-

FETs kleiner Leistung ausgelegt, die vor

allem in NF-, HF- und Meßschaltungen

vorkommen.

K

L E I N E

J F E T- K

U N D E

Wer sich noch nie oder schon länger

nicht mehr mit diesen Drain-Source-

Gate-Transistoren beschäftigt hat, fin-

det hier eine kurze Zusammenfassung

des relevanten Basiswissens. Bild 1

zeigt das Schaltsymbol und das grund-

legende Prinzipschaltbild. An dem

nach innen gerichteten Pfeil des Gate-

Symbols am Gate-Anschluß (G) erken-

nen wir, daß es sich um einen N-Kanal-

Junction-FET handelt. Beim P-Kanal-

JFET ist der Pfeil nach außen gerichtet,

und beim MOSFET-Transistor gibt es

gar keinen Pfeil. Obwohl die Anschluß-

bezeichnung von der bei bipolaren

Transistoren abweicht (Gate, Source,

Drain statt Basis, Emitter, Kollektor), ist

die Analogie in der prinzipiellen

Beschaltung nicht zu übersehen.

Eigentlich fließt der Kollektorstrom

genauso wie beim NPN-Transistor über

den Transistor - vom Kollektor zum

Emitter - nur daß der Kollektor hier mit

Drain (D) und der Emitter mit Source

(S) bezeichnet ist. Beim Vergleich zwi-

schen der Basis beim normalen NPN-

Transistor und dem Gate beim N-

Kanal-JFET hört die Analogie aber auf.

Während die Basis beim NPN-Transi-

Viele Elektroniker

stehen FETs in

Analogschaltun-

gen eher reser-

viert gegenüber,

obwohl sie in vie-

len Fällen Vorteile

bieten, wie zum

Beispiel hohe Ein-

gangsimpedanz,

hohe Grenzfre-

quenzen, relativ

niedriges Rau-

schen und gerin-

gen Beschal-

tungsaufwand.

Ein Nachteil ist

allerdings, daß

man mit einer

relativ großen

Parameterstreuung

rechnen muß. Wenn

man aber einen ein-

fach handzuhaben-

den Tester hat, ist das

gar kein Nachteil, weil

man die tatsächlichen

Daten leicht feststel-

len und entsprechend

berücksichtigen kann.

20

Entwurf von M. Frankowski

JFET-Tester

Einfaches Testen und Selektieren

stor gegenüber dem Emitter positiv ist

und Basisstrom in die Basis hinein-

und über den Emitter abfließt, muß die

Gatespannung beim N-Kanal-JFET

immer negativ gegenüber der Span-

nung am Sourceanschluß sein, um den

Strom durch den FET - von Drain

nach Source - steuern zu können. Der

Gate-Source-Übergang (GS-Übergang)

ist denn auch gesperrt. Zwischen

Drain-Source-Strecke und dem nega-

tiven Gate bildet sich eine Sperrschicht

aus (daher auch die Bezeichnung

“Sperrschicht-FET”), die den Drain-

Source-Strom um so stärker

“abschnürt”, je negativer das Gate

wird. Im Gegensatz zum NPN-Transi-

stor fließt über das Gate im Normalfall

(= negative Gate-Sourcespannung)

kein Strom.

Im Bild 1 sind auch drei wichtige Para-

meter der Meßschaltung eingetragen:

V

GS

ist die Spannung, die zwischen

Gate und Source gemessen wird

(Gate-Source-Spannung)

V

DS

ist die Spannung, die zwischen

Drain und Source gemessen

wird

(Drain-Source-Spannung)

I

D

ist der Strom, der über den

Drainanschluß (und die Drain-

Source-Strecke) fließt

(Drainstrom)

P

I N C H

-

O F F

- S

P A N N U N G

Neben den zuvor genannten drei

Parametern ist die sogenannte Pinch-

off-Spannung (Deutsch: Abschnür-

spannung) der wichtigste Kennwert

eine Junction-FETs. Damit ist diejenige

Gate-Source-Spannung (V

GS

) gemeint,

bei der die Drain-Source-Strecke so

weit verengt (abgeschnürt) ist, daß

(praktisch) kein Drainstrom mehr

fließt. Der bei der Pinch-off-Spannung

noch fließende (Leck-)Drainstrom ist je

nach Hersteller mit 1 nA, 10 nA oder

sogar 10 µA spezifiziert. Dabei wird

von einer konstanten V

DS

ausgegan-

gen. Auch hier gibt es unterschiedliche

Festlegungen. Je nach Hersteller wird

die -V

GS(p)

bei V

DS

= 10 V oder 15 V

spezifiziert. Allerdings ergeben sich

dadurch keine allzu großen Unter-

schiede, wichtig ist, daß die V

DS

in die-

ser Größenordnung liegt und konstant

ist. Der in diesem Beitrag beschriebene

JFET-Tester mißt die Pinch-off-Span-

nung bei einem Drainstrom von 10 nA

und verwendet dabei noch nicht ein-

mal eine konstante Drain-Sourcespan-

nung - auch das geht!

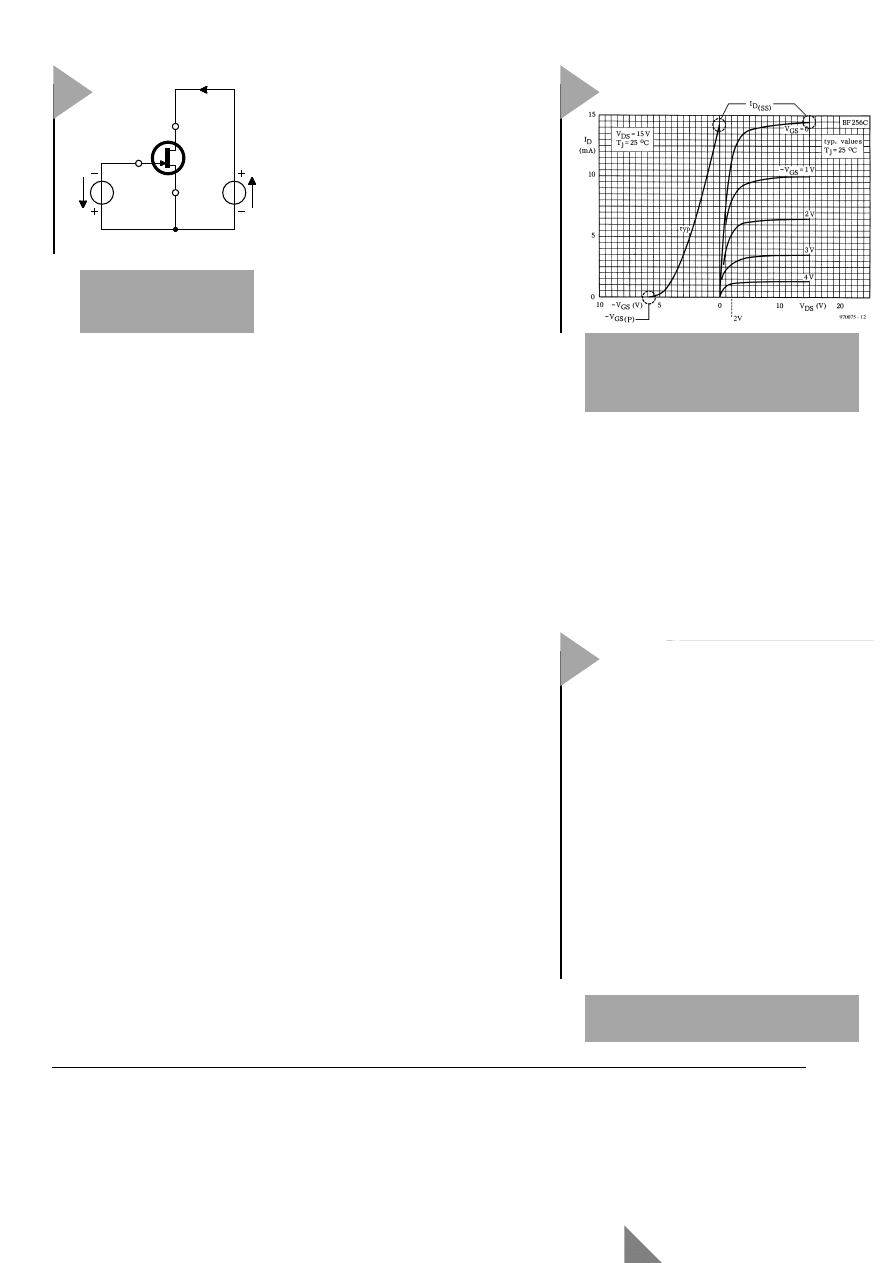

Wenn man Bild 2 näher betrachtet,

sieht man, daß die Kurve für den

Drainstrom ab einer Drain-Source-

Spannung (V

DS

) von etwa 2 V ganz

flach verläuft, wenn die V

GS

in den

Bereich starker Abschnürung (nahe

der Pinch-off-Spannung) kommt. In

Bild 2 ist dies zum Beispiel bei der I

D

-

Kurve der Fall, die für eine V

GS

von 4

V angegeben ist. Da sich bei starker

Abschnürung der Drainstrom im V

DS

-

Bereich zwischen 3 V und 15 V prak-

tisch nicht ändert, ist auch ein nicht

konstanter Wert der V

DS

bei der Mes-

sung der -V

GS(p)

ohne nennenswerten

Einfluß auf das Meßergebnis. Der kon-

stante Drainstrom bei variabler

Drainspannung ist auch der Grund

dafür, warum man Junction-FETs

gerne in Stromquellen oder Stromsen-

ken einsetzt.

D

R A I N

- S

Ä T T I G U N G S

-

S T R O M

Der zweite wichtige Parameter neben

der Pinch-off-Spannung ist der Drain-

Source-Strom bei “offenem” Kanal, das

heißt, wenn die -V

GS

bei 0 V liegt und

die V

DS

bei 15 V (üblicherweise). Der

Drainstrom steigt dann nicht mehr

weiter an, er hat seinen Sättigungswert

erreicht. Dieser Drain-Sättigungsstrom

ist mit I

D(ss)

bezeichnet. Wie Bild 3

zeigt, geht der Drainstrom mit zuneh-

mender Temperatur zurück, dies gilt

auch für den Sättigungsstrom (I

D

bei

V

GS

= 0).

P

R A K T I S C H E

T

E S T S C H A L T U N G

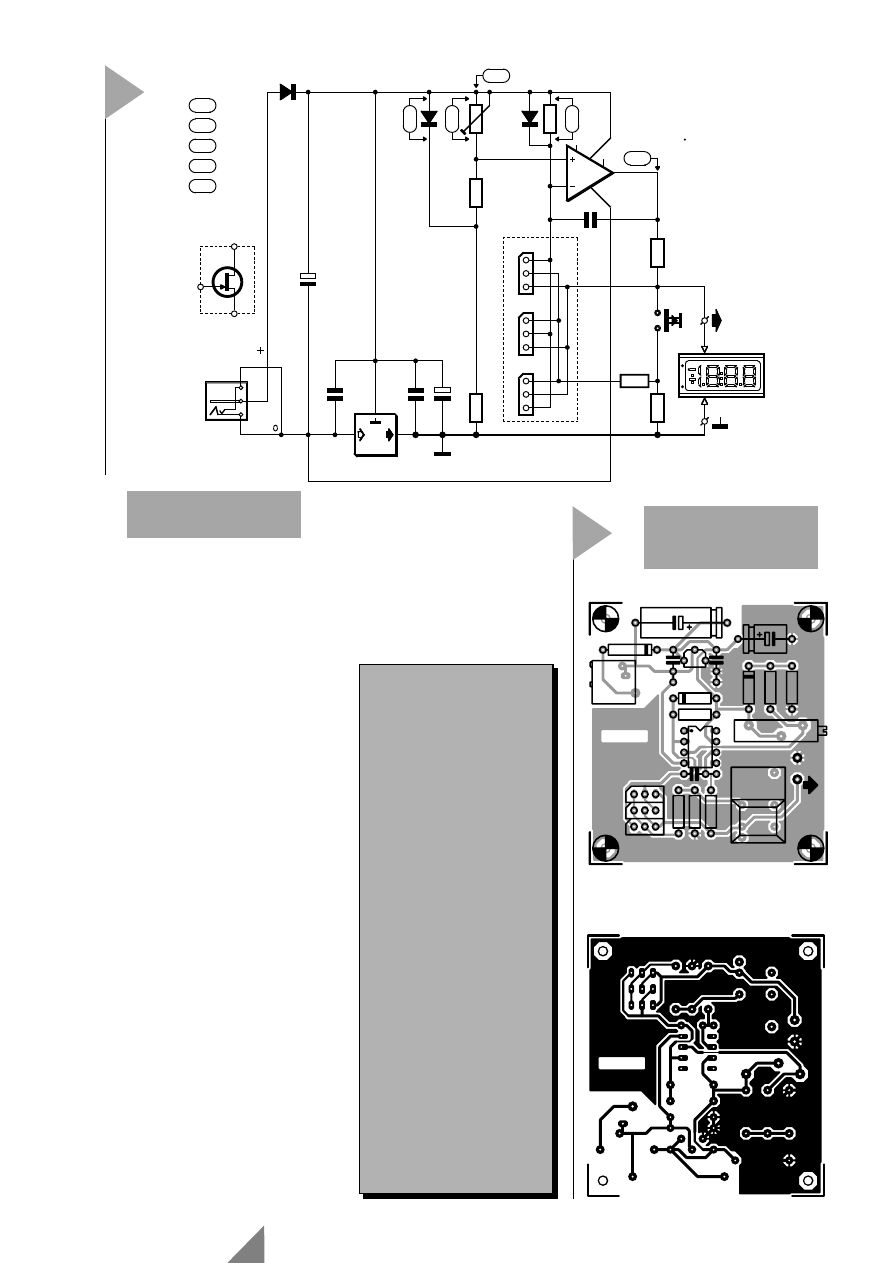

Wie Bild 4 zeigt, ist der Bau eines

JFET-Testers mit recht geringem Schal-

tungsaufwand verbunden. Wenn man

von dem DVM-Modul einmal absieht

(dafür könnte man ja auch ein Digi-

talmultimeter anschließen), besteht die

Schaltung im wesentlichen aus einem

21

Elektor

2/98

D

G

S

GS

V

V

DS

970075 - 11

I

D

1

Bild 1. Schaltsymbol

eines N-Kanal-J-FETs

und Prinzipschaltbild.

2

Bild 2. Pinch-off-Spannung und Sät-

tigungsstrom lassen sich aus die-

sem Standard-Kennlinienfeld leicht

entnehmen.

3

Bild 3. Mit höherer Temperatur

nimmt der Drainstrom ab.

Anzeige

Operationsverstärker und einem

Spannungsregler, also aus zwei sehr

preiswerten ICs. Die Funktion läßt sich

am besten anhand der Testfunktionen

beschreiben:

Pinch-off-Spannungsmessung (S1 ist

offen)

Dazu muß man sich einen an K2, K3

oder K4 richtig angeschlossenen FET

vorstellen.

Am nichtinvertierenden Eingang des

Opamps liegt eine Referenzspannung

von 100 mV. Als Referenzspannungs-

quelle dient die Diode D2, an der eine

Spannung von etwa 650 mV abfällt.

An dem parallelgeschalteten Span-

nungsteiler (P1/R2) läßt sich mit dem

Trimmpoti P1 der Wert von 100 mV

einstellen.

Der invertierende Eingang des

Opamps liegt über einen sehr hoch-

ohmigen Widerstand (R3) von 10 MΩ

an der Betriebsspannung und gleich-

zeitig auch am Drainanschluß des zu

testenden FETs, der über R5 mit seiner

Drain-Source-Strecke im Gegenkopp-

lungszweig des Opamps liegt. Der

parallelgeschaltete Kondensator C4

sorgt für eine starke Bandbreitenbe-

grenzung, damit der Opamp als

Gleichspannungsverstärker und nicht

als HF-Verstärker oder gar als Oszilla-

tor arbeitet.

Da das Gate des FETs über R4 und R6

an Masse liegt, wird das Gate auf eine

(gegenüber der Source) negative Span-

nung (-V

GS

) eingestellt. Da der Opamp

über die Gegenkopplung eine Span-

22

Elektor

2/98

IC1

79L12

C2

100n

C3

100n

C5

10

µ

63V

R1

5k6

R2

22k

R3

10M

R5

100k

R6

10

Ω

R4

100k

K1

C1

100

µ

16V

C4

1n

5k

P1

TL071

IC2

2

3

6

7

4

1

5

D1

1N4001

D2

1N4148

D3

1N4148

S1

K2

D

G

S

K3

S

K4

G

D

G

S

D

D

G

S

D

G

S

15V

5mA

A

B

C

D

E

A

12V

0V65

0V1

B

C

D

E

0V1 / 0V7

4V6 / 11V3

M 1

DVM

*

T2

zie tekst

*

see text

*

siehe Text

*

voir texte

*

0V / DVM

970075 - 14

D.U.T.

D.U.T.

4

Bild 4. Schaltbild des

J-FET-Testers.

Bild 5. Layout und

Bestückungsplan der

Platine.

970075-1

C1

C2

C3

C4

C5

D1

D2

D3

HOEKEN

HOEKEN1

HOEKEN2

HOEKEN3

IC1

IC2

K1

K2

K3

K4

OUT

P1

R1

R2

R3

R4

R5

R6

S1

d g s

g s d

g d s

0

+

T

DVM

970075-1

970075-1

5

Stückliste

Widerstände:

R1 = 5k6

R2 = 22 k

R3 = 10 M

R4,R5 = 100 k

R6 = 10

Ω (möglichst 1 %,

siehe Text)

P1 = 5 k Trimmpoti, 10-Gang-

Cermet, stehend

Kondensatoren:

C1 = 100

µ/16V

C2,C3 = 100 n

C4 = 1 n

C5 = 10

µ/63V

Halbleiter:

D1 = 1N4001

D2,D3 = 1N4148

T1 = zu testender Transistor

(N-Kanal-JFET)

IC1 = 79L12

IC2 = TL071CP

Außerdem:

M1 = DVM (siehe Text)

K2,K3,K4 = 3 Reihen mit je

drei gedrehten IC-Fassungs-

Pins

S1 = Digitaster, 1 Schließer

(ITT-Schadow).

K1 = Netzteil-Anschlußbuchse,

flache Ausführung

nungsdifferenz zwischen seinen bei-

den Eingängen auszugleichen ver-

sucht, wird die Spannung an R3 eben-

falls auf die eingestellte Referenzspan-

nung von 100 mV eingeregelt, was bei

dem Wert von 10 M

einem Strom

von nur 10 nA entspricht. Damit wird

auch der Strom über den FET auf 10

nA eingestellt (die 10 nA fließen über

R3, die Drain-Source-Strecke des FETs

und R5 in den Ausgang des Opamps).

Da kein Gatestrom fließt, fällt an den

Widerständen R4 und R6 auch ke i n e

Spannung ab, das Gate liegt daher auf

potentialmäßig auf Masse. Das zwi-

schen Source und Masse und damit

zwischen Source und Gate geschaltete

DVM zeigt somit die Spannung zwi-

schen Gate und Source an. Die so

gemessene V

G S

ist bei dem winzigen

Drain-Sourcestrom von 10 nA nichts

anderes als die Pinch-o f f- S p a n n u n g

V

G S ( p )

des FETs .

Die Fehlerquellen in dieser Messung

sind ein Leckstrom von etwa 10 pA

über D3 (parallel zu R3), ein Ein-

gangsleckstrom des TL071 (kleiner 200

pA) und die Eingangsoffsetspannung

des Opamps (kleiner 10 mV), die aber

auf die gemessene Pinch-o f f- S p a n-

nung keinen nennenswerten Einfluß

h a b e n .

Einige J- F E Ts haben sehr kleine Pinch-

o f f-Spannungen im Bereich von 0 und

-2 V. Damit auch diese FETs getestet

werden können, wurde ein Span-

nungsregler in der negativen Betriebs-

spannungsleitung vorgesehen. Durch

eine Versorgung des Opamps mit 15 V

statt mit 12 V (wie der Rest der Schal-

tung) wird der V

G S

-Bereich entspre-

chend erw e i t e r t .

Messung des Drain-Sättigungsstro m s

(S1 geschlossen)

Diese Messung ist wesentlich einfa-

c h e r. Drücken von S1 bewirkt, daß die

Source mit dem Gate verbunden ist, so

daß die V

G S

= 0 V wird. Obwohl die

Referenzspannung am nichtinvertie-

renden Eingang von IC2 100 mV

bleibt, fällt an D3 jetzt die norm a l e

Durchflußspannung von etwa 0,7 V

ab. In der Folge geht der Ausgang des

Opamps fast auf den Wert der positi-

ven Betriebsspannung. Über Wi d e r-

stand R5 fließen dann:

(12 V - 0,7 V)/100 k

Ω

= 113 A

In der Praxis werden es etwas über 100

A sein. Dieser Strom fließt auch über

R6 - zusammen mit dem I

D ( s s )

d e s

F E Ts, der sich hinzuaddiert. Da der

Drain-Sättigungsstrom im mA-Bereich

liegt, kann man den Fehler durch die

zusätzlichen 100 A vern a c h l ä s s i g e n .

Der vom DVM angezeigte mV-We r t

um den Faktor 10 höher als der I

D ( s s )

in mA. Bei einem I

D ( s s )

von 10 mA

mißt das DVM an R6 eine Spannung

von 100 mV an R6 (= 10 ). Bei einem

1 - -Widerstand für R6 wäre die Span-

nung in mV wertgleich mit dem I

D ( s s )

in mA - allerdings wäre die Au f l ö s u n g

bei einem 2-V-Meßbereich und selbst

bei einem 200-mV-Meßbereich des

DVMs nicht optimal. Wer aber ein

Digitalmultimeter mit höherer Au f l ö-

sung verwendet, kann für R6 einen 1-

-Widerstand einsetzen. In jedem Fa l l

sollte R6 ein 1-%-Widerstand sein.

Bei den im Schaltbild angegebenen

Gleichspannungswerten handelt es

sich um typische Werte. Bei zwei

Angaben zu einem Meßpunkt gilt der

erste Wert für offenen S1-Kontakt und

der zweite für geschlossenen S1-Ko n-

takt. Wenn nichts anderes eingezeich-

net ist, wird der Meßwert gegen Masse

gemessen (gilt für Meßpunkt A und

E ) .

Zur Stromversorgung wird ein einfa-

ches Stecke rnetzteil mit etwa 15 V

Gleichspannung verwendet. Die

Stromaufnahme der Schaltung ist bei

nicht gedrücktem S1 sehr gering (ca. 5

mA) und bei geschlossenem S1 nicht

viel höher als der gemessene I

D ( s s )

, also

im Bereich bis etwa 30-40 mA. Bei so

geringer Belastung liefern auch die

meisten unstabilisierten 12-V- S t e c ke r-

netzteile eine (Fa s t - ) L e e r l a u f s p a n n u n g

von 15 V, sie können dann ebenfalls

für die Stromversorgung verw e n d e t

w e r d e n .

A

U F B A U

U N D

A

B G L E I C H

Platinenlayout und Bestücku n g s p l a n

sind in Bild 5 zu finden. Beim

B e s t ü c ken liegt nichts Besonderes an,

nur auf die Polarität der Dioden und

E l kos sollte man achten. Für die zu

testenden FETs sind drei Fa s s u n g e n

(ais jeweils drei gedrehten Einzelpins)

für

FETs mit

unterschiedlicher

Anschlußbelegung vorgesehen. Es hat

keinen Zweck, die Anschlußbelegung

durch Versuch und Irrtum herausfin-

den zu wollen. Die Anschlußbelegung

muß bekannt sein - wenn nicht, muß

man in Datenbüchern nachsehen. Ein-

ziger Abgleichpunkt ist die Einstellung

des Spannungsabfalls an P1 (Meß-

punkt C) mit einem Digitalmultimeter,

6

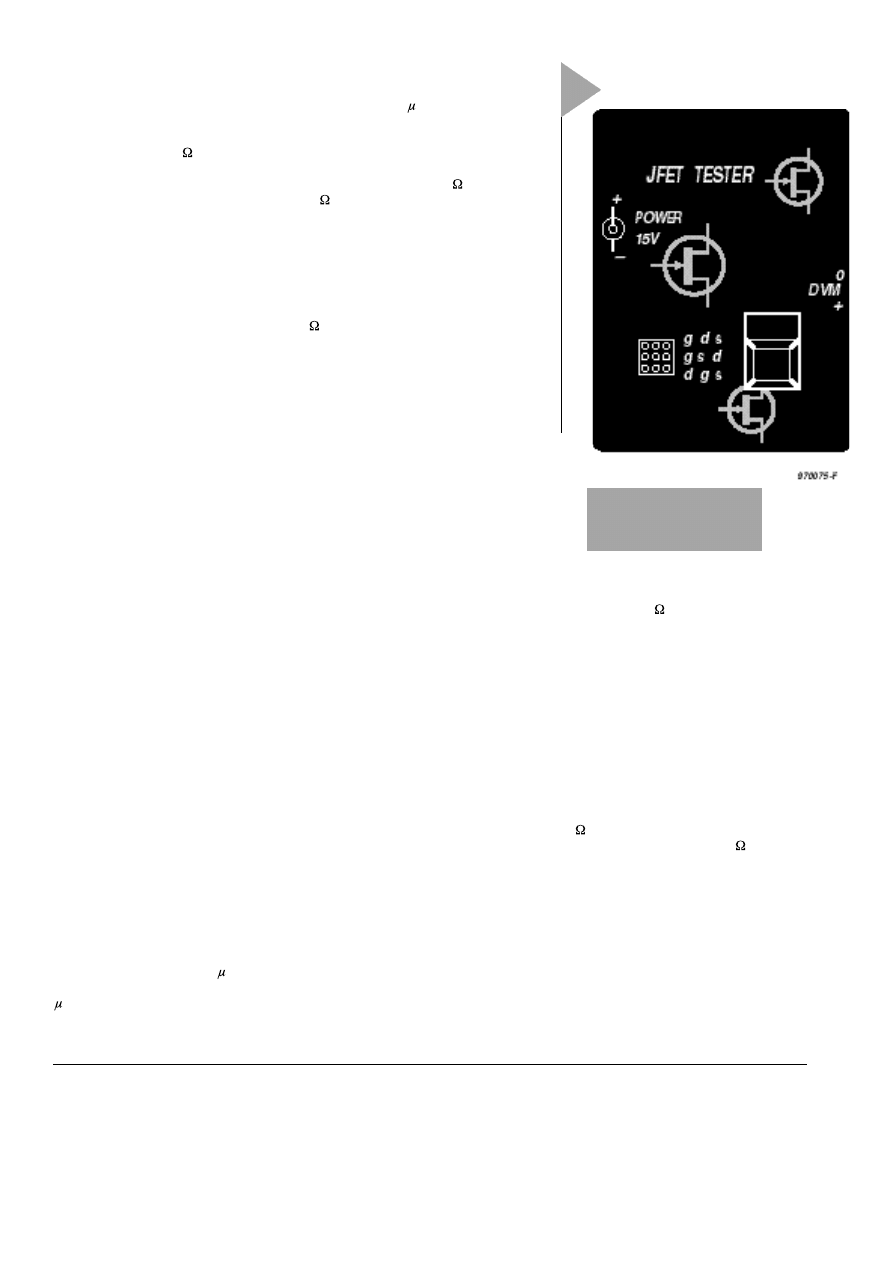

Bild 6. Vorschlag für

die Frontplattenge-

s t a l t u n g .

das den üblichen DC- E i n g a n g s w i d e r-

stand von 10 M

a u f w e i s t .

Einen Vorschlag für die Fr o n t p l a t t e n-

gestaltung zeigt Bild 6.

T

I P S

U N D

T

R I C K S

Für das Ausprobieren mit bekannten

F E Ts empfehlen sich die Typen BF245

und BF256.

Der höchste I

D ( s s )

, der mit der Schal-

tung gemessen werden kann, beträgt

etwa 40 mA. Wenn Ihr DVM bei der

Messung einen höheren Wert anzeigt,

stimmt etwas mit der Messung nicht.

Bei der Messung der 100 mV an R3 (10

M ) muß man berücksichtigen, daß

das DMM mit ebenfalls 10 M

p a r a l-

lel liegt und den Meßwert verf ä l s c h e n

k a n n .

Für das Paaren von FETs reicht die

Messung der beiden Parameter Pinch-

o f f-Spannung und Sättigungsstrom

n o rm a l e rweise gut aus. Damit lassen

sich fast identische Exemplare aus

einer größeren Menge selektieren, wie

man sie zum Beispiel für Differenz-

stufen in Au d i o- und Meßschaltungen

benötigt.

( 9 7 0 0 7 5 - 1 )

Anzeige

Wyszukiwarka

Podobne podstrony:

IC Tester, Teil 1 Schaltung und Aufbau

Laser Lichtschranke Einfach und wirkungsvoll

Einfache Spannungsanpassung fuer K6, 6x86 und MMX

Einfacher Thyristor Triac Tester

Einfacher MD Vorverstaerker

09 Absichten und Möglichkeiten (B)

Badanie tranzystorów unipolarnych typu JFET i MOSFET

Ausgewählte polnische Germanismen (darunter auch Pseudogermanismen und Regionalismen) Deutsch als F

Powerprojekte mit Arduino und C

15 Wzmacniacze Selektywne W Cz

Glottodydaktyka, Traditionelle und alternative Unterrichtsmethoden

Ich und meine?milie

109 JFET charakterystyka

2 7T Pressure Tester

Petterson Und Findus Malvorlagen Windowcolor

45 Progression Stufen der Sprachfertigkeit ( variationsloses, gelenkt varrierendes und freies Sprech

Tester diagnostyczny mega macs, nauka, Urządzenia diagnostyczne

OpisZadania TesterFiltrowDP

więcej podobnych podstron