2. Synteza układu sekwencyjnego.

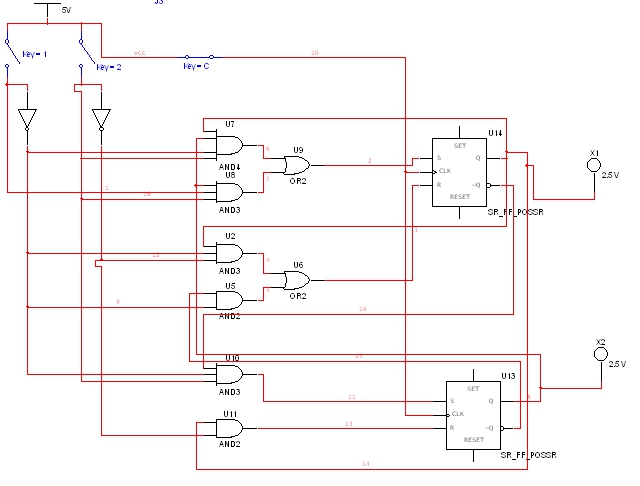

Wykorzystując przerzutniki asynchroniczne RS zaprojektować układ sekwencyjny działający zgodnie z grafem przejść i wyjść podanym przez prowadzącego.

Obliczam równania S oraz R uzupełniając wpierw tablice Karnaugha dla odzwierciedlenia grafu. Wykonuję to przyjmując, że moje Q1Q2 w tablicy to wartość z okręgu w grafie, X1X2 to wartości na strzałkach. Do tablicy wpisujemy wartość okręgu, do której Q1Q2 poprzez X1X2 wykonuje przyjście.

Q1Q2 X1X2 |

00 |

01 |

11 |

10 |

00 |

00 |

11 |

00 |

00 |

01 |

01 |

01

|

11 |

00 |

11 |

00 |

11 |

11 |

10 |

10 |

01 |

01 |

10 |

10 |

Następnie wykorzystując zbudowaną tablicę Karnaugha obliczam R1,S1, które wyznaczam biorąc pod uwagę Q1 oraz pierwszą liczbę wypełnioną w tabeli (zaznaczoną na jasno szaro), powtarzając czynność dla każdego wiersza tabeli oraz korzystając z tabeli poniżej:

Czynności te powtarzamy następnie dla Q2 oraz drugą liczbą wypełnioną w tabeli, co nam daje R2

i S2. W poniższych tabelach Karnaugha przedstawione są wyniki dla mojego grafu.

S1

Q1Q2 X1X2 |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

0 |

0 |

01 |

0 |

0

|

- |

0 |

11 |

0 |

1 |

- |

- |

10 |

0 |

0 |

- |

- |

R1

Q1Q2 X1X2 |

00 |

01 |

11 |

10 |

00 |

- |

0 |

1 |

1 |

01 |

- |

-

|

0 |

1 |

11 |

- |

0 |

0 |

0 |

10 |

- |

- |

0 |

0 |

S2

Q1Q2 X1X2 |

00 |

01 |

11 |

10 |

00 |

0 |

- |

0 |

0 |

01 |

1 |

-

|

- |

0 |

11 |

0 |

- |

- |

0 |

10 |

0 |

- |

0 |

0 |

R2

Q1Q2 X1X2 |

00 |

01 |

11 |

10 |

00 |

- |

0 |

1 |

- |

01 |

0 |

0

|

0 |

- |

11 |

- |

0 |

0 |

- |

10 |

0 |

0 |

1 |

- |

Otrzymane równania:

3. Synteza licznika asynchronicznego.

3.1. Wykorzystując przerzutniki typu JK oraz niezbędne dodatkowe elementy logiczne zbudować licznik asynchroniczny o pojemności 9.

4. Realizacja rejestru.

4.1. Wykorzystując przerzutniki typu JK oraz niezbędne dodatkowe elementy logiczne zbudować 3-bitowy rejestr równoległo-szeregowy z możliwością synchronicznego wprowadzania informacji z dwóch źródeł oraz wyprowadzania do dwóch odbiorników.

5. Synteza licznika synchronicznego.

5.1. Wykorzystując przerzutniki typu D oraz niezbędne dodatkowe elementy logiczne zbudować licznik synchroniczny działający zgodnie z podaną poniżej tabelą przejść:

Stan |

QD |

QC |

QB |

QA |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

3 |

1 |

0 |

0 |

1 |

4 |

1 |

1 |

1 |

0 |

5 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

9 |

0 |

0 |

1 |

1 |

10 |

1 |

1 |

0 |

1 |

11 |

1 |

0 |

1 |

1 |

12 |

1 |

1 |

0 |

0 |

13 |

1 |

0 |

1 |

0 |

14 |

0 |

1 |

1 |

1 |

15 |

0 |

1 |

0 |

0 |

Analizujemy i tworzymy tabele przejść dla QD, QC, QB oraz QA wg tabeli dla przerzutnika D:

QD

QBQA QDQC |

00 |

01 |

11 |

10 |

00 |

0 |

0 |

1 |

1 |

01 |

0 |

0

|

0 |

1 |

11 |

1 |

1 |

0 |

0 |

10 |

1 |

1 |

1 |

0 |

QC

QBQA QDQC |

00 |

01 |

11 |

10 |

00 |

0 |

0 |

1 |

0 |

01 |

0 |

1

|

1 |

0 |

11 |

0 |

0 |

0 |

1 |

10 |

1 |

1 |

1 |

1 |

QB

QBQA QDQC |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

0 |

0 |

01 |

0 |

1

|

0 |

0 |

11 |

1 |

1 |

1 |

0 |

10 |

1 |

1 |

0 |

1 |

QA

QBQA QDQC |

00 |

01 |

11 |

10 |

00 |

1 |

0 |

1 |

1 |

01 |

0 |

0

|

0 |

0 |

11 |

0 |

1 |

1 |

1 |

10 |

1 |

0 |

0 |

1 |

Wyszukiwarka

Podobne podstrony:

Prezentacja 18

podrecznik 2 18 03 05

9 1 18 Szkolenie dla KiDów

Lab4

Planowanie strategiczne i operac Konferencja AWF 18 X 07

Przedmiot 18 1

18 piątek

AutomatykaII 18

18 Badanie słuchu fonemowego z uzyciem testu sylab nagłosowychid 17648 ppt

18 poniedziałek

18 10 2014 (1)

18 Prowadzenie procesów jednostkowych w technologii

18 FALA TETNAid 17717 Nieznany (2)

więcej podobnych podstron