Rozdział 4.

Pamięci stałe i statyczne

Układy pamięci służą [Author ID1: at Fri Dec 14 21:09:00 2001

]D[Author ID1: at Fri Dec 14 21:09:00 2001

]d[Author ID1: at Fri Dec 14 21:09:00 2001

]o przechowywania informacji służą układy pamięci[Author ID1: at Fri Dec 14 21:09:00 2001

].[Author ID1: at Fri Dec 14 21:10:00 2001

] M[Author ID1: at Fri Dec 14 21:10:00 2001

]i m[Author ID1: at Fri Dec 14 21:10:00 2001

]ożna wśród nich wyróżnić -->następujące [Author ID1: at Sat Dec 15 14:44:00 2001

]grupy:

pamięci stałe, które nie tracą zawartości po wyłączeniu zasilania:

pamięci typu ROM (ang. Read Only Memory), produkowane z

,[Author ID1: at Fri Dec 14 21:11:00 2001 ]pamięci typu PROM (ang. Programmabl[Author ID1: at Fri Dec 14 22:00:00 2001 ]e Read Only Memory), które mogą być jednokrotnie zaprogramowane przez użytkownika;[Author ID1: at Fri Dec 14 21:12:00 2001 ]

,[Author ID1: at Fri Dec 14 21:12:00 2001 ]pamięci typu EPROM (ang. Erasable Programm

b[Author ID1: at Fri Dec 14 22:01:00 2001 ]ab[Author ID1: at Fri Dec 14 22:01:00 2001 ]le Read Only Memory), które mogą być wielokrotnie programowane, jednak przedtem należy skasować ich zawartość przez naświetlenie promieniami UV;[Author ID1: at Fri Dec 14 21:47:00 2001 ],[Author ID1: at Fri Dec 14 21:47:00 2001 ]pamięci typu EEPROM lub E2PROM (ang. Electrically Erasable Programm

b[Author ID1: at Fri Dec 14 22:01:00 2001 ]ab[Author ID1: at Fri Dec 14 22:02:00 2001 ]le Read Only Memory), które różnią się od pamięci EPROM tym, że kasowanie jest sterowane elektrycznie i nie wymaga naświetlania;pamięci o swobodnym dostępie RAM (ang. Random Access Memory), które tracą zawartość po wyłączeniu zasilania:

pamięci statyczne SRAM (ang. Static Random Access Memory), nie wymagające odświeżania, charakteryzujące się krótszym czasem dostępu, ale też mniejszą pojemnością i wyższą ceną;[Author ID1: at Fri Dec 14 22:06:00 2001 ]

,[Author ID1: at Fri Dec 14 22:06:00 2001 ]pamięci dynamiczne DRAM (ang. Dynamic Random Access Memory), które wymagają złożonych układów sterujących i mają dłuższy czas dostępu, ale za to mają większą pojemność i są tańsze;[Author ID1: at Fri Dec 14 22:06:00 2001 ]

,[Author ID1: at Fri Dec 14 22:06:00 2001 ]pamięci pseudostatyczne PRAM (ang. Pseudostatic Random Access Memory), mające wewnętrzną strukturę pamięci dynamicznej, ale na zewnątrz zachowujące się jak pamięć statyczna.

Cechą każdego układu pamięci jest tzw. organizacja. Określa ona liczbę słów pamiętanych przez układ oraz długość pojedynczego słowa wyrażoną w bitach. Organizację konkretnego układu pamięci można łatwo ustalić, biorąc pod uwagę wyprowadzenia adresowe i wyprowadzenia [Author ID1: at Fri Dec 14 22:10:00 2001

]danych. Jeżeli liczba wejść adresowych wynosi n, a liczba wejść-wyjść danych —[Author ID1: at Fri Dec 14 22:11:00 2001

]-[Author ID1: at Fri Dec 14 22:11:00 2001

] w, to pamięć ma organizację 2n [Author ID1: at Sat Dec 15 14:22:00 2001

]× [Author ID1: at Sat Dec 15 14:22:00 2001

]w. Wyjątkiem od tej reguły są dynamiczne pamięci RAM, w których liczba wejść adresowych jest zazwyczaj dwukrotnie mniejsza, niż wynikałoby to z liczby słów w układzie pamięci.

Pamięci PROM i EPROM oraz pamięci statyczne mają niemal identyczne zasady stosowania. Pamięci dynamiczne natomiast wymagają odmiennych, specyficznych technik konstrukcyjnych i dlatego został im poświęcony osobny rozdział.

Pamięci PROM

Pamięci typu PROM mogą mieć pojemność od 32 [Author ID1: at Fri Dec 14 22:17:00 2001

]× [Author ID1: at Fri Dec 14 22:17:00 2001

]8 bitów do 1 [Author ID1: at Sat Dec 15 15:04:00 2001

]024 [Author ID1: at Fri Dec 14 22:18:00 2001

]× [Author ID1: at Fri Dec 14 22:18:00 2001

]8 lub 2 [Author ID1: at Sat Dec 15 15:04:00 2001

]048 [Author ID1: at Fri Dec 14 22:18:00 2001

]× [Author ID1: at Fri Dec 14 22:18:00 2001

]4 bity[Author ID1: at Sat Dec 15 15:06:00 2001

]ó[Author ID1: at Sat Dec 15 15:06:00 2001

]w[Author ID1: at Sat Dec 15 15:05:00 2001

]. Wyjścia układów pamięci są najczęściej trójstanowe albo z otwartym kolektorem, dzięki czemu można je łatwo podłączać do magistral w systemach mikroprocesorowych. Każdy układ ma co najmniej jedno wejście bramkujące CS (ang. Chip Select) lub CE (ang. Chip Enable), aktywne w [Author ID1: at Fri Dec 14 22:19:00 2001

]stani[Author ID1: at Fri Dec 14 22:19:00 2001

]em[Author ID1: at Fri Dec 14 22:19:00 2001

] wysokim lub niskim. Stan nieaktywny na tym wejściu powoduje w układach z wyjściami trójstanowymi[Author ID1: at Fri Dec 14 22:20:00 2001

] przejście wyjść w stan wysokiej impedancji, natomiast[Author ID1: at Fri Dec 14 22:22:00 2001

]zaś[Author ID1: at Fri Dec 14 22:22:00 2001

] w układach z wyjściem z otwartym kolektorem - [Author ID1: at Fri Dec 14 22:23:00 2001

]pozostawia[Author ID1: at Fri Dec 14 22:23:00 2001

]enie[Author ID1: at Fri Dec 14 22:23:00 2001

] wyjścia[Author ID1: at Fri Dec 14 22:23:00 2001

]ć[Author ID1: at Fri Dec 14 22:23:00 2001

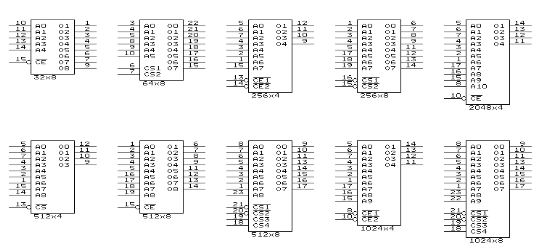

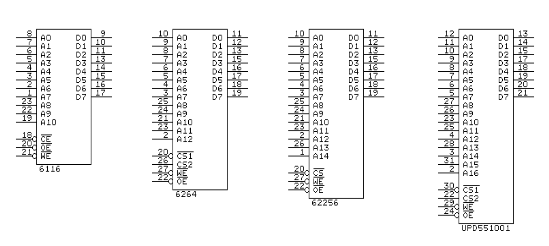

] w stanie „1”. Jeżeli układ ma kilka wejść bramkujących, to wszystkie muszą być aktywne, aby można było odczytać zawartość pamięci. Wyprowadzenia pamięci PROM o różnych organizacjach ilustruje rysunek 4.1[Author ID1: at Fri Dec 14 22:24:00 2001

] [Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

]Rysunek [Author ID1: at Fri Dec 14 22:24:00 2001

]1[Author ID1: at Fri Dec 14 22:24:00 2001

][Author ID1: at Fri Dec 14 22:24:00 2001

].

Rysunek 4.1. [Author ID1: at Fri Dec 14 22:25:00 2001

][Author ID1: at Fri Dec 14 22:25:00 2001

][Author ID1: at Fri Dec 14 22:25:00 2001

][Author ID1: at Fri Dec 14 22:25:00 2001

]1[Author ID1: at Fri Dec 14 22:25:00 2001

][Author ID1: at Fri Dec 14 22:25:00 2001

]. [Author ID1: at Fri Dec 14 22:25:00 2001

]Wyprowadzenia układów pamięci PROM

Pamięci PROM są produkowane przez wiele firm. Niestety,[Author ID1: at Fri Dec 14 22:26:00 2001

] oznaczenia stosowane przez poszczególne firmy nie są zgodne ze sobą. Przykładowo, układy firmy AMD mają przedrostek 27S, Texas Instruments —[Author ID1: at Fri Dec 14 22:26:00 2001

]-[Author ID1: at Fri Dec 14 22:26:00 2001

] 74S, Signetics —[Author ID1: at Fri Dec 14 22:26:00 2001

]-[Author ID1: at Fri Dec 14 22:26:00 2001

] 82S, a Intel —[Author ID1: at Fri Dec 14 22:26:00 2001

]-[Author ID1: at Fri Dec 14 22:26:00 2001

] 36. Oznaczenia niektórych układów PROM o różnych organizacjach i typach wyjść zebrano

-->

w tabeli 1.[Author:EK]

[Author ID1: at Fri Dec 14 22:35:00 2001

]

Ze względu na stosunkowo nieduże pojemności i krótki czas dostępu, pamięci PROM stosuje się w układach dekoderów adresów lub w [Author ID1: at Fri Dec 14 22:41:00 2001

]innych układach kombinacyjnych, których realizacja w[Author ID1: at Sat Dec 15 18:27:00 2001

] oparta[Author ID1: at Sat Dec 15 18:27:00 2001

]ciu[Author ID1: at Sat Dec 15 18:27:00 2001

] na[Author ID1: at Sat Dec 15 18:27:00 2001

]o[Author ID1: at Sat Dec 15 18:27:00 2001

] bramkach[Author ID1: at Sat Dec 15 18:27:00 2001

]i[Author ID1: at Sat Dec 15 18:27:00 2001

] TTL,[Author ID1: at Fri Dec 14 22:39:00 2001

] lub nawet na [Author ID1: at Sat Dec 15 18:27:00 2001

]bardziej złożonych[Author ID1: at Sat Dec 15 18:27:00 2001

]e[Author ID1: at Sat Dec 15 18:27:00 2001

] układach[Author ID1: at Sat Dec 15 18:27:00 2001

]y[Author ID1: at Sat Dec 15 18:27:00 2001

] (demultiplekserach[Author ID1: at Sat Dec 15 18:27:00 2001

]y[Author ID1: at Sat Dec 15 18:27:00 2001

], komparatorach[Author ID1: at Sat Dec 15 18:28:00 2001

]y[Author ID1: at Sat Dec 15 18:28:00 2001

] itp.),[Author ID1: at Fri Dec 14 22:39:00 2001

] byłaby zbyt trudna. Przykładem może być

-->

dekoder kodu dwójkowego na kod wyświetlacza 7-segmentowego pozwalający na wyświetlanie cyfr szesnastkowych[Author:EK]

[Author ID1: at Fri Dec 14 23:12:00 2001

] lub dekoder rodzaju cyklu maszynowego mikroprocesora Z-[Author ID1: at Fri Dec 14 22:43:00 2001

]80.

Pamięci EPROM

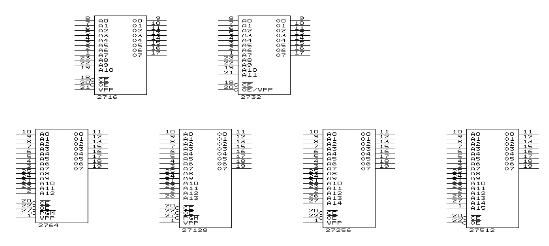

Pamięci EPROM mają najczęściej organizację 8- lub 16-bitową i pojemności od 2 [Author ID1: at Fri Dec 14 23:30:00 2001

]048 [Author ID1: at Fri Dec 14 23:15:00 2001

]× [Author ID1: at Fri Dec 14 23:15:00 2001

]8 (2K [Author ID1: at Fri Dec 14 23:16:00 2001

]× [Author ID1: at Fri Dec 14 23:16:00 2001

]8) do 65 [Author ID1: at Fri Dec 14 23:30:00 2001

]536 [Author ID1: at Fri Dec 14 23:16:00 2001

]× [Author ID1: at Fri Dec 14 23:16:00 2001

]8 (64K [Author ID1: at Fri Dec 14 23:16:00 2001

]× [Author ID1: at Fri Dec 14 23:16:00 2001

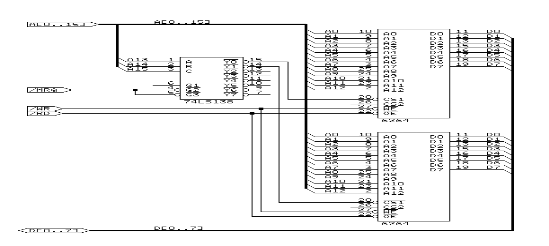

]8). Wszystkie układy mają wyjścia trójstanowe. Oprócz wejść adresowych i wyjść danych układy posiadają także wejścia sterujące. Podczas normalnej pracy układu wykorzystywane jest wejście ![]()

(ang. Chip Enable) oraz ![]()

(ang. Output Enable), oba aktywne w [Author ID1: at Fri Dec 14 23:31:00 2001

]stani[Author ID1: at Fri Dec 14 23:31:00 2001

]em[Author ID1: at Fri Dec 14 23:31:00 2001

] niskim. Jeżeli na wejściu ![]()

jest „0”, to układ dekoduje stan wejść adresowych w celu „znalezienia” żądanej komórki pamięci. Jednakże zawartość tej komórki jest podawana na wyjścia danych dopiero wtedy, gdy na wejściu ![]()

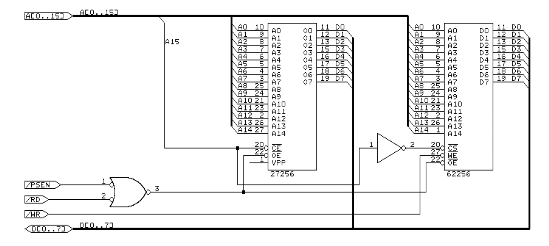

jest również „0”. Wyprowadzenia układów pamięci EPROM ilustruje rysunek 4.2[Author ID1: at Fri Dec 14 23:32:00 2001

] [Author ID1: at Fri Dec 14 23:32:00 2001

][Author ID1: at Fri Dec 14 23:32:00 2001

][Author ID1: at Fri Dec 14 23:32:00 2001

][Author ID1: at Fri Dec 14 23:32:00 2001

][Author ID1: at Fri Dec 14 23:32:00 2001

]Rysunek [Author ID1: at Fri Dec 14 23:32:00 2001

]2[Author ID1: at Fri Dec 14 23:32:00 2001

][Author ID1: at Fri Dec 14 23:32:00 2001

]. Warto zauważyć, że rozkład wyprowadzeń umożliwia zastosowanie układu o większej pojemności bez znaczących zmian w układzie.

Rysunek 4.2. [Author ID1: at Fri Dec 14 23:33:00 2001

][Author ID1: at Fri Dec 14 23:33:00 2001

][Author ID1: at Fri Dec 14 23:33:00 2001

][Author ID1: at Fri Dec 14 23:33:00 2001

]2[Author ID1: at Fri Dec 14 23:33:00 2001

][Author ID1: at Fri Dec 14 23:33:00 2001

]. [Author ID1: at Fri Dec 14 23:33:00 2001

]Wyprowadzenia układów pamięci EPROM

Pamięci EPROM są obecnie stosowane najczęściej jako pamięć programu. Oczywiście mogą one także przechowywać duże obszary danych, np. wzorce znaków do wyświetlania lub parametry sterowanego obiektu.

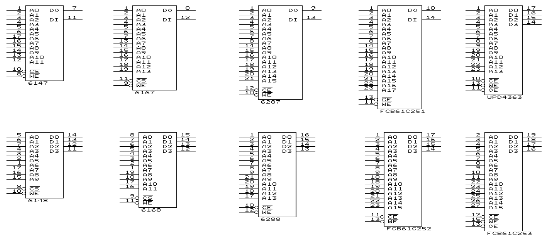

Pamięci statyczne RAM

Pierwsze pamięci statyczne RAM miały organizację 1- i 4-bitową, natomiast obecnie najczęściej stosuje się układy o organizacji 8-bitowej. Pojemność pamięci wynosi od 4K [Author ID1: at Fri Dec 14 23:33:00 2001

]× [Author ID1: at Fri Dec 14 23:33:00 2001

]1 do 256K [Author ID1: at Fri Dec 14 23:34:00 2001

]× [Author ID1: at Fri Dec 14 23:34:00 2001

]1, od 1K [Author ID1: at Fri Dec 14 23:34:00 2001

]× [Author ID1: at Fri Dec 14 23:34:00 2001

]4 do 64K [Author ID1: at Fri Dec 14 23:34:00 2001

]× [Author ID1: at Fri Dec 14 23:34:00 2001

]4 lub od 2K [Author ID1: at Fri Dec 14 23:34:00 2001

]× [Author ID1: at Fri Dec 14 23:34:00 2001

]8 do 128K [Author ID1: at Fri Dec 14 23:34:00 2001

]× [Author ID1: at Fri Dec 14 23:34:00 2001

]8. Pamięci o organizacji 1-bitowej mają rozdzielone wejście i wyjście danych. Pozostałe układy mają dwukierunkowe linie wejścia-wyjścia danych, przy czym wyjścia te są trójstanowe. Wszystkie układy mają wejście ![]()

(ang. Chip Enable) oraz ![]()

(ang. Write Enable), oba aktywne w [Author ID1: at Fri Dec 14 23:36:00 2001

]stani[Author ID1: at Fri Dec 14 23:36:00 2001

]em[Author ID1: at Fri Dec 14 23:36:00 2001

] niskim. Niektóre układy pamięci statycznych mają ponadto wejście ![]()

(ang. Output Enable) aktywne w [Author ID1: at Fri Dec 14 23:36:00 2001

]stani[Author ID1: at Fri Dec 14 23:36:00 2001

]em[Author ID1: at Fri Dec 14 23:36:00 2001

] niskim. Jeżeli układ posiada więcej niż jedno wejście CE, to każde z nich musi być w stanie aktywnym, aby było możliwe wykonanie operacji na pamięci. Operacją tą może być odczyt lub zapis. Jeżeli układ nie ma wejścia ![]()

, to odczyt jest możliwy, jeżeli [Author ID1: at Fri Dec 14 21:05:00 2001

] [Author ID1: at Fri Dec 14 21:05:00 2001

]![]()

[Author ID1: at Fri Dec 14 23:38:00 2001

]= [Author ID1: at Fri Dec 14 23:38:00 2001

]„0” i ![]()

[Author ID1: at Fri Dec 14 23:38:00 2001

]= [Author ID1: at Fri Dec 14 23:38:00 2001

]„1”; zapis następuje, gdy oba te sygnały są w stanie „0”. W układach wyposażonych w sygnał ![]()

stan niski na wejściach ![]()

i ![]()

powoduje odczyt, a na wejściach ![]()

[Author ID1: at Sat Dec 15 14:19:00 2001

]i ![]()

—[Author ID1: at Fri Dec 14 23:38:00 2001

]-[Author ID1: at Fri Dec 14 23:38:00 2001

] zapis.

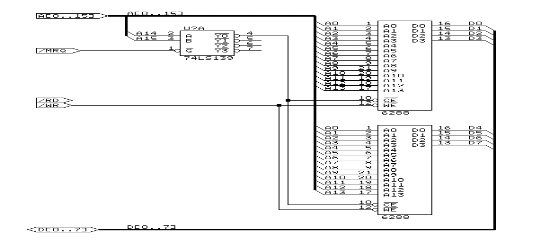

Rozkład wyprowadzeń układów pamięci statycznej RAM o organizacji 1- i 4-bitowej ilustruje rysunek 4.3.[Author ID1: at Fri Dec 14 23:40:00 2001

][Author ID1: at Fri Dec 14 23:39:00 2001

][Author ID1: at Fri Dec 14 23:39:00 2001

][Author ID1: at Fri Dec 14 23:39:00 2001

][Author ID1: at Fri Dec 14 23:39:00 2001

]Rysunek [Author ID1: at Fri Dec 14 23:39:00 2001

]3[Author ID1: at Fri Dec 14 23:39:00 2001

][Author ID1: at Fri Dec 14 23:39:00 2001

].[Author ID1: at Fri Dec 14 23:39:00 2001

]

Rysunek 4.3. [Author ID1: at Fri Dec 14 23:40:00 2001

][Author ID1: at Fri Dec 14 23:40:00 2001

][Author ID1: at Fri Dec 14 23:40:00 2001

][Author ID1: at Fri Dec 14 23:40:00 2001

]3[Author ID1: at Fri Dec 14 23:40:00 2001

][Author ID1: at Fri Dec 14 23:40:00 2001

]. [Author ID1: at Fri Dec 14 23:40:00 2001

]Wyprowadzenia układów pamięci [Author ID1: at Fri Dec 14 21:05:00 2001

] [Author ID1: at Fri Dec 14 21:05:00 2001

] [Author ID1: at Fri Dec 14 21:05:00 2001

]statycznej RAM o organizacji 1- i 4-bitowej

Rozkład wyprowadzeń układów pamięci statycznej RAM o organizacji 8-bitowej ilustruje rysunek 4.4.[Author ID1: at Fri Dec 14 23:41:00 2001

] [Author ID1: at Fri Dec 14 23:41:00 2001

][Author ID1: at Fri Dec 14 23:41:00 2001

][Author ID1: at Fri Dec 14 23:41:00 2001

][Author ID1: at Fri Dec 14 23:41:00 2001

]Rysunek [Author ID1: at Fri Dec 14 23:41:00 2001

]4[Author ID1: at Fri Dec 14 23:41:00 2001

][Author ID1: at Fri Dec 14 23:41:00 2001

].[Author ID1: at Fri Dec 14 23:41:00 2001

]

Układy pamięci statycznej stosuje się jako pamięć danych w układach mikroprocesorowych. Układy pamięci m[Author ID1: at Fri Dec 14 23:42:00 2001

]M[Author ID1: at Fri Dec 14 23:42:00 2001

]ogą też być wykorzystywane jako pamięć programu, jednak wówczas system musi zawierać też pamięć stałą. W pamięci tej zawarty jest fragment oprogramowania, który wczytuje do pamięci RAM program użytkowy.

W dużych systemach mikroprocesorowych pamięci statyczne stosowane są jako pamięci podręczne mikroprocesorów, podczas gdy główna pamięć takiego systemu jest pamięcią dynamiczną. Dzięki takiemu rozwiązaniu możliwe jest wyposażenie układu we względnie tanią pamięć dynamiczną o dużej pojemności przy jednoczesnym zachowaniu wysokiej efektywności pamięci statycznej. Efektywność ta zwiększa się podczas wielokrotnego wykonywania małych fragmentów programu lub podczas wielokrotnych odwołań do tych samych obszarów danych.

Rysunek 4.4. [Author ID1: at Fri Dec 14 23:44:00 2001

][Author ID1: at Fri Dec 14 23:44:00 2001

][Author ID1: at Fri Dec 14 23:44:00 2001

][Author ID1: at Fri Dec 14 23:44:00 2001

]4[Author ID1: at Fri Dec 14 23:44:00 2001

][Author ID1: at Fri Dec 14 23:44:00 2001

]. [Author ID1: at Fri Dec 14 23:44:00 2001

]Wyprowadzenia układów pamięci statycznej RAM o organizacji 8-bitowej

Konstrukcja modułów pamięci

Dostępne scalone układy pamięcie[Author ID1: at Fri Dec 14 23:47:00 2001

], jakkolwiek liczne, bardzo rzadko w pełni zaspokajają potrzeby konstruktorów systemów jeśli chodzi o organizację projektowanego modułu pamięci. Zarówno liczba słów, jak i długość słowa, mogą okazać się niewystarczające. Należy wówczas odpowiednio połączyć układy pamięci, aby uzyskać pożądaną organizację modułu. Techniki te umożliwiają:

zwiększenie liczby słów w pamięci,

zwiększenie długości słowa,

zwiększenie liczby słów i długości słowa pamięci.

Wymienione techniki stanowią podstawę konstrukcji modułów pamięci i są wykorzystane w przykładach.

Przykłady

Przykład 1.[Author ID1: at Fri Dec 14 23:47:00 2001 ]

Zaprojektować moduł pamięci statycznej RAM o pojemności 16K [Author ID1: at Fri Dec 14 23:47:00 2001

]× [Author ID1: at Fri Dec 14 23:47:00 2001

]8 dla mikroprocesora Z-80. Do budowy układu należy [Author ID1: at Sun Dec 16 23:16:00 2001

]wykorzystać układy pamięci o organizacji 8K [Author ID1: at Fri Dec 14 23:47:00 2001

]× [Author ID1: at Fri Dec 14 23:48:00 2001

]8 i 16K [Author ID1: at Fri Dec 14 23:48:00 2001

]× [Author ID1: at Fri Dec 14 23:48:00 2001

]4. Pamięć powinna zajmować adresy 0000 - [Author ID1: at Fri Dec 14 23:48:00 2001

]-[Author ID1: at Fri Dec 14 23:48:00 2001

]3FFFh.

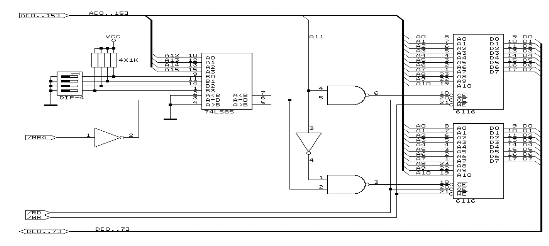

W przypadku zastosowania pamięci o organizacji 8K [Author ID1: at Fri Dec 14 23:48:00 2001

]× [Author ID1: at Fri Dec 14 23:48:00 2001

]8 należy zastosować technikę zwiększania liczby słów, ponieważ długość słowa pamięci jest równa szerokości magistrali danych. Linie danych łączy się do wspólnej magistrali, a [Author ID1: at Fri Dec 14 21:05:00 2001

] [Author ID1: at Fri Dec 14 21:05:00 2001

]wejścia adresowe należy dołączyć do magistrali adresowej. Po tej operacji pozostają trzy najstarsze bity adresu. Należy je wykorzystać do wyboru jednego z dwóch przyłączonych układów pamięci. W celu spełnienia tego zadania należy je podłączyć do wejść adresowych demultipleksera 74138. Demultiplekser powinien być aktywny tylko wtedy, gdy mikroprocesor żąda dostępu do przestrzeni adresowej pamięci (sygnał ![]()

[Author ID1: at Fri Dec 14 23:49:00 2001

]= [Author ID1: at Fri Dec 14 23:49:00 2001

]„0”). Jeden z układów pamięci (sterowany wyjściem ![]()

[Author ID1: at Fri Dec 14 23:50:00 2001

]układu 74138) zajmuje pierwszą połowę wyznaczonej przestrzeni adresowej, tj. zakres 0000 - [Author ID1: at Fri Dec 14 23:50:00 2001

]-[Author ID1: at Fri Dec 14 23:50:00 2001

]1FFFh, drugi natomiast (sterowany wyjściem ![]()

) —[Author ID1: at Fri Dec 14 23:50:00 2001

]-[Author ID1: at Fri Dec 14 23:50:00 2001

] 2000 - [Author ID1: at Fri Dec 14 23:50:00 2001

]-[Author ID1: at Fri Dec 14 23:50:00 2001

]3FFFh. W zależności od tego, czy procesor przeprowadza odczyt czy zapis pamięci, należy odpowiednio uaktywnić sygnał ![]()

lub ![]()

pamięci. Sygnał ten może być aktywny w obu układach, ponieważ co najwyżej jeden z nich jest włączony.

--> Rysunek 4.5.[Author ID1: at Fri Dec 14 23:51:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 13:46:00 2001 ][Author ID1: at Fri Dec 14 23:51:00 2001 ]

W przypadku zastosowania pamięci o organizacji 16K [Author ID1: at Sat Dec 15 13:49:00 2001

]× [Author ID1: at Sat Dec 15 13:49:00 2001

]4 należy zastosować technikę zwiększania długości słowa, ponieważ liczba słów pamięci jest wystarczająca. Linie danych łączy się do magistrali w ten sposób, że jeden układ pamięci jest dołączony do bardziej znaczącej połowy magistrali, a drugi —[Author ID1: at Sat Dec 15 13:50:00 2001

]-[Author ID1: at Sat Dec 15 13:50:00 2001

] do mniej znaczącej. Wejścia adresowe należy dołączyć do magistrali adresowej. Po tej operacji pozostają dwa najstarsze bity adresu. Należy je wykorzystać do uaktywnienia obu układów pamięci, ponieważ mikroprocesor Z-80 operuje na danych 8-bitowych. Podczas operacji odczytu aktywny jest tylko sygnał ![]()

[Author ID1: at Sat Dec 15 14:17:00 2001

]w obu układach, natomiast podczas operacji zapisu —[Author ID1: at Sat Dec 15 13:51:00 2001

]-[Author ID1: at Sat Dec 15 13:51:00 2001

] sygnały ![]()

i ![]()

. Wykorzystanie pozostałych wyjść demultipleksera 74139 umożliwia powiększenie modułu pamięci do 64 KB (4 [Author ID1: at Sat Dec 15 13:52:00 2001

]× [Author ID1: at Sat Dec 15 13:52:00 2001

]16 KB).

Przykład 2.[Author ID1: at Sat Dec 15 13:52:00 2001 ]

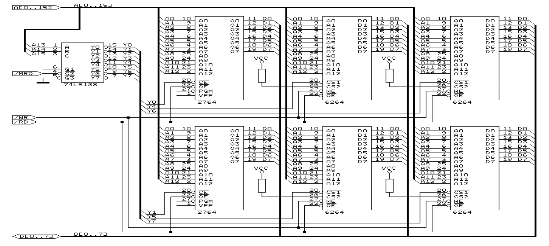

Zaprojektować moduł pamięci statycznej RAM o pojemności 16K [Author ID1: at Sat Dec 15 13:56:00 2001

]× [Author ID1: at Sat Dec 15 13:56:00 2001

]8 dla mikroprocesora Z-80. Do budowy układu należy [Author ID1: at Sun Dec 16 23:16:00 2001

]wykorzystać układy pamięci o organizacji 16K [Author ID1: at Sat Dec 15 13:56:00 2001

]× [Author ID1: at Sat Dec 15 13:56:00 2001

]1. Pamięć powinna zajmować adresy C000 - [Author ID1: at Sat Dec 15 13:56:00 2001

]-[Author ID1: at Sat Dec 15 13:56:00 2001

]FFFFh.

Ponieważ moduły pamięci o organizacji 16K [Author ID1: at Sat Dec 15 13:57:00 2001

]× [Author ID1: at Sat Dec 15 13:57:00 2001

]1 mają rozdzielone wejście i wyjście danych, proste dołączenie ich do magistrali danych nie gwarantuje poprawnej pracy układu. Pamięci te nie mają osobnego wejścia odczytu (![]()

). Jeżeli zatem na wejściu ![]()

jest stan wysoki, a na wejściu ![]()

niski, to pamięć wykonuje cykl odczytu. W większości mikroprocesorów (np. Z-80) sygnał zapisu [Author ID1: at Fri Dec 14 21:05:00 2001

] [Author ID1: at Fri Dec 14 21:05:00 2001

](![]()

) jest jednak generowany z pewnym opóźnieniem w stosunku do chwili wysłania danych na magistralę. Może się więc zdarzyć w cyklu zapisu, że pamięć rozpocznie już operację odczytu i wyśle dane na magistralę, gdy mikroprocesor dopiero uaktywni sygnał ![]()

. W najlepszym przypadku takie „zderzenie” sygnałów na magistrali danych spowoduje tylko zakłócenia, w najgorszym —[Author ID1: at Sat Dec 15 14:07:00 2001

]-[Author ID1: at Sat Dec 15 14:07:00 2001

] możliwe jest nawet spalenie wyjść układów pamięci lub mikroprocesora.

--> Rysunek 4.6. [Author ID1: at Sat Dec 15 14:08:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 14:08:00 2001 ][Author ID1: at Sat Dec 15 14:08:00 2001 ]

Aby zapobiec niekorzystnym zjawiskom na magistrali stosuje się bufor 8216, przeznaczony specjalnie do sprzęgania dwukierunkowych magistral danych z pamięciami o rozdzielonych wejściach i wyjściach. Jest on wyposażony w cztery linie dwukierunkowe (D0 - [Author ID1: at Sat Dec 15 14:10:00 2001

]-[Author ID1: at Sat Dec 15 14:10:00 2001

]D4), czetry wyjściowe (DO0 - [Author ID1: at Sat Dec 15 14:10:00 2001

]-[Author ID1: at Sat Dec 15 14:10:00 2001

]DO4) i cztery wejściowe (DI0 - [Author ID1: at Sat Dec 15 14:10:00 2001

]-[Author ID1: at Sat Dec 15 14:10:00 2001

]DI4) [Author ID1: at Sat Dec 15 14:16:00 2001

]. Ponadto zawiera wejście bramkujące ![]()

oraz wejście wyboru kierunku ![]()

(ang. Data Input Enable), oba aktywne stanem niskim. Jeżeli ![]()

[Author ID1: at Sat Dec 15 14:10:00 2001

]= [Author ID1: at Sat Dec 15 14:10:00 2001

]„1”, to wyjścia danych (jedno- [Author ID1: at Sat Dec 15 14:11:00 2001

]i dwukierunkowe) układu są w stanie wysokiej impedancji. W przeciwnym przypadku kierunek przesyłu danych zależy od stanu wejścia wyboru kierunku: jeżeli ![]()

[Author ID1: at Sat Dec 15 14:11:00 2001

]= [Author ID1: at Sat Dec 15 14:11:00 2001

]„0”, to układ przekazuje dane z wejść DI na odpowiadające im linie D, gdy natomiast ![]()

[Author ID1: at Sat Dec 15 14:11:00 2001

]= [Author ID1: at Sat Dec 15 14:11:00 2001

]„1”, stan linii D powielany jest na wyjściach DO. Dlatego też wyjścia DO bufora należy połączyć z wejściami DI układów pamięci, zaś wejścia DI bufora —[Author ID1: at Sat Dec 15 14:12:00 2001

]-[Author ID1: at Sat Dec 15 14:12:00 2001

] z wyjściami DO pamięci.

Ponieważ magistrala mikroprocesora Z-80 jest 8-bitowa, a pojedynczy bufor 8216 jest w stanie przesłać tylko cztery bity, do konstrukcji modułu potrzebne są dwa takie układy, z których każdy „obsługuje” cztery układy pamięci. Oba bufory, jak również wszystkie układy pamięci, powinny być uaktywnione tylko wówczas, gdy mikroprocesor żąda dostępu do przestrzeni adresowej pamięci (sygnał ![]()

w stanie niskim), o ile adres na magistrali zawiera się w założonym przedziale C000 - [Author ID1: at Sat Dec 15 14:13:00 2001

]-[Author ID1: at Sat Dec 15 14:13:00 2001

]FFFFh. Spełnienie obu warunków sprawdzane jest w demultiplekserze 74139, którego wejścia adresowe A i B dołączone są do bitów A14 i A15 magistrali adresowej, a wejście bramkujące —[Author ID1: at Sat Dec 15 14:14:00 2001

]-[Author ID1: at Sat Dec 15 14:14:00 2001

] do sygnału ![]()

. Gdy warunki te są spełnione, układ ten wyprowadza stan „0” na wyjście ![]()

. Wobec tego na wejściach ![]()

[Author ID1: at Sat Dec 15 14:15:00 2001

]układów pamięci i na wejściach ![]()

buforów znajduje się stan aktywny, co powoduje włączenie układów.

Sygnał ![]()

pamięci powinien być sterowany sygnałem żądania zapisu mikroprocesora Z-80 (![]()

). Natomiast sygnał ![]()

steruje pracą buforów 8216, wybierając w nich kierunek przesyłu danych.

--> Rysunek 4.7. [Author ID1: at Sat Dec 15 14:28:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 14:29:00 2001 ][Author ID1: at Sat Dec 15 14:28:00 2001 ]

Przykład 3.[Author ID1: at Sat Dec 15 14:28:00 2001 ]

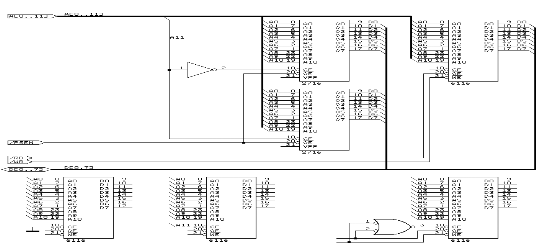

Zaprojektować moduł pamięci statycznej RAM o pojemności 4K [Author ID1: at Sat Dec 15 14:56:00 2001

]× [Author ID1: at Sat Dec 15 14:56:00 2001

]8 dla mikroprocesora Z-80. Do budowy układu należy [Author ID1: at Sun Dec 16 23:17:00 2001

]wykorzystać układy pamięci o organizacji 2K [Author ID1: at Sat Dec 15 14:56:00 2001

]× [Author ID1: at Sat Dec 15 14:56:00 2001

]8. Pamięć powinna zajmować adresy x000 - [Author ID1: at Sat Dec 15 14:57:00 2001

]-[Author ID1: at Sat Dec 15 14:57:00 2001

]xFFFh, gdzie x jest dowolną liczbą z zakresu 0 - [Author ID1: at Sat Dec 15 14:57:00 2001

]-[Author ID1: at Sat Dec 15 14:57:00 2001

]15 (innymi słowy jest dowolną cyfrą szesnastkową z zakresu 0 - [Author ID1: at Sat Dec 15 14:57:00 2001

]-[Author ID1: at Sat Dec 15 14:57:00 2001

]F).

Ponieważ projektowany moduł pamięci ma zapewnić możliwość dowolnego ustawienia czterech najstarszych bitów adresowych, do konstrukcji dekodera adresów należy zastosować komparator 4-bitowy (7485). Wejścia A komparatora dołączone są do bitów A12 - [Author ID1: at Sat Dec 15 14:58:00 2001

]-[Author ID1: at Sat Dec 15 14:58:00 2001

]A15 magistrali adresowej, natomiast wejścia B mogą być dowolnie ustawiane za pomocą przełączników. Komparator rozpoczyna porównywanie wejść A i B, gdy sygnał ![]()

jest w stanie niskim, co oznacza, że mikroprocesor adresuje pamięć. Jeżeli A [Author ID1: at Sat Dec 15 14:58:00 2001

]= [Author ID1: at Sat Dec 15 14:58:00 2001

]B, to w zależności od stanu linii A11 następuje uaktywnienie jednego z dwóch układów pamięci poprzez ustawienie jej wejścia ![]()

w stan „0”. W przeciwnym przypadku natomiast żaden układ nie zostanie uaktywniony.

Pozostałe linie adresowe (A0 - [Author ID1: at Sat Dec 15 15:00:00 2001

]-[Author ID1: at Sat Dec 15 15:00:00 2001

]A10) należy dołączyć bezpośrednio do wejść adresowych obu układów pamięci. Podobnie linie danych pamięci powinno się dołączyć bezpośrednio do magistrali danych. Wejścia ![]()

i ![]()

powinny być dołączone odpowiednio do sygnałów ![]()

i ![]()

mikroprocesora.

Warto zauważyć, że zamiast układów pamięci statycznej RAM można zastosować pamięć EPROM o identycznej organizacji (np. 2 [Author ID1: at Sat Dec 15 15:20:00 2001

]716). Mają one bowiem taki sam rozkład wyprowadzeń. Co prawda pamięć EPROM nie ma wejścia ![]()

, jednak pozostawienie sygnału ![]()

nie przeszkadza w poprawnej pracy układu.

--> Rysunek 4.8. [Author ID1: at Sat Dec 15 15:21:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 15:21:00 2001 ][Author ID1: at Sat Dec 15 15:21:00 2001 ]

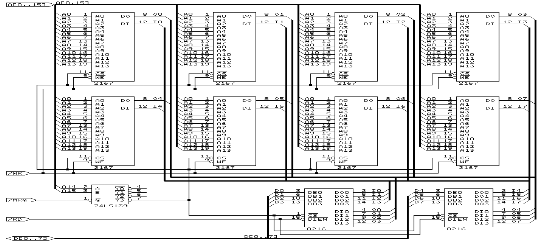

Przykład 4.[Author ID1: at Sat Dec 15 15:22:00 2001 ]

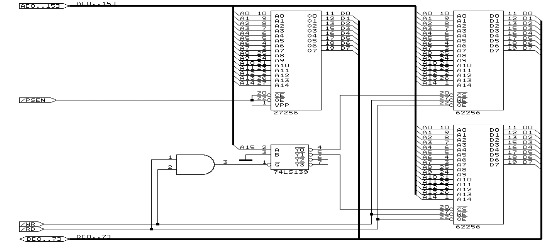

Zaprojektować moduł dla mikroprocesora Z-80, zawierający pamięć EPROM o pojemności 16 KB (adresy 0000 - [Author ID1: at Sat Dec 15 15:23:00 2001

]-[Author ID1: at Sat Dec 15 15:23:00 2001

]3FFFh) oraz pamięć statyczną RAM o pojemności 32 KB (adresy 8000 - [Author ID1: at Sat Dec 15 15:23:00 2001

]-[Author ID1: at Sat Dec 15 15:23:00 2001

]FFFFh). W zadaniu należy w[Author ID1: at Sun Dec 16 23:17:00 2001

]ykorzystać układy pamięci o organizacji 8K [Author ID1: at Sat Dec 15 15:23:00 2001

]× [Author ID1: at Sat Dec 15 15:23:00 2001

]8.

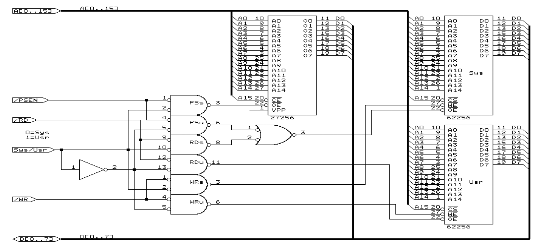

--> Rysunek 4.9. [Author ID1: at Sat Dec 15 15:42:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 15:42:00 2001 ][Author ID1: at Sat Dec 15 15:42:00 2001 ]

Ze względu na wykorzystanie układów pamięci o pojemności 8 KB należy podzielić przestrzeń adresową mikroprocesora (64 KB) na 8 fragmentów po 8 KB każdy. Dwa pierwsze fragmenty są zajęte przez pamięć EPROM, następne dwa są wolne, a kolejne cztery przeznaczone są dla pamięci RAM. Wejścia adresowe i linie danych układów pamięci należy połączyć razem do odpowiednich magistral. Po takim połączeniu pozostają trzy linie adresowe (A13 - [Author ID1: at Sat Dec 15 15:23:00 2001

]-[Author ID1: at Sat Dec 15 15:23:00 2001

]A15), które należy wykorzystać do podziału pamięci na fragmenty o rozmiarze 8 KB. Dekodowanie stanu tych linii adresowych odbywa się w układzie 74 [Author ID1: at Sat Dec 15 15:24:00 2001

]138, który jest aktywny tylko wtedy, gdy mikroprocesor żąda dostępu do pamięci (sygnał ![]()

w stanie niskim). Wówczas jedno (wybrane na podstawie stanu wejść A - [Author ID1: at Sat Dec 15 15:24:00 2001

]-[Author ID1: at Sat Dec 15 15:24:00 2001

]C) wyjście układu ustawia w stan aktywny wejście ![]()

układu pamięci. Pozostałe sygnały sterujące pamięci (![]()

i ![]()

) należy połączyć razem tak, aby były sterowane sygnałami ![]()

i ![]()

mikroprocesora.

Przykład 5.[Author ID1: at Sat Dec 15 15:25:00 2001 ]

Zaprojektować moduł pamięci dla mikroprocesora 8048, zawierający 4 KB pamięci EPROM,[Author ID1: at Sat Dec 15 15:37:00 2001 ] widzianej jako pamięć programu oraz 2 KB pamięci SRAM,[Author ID1: at Sat Dec 15 15:26:00 2001 ] widzianej jako pamięć danych. Do stronicowania pamięci SRAM należy użyć port PC mikroprocesora. W zadaniu należy również w[Author ID1: at Sun Dec 16 23:19:00 2001 ]ykorzystać układy o organizacji 2K [Author ID1: at Sat Dec 15 15:26:00 2001 ]× [Author ID1: at Sat Dec 15 15:26:00 2001 ]8.

--> Rysunek 4.[Author ID1: at Sat Dec 15 15:40:00 2001 ]10.[Author ID1: at Sat Dec 15 15:43:00 2001 ] [Author ID1: at Sat Dec 15 15:40:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 15:40:00 2001 ][Author ID1: at Sat Dec 15 15:40:00 2001 ]

Mikroprocesor 8048 potrafi zaadresować 4 KB pamięci programu i 256 B pamięci danych. Są to oddzielne przestrzenie adresowe, sterowane różnymi sygnałami.

W przestrzeni adresowej pamięci programu należy umieścić układy pamięci EPROM. Ponieważ każdy z nich ma po 2 KB, wybór układu odbywa się na podstawie najstarszego bitu adresowego (A11), sterującego wejścia ![]()

obu układów pamięci. Otwarcie buforów wyjściowych następuje, gdy sygnał ![]()

[Author ID1: at Sat Dec 15 15:28:00 2001

]mikroprocesora jest w stanie aktywnym, co oznacza dostęp do pamięci programu. W przypadku zastosowania tylko jednego układu pamięci EPROM wejście ![]()

[Author ID1: at Sat Dec 15 15:27:00 2001

]można także sterować sygnałem ![]()

lub dołączyć do masy.

Pamięć SRAM należy umieścić w przestrzeni adresowej pamięci danych. Pojemność dołączanego układu przekracza możliwości mikroprocesora. Można zatem pogodzić się z tym faktem i używać tylko 256 B dołączonego układu, albo zastosować technikę stronicowania. Polega ona na tym, że w danym momencie mikroprocesor „widzi” tylko jedną stronę o pojemności 256 B, jednak do jego dyspozycji jest więcej takich stron (w rozpatrywanym przykładzie pamięć 2 KB umożliwia utworzenie 8 stron po 256 B). Wybór strony aktywnej („widocznej”) odbywa się programowo. Numer strony można umieścić w rejestrze, jednak w mikrokomputerach jednoukładowych wygodniej jest wykorzystać do tego celu linie portu. W omawianym przykładzie mogą być to linie PC0 - [Author ID1: at Sat Dec 15 15:29:00 2001

]-[Author ID1: at Sat Dec 15 15:29:00 2001

]PC2. Linie te i tak wykorzystywane są już[Author ID1: at Sat Dec 15 15:32:00 2001

] podczas odwołań do pamięci programu, zatem strata funkcjonalności portu jest niewielka. Należy tylko zwrócić uwagę na to, że użycie mechanizmu stronicowania jest na przedstawionym schemacie niewidoczne. Dzieje się tak dlatego, że wykorzystane linie portu służą także do generowania adresów pamięci programu, której maksymalna pojemność jest większa.

Linie sterujące ![]()

i ![]()

należy sterować sygnałami ![]()

i ![]()

mikroprocesora, gdyż są one aktywne podczas odwołań do zewnętrznej pamięci danych.

Nieco większego komentarza wymaga sposób sterowania sygnału ![]()

pamięci SRAM. Na podstawowym schemacie nie jest on podłączony, ponieważ istnieje wiele możliwości, z których kilka pokazano pod schematem. Dołączenie sygnału ![]()

na stałe do masy powoduje, że układ pamięci stale monitoruje stan wejść adresowych, skutkiem czego pobiera zwiększony prąd ze źródła zasilania. Można zatem dołączyć to wejście do linii adresowej A11. Jest to rozwiązanie lepsze, ale nie idealne, ponieważ układ pamięci jest aktywny, gdy A11 [Author ID1: at Sat Dec 15 15:35:00 2001

]= [Author ID1: at Sat Dec 15 15:35:00 2001

]„0”, także podczas odwołań mikroprocesora do pamięci programu. Ostatnie z pokazanych rozwiązań pozwala włączyć układ pamięci tylko wtedy, gdy mikroprocesor przeprowadza cykl odczytu lub zapisu zewnętrznej pamięci danych. To rozwiązanie ma też pewne wady. Przede wszystkim wymaga zastosowania dodatkowej bramki lub nawet bardziej złożonego układu, jeżeli moduł zawiera więcej układów umieszczonych w przestrzeni pamięci danych. Ponadto narzuca się tu większe wymagania na szybkość układu pamięci. Wybrane rozwiązanie powinno zatem uwzględniać specyficzne wymagania stawiane wobec układu.

Przykład 6.[Author ID1: at Sat Dec 15 15:36:00 2001 ]

Zaprojektować moduł pamięci dla mikroprocesora 8051, zawierający 32 KB pamięci EPROM widzianej jako pamięć programu oraz 64 KB pamięci SRAM widzianej jako pamięć danych. W zadaniu należy w[Author ID1: at Sun Dec 16 23:20:00 2001 ]ykorzystać układy o organizacji 32K [Author ID1: at Sat Dec 15 15:36:00 2001 ]× [Author ID1: at Sat Dec 15 15:36:00 2001 ]8.

--> Rysunek 4.[Author ID1: at Sat Dec 15 15:38:00 2001 ]11.[Author ID1: at Sat Dec 15 15:43:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 15:44:00 2001 ][Author ID1: at Sat Dec 15 15:38:00 2001 ]

Mikroprocesor 8051 może bezpośrednio zaadresować 64 KB pamięci programu i 64 KB pamięci danych. Podobnie jak w mikroprocesorze 8048 są to oddzielne przestrzenie adresowe, sterowane różnymi sygnałami.

Pamięć EPROM należy umieścić w przestrzeni pamięci programu. Do sterowania układu tej pamięci wystarczy sygnał ![]()

, dołączony zarówno do wejścia ![]()

, jak i ![]()

. Pamięć jest aktywna tylko wtedy, gdy mikroprocesor realizuje odczyt z przestrzeni pamięci programu —[Author ID1: at Sat Dec 15 15:38:00 2001

]-[Author ID1: at Sat Dec 15 15:38:00 2001

] sygnał ![]()

jest wówczas w stanie „0”. Takie połączenie sygnałów (a szczególnie sygnału ![]()

) powoduje, że układ jest widoczny nie tylko pod adresami 0000 - [Author ID1: at Sat Dec 15 16:47:00 2001

]-[Author ID1: at Sat Dec 15 16:47:00 2001

]7FFFh, lecz także 8000 - [Author ID1: at Sat Dec 15 16:47:00 2001

]-[Author ID1: at Sat Dec 15 16:47:00 2001

]FFFFh. Dzieje się tak dlatego, że nie jest sprawdzany stan najstarszej linii adresowej A15. Takie dekodowanie nazywamy dekodowaniem niepełnym. Można oczywiście spowodować[Author ID1: at Sat Dec 15 16:48:00 2001

]zapewnić[Author ID1: at Sat Dec 15 16:48:00 2001

], że pamięć będzie aktywna tylko w czasie dostępu do adresów 0000 - [Author ID1: at Sat Dec 15 16:48:00 2001

]-[Author ID1: at Sat Dec 15 16:48:00 2001

]7FFFh

-->

w pamięci programu[Author:EK]

[Author ID1: at Sat Dec 15 16:51:00 2001

]. Wówczas będzie to dekodowanie pełne. Niepełne dekodowanie upraszcza układ, może jednak być stosowane tylko wtedy, gdy mamy pewność, że nie spowoduje ono konfliktów między dołączonymi układami. Należy podkreślić, że takie konflikty mogą się pojawić dopiero w przyszłości, gdy do istniejącego układu zostanie dołączony dodatkowy moduł.

Do wysterowania układów pamięci statycznej można wykorzystać demultiplekser 74139 oraz bramkę AND. Jeżeli mikroprocesor przeprowadza operację odczytu lub zapisu zewnętrznej pamięci danych, to demultiplekser jest aktywny i zależnie od stanu wejścia A (dołączonego do najstarszej linii adresowej A15) wybiera jeden z dwóch układów pamięci statycznej. Linie sterujące ![]()

i ![]()

dołączone są do sygnałów ![]()

i ![]()

mikroprocesora.

Przykład 7.[Author ID1: at Sat Dec 15 16:53:00 2001 ]

Zaprojektować moduł pamięci dla mikroprocesora 8051, zawierający 32 KB pamięci EPROM oraz 32 KB pamięci SRAM. Obie pamięci powinny być widziane zarówno w przestrzeni adresowej programu, jak i danych. Pamięć EPROM powinna zajmować adresy 0000 - [Author ID1: at Sat Dec 15 16:53:00 2001

]-[Author ID1: at Sat Dec 15 16:53:00 2001

]7FFFh, natomiast SRAM —[Author ID1: at Sat Dec 15 16:53:00 2001

]-[Author ID1: at Sat Dec 15 16:53:00 2001

] 8000 - [Author ID1: at Sat Dec 15 16:53:00 2001

]-[Author ID1: at Sat Dec 15 16:53:00 2001

]FFFFh.

--> Rysunek 4.12. [Author ID1: at Sat Dec 15 16:53:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 16:54:00 2001 ][Author ID1: at Sat Dec 15 16:53:00 2001 ]

Umieszczenie pamięci EPROM w przestrzeni danych, podobnie jak umieszczenie pamięci SRAM w przestrzeni programu, wymaga, by sygnał odczytu pamięci (![]()

) był aktywny zarówno w cyklu odczytu pamięci programu (sygnał ![]()

w stanie „0”), jak i podczas cyklu odczytu pamięci danych (stan niski sygnału ![]()

). Ponadto wejścia ![]()

[Author ID1: at Sat Dec 15 16:57:00 2001

]obu pamięci powinny być uzależnione tylko od adresu generowanego przez mikroprocesor, a niezależne od przestrzeni adresowej, do której ten adres jest kierowany. Sygnał zapisu pamięci ![]()

może być dołączony bezpośrednio do wyjścia ![]()

mikroprocesora, ponieważ zapis możliwy jest tylko dla pamięci danych.

Prezentowane rozwiązanie umożliwia zarówno wygodny dostęp programowy np. do dużych tablic umieszczonych w pamięci programu (pamięci stałej), jak i ładowanie dowolnego programu do pamięci danych (pamięci RAM). Wadą tego układu jest jednak połączenie rozdzielonych przestrzeni adresowych, co wiąże się ze zmniejszeniem całkowitej pojemności pamięci adresowanej przez mikroprocesor.

Przykład 8[Author ID1: at Sun Dec 16 23:22:00 2001

]6[Author ID1: at Sun Dec 16 23:22:00 2001

].[Author ID1: at Sat Dec 15 16:57:00 2001

]

Zaprojektować moduł pamięci dla mikroprocesora 8051, zawierający 32 KB pamięci EPROM widzianej jako pamięć programu, 32 KB pamięci SRAM „systemowej” i 32 KB pamięci SRAM „użytkownika”. Zapewnić możliwość pracy[Author ID1: at Sat Dec 15 16:57:00 2001

]u[Author ID1: at Sat Dec 15 16:57:00 2001

] modułu w dwóch trybach:

Tryb „systemowy”. Kody rozkazów pobierane są z pamięci EPROM, odczyt i zapis danych odwołują się tylko do pamięci „systemowej”.

Tryb „użytkownika”. Kody rozkazów pobierane są z pamięci „systemowej”, odczyt i zapis danych odwołują się tylko do pamięci „użytkownika”.

Wykorzystać układy pamięci o organizaji 32K [Author ID1: at Sat Dec 15 16:58:00 2001

]× [Author ID1: at Sat Dec 15 16:58:00 2001

]8. Pamięci programu i danych powinny zajmować adresy 0000 - [Author ID1: at Sat Dec 15 16:58:00 2001

]-[Author ID1: at Sat Dec 15 16:58:00 2001

]7FFFh w odpowiednich przestrzeniach adresowych niezależnie od trybu.

--> Rysunek 4.13. [Author ID1: at Sat Dec 15 17:00:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 17:01:00 2001 ][Author ID1: at Sat Dec 15 17:00:00 2001 ]

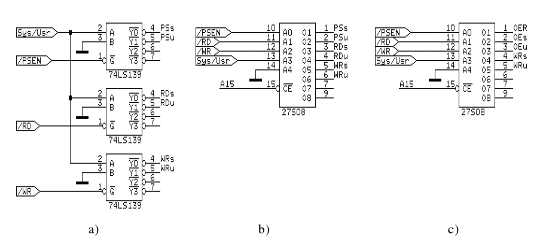

Najważniejszym fragmentem zadania jest odpowiednie bramkowanie sygnałów sterujących. Do tego celu służy zespół sześciu bramek OR. Do przełączania trybu wprowadzono sygnał Sys/Usr, generowany przez układ zewnętrzny (może to być przełącznik, rejestr albo wyjście portu mikroprocesora). W zależności od stanu tego sygnału („0” —[Author ID1: at Sat Dec 15 16:59:00 2001

]-[Author ID1: at Sat Dec 15 16:59:00 2001

] tryb systemowy, „1” —[Author ID1: at Sat Dec 15 16:59:00 2001

]-[Author ID1: at Sat Dec 15 16:59:00 2001

] tryb „użytkownika”) zbiór sygnałów sterujących mikroprocesora (![]()

, ![]()

![]()

, ![]()

) jest rozdzielany na sygnały trybu „systemowego” (PSs, RDs, WRs) i sygnały trybu [Author ID1: at Sat Dec 15 17:00:00 2001

]„użytkownika” (PSu, RDu, WRu). Sygnały te następnie sterują wejścia pamięci. Odczyt z pamięci RAM „systemowej” jest możliwy w dwóch przypadkach:

w trybie „systemowym” przy odwołaniach do pamięci danych,

w trybie „użytkownika” przy odwołaniach do pamięci programu.

Dlatego też wejście ![]()

tego układu pamięci jest pobudzane, gdy aktywny jest sygnał RDs lub PSu. Wejścia ![]()

wszyskich układów pamięci jest dołączone do linii adresowej A15, co zapewnia ich widoczność w żądanym zakresie adresów.

Układ sterujący jest dość skomplikowany. Można go nieco uprościć, stosując zamiast bramek demultipleksery, np. 74139. Każdy demultiplekser rozdziela wówczas jeden sygnał sterujący. Sygnał Sys/Usr jest podłączony do jednego wejścia adresowego. Drugie wejście adresowe pozostaje nie wykorzystane, można jednak podłączyć je do linii A15, co umożliwi późniejszą rozbudowę układu o dodatkowe pamięci. Wejścia bramkujące ![]()

są sterowane odpowiednimi sygnałami sterującymi (rysunek 4.14 —[Author ID1: at Sun Dec 16 22:59:00 2001

] [Author ID1: at Sun Dec 16 23:00:00 2001

]a)[Author ID1: at Sun Dec 16 22:59:00 2001

]. rys. xxx a.[Author ID1: at Sun Dec 16 22:59:00 2001

]

Dalsze uproszczenie (rysunek 4.14 — b)[Author ID1: at Sun Dec 16 23:03:00 2001

] można uzyskać, stosując pojedynczą pamięć PROM o organizacji 32 [Author ID1: at Sat Dec 15 17:07:00 2001

]× [Author ID1: at Sat Dec 15 17:07:00 2001

]8.[Author ID1: at Sun Dec 16 23:04:00 2001

] J[Author ID1: at Sun Dec 16 23:04:00 2001

](j[Author ID1: at Sun Dec 16 23:04:00 2001

]est to najmniejsza pamięć PROM.[Author ID1: at Sun Dec 16 23:04:00 2001

]),[Author ID1: at Sun Dec 16 23:04:00 2001

] pokazane na rys[Author ID1: at Sun Dec 16 23:04:00 2001

]. xxx b[Author ID1: at Sun Dec 16 23:01:00 2001

]. [Author ID1: at Sun Dec 16 23:04:00 2001

]Pamięć ta wymaga tylko odpowiedniego zaprogramowania. Aby jeszcze bardziej uprościć układ, należy tę pamięć zaprogramować tak, aby generowała bezpośrednio sygnały dla układów pamięci EPROM i SRAM, dzięki czemu nie będzie już potrzebna bramka AND (rysunek[Author ID1: at Sun Dec 16 23:05:00 2001

].[Author ID1: at Sun Dec 16 23:06:00 2001

] 4.14 — [Author ID1: at Sun Dec 16 23:06:00 2001

]c).

--> Rysunek 4.14.[Author ID1: at Sat Dec 15 17:10:00 2001 ][Author:EK] [Author ID1: at Sat Dec 15 17:10:00 2001 ]

2 Część I ♦ Podstawy obsługi systemu WhizBang (Nagłówek strony)

2 C:\Moje dokumenty\Korekta\Uklady mikro\1 Od autora\r4-1.doc

[Author ID1: at Fri Dec 14 22:35:00 2001 ][Author ID1: at Fri Dec 14 22:35:00 2001 ][Author ID1: at Fri Dec 14 22:35:00 2001 ][Author ID1: at Fri Dec 14 22:35:00 2001 ][Author ID1: at Fri Dec 14 22:35:00 2001 ] Co to za tabela?[Author ID1: at Fri Dec 14 22:35:00 2001 ] [Author ID1: at Sat Dec 15 18:33:00 2001 ]W tym rozdziale nie ma żadnej tabeli. [Author ID1: at Fri Dec 14 22:38:00 2001 ]Tabela 1.1, która znajduje się w rozdziale 1. nosi tytuł [Author ID1: at Fri Dec 14 22:35:00 2001 ]„Parametry elektryczne cyfrowych układów scalonych różnych serii[Author ID1: at Fri Dec 14 22:36:00 2001 ]”. Czyżby chodziło o tę tabelę?[Author ID1: at Fri Dec 14 22:37:00 2001 ]

[Author ID1: at Fri Dec 14 23:12:00 2001 ][Author ID1: at Fri Dec 14 23:12:00 2001 ][Author ID1: at Fri Dec 14 23:12:00 2001 ][Author ID1: at Fri Dec 14 23:12:00 2001 ][Author ID1: at Fri Dec 14 23:12:00 2001 ] Może lepiej byłoby powiedzieć: ...dekoder, który zamienia kod dwójkowy na kod wyświetlacza 7-segmentowego i pozwala na wyświetlanie cyfr szesnastkowych lub dekoder ...[Author ID1: at Fri Dec 14 23:12:00 2001 ]

[Author ID1: at Sat Dec 15 13:46:00 2001 ][Author ID1: at Sat Dec 15 13:46:00 2001 ][Author ID1: at Sat Dec 15 13:46:00 2001 ][Author ID1: at Sat Dec 15 13:46:00 2001 ][Author ID1: at Sat Dec 15 13:46:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 13:46:00 2001 ]

[Author ID1: at Sat Dec 15 14:08:00 2001 ][Author ID1: at Sat Dec 15 14:08:00 2001 ][Author ID1: at Sat Dec 15 14:08:00 2001 ][Author ID1: at Sat Dec 15 14:08:00 2001 ][Author ID1: at Sat Dec 15 14:08:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 14:08:00 2001 ]

[Author ID1: at Sat Dec 15 14:29:00 2001 ][Author ID1: at Sat Dec 15 14:29:00 2001 ][Author ID1: at Sat Dec 15 14:29:00 2001 ][Author ID1: at Sat Dec 15 14:29:00 2001 ][Author ID1: at Sat Dec 15 14:29:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 14:29:00 2001 ]

[Author ID1: at Sat Dec 15 15:21:00 2001 ][Author ID1: at Sat Dec 15 15:21:00 2001 ][Author ID1: at Sat Dec 15 15:21:00 2001 ][Author ID1: at Sat Dec 15 15:21:00 2001 ][Author ID1: at Sat Dec 15 15:21:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 15:21:00 2001 ]

[Author ID1: at Sat Dec 15 15:42:00 2001 ][Author ID1: at Sat Dec 15 15:42:00 2001 ][Author ID1: at Sat Dec 15 15:42:00 2001 ][Author ID1: at Sat Dec 15 15:42:00 2001 ][Author ID1: at Sat Dec 15 15:42:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 15:42:00 2001 ]

[Author ID1: at Sat Dec 15 15:40:00 2001 ][Author ID1: at Sat Dec 15 15:40:00 2001 ][Author ID1: at Sat Dec 15 15:40:00 2001 ][Author ID1: at Sat Dec 15 15:40:00 2001 ][Author ID1: at Sat Dec 15 15:40:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 15:40:00 2001 ]

[Author ID1: at Sat Dec 15 15:44:00 2001 ][Author ID1: at Sat Dec 15 15:44:00 2001 ][Author ID1: at Sat Dec 15 15:44:00 2001 ][Author ID1: at Sat Dec 15 15:44:00 2001 ][Author ID1: at Sat Dec 15 15:44:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 15:44:00 2001 ]

[Author ID1: at Sat Dec 15 16:51:00 2001 ][Author ID1: at Sat Dec 15 16:51:00 2001 ][Author ID1: at Sat Dec 15 16:51:00 2001 ][Author ID1: at Sat Dec 15 16:51:00 2001 ][Author ID1: at Sat Dec 15 16:51:00 2001 ] Czy ten okolicznik miejsca jest tutaj niezbędny? Zrezygnowałabym z niego.[Author ID1: at Sat Dec 15 16:51:00 2001 ]

[Author ID1: at Sat Dec 15 16:54:00 2001 ][Author ID1: at Sat Dec 15 16:54:00 2001 ][Author ID1: at Sat Dec 15 16:54:00 2001 ][Author ID1: at Sat Dec 15 16:54:00 2001 ][Author ID1: at Sat Dec 15 16:54:00 2001 ] Brak podpisu.[Author ID1: at Sat Dec 15 16:54:00 2001 ]

[Author ID1: at Sat Dec 15 17:01:00 2001 ][Author ID1: at Sat Dec 15 17:01:00 2001 ][Author ID1: at Sat Dec 15 17:01:00 2001 ][Author ID1: at Sat Dec 15 17:01:00 2001 ][Author ID1: at Sat Dec 15 17:01:00 2001 ]Brak podpisu.[Author ID1: at Sat Dec 15 17:01:00 2001 ]

[Author ID1: at Sat Dec 15 17:10:00 2001 ][Author ID1: at Sat Dec 15 17:10:00 2001 ][Author ID1: at Sat Dec 15 17:10:00 2001 ][Author ID1: at Sat Dec 15 17:10:00 2001 ][Author ID1: at Sat Dec 15 17:10:00 2001 ] Brak rysunku[Author ID1: at Sat Dec 15 17:10:00 2001 ]

Tabela 1. Organizacja przykładowych układów pamięci PROM

Organizacja |

Wyjście z otwartym kolektorem |

Wyjście trójstanowe |

32×8 |

27S08, 74S188, 82S23 |

27S09, 74S288, 82S123 |

64×8 |

82S186 |

|

256×4 |

27S10, 74S387, 82S126, 3601 |

27S11, 74S287, 82S129, 3621 |

256×8 |

74S470 |

74S471, 82S114 |

512×4 |

74S570, 82S130, 3602 |

74S571, 82S131, 3622 |

512×8 |

74S472, 3604 |

74S473, 3624 |

512×8 |

82S140 |

82S141 |

1024×4 |

74S572, 82S136 |

74S573, 82S137 |

1024×8 |

82S180, 3608 |

82S181, 82S28 |

2048×4 |

82S184 |

82S185 |

Wyszukiwarka

Podobne podstrony:

7826

7826

praca-magisterska-wa-c-7826, Dokumenty(2)

7826

7826

7826

7826

7826

air varie for clarinet and piano 7826

7826

więcej podobnych podstron