Architektura von Neumanna

Posiada skończoną i funkcjonalną listę rozkazów

Posiada ALU, urządzenia wejścia / wyjścia, pamięć (dane i program razem)

Posiada możliwość wprowadzenia programu z zewnątrz i przechowywania go wraz z danymi w pamięciu

Procesor ma jednakowy dostęp do instrukcji i danych

Instrukcje są wykonywane sekwencyjnie

Pierwsza architektura ogólnego przeznaczenia

Stworzona wspólnie z Eckertem i Mauchlym (1945)

Architektura Harvardzka

W odróżnieniu od AVN, dane i program znajdują się w osobnych pamięciach

Dzięki temu jest szybsza

Architektura

Atrybuty systemu widzialne dla programisty, mające wpływ na logiczne wykonywanie programu

Przykładowe atrybuty architektury: lista rozkazów, ilość bitów na dany typ, metody adresowania, mechanizmy wejścia-wyjścia

Architektura określa np. czy w komputerze występuje rozkaz mnożenia

Organizacja

Odnosi się do jednostek operacyjnych i połączeń, stanowiących realizację danej architektury

Rozwiązania sprzętowe niewidoczne dla programisty

Przykładowe atrybuty: sygnały sterujące, interfejs komputer - urządzenia peryferyjne, technologia pamięci

Organizacja określa np, co realizuje operacje mnożenia

Taksonomia Flynna

Klasyfikacja systemów równoległego przetwarzania danych:

SISD |

Single instruction, single data. Pojedynczy procesor obsługuje pojedynczy strumień rozkazów operując na danych zapisanych w pojedynczej pamięci - komputery jednoprocesorowe |

SIMD |

Single instruction, multiply data. Pojedynczy rozkaz maszynowy steruje działaniem większej grupy elementów przetwarzających. Każdy element posiada własną pamięć. Każdy rozkaz jest wykonywany na różnych zbiorach danych przez różne procesory. Procesory wektorowe i tablicowe. GPU. |

MISD |

Multiply instruction, single data. Wiele rozkazów jest wykonywanych przez wiele procesorów na tym samym zbiorze danych. Nie zaimplementowano komerycjnie. |

MIMD |

Multiply instruction, multiply data. Wiele procesorów równocześnie wykonuje różne rozkazy, na różnych danych. Implementacja w SMP, klastrach i NUMA. |

SMP (Symmetric Multiprocessor)

Sprzętowa architektura komputera

Dwa lub więcej procesorów o podobnych możliwościach

Wspólna pamięć główna i urządzenia we-wy

Czas dostępu do pamięci taki sam (!) dla każdego procesora

Wszystkie procesory mogą realizować te same funkcje (stąd symmetric)

Sterowanie przez zintegrowany system operacyjny

Możliwość stopniowej rozbudowy

Uszkodzenie jednego procesora powoduje tylko obniżenie wydajności

Obsługa współdzielenia zasobów poprzez magistralę

NUMA

Rodzaj architektury

Charakteryzuje się niejednorodnym dostępem do pamięci (czas dostępu dla różnych procesorów jest różny)

Ma to służyć polepszeniu efektywności i nie przeciążaniu magistrali (według twórców dla aplikacji reprezentatywnych, które posiadają większość danych lokalnie w cache działa wydajniej niż SMP)

Wady: słaba przenoszalność pomiędzy SMP a (CC)-NUMA, dostępność

MESI

Główne rozwiązanie problemu spójności pamięci podręcznych (jeden procesor aktualizuje cache, inne procesory wówczas mają nieaktualne dane - stąd problem)

Każdy cache znakowany przez 2 bity stanu:

zmodyfikowany - wiersz w cache został zmodyfikowany i jest osiągalny tylko tam,

wyłączny - wiersz w cache jest identyczny jak ten w głównej pamięci i nie występuje w innych cache,

wspólny - wiersz w cache taki sam jak w pamięci i głównej i może występować w innych pamięciach,

nieważny - wiersz w cache nie zawiera danych ważnych

możliwości operacji na danych: chybienie / trafienie odczytu / zapisu

Failover i Failback

FO (przejmowania danych) - w odniesieniu do klastrów: funkcja przełączania aplikacji i zasobów danych z systemu uszkodzonego do inne go systemu w klastrze

FB (przywracanie) - w odniesieniu do klastrów: funkcja przywracania aplikacji i zasobów danych do systemu początkowego, gdy zostanie on naprawiony

Klaster

Alternatywna dla SMP i NUMA

Bardziej wydajny i dostępny - stosowany w serwerach

Grupa połączonych kompletnych (mogących funkcjonować w oderwaniu od klastra) komputerów (nazywanych węzłami), tworzących zasób obliczeniowy imitujący jedną maszynę

Możliwe jest tworzenie bardzo dużych klastrów przewyższających możliwościami największe samodzielne jednostki

Istnieje możliwość nieinwazyjnego stopniowego powiększania klastra

Każdy węzeł klastra jest kompletny - jego odłączenie nie powoduje uszkodzenia systemu

Bardzo dobry stosunek cena / wydajność

Rodzaje:

rezerwa bierna - pseudoklaster, istnieje dodatkowy serwer, który włącza się dopiero gdy serwer główny pada (przestaje wysyłać sygnał „bicia serca”)

dodatkowy czynny serwer - bardziej złożony, dodatkowy serwer nie „śpi” i również przetwarza dane

odrębne serwery - serwery pracują na oddzielnych dyskach, większa dostępność, większe obciążenie łącza (ciągłe kopiowanie danych)

serwery połączone z dyskami - praca na wspólnym dysku + własne dyski, mniejsze obciążenie łącza, wymaga tworzenia kopii RAID

serwery współużytkujące dyski - wiele serwerów ma jednocześnie dostęp do dysków, wymaga mechanizmów blokowania, niskie obciążenie łącza

Duży plus klastrów to zasadnicza jednolitość: sterowania, interfejsów, przestrzeni pamięci, hierarchii plików ...itd.

CISC

Architektura mikroprocesorów o pełnej liście rozkazów

Dużo ilość, skomplikowanych (zajmujących kilka cyklów procesora) rozkazów

Duża liczba trybów adresowania (5 do 20), powolny dekoder adresów

Projektowane głównie po to, by zapewnić odpowiednią współpracę z językami wysokiego poziomu, dążono do uproszczenia kompilatorów i lepszej wydajności

Stosowane dawniej również ze względów ekonomicznych - teoretycznie programy na architekturę CISC zajmowały mniej miejsca w pamięci, co było bardzo cenne

Wolniejsze od architektur typu RISC, bo jest duża liczba odwołań do danych w pamięci

Mniejsza liczba rejestrów

Różna długość rozkazów

Łatwiejsze programowanie, krótsze programy

Droższe w budowie i eksploatacji

Na każdy rozkaz składa się mikroprogram złożony z mikrooperacji/mikrorozkazów (a każdy mikrorozkaz zawiera sekwencję bitów, która reprezentuje mikrooperację sterującą przemieszczaniem informacji między różnymi podzespołami i rejestrami procesora);

RISC

Duża liczba rejestrów - operacje typu z rejestru do rejestru, implikują dużo szybsze działanie niż pobieranie danych z pamięci podręcznej

W dużych rejestrach zmienne lokalne, także globalne - szybsze wykonywanie rozkazów

Krótkie, proste rozkazy - łatwe do implementacji w procesorze, a jednocześnie będące podstawowym budulcem programów (wykorzystywane w ponad 90% przypadków)

Jeden rozkaz na jeden cykl - przyspieszenie działania

Proste tryby adresowania i ich niewielka liczba

Architektura load-store

Intensywne wykorzystanie przetwarzania potokowego

Proste formaty rozkazów

Rozkazy mają jednakową długość, brak adresowania pośredniego, brak operacji łączących ładowanie / zapis z arytmetyką

Przykłady realizacji:

MIPS - dodatkowe ALU,która mogłaby współpracować z istniejącymi. Potok wykorzystywany do aktywowania więcej niż jednej operacji. Ciężar zapewnienia poprawności wykonania spoczywa na kompilatorze; usprawnienie obliczeń

SPARC -otwarta architektura RISC, zysk z wyrzucenia sprzętu ze środka procesora a dołączenia wielu rejestrów generalnego przeznaczenia. przełączanie kontekstów, okno z rejestrami, dużo rejestrów

ARM - brak zagospodarowania wolnego miejsca (po redukcji rozkazów) - mniejsza jednostka (zmniejszenie struktury) - mniejsze zużycie energii, mniej wydalanego ciepła - możliwe wyższe obroty -czyli praca z wysokimi częstotliwościami

POWERPC - podobne do MIPS, dodatkowe bloki funkcjonalne (dla floatów np.); rozdzielamy pewne typy operacji i wykonujemy je na oddzielnych jednostkach, aby zrównoleglić obliczenia.

Porównywanie RISC i CISC jest o tyle niezasadne, iż obie technologie od jakiegoś czasu przenikają się, wpływają na siebie i uzupełniają się

ENIAC

Electronic Numerical Integrator And Computer

Autorzy: John Mauchly, John Eckert

Pierwszy elektroniczny komputer o przeznaczeniu ogólnym

Projektowany dla wojskowych obliczeń balistycznych

30 ton, 1400 m2, 18000 lamp próżniowych, 140kW - zużycie mocy, 5000 obliczeń na sekundę

Maszyna dziesiętna (liczba reprezentowana przez pierścień lamp), 20 akumulatorów, ukończony w 1946 roku, rozebrany w 1955 r.

Trudny do reprogramowania, ale uniwersalny

Nie posiadał pamięci operacyjnej

Urządzenie Sterujące

Jeden z elementu funkcjonalnego obrazu komputera

Zarządza zasobami komputera i koordynuje działanie jego składników funkcjonalnych w zależności od wprowadzonych poleceń

Jednostka sterująca CPU - steruje działaniem komputera, składa się z: układów logicznego sterowania, rejestrów i dekoderów jednostki sterującej i pamięci sterującej

Schemat Funkcjonalny Komputera

Komputer realizuje 4 podstawowe funkcje: przetwarzanie danych, przechowywanie danych, przenoszenie danych, sterowanie

Jeżeli komputer otrzymuje dane od urządzenia bezpośrednio podłączonego do niego - to jest to proces we-wy, a urządzenie nazywa się peryferyjnym

Jeżeli przenoszenie danych odbywa się na duże odległości, to proces ten nazywamy transmisją danych

W komputerze wyróżnia się 4 podstawowe elementy: CPU, pamięć główna, wejście-wyjście i magistrala systemowa

RAID

Schemat projektowania baz danych dla pamięci wielodyskowych

Ma zwiększać wydajność (w pewnym sensie także pojemność całościową) pamięci dyskowych, a także polepszać bezpieczeństwo danych

Jest to zespół fizycznie istniejących napędów dyskowych, widzianych przez OS jako jeden napęd logiczny

Dane są rozproszone, tworzą tablice

Implementuje przechowywanie danych o parzystości, co gwarantuje odzyskiwanie danych w wypadku awarii któregoś z napędów

Istnieje siedem poziomów RAID:

RAID 0 - nie przewiduje redundancji, stosowany w celu poprawienia wydajności i pojemności, dane rozproszone na wszystkich dyskach w postaci pasków, zwiększa szybkość transferu we-wy

RAID 1 - redundancja osiąga przez powielanie wszystkich danych, takie same dane są równolegle na dwóch dyskach - szybszy odczyt, w razie awarii każde dane posiadają kopię na drugim dysku, wady: wolniejszy zapis i koszt

RAID 2 - dostęp do danych - równoległy, stosowany jest kod Hamminga, mniej kosztowny niż RAID 1, ale nadal kosztowny, stosowany dla tablic o dużej zawodności

RAID 3 - analogiczny do RAID 2, wymaga tylko jednego dysku redundancyjnego, dostęp równoległy, wykorzystuje obliczanie bitów parzystości (redundancja implementowana za pomocą funkcji XOR)

RAID 4 - dostęp do danych - niezależny, każdy dysk działa niezależnie, mogą być obsługiwane równolegle, dobry w sytuacji, gdy potrzeba szybkich odpowiedzi na żądania we-wy a niekoniecznie dużego transferu, gorsza wydajność zapisu, paski parzystości znajdują się na jednym dysku (wąskie gardło)

RAID 5 - podobny do RAID 4, jednak paski parzystości są rozproszone na wszystkich dyskach

RAID 6 - znaczne polepszenie dostępności, parzystość obliczana jest podwójne, jednak dzieje się to kosztem wydajności i szybkości zapisu

INTEL 8086

Mikroprocesor ogólnego przeznaczenia

Dużo bardziej zaawansowany, niż 8080

16-bitowy mikroprocesor

Szersza ścieżka danych, większe rejestry, podręczna pamięć rozkazów

Mechanizmy pracy wieloprocesorowej

Segmentacja pamięci

Rozszerzone możliwości adresowania operandów

Adresowanie natychmiastowe, rejestrowe, bezpośrednie, pośrednie, indeksowe i bazowe

Wprowadzenie układu kolejki (pamiętanie 6 bajtów z pamięci w czasie zajętości procesora)

2 części: jednostka wykonawcza, zespół łącza z magistralą systemową

Rozkazy: arytmetyczno-logiczne, przesłań, skoków, obsługi pętli, wywołań i powrotów z podprogramu, dotyczące rejestrów segmentowych ,wykonujące operacje na ciągach słów, wejścia/wyjścia i inne

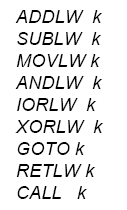

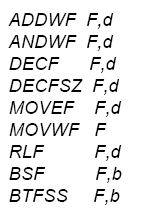

PIC (16F84A)

Jednoukładowy komputer stosowany w systemach wbudowanych

Architektura RISC

Należy podłączyć do niego zegar i zasilanie

Zawiera 68 8-bitowych rejestrów, stos (8 wierszy 13-bitowych, ma do niego dostęp licznik programu),

Peryferyjne: pamięć EEPROM, TIMER, I/O Ports

Ostatni wpis ze stosu jest wpisywany do Program Counter

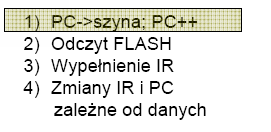

Zbudowany wg paradygmatu von Neumanna, jednak w architekturze Harvardzkiej - gwarantuje to większą szybkość - równoległe pobieranie danych i instrukcji

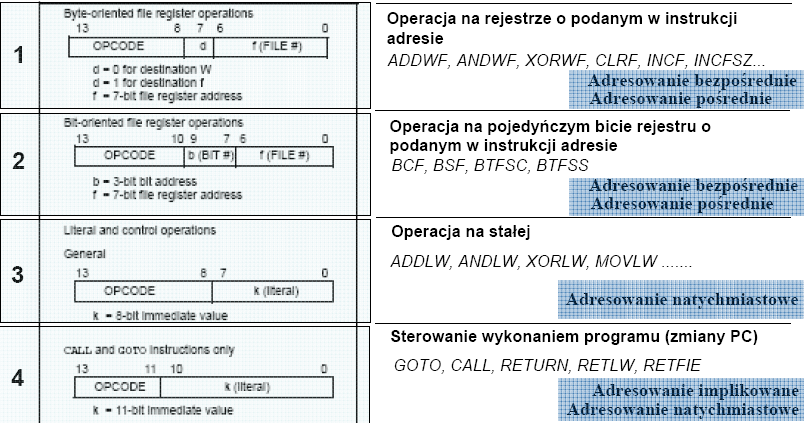

Stała długość instrukcji - 14 bitów

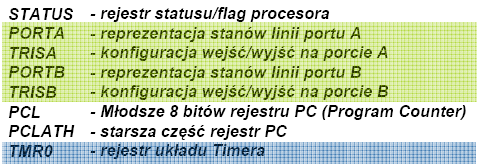

Rejestry:

Adresowanie:

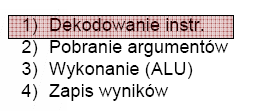

Cykle

Dla stałych i rejestrów

14.Rejestry ogólnego przeznaczenia MP 80386 i ich wykorzystanie.

Rejestry można podzielić na trzy funkcjonalne grupy : ogólnego przeznaczenia, sowe, statusowe i sterujące.

Rejestry ogólnego przeznaczenia:

AX - odpowiednik akumulatora, pamięć tego rejestru jest wykorzystywana przez arytmometr, AX jest rejestrem używanym w operacjach logicznych, arytmetycznych i do odkładania wyników wielu operacji.

BX - rejestr bazowy, służący do adresowania.

CX - rejestr zliczający ( jest licznik w pętlach ).

DX - rejestr danych, umożliwia przekazywanie i odbieranie danych z portów.

SI - rejestr źródła ciągów łańcuchów danych.

DI - rejestr przeznaczenia ciągów łańcuchów danych.

SP - wskaźnik stosu.

BP - wskaźnik bazy.

15Rejestry sowe MP 80386 i ich przeznaczenie

Procesor 386 ma zespół ośmiu rejestrów 32 - bitowych ogolnego przeznaczenia EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP, które mogą przechowywać dane albo adresy. Mymy równierz sześć rejestrów sowych CS, SS, DS., ES, FS i GS. Stosuje się je w połączeniu z adresami zapisanymi w rejestrach ogólnego przeznaczenia lub w rejestrze lub w rejestrze wskaźnika rozkazów (EIP) do uzyskania fizycznego adresu na szynie adresowej. Rejestr CS (s kodu ) z rejestrem wskaźnika rozkazów określa fizyczny adres do pobrania rozkazu, a rejestr SS (s stosu) jest używany do określenia adresu stosu. Inne rejestry sowe stosuje się zwykle do adresacji danych. Każdy z rejestrów sowych jest związany z rejestrem deskryptorów sów, niewidocznych dla programisty. Przy czym :

EAX - Akumulator

EBX - Rejestr bazowy

ECX - Rejestr licznika

EDX - Rejestr danych

ESI - Indeks źródłowy

EDI - Indeks przeznaczenia

ESP - Wskaźnik stosu

EBP - Wskaźnik bazowy

EIP - Wskaźnik rozkazu

EFL - Znacznik stanu

CS - S kodu

SS - S stosu

DS - S danych

ES - S danych

FS - S danych

GS - S danych

Watchdog - układ chroniący mikroprocesor przed zbyt długim przebywaniem w stanie zawieszenia, implementowany jako dekrementujący się licznik, odnawiany co jakiś czas przez mikroprocesor, jeśli mikroprocesor nie odnowi wartości licznika i ten odliczy do zera, następuje zresetowanie układu

BANKI PAMIĘCI

Jeden ze sposobów na zwiększenie obszaru adresowania

Przykład: magistrala 8-bitowa pozwala zaadresować 64 * wielkość słowa

Gdy przy stałej magistrali rosły wielkości pamięci pojawił się problem, jak zaadresować „nadmiarową” ilość pamięci

W PICu (także Atari, komputery Apple) użyto tzw. banków pamięci

Każdy bank na swój identyfikator (0,1...), każdy bank obejmuje odpowiednią część pamięci, naraz można się odwołać bezpośrednio tylko do jednego banku

By zmienić bank, należy zmienić bit RP0 w rejestrze statusu. Ten bit przechowuje najstarszy bit szyny adresowej.

Można się przełączać między bankami, lecz wymaga to instrukcji, które by zmieniały odpowiednio wartość rejestru

W prostych układach 8-bitowych, za przełączanie banków odpowiada MMU (Memory Management Unit)

Sposób dość powolny - duża strata czasu - przełączanie między bankami

Adres fizyczny jest sklejany: 1 bit z RP0 i 7 bitowy offset pobierany z instrukcji

SEGMENTACJA PAMIĘCI

Pamięć jest logicznie podzielona na pewne obszary

Każdy z obszarów jest reprezentowany w danym rejestrze segmentowym (Intel 8086 - CS,DS,SS,ES)

Adresowanie polega na sumowaniu wartości offsetu i zawartości danego rejestru-wymagana jest więc dodatkowa operacja dodawania

Takie „dwuetapowe” (najpierw segment, potem offset) adresowanie zwiększa ilość danych, które można zaadresować

Ponadto segmentacja umożliwiała logiczne oddzielenie różnych elementów w pamięci (programu, danych, stosu)

W rejestrach znajdowały się także odpowiednie bity odpowiadające za poziom dostępu do danego segmentu, co umożliwiało ochronę danych

Implementacje segmentacji wymuszały jednak dość ograniczone dzielenie pamięci, dzielenie jej w sposób dość nienaturalny i kłopotliwy, przez co obecnie segmentacja nie jest stosowana

Przenaszalnośc kodu w rózne miejsca pamięci

Każdy program mógł się zaczynać w dowolnym miejscu.

Początek segmentu umieszczany w adresach podzielnych przez 16

Tryby Adresowania

natychmiastowy (PIC, 8086)

Argument pobierany jest bezpośrednio z rozkazu. W tym trybie wskazywany jest wyłącznie operand źródłowy. Np. MOV AX, 20 - w rejestrze AX zostanie zapisana liczba 20. używany tylko w odniesieniu do stałych: MOV LWbezpośredni (PIC, 8086)

Adres operandu znajduje się bezpośrednio w kodzie instrukcji. Np. MOV AX, [40] - w rejestrze AX zostanie zapisana zawartość komórki pamięci (segment danych) o adresie 40.pośredni (PIC, 8086)

W trybie adresowania pośredniego odwołujemy się do jednego z rejestrów roboczych procesora (np. BX) lub do komórki pamięci (np.19). W rejestrze (BX) zapisany jest numer komórki pamięci, do której trzeba sięgnąć aby odczytać tam zawarty adres i przenieść do drugiego rejestru (AX). Np. MOV AX, [CX] - w rejestrze AX zostanie zapisana zawartość komórki pamięci o adresie, który znajduje się w rejestrze CX.

ja bym ujęła to tak: instrukcja zawiera adres komórki pamięci, która zawiera adres efektywny.implikowany (PIC)

Adresowanie implikowane dotyczy instrukcji jednobajtowych, dla których zarówno operand jak i miejsce przeznaczenia są określone przez dany rozkaz. Ten tryb adresowania jest używany wyłącznie w odniesieniu do wewnętrznych rejestrów mikrokontrolera, szczególnie w odniesieniu do akumulatora. Ze względu na krótki format instrukcji tryb ten jest bardzo efektywny, a ograniczeniem jest tylko liczba dostępnych rejestrów. Np. CLRW,względny (PIC)

Adresowanie względne służy natomiast do adresowania pamięci względem adresu aktualnie wykonywanej instrukcji w pamięci programu. Adres ten jest przechowywany w specjalnie do tego przeznaczonym rejestrze zwanym wskaźnikiem instrukcji (IP). Tryb ten jest wykorzystywany przez rozkazy skoku.indeksowy (PIC, 8086)

Adresowanie to polega na obliczaniu adresu przez sumowanie zawartości specjalnie przeznaczonego do indeksowania rejestru, zwanego rejestrem indeksowym z adresem bezpośrednim, zapisanym w instrukcji. Obliczony w ten sposób adres jest adresem efektywnym. Tryb ten jest korzystny, gdy operujemy na blokach danych.bazowo-indeksowy ( 8086)

Zawartość rejestru bazowego (BX, BP) jest dodawana do zawartości rejestru indeksowego (SI, DI), tworząc adres do pamięci, pod którym znajduje się wartość danej. NOT [BX+DI]bazowo-indeksowe z przemieszczeniem

Stała jest dodawana do rejestru bazowego (BX, BP) oraz rejestru indeksowego (SI, DI), tworząc adres do pamięci, pod którym znajduje się wartość danej np. NOT [BX+DI+8]rejestrowy (i rejestrowy pośredni) (8086)

W adresowaniu rejestrowym operandy znajdują się w rejestrach wewnętrznych mikroprocesora. Jeżeli operand znajduje się w pamięci, to zespół wykonawczy EY oblicza jego 16-bitowy adres (przesunięcie) wewnątrz segmentu. Zespół BIU oblicza adres rzeczywisty na podstawie otrzymanego przesunięcia (adresu efektywnego EA) i zawartości wybranego rejestru segmentowego. Np. MOV AX, BX - w rejestrze AX zostanie zapisana zawartość rejestru BX.bazowy (8086)

Adresowanie bazowe jest to rodzaj adresowania pośredniego, gdzie rozkaz wskazuje na jeden z rejestrów bazowych BX lub BP i może zawierać 8-; lub 16-bitową wartość stanowiącą lokalne przemieszczenie. Adresem efektywnym jest suma zawartości rejestru bazowego i przemieszczenia. Np. MOV AX, [BP].

DMA

jest to bezpośredni dostęp do pamięci

dodatkowy moduł na magistrali systemowej

udaje procesor i w rzeczywistości przejmuje od procesora sterowanie systemem

moduł DMA działa na zasadzie wykradania cyklu procesora

Przetwarzanie potokowe

Na jednym końcu przyjmowane nowe elementy wejściowe, zanim jeszcze elementy poprzednio przyjęte ukażą się na wyjściu. W celu realizacji tej koncepcji stosujemy takie techniki jak:

zwielokrotnienie strumienia

pobieranie rozkazu z wyprzedzeniem

bufor pętli

przewidywanie rozgałęzienia

opóźnienie rozgałęzienia

System 360

był pierwszą zaplanowaną rodziną komputerów

modele różniły się wydajnością i ceną

wszystkie modele były kompatybilne programowo

z pewnymi rozszerzeniami i modyfikacjami architektura serii 360 pozostaje do dziś architekturą dużych komputerów

304 instrukcje o zmiennej długości i czasie wykonania

3 różne możliwe długości rozkazu

-16 trybów adresowania

Kod horyzontalny / wertykalny

V: - rozbudowany dekoder i minimalne słowo instrukcji!

H: - ograniczony dekoder, maksymalne słowo instrukcji

WDM

Typ sterowników typu PnP stosowany od Windowsa 98

następna VxD, obejmuje wsparciem Windowsy 98- Vista

Wyróżnia się 4 rodzaje (driver funkcyjny - główny driver, najczęściej napisany przez producenta i niezbędny do działania urządzenia) :

class driver - sterownik funkcyjny, mogący operować na dużej liczbie urządzeń tego samego typu (nie ma potrzeby pisania oddzielnych driverów dla każdej wersji urządzenia), w ujęciu programistycznym class driver może służyć jako baza dla bardziej specjalizowanych sterowników np. typu miniport (udostępnia interfejs)

miniport driver - sterownik funkcyjny do obsługi USB, SCSI, Audio i urządzeń sieciowych

bus driver - sterownik do obsługi magistral, może służyć jako kontroler, adapter czy mostek, może obsługiwać więcej niż jedną magistralę danego typu, używany jest do obsługi choćby USB, PCI, SCSI, FireWire...

filter driver - mogą dodawać i modyfikować funkcje obecnych już sterowników, nie muszą być związane z urządzeniem,

Wady: wygórowane wymagania dla nauki WDM, brak odpowiedniej współpracy z systemem zasilania, brak wsparcia dla sterowników pisanych czysto w user-mode

Scoreboarding

Algorytm stosowany w procesorach superskalarnych

Umożliwia synchronizację potoku i zabezpiecza przed hazardem RAW (wartość nim zostanie zapisana przez poprzednią instrukcję, jest już odczytana przez następną)

Polega na identyfikowaniu rejestrów procesora jako: ważnych i nieważnych

Odczyt możliwy jest tylko z ważnego rejestru

Rejestr oznaczany jest jako nieważny, gdy instrukcja mająca zapisać coś do tego rejestru opuszcza fazę odczytu

Wówczas inne instrukcje nie mają prawa korzystania z danego rejestru

Gdy instrukcja opuszcza fazę zapisu, rejestr oznaczany jest jako ważny i dane z rejestru są „odblokowywane” dla innych instrukcji

Algorytm Zastępowania Stron

Stosowany w stronicowaniu, jako element obsługi braku strony

W momencie, gdy brakuje wolnych ramek w pamięci należy zwolnić jedną z ramek poprzez zapisanie znajdującej się w niej strony na dysk

Taki zapis można dokonać tylko wówczas gdy odpowiedni bit (modyfikacji) w ramce jest ustawiony na 1

Szukaniem strony, która ma być usunięta z pamięci i zapisana na dysk zajmują się różne algorytmy:

FIFO - usuwamy stronę najdłużej znajdującą się w pamięci, prosty, łatwy w implementacji, zagrożenie to błędy - np. anomalia Beladiego

Algorytm Optymalny - usuwamy stronę najdłużej nieużywaną, idealny - teoretyczny - niemożliwy do implementacji

LRU - usuwamy stronę, która nie była używana najdłużej - lepszy wynik od FIFO, dosyć trudny do implementacji

Drugiej Szansy - analogiczny do FIFO, ale korzysta z bity odwołania (na początku zero, jeśli do strony się odwołaliśmy ustawiany na 1) - jeżeli bit odwołania jest równy 1, wówczas strona dostaje „drugą szansę” - bit ustawia się na 0 a strona ląduje na koniec kolejki

Zliczające (LFU i MFU) - zliczają liczby odwołań i usuwana jest albo strona o najmniejszej albo największej liczbie odwołań, trudne do implementacji, niezbyt skuteczne

Barrel Shifter

Ukł cyfrowy, zbudowany z MUX

Potrafi w jednym cyklu przesunąć słowo o daną liczbę bitów

Używany w ALU (jako stały komponent), chociażby przy okazji wyrównywania mantys w obliczeniach zmiennoprzecinkowych

Informacja

Miara niepewności pewnego zdarzenia

Rejestry

Rejestr wskaźników - zwany rejestrem stanu, przechowuje pewne specyficzne dane wynikające z obliczeń ALU takie jak: wynik równy zero, przeniesienie, przepełnienie, pożyczka, znak wyniku, parzystość. Można wykorzystywać ten rejestr do testowania pewnych warunków i tym samym implementować rozgałęzienia

Rejestr przejściowy - rejestr pomocniczy ALU, podobny do akumulatora, jednak dane z tego rejestru nie mogą być wyprowadzane na szynę danych

Rejestr rozkazów - wchodzi w skład jednostki sterującej, w nim przechowywany jest aktualnie wykonywany rozkaz

Rejestry 8086

Rejestry:

AX - Accumulator Register

BX - Base Address Register

CX - Count Register

DX - Data Register

BP - Base Pointer

SP - Stack Pointer

SI - Source Index Register

DI - Destination Index Register

IP - Instruction Pointer

Flagi:

OF - Overflow Flag

DF - Direction Flag

IF - Interrupt Enable Flag

TF - Trap Flag

SF - Sign Flag

ZF - Zero Flag

AF - Auxiliary Flag

PF - Parity Flag

CF - Carry Flag

Prawo Groscha

Zakup komputera większego i dwa razy droższego gwarantuje 4-krotne zwiększenie mocy obliczeniowej - obalone przez wprowadzenie układów scalonych

Mikroprogram

Opisuje cykl zegara za pomocą cyklu instrukcji

Każda instrukcja to wskaźnik na fragment mikrokodu, ładowanego i wykonywanego przez układ sterujący

Obecnie niezbyt powszechny

Mikroprocesor a mikrokontroler

Mikroprocesor: nastawiony na obliczenia, ograniczony kontakt z otoczeniem (wymaga od otoczenia więcej w ramach komunikacji )

Mikrokontroler: większy nacisk na kontakt z otoczeniem (porty komunikacyjne pozwalające wyprowadzać dane bezpośrednio na zewnątrz), słabsza moc obliczeniowa

Obecnie różnice się zacierają - producent określa czym jest produkt

Mechanizmy przerwań

sprzętowe: sytuacja wyjątkowa - krytyczna, maskowalna - można zwrócić uwagę

oprogramowania: programowe, breakpoints

Prawo Amdahla

Odnosi się do zwiększania wydajności

Nawet jeśli radykalnie przyspieszymy działanie dominującego elementu, to nie nastąpi radykalny wzrost wydajności całego systemu, gdyż wówczas elementem decydującym o wydajności stanie się element wcześniej niedominujący

Przyspieszenie: 1 / ( (1-t) + t / n ) ) , gdzie n - nkrotne przyspieszenie elementu, a t - udział elementu w systemie (np. 0.7 dla 70 %)

Kernel

Jądro systemu

Podstawowa część systemu operacyjnego, odpowiedzialna za wszystkie jego zadania

Wyróżniamy kilka podstawowych metod konstrukcji jąder:

jądro monolityczne - często stosowane w systemach typu Unix. Wszystkie zadania są wykonywane przez jądro, będące jednym, dużym programem działającym w trybie jądra.

mikrojądro - w tej technice z monolitycznego jądra zostaje tylko jego podstawowa część, reszta realizowana jako osobne procesy.

nanokernel - nanokernel jest jeszcze mniejszy od mikrojądra

exokernel - odmiana nanojądra. Cechą wyróżniającą jest możliwość zarządzania zasobami systemu przez nieuprzywilejowanego użytkownika, a rola jądra sprowadza się do zabezpieczania zasobów.

cachekernel - w tej technice jądro systemu buforuje obiekty systemowe takie jak wątki czy przestrzenie adresowe tak jak sprzęt komputerowy buforuje pamięć

jądro hybrydowe - kompromis między architekturą jądra monolitycznego i mikrojądra. W krytycznych usługach - np. stos sieci - usługi są na stałe wkompilowane w główny kod jądra, inne usługi pozostają oddzielone od głównego jądra i działają jako serwery (w przestrzeni jądra).Monolityczne: Linuch, Hybrydowe: Windows

Rodzaje Sterowników

Linuch:

Character Devide Drivers - sterowniki urządzeń sekwencyjnych.

Block Device Drivers - sterowniki urządzeń blokowych.

Network Device Drivers - chyba nie muszę pisać.

Windows:

Dos - sterownik to plik wykonywalny pracujący w trybie rzeczywistym

MS Windows (nakładka na Dos) - sterowniki to wykonywalne pliki .drv

Windows 3.x - pojawienie się koncepcji maszyny wirtualnej, pliki VxD ( Virtual Device Driver )

XP - WDM ( Windows Driver Model ).

Rodzaje Pamięci

Rejestry

RAM ( Random Access Memory )

SRAM ( Statyczna )

DRAM ( Dynamiczna )

SDRAM ( Synchronous Dynamic RAM , jedna dana na cykl zegara )

DDR ( Transmisja na obu zboczach sygnału )

RDRAM ( Rambus )

ROM (Read Only Memory )

PROM ( 1 krotnie programowalna , nie używana )

EPROM ( kasowanie za pomocą UV )

EEPROM ( wielokrotnie programowalna,kasowanie i zapis na drodze elektronicznej)

FLASH ( operacja na wielu komórkach w tym samym czasie ) ( NOR - RAM , NAND - w zastępstwie dysków )

Pamięć magnetyczna

DRAM jest tańszy oraz wolniejszy od SRAM.

SRAM nie wymaga ona odświeżania.

SRAM używa przerzutników (zestaw tranzystorów)

DRAM używa kondensatorów - ładunek trzeba odnawiać

SRAM jest bardzo drogi - jedna komórka pamięci składa się z czterech tranzystorów i dwóch oporników, dla porównania do utrzymania jednego bajta w DRAMie potrzeba jedynie tranzystora i kondensatora.

BIOS

BIOS to zapisany w pamięci stałej, inny dla każdego typu płyty głównej komputera, zestaw podstawowych procedur pośredniczących pomiędzy systemem operacyjnym a sprzętem.

W wypadku płyty głównej BIOS testuje sprzęt po włączeniu komputera, przeprowadza tzw. POST ("Power On Self Test"), zajmuje się wstępną obsługą urządzeń wejścia/wyjścia, kontroluje transfer danych pomiędzy komponentami takimi jak dysk twardy, procesor czy napęd CD-ROM. Inicjuje program rozruchowy.

TRYBY PRACY PROCESORA 386

określają m.in. sposób zarządzania pamięcią i uprawnienia uzytkownika

Wyróżniamy tryby:

Tryb Rzeczywisty - W trybie tym brak ochrony pamięci przed użyciem przez inny proces i brak obsługi wielozadaniowości. W trybie rzeczywistym pracowały programy w systemie operacyjnym DOS. Dwa adresy logiczne mogą wskazywać na ten sam adres fizyczny. Adresowanie pamięci w zakresie 1 MB.

Tryb Chroniony - Umożliwia adresowanie pamięci w większym zakresie niż 1MB (tryb rzeczywisty), wprowadza wiele nowych udogodnień wspierających wielozadaniowość(!), takich jak: sprzętowa ochrona pamięci (układ MMU), wsparcie przełączania kontekstu procesora i wiele innych. Wszystko pod kontrolą OS, aby aplikacja nie mogła „namieszać” w systemie.

Tryb Wirtualny - Tryb pracy procesorów, dostępny w trybie chronionym, który umożliwia uruchamianie programów przeznaczonych dla trybu rzeczywistego. W odróżnieniu od "prawdziwego" trybu rzeczywistego, dostęp do portów procesora jest sankcjonowany przez system operacyjny pracujący w trybie chronionym.

Tryb Wirtualny jest wykorzystywany do uruchamiania programów DOS-owych. System Windows posiada wbudowane mechanizmy umożliwiające uruchomienie takich programów (w Windows NT jest to NTVDM), natomiast dla systemu Linux istnieją programy dosbox oraz dosemu.

Tryb SMM- tryb zarządzania sprzętem przez sys operacyjny, niedostępny z poziomu uzytkownika

Komendy Assemblera

Arytmetyczne:

ADD - dodawanie

SUB - odejmowanie

MUL - mnożenie

DIV - dzielenie

INC/DEC - inkrementacja/dekrementacja

Logiczne:

AND , OR , EXOR , NOT

Przesłań:

MOV - przenieś

STR - zachowaj ( store )

LD - load ( załaduj )

IN - input

OUT - :]

SET - ustaw

PUSH/POP

Sterujące programem:

JMP - skocz

Jc - warunek skoku

CALL - skocz do funkcji

RET - return

SKIP

Endiany !! What is that?!

Wyszukiwarka

Podobne podstrony:

Caporegime Capruzzi, Semestr 3, Architektura Systemów Komputerowych

Zegar sciaga, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Ściągi

sciaga, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Zaliczenie z ASK

sciaga grafika, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Ściągi

klawiatura, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Sprawozdania

ZAGADNIENIA EGZAMINACYJNE Z PRZEDMIOTU, Semestr 4, Architektura systemów komputerowych

arch zal, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Zaliczenie z ASK

zagadnienia na zaliczenie, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych,

arch02, UŁ Sieci komputerowe i przetwarzanie danych, Semestr II, Architektura systemów komputerowych

ASK-koło pierwsze pytania z mojej grupy, Edukacja, studia, Semestr IV, Architektura Systemów Kompute

arch05, UŁ Sieci komputerowe i przetwarzanie danych, Semestr II, Architektura systemów komputerowych

arch07, UŁ Sieci komputerowe i przetwarzanie danych, Semestr II, Architektura systemów komputerowych

ask4, Edukacja, studia, Semestr IV, Architektura Systemów Komputerowych, Wyklad

opracowane pytania na ASK@, Edukacja, studia, Semestr IV, Architektura Systemów Komputerowych, Oprac

Projekt 3, Edukacja, studia, Semestr IV, Architektura Systemów Komputerowych, Projekt, Projekt 3

arch06, UŁ Sieci komputerowe i przetwarzanie danych, Semestr II, Architektura systemów komputerowych

ask1, Edukacja, studia, Semestr IV, Architektura Systemów Komputerowych, Wyklad

arch01, UŁ Sieci komputerowe i przetwarzanie danych, Semestr II, Architektura systemów komputerowych

Teoria 2003, Edukacja, studia, Semestr IV, Architektura Systemów Komputerowych, Opracowania pytań

więcej podobnych podstron