CMOS3

4093 Cztery 2-wejściowe bramki NAND Schmitta

• Cz83 propagacji: 300ri8 przy 5Vr 150ns przy tOV

• Liczny pobór prądu: 0.4mA przy 5V. 0,8mA przy 10V

• Częstotliwość pracy: 1 MHz

|

A |

e |

0 |

|

L |

L |

H |

|

L |

M |

M |

|

H |

L |

M |

|

H |

H |

L |

l±J LŁJ LU L2J L2J Q

A b o

|

J1 (KI) |

J2(K2) |

J3(K3J |

J (K) |

|

L |

X |

X |

L |

|

X |

L |

X |

L |

|

X |

X |

H |

L |

|

H |

H |

L |

H |

KI K2 K3 O

4504 Sześciokrotny konwerter poziomów TTL na CMOS

RR - rejestr wyniku IO...I3-we|ścia instrukcji

u*. w o^<h, S9

|

nr |

i,iyi rei nn n |

ii r |

ii rei i i |

|

>r TT | |||

|

n j-iir iii iii l |

J L J UJ | ||

CHp MM OM* O 1} II D -L

|

Modę |

E | Pcdom |

0 |

Po? tom | |

|

L |

Jlh |

CMOS |

L |

CMOS |

|

Ł |

H |

CMOS |

H |

CMOS |

|

H |

L |

TTL |

L |

CMOS |

|

H |

H |

TTL |

H |

CMOS |

4094 8-brtowy uniwersalny rejestr magistrali

-

W TJ V» Vł Y Yt VT C MH

|

n u rur | |||

|

L \ | |||

|

- \2W£kn%£iyy: |

1 | ||

|

L . |

i jujTżnŁdjiLiLiT |

iJ | |

x i7 a n m n e n

Uh 06 06 OB 07 O* CW

|

rei re rei rei re r |

jO-iy. |

-ClL |

|

\ ; T; T / • pT~7'- | ||

|

i i lii 111 i i ilr iii tli | ||

O T 01 Q2 OJ O*

4095 Przerzutrtik JK Master-Slave

|

T |

j |

K |

8 |

R |

Qm1 |

On*1 |

|

X |

X |

X |

L |

H |

L |

H |

|

X |

X |

X |

H |

L |

H |

L |

|

X |

X |

X |

H |

H |

L |

L |

|

L |

L |

L |

Oi |

On | ||

|

r |

L |

H |

L |

L |

L |

L |

|

i |

H |

L |

L |

L |

H |

L |

|

i |

H |

H |

L |

L |

On |

On |

|

J1<K1) |

J2<K2) |

JS(K3> |

JfK) |

|

L |

X |

X |

L |

|

X |

L |

X |

L |

|

X |

X |

L |

U |

|

H |

H |

H |

H |

9 T Ki K2 K3 O

j i rei np m

LUTU

4098 Podwójny multiwibrator monostabilny

|

"rii rEi n |

R *tr -re 0 <3' 4i rei rei nn rei rri | |

|

> | ||

|

yL |

i m n i ri m * n *tttt R .TB -Ttł 0 5 -I- | |

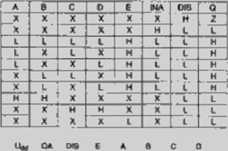

4501 Trzy bramki NAND

|

A |

8 |

c |

D |

0 |

|

H |

H |

H |

H |

L |

|

l |

X |

X |

X |

H |

|

X |

L |

X |

X |

H |

|

X |

X |

L |

X |

H |

|

X |

X |

X |

L |

H |

|

fc.11 |

k.12 |

k.14 |

k-15 |

|

L |

L |

M |

L |

|

L |

H |

L |

H |

|

H |

L |

L |

H |

|

H |

« |

L |

H |

U« o od

LU UJ UJ LU ute o *

T

4505 64x1 bit statyczna pamięć RAM

|

CE1 |

CE2 |

sirobe |

R/W |

FunKcjń |

|

t |

X |

X |

X |

- |

|

X |

L |

X |

X |

- |

|

X |

X |

L |

X |

- |

|

H |

H |

H |

L |

wrtta |

|

H |

H |

M |

H |

reart |

4099 8-błtowy adresowalny zatrzask

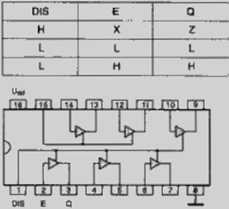

4502 Sześciokrotny inwertef/foufor z wyjściami trójstanowymi

|

ots |

INH |

E |

Q |

|

L |

L |

L |

H |

|

L |

L |

M |

L |

|

L |

H |

X |

L |

|

M |

X |

X |

z |

4506 Dwie bramki AND/OR z możSwośdą ekspansji

rei rei rei rei pgnn rei

|

i | ||

|

iJj UU LlJ'LiJ ii |

TuTTLTTTr | |

A 8 C D E INA OB

■ĘSl

O* 08 Oi 09 OJ Ol

|

rTTTTTT | ||||

|

( U»- 7 | ||||

|

TC |

U, I | |||

|

J lii lii ll) UJ | ||||

4096 Przerzutnik JK Master-Slave

|

T |

j |

K |

S |

R |

Qn+1 |

On*1 |

|

X |

X |

^ X |

L |

H |

L |

H |

|

X |

X |

X |

H |

L |

H |

L |

|

X |

X |

X |

H |

M |

t |

L |

|

L |

L |

L |

L |

On |

<y | |

|

J |

L |

H |

L |

l |

L |

L |

|

r |

H |

L |

L |

L |

H |

L |

|

r |

H |

H |

L |

L |

& |

On |

4500 Procesor 1-bitowy

|

I* |

W |

1 -A*0 | ||||||

|

* 1, L L i tri |

k H |

MOPO |

Md | |||||

|

i 4 |

L i. M L M L |

H |

*07 |

-T **” |

•PKMk-AA OPO.li-.MK | |||

|

1 ♦ |

i w K ' " |

c M |

M t |

0"C |

OM | |||

|

L |

* |

N |

K |

«X5A | ||||

|

* |

m |

i |

l |

k t*> |

om | |||

|

> |

rt |

L |

1 |

M PK |

i —W*. | |||

|

A |

* |

L |

NJ>. •* |

. | ||||

|

C |

M |

H |

Ł L J** |

ltrv |

1 | |||

|

t> |

M |

M |

i h Hm | |||||

|

f |

N |

H |

.2=- | |||||

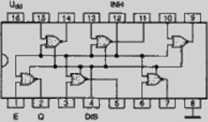

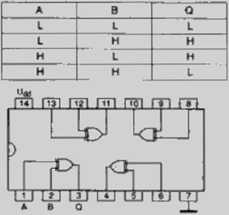

4503 Sześciokrotny bufor z wyjściami trójstanowymi

• Czas propagacji: 30ns przy 10V, 40ns przy 5V

• Łączny pobór prądu: 3mA przy 5V, 6mA przy 10V

• Częstotliwość na wejściu: 1MHz

4507 Cztery bramki EX-OR

4508 Podwójny zatrzask 4-bitowy

• Czas propagacji: 350ns przy 10V, 175ns przy 5V

• Łączny pobór prądu: 0,4mA przy 5V, 0,8mA przy 10V

• Częstotliwość danych: 1MHz

Wyszukiwarka

Podobne podstrony:

112 113 112 Rys. 4.7. Charakterystyka wejściowa / bramki NAnD - TTL kierunek prądu wejściowego ma sp

Charakterystyki wejściowej bramki NAND Druga część ćwiczenia miała na celu uzyskanie charakterystyki

CIMG5129 11. Podstawowe bramki logiczne11.1. Bramka NAND Tablica prawdy i schemat elektryczny dwu we

Układ scalony 4093 cztery bramki NAND z histerezą 14 13 12 11 10 9 8 n n n n n n n □ □□□□□ u

alarm motocykl horn Circuit for motorcycle use Gates Ul-a and Ul-b of the 4093 ąuad 2-input NAND Sch

alarm motocykl horn Circuit for motorcycle use Gates Ul-a and Ul-b of the 4093 ąuad 2-input NAND Sch

alarm motocykl horn Circuit for motorcycle use Gates Ul-a and Ul-b of the 4093 ąuad 2-input NAND Sch

Image475 8( - Bramki z układem Schmitta b Start U ” St1_I L Rys. 4.593. Autorozdzi

Image511 określają poziom dyskryminacji sygnałów wejściowych. Jeżeli na wejście prze-rzutnika Schmit

strona7 (6) Zadanie 24. Którą charakterystykę bramki NAND przedstawia rysunek? A.

• Wejścia i bramki nie wykorzystane Konsekwencją minimalizacji liczby układów scalonych jest niekied

112 113 112 Rys. 4.7. Charakterystyka wejściowa bramki NATO - TTL kierunek prądu wejściowego ma spos

122 123 1S5» Z uwagi na wysoką Oporność wejściową bramki, impedancja wejściowa takiego tranzystora m

http://layer.uci.agh.edu.pl/maglay/wrona Rys. 4.2 Schemat ideowy bramki NAND z serii standardowej TT

http ://l ay er. uci. agh. edu. pl/maglay/wrona 5.4.1. Bramki NAND i

więcej podobnych podstron