Image166

Dane

ft

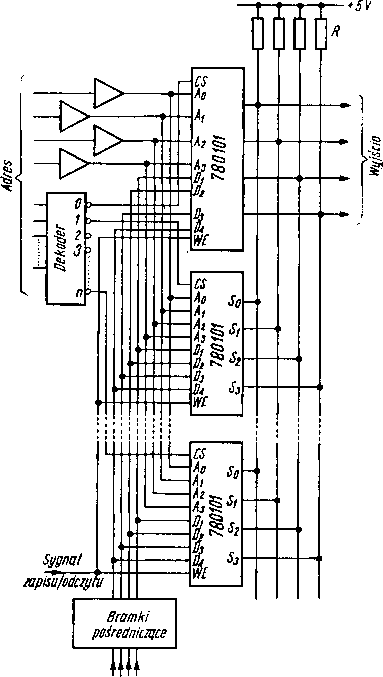

Bramki sterujące wejścia adresowe i wejścia danych

b Przy dużej liczbie wejść obciążających

Rys. 4.123. Blok pamięci o pojemności 16 słów czterobitowych

nmax = 40 układów pamięci

in Q4

“t>—{ nmax - 50 układów pamięci iS04

—-1 nmax-80 układów pamięci

r>-

‘-0-.

Wejścia

adresowe

pamięci

a

Aą~

b

-CS,

-CSi

As ■

-CSi

A<—?-£>>-

cs.

CStf

42

-cs$

7

S 3 3>

H \-CSj AS

1 1-/ At

Al

|

c |

A 154 B p |

|

i | |

|

D | |

-CSf -CSi -CSJ

-CSfs

-CS/e

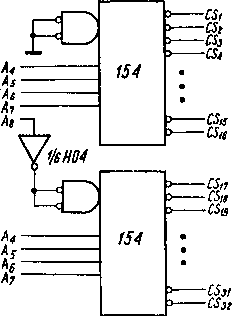

Rys. 4.124. Przykłady wejściowych układów sterujących

a) z zastosowaniem bramek 04, H04, S04,

b) z bramek z równoległymi wejściami

Rys. 4.125. Dekodery sterujące wejściami CS w blokach pamięci o pojemności:

a) 2X16 stów. b) 4X16 stów. c) 8X16 s!6w. d) 16X16 stów. e) 32X16 słów

176

Wyszukiwarka

Podobne podstrony:

Image104 + y(t) = ku(t), gdzie dt u(t) - sygnał wejściowy, y(t) - sygnał wyjściowy, T - stała czasow

Image14 dla pierwszej składowej sygnału wejściowego U] (t)

122 123 1S5» Z uwagi na wysoką Oporność wejściową bramki, impedancja wejściowa takiego tranzystora m

Funkcia: scanf() <stdio.h> odczytuje dane ze standardowego strumienia wejści

10 (69) 10 Wzorcowe czasy otwarcia bramki na wejściu (2) uzyskiwane są przez odpowiednie obniżenie (

CMOS3 4093 Cztery 2-wejściowe bramki NAND Schmitta • Cz83 propagacji: 300ri8 przy

Slajd8 Schemat monitora ze zmienną warunkową Dane dzielone C: Condition kolejka wejściowa kolejka zm

122 123 .......... Z uwagi na wysoką óporność wejściową bramki, impedancja wejściowa takiego tranzys

blokuje bramkę B24» która zamyka przejście dla wzorcowych impulsów zegarowych sterujących wejście W

lab2 Wejścia danych

Bramki logiczne cz2 Układy cyfrowe 37 bramki wielo wejściowe. Symbol przykładowej cztero wejściowej

Image12 3, P-z^kłady nikroorcgramowanych układów sterujących do wykonania w trakcie ćy/iczama i :J/.

więcej podobnych podstron