Image175

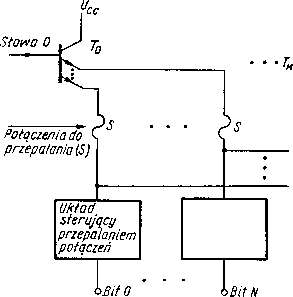

spowodował dołączenie emitera tranzystora do wspólnego potencjału. Jednocześnie zostaje podwyższone napięcie Ucc powodując zwiększenie wartości prądu płynącego w wybranych połączeniach 5 i przepalenie ich.

'BH •B0

Rys. 4.134. Typowa komórka pamięci PROM

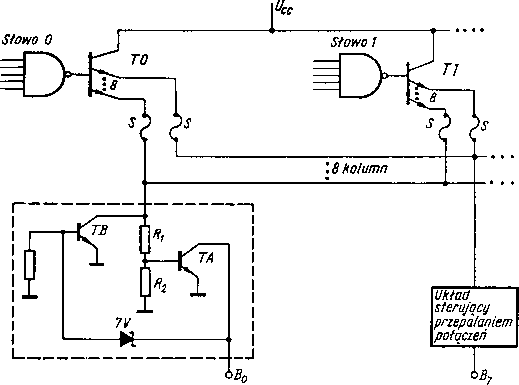

Typowy schemat ideowy pamięci PROM o organizacji 32X8 bitów przedstawiono na rys. 4.135. Pamięć zawiera 32 tranzystory n-p-n, z których każdy ma połączenie S przepalone w obwodach emiterów. Poszczególne linie słowa są wybierane poprzez 5-argumentowe bramki I-NIE (NAND), które powodują wysterowanie tranzystora i przepływ prądu przez rezystory Rr i R2.

Załóżmy, że należy zaprogramować stan 1 w pierwszej pozycji słowa 0, a na pozostałych pozycjach stany 0. Na wejście B0 należy wówczas podać napięcie

Rys. 4.135. Schemat ideowy pamięci PROM o organizacji 32X8 bitów

185

Wyszukiwarka

Podobne podstrony:

Image418 -emiter tranzystora T8 osiągnie wartość wystarczającą do wprowadzenia go w stan przewodzeni

skany048 9 i < wspólnym wykresie charakterystyki diody, złącza emiterowego tranzystora i prostej

Współczynnik a określa jaka część prądu emitera dopływa do kolektora. W dobrych tranzystorach jest o

Image14 (14) Projekty AVT Projekty AVT Rys. 2 Rys. 3 podłączanej z jednego końca do wspólnego zacisk

Image115 r W układach praktycznych należy dążyć do tego, aby stan 1 na wejściu synchronizującym trwa

image11 Dopasowanie nacięcia modułu SIMM do gniazda

Image122 a Rys. 4.62 Układ służący do równoległego wprowadzania informacji z czterech źródeł do reje

Image124 Rys. 4.66. Układ służący do równoległego wyprowadzania informacji z rejestru Q

Image12 3, P-z^kłady nikroorcgramowanych układów sterujących do wykonania w trakcie ćy/iczama i :J/.

Image522 Tranzystory T3 i T4 pracują w układzie wtórników emiterowych, tranzystor TI — w układzie kl

więcej podobnych podstron