Image257

Na rysunku 4.280 przedstawiono schemat ideowy układu, umożliwiającego realizację operacji X2±Y2. Przed rozpoczęciem wykonywania tej operacji należy wyzerować liczniki i wpisać wartość X i Y do liczników L3 i L4 zliczających wstecz. Po podaniu sygnału „Start” impulsy o częst. F są podawane z odpowiednim przesunięciem czasowym na wejście liczników Lx i L3. Impulsy przepełnienia licznika Lx są odejmowane od zawartości licznika L3.

W każdym cyklu działania licznika Lu do licznika L5 i licznika rewersyjnego jest wprowadzane X impulsów. W chwili wyzerowania licznika L2 następuje odblokowanie wejścia licznika Lx i do licznika L5 i licznika rewersyjnego zostaje wprowadzone X*X = X2 impulsów. Podobnie działają liczniki L2 i L4, realizujące operację Y • Y = Y2.

Impulsy z liczników Lx i L2 są sumowane za pomocą bramki LUB (OR). Wynika stąd konieczność przesunięcia czasowego impulsów podawanych na wejścia liczników Lx i L2. Stan wyzerowania licznika L3 lub LA powoduje blokadę generatora.

Obliczanie pierwiastka kwadratowego

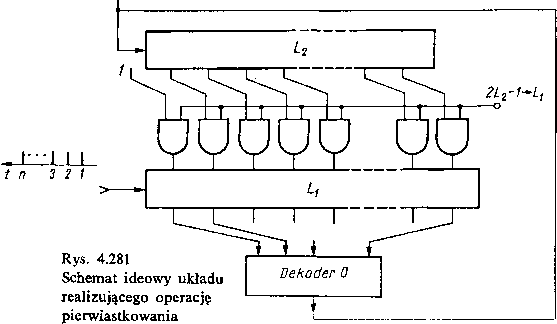

Schemat blokowy układu służącego do obliczania pierwiastka kwadratowego jest przedstawiony na rys. 4.281. Przed rozpoczęciem operacji licznik Lx zlicza-

L3

jący wstecz należy ustawić w stan 1. Po podaniu na jego wejście pierwszego impulsu osiągnie on stan zerowy. W następstwie tego, dekoder 0 wytwarza impuls (impulsy wytwarzane przez dekoder 0 są zliczane za pomocą licznika L2). Stany liczników w poszczególnych etapach operacji są przedstawione w tablicy 4.16. Każdy z etapów kończy się wówczas, gdy licznik Lx osiągnie stan zerowy. Wtedy zawartość licznika L2 podwojona i zwiększona o 1 zostaje przepisana do licznika Lu a następnie impulsy wejściowe ciągu X są podawane na wejście licznika Ll9 aż do chwili, w której licznik Lx osiągnie stan zerowy. Jeśli wynik

Wyszukiwarka

Podobne podstrony:

Image146 Wyjścia Na rysunku 4.98 przedstawiono schemat ideowy układu licznika Johnsona mod. 16 zbudo

Image274 Na rysunku 4.305 przedstawiono schemat ideowy kaskadowego połączenia trzech programowanych

Image100 Na rysunku 4.22 przedstawiono schemat ideowy bramki I-LUB-NIE realizującej funkcję: F= AB+C

Image141 Na rysunku 4.88 przedstawiono schemat ideowy pamięci szeregowej, zbudowanej z rejestrów prz

Image145 Na rysunku 4.95 przedstawiono schemat ideowy wykorzystania rejestru 198 jako licznika pierś

Image215 Na rysunku 4.209 przedstawiono schemat logiczny 8-bitowego licznika synchronicznego, z doda

Image431 Na rysunku 4.515 podano schemat ideowy układu zbudowanego w oparciu o jeden przerzutnik mon

Image481 Na rysunku 4.602 przedstawiono schemat logiczny układu, stanowiącego rozwinięcie schematu i

Image517 Na rysunku 4.658 przedstawiono schemat ideowy translatora sygnałów, w którym czasy narastan

Image566 Na rysunku 4.747 przedstawiono schemat logiczny układu sterującego polem odczytowym, składa

więcej podobnych podstron