Image215

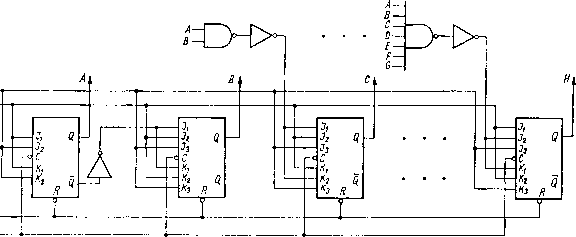

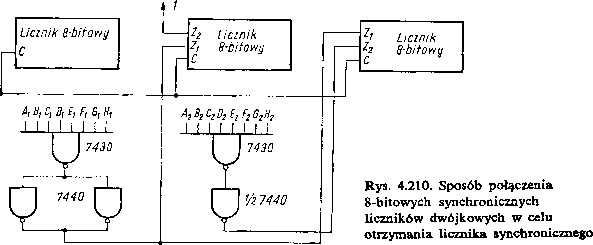

Na rysunku 4.209 przedstawiono schemat logiczny 8-bitowego licznika synchronicznego, z dodatkowymi wyprowadzeniami Zx i Z2# które będą wykorzystywane do wprowadzenia sygnałów przeniesienia, przy łączeniu jednostek 8-bitowych w licznik o większej pojemności. Zasadę łączenia tego typu jednostek licznika w licznik o większej pojemności przedstawiono na rys. 4.210. Maksy-

Rys. 4.209. Synchroniczny licznik dwójkowy z przeniesieniami równoległymi i dodatkowymi wyprowadzeniami Z\ i Z2

Wyszukiwarka

Podobne podstrony:

Image284 Przykłady rozwiązań dwójkowych sumatorów równoległych Na rysunku 4.324 przedstawiono schema

Image125 Na rysunku 4.68 przedstawiono schemat logiczny czterobitowego rejestru przesuwającego, zbud

Image257 Na rysunku 4.280 przedstawiono schemat ideowy układu, umożliwiającego realizację operacji X

Image274 Na rysunku 4.305 przedstawiono schemat ideowy kaskadowego połączenia trzech programowanych

Image481 Na rysunku 4.602 przedstawiono schemat logiczny układu, stanowiącego rozwinięcie schematu i

Image566 Na rysunku 4.747 przedstawiono schemat logiczny układu sterującego polem odczytowym, składa

Image146 Wyjścia Na rysunku 4.98 przedstawiono schemat ideowy układu licznika Johnsona mod. 16 zbudo

Image100 Na rysunku 4.22 przedstawiono schemat ideowy bramki I-LUB-NIE realizującej funkcję: F= AB+C

Image141 Na rysunku 4.88 przedstawiono schemat ideowy pamięci szeregowej, zbudowanej z rejestrów prz

Image145 Na rysunku 4.95 przedstawiono schemat ideowy wykorzystania rejestru 198 jako licznika pierś

Image305 Na rys. 4.350 przedstawiono schemat logiczny tetrady sumatora dziesiętnego — akumulującego.

więcej podobnych podstron