Image390

słowa wejściowego. Generator przedstawiony na rys. 4.455 wymaga zastosowania tylu przełączników, ile bitów ma generowane słowo. Długość generowanych słów można w tego typu rozwiązaniach zwielokrotnić łącząc multipleksery w układy o zwiększonej liczbie wejść.

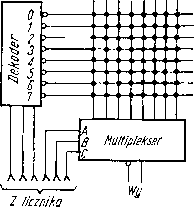

Generatory słów o zaprogramowanej sekwencji bitów w cyklu można zbudować wykorzystując dekodery i multipleksery (rys. 4.456). Układ, składający się

Rys. 4.456. Schemat logiczny generatora słów o zaprogramowanej sekwencji bitów w cyklu

z dekodera o ośmiu wyjściach i multipleksera o ośmiu wejściach, wytwarza słowo o długości 64 bitów. Rozwiązanie takie jest mniej elementochłonne niż rozwiązanie wykorzystujące tylko multipleksery.

Pamięci

W wielu zastosowaniach są wymagane pamięci o niewielkiej pojemności, z możliwością łatwego ich przeprogramowania. Pamięć taką można zbudować wykorzystując multipleksery (rys. 4.457a). Wejścia D0 ~ Z)7 multiplekserów są wejściami służącymi do programowania. Jeśli na wejścia adresowe A, B i C będą podawane adresy z wyjść 3-bitowego licznika zliczającego w naturalnym kodzie dwójkowym, to na wyjściach otrzymuje się kolejno 8 słów n-bitowych, przy czym n — liczba multiplekserów. Pamięć przystosowaną do programowania za pomocą zwieraczy kołkowych przedstawiono na rys. 4.457b.

Przykładowe rozwiązanie pamięci o pojemności 64 słów 4-bitowych jest przedstawione na rys. 4.458. Do zbudowania tej pamięci wykorzystano dekodery i multipleksery. W tak rozwiązanej pamięci zaleca się stosować diody germanowe, ponieważ charakteryzują się małym spadkiem napięcia w kierunku przewodzenia.

Na rysunku 4.459a przedstawiono implementację pamięci stałej. Pamięć ta służy do konwersji 4-bitowego naturalnego kodu dwójkowego na 16 znaków międzynarodowego alfabetu telegraficznego nr 2 (rys. 4.459b).

Układ do przesuwania danych

Przesuwanie danych, integralna część operacji cyfrowego mnożenia, dzielenia i skalowania, jest zazwyczaj realizowane za pomocą układów zbudowanych w oparciu o rejestr przesuwający. Dane są wprowadzane równolegle do rejestru, przesuwane w lewo lub w prawo i wyprowadzane równolegle. W przypadku zastosowania rejestru, przesunięcie danej o jedną pozycję odbywa się w czasie

Wyszukiwarka

Podobne podstrony:

Image349 Implementacja równań (6) jest przedstawiona na rys. 4.400. Typowy czas propagacji sygnału w

Image365 W dekoderze dwupoziomowym 6/64 przedstawionym na rys. 4.420 najpierw są dekodowane 3 najsta

066 (8) - 66 - Zadanie 3«75« Określić impedancję wejściową Z-e dwójnika przedstawionego na rys. 3*75

Image312 Schemat logiczny jednotetradowego sumatora w kodzie „+3” przedstawiono na rys. 4.357. Na ry

Image325 Układ przedstawiony na rys. 4.372, spełniający równanie (14), jest układem najszybszym, gdy

Image345 Implementacje funkcji (1) i (2) przedstawiono na rys. 4.394. W układach tych, jeśli żadne z

Image348 W układzie przedstawionym na rys. 4.399 sygnał przeniesienia blokującego propaguje tylko pr

Image355 Implementacje układów realizujących funkcje (3) oraz funkcje (4) przedstawiono na rys. 4.40

Image371 Schemat logiczny układu realizującego powyższe funkcje przełączające przedstawiono na rys.

Image378 Lamp Test). Schematy logiczne transkoderów scalonych 46, 47 i 48 są przedstawione na rys. 4

276 (31) 27t) OHi.ICV.ANIK KONSTRUKCYJNE wzmacniacza, przedstawiono na rys. XVI 1.7. Napięcie z gene

więcej podobnych podstron