skanuj0008

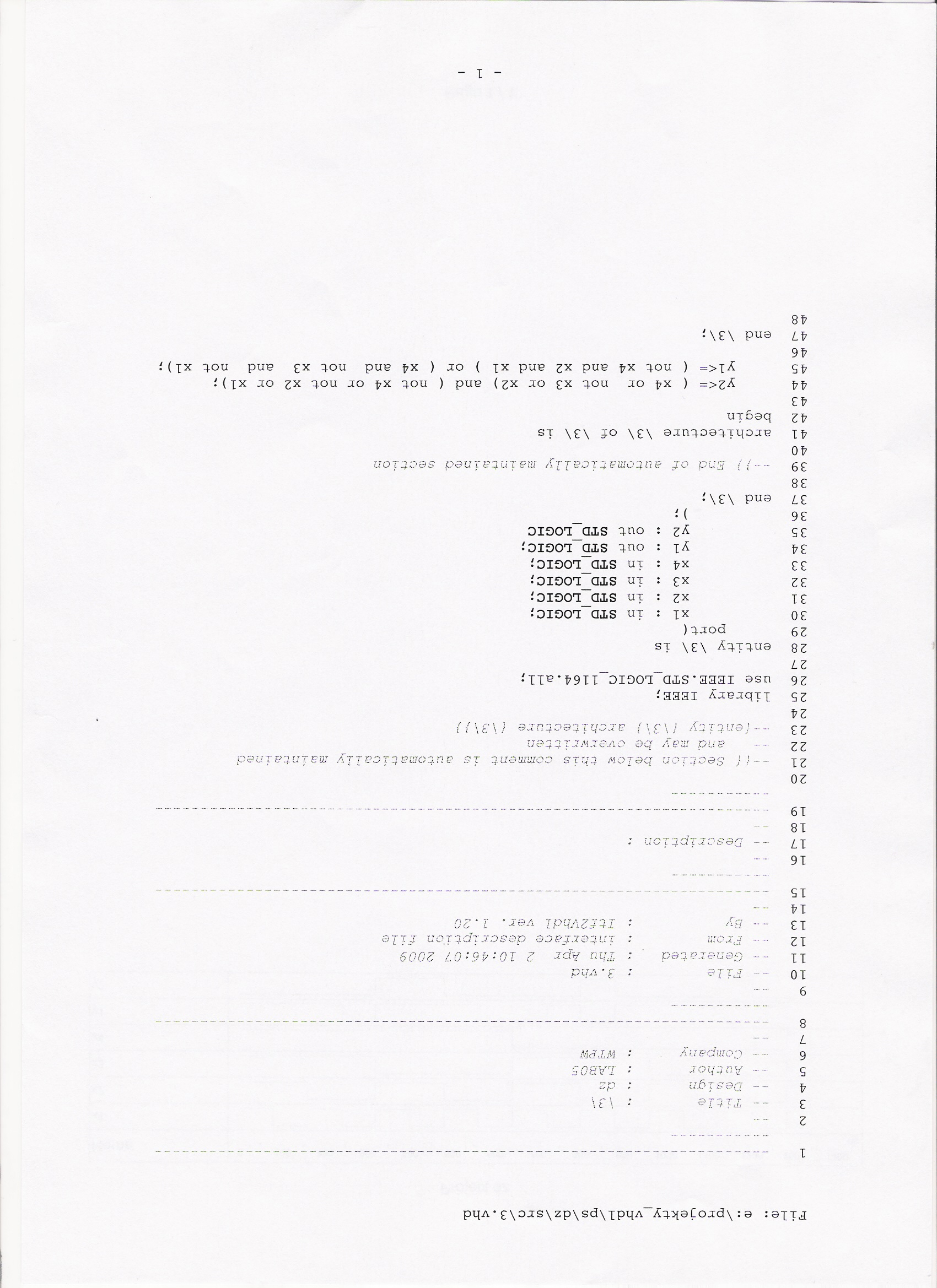

File: e:\projekty_vhdl\ps\dz\src\3.vhd

1

2

3 Titla : \3\

4 -- Design : dz

5 ...... Aut hor : LABO5

6 Company : W7PN

7

9

10 11 12

13

14

15

16

17

18

19

20 21 22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

■File : 3.vhd

Generated ; Thu Apr 2 10:46:07 2009

....... From : interface deser iptibn file

...... By : It£2Vhdl. ver. 1.20

-- Description :

-{{ Section below this comment is automatically maintained and may be overwrittetn ■- - {en t i ty {\ 3 \} arch i tecture {13 \ } }

library IEEE;

use IEEE.STD_LOGIC_l164.all;

entity \3\ is port (

x 1 : x2 : x3 : x4 : yl : y2 : );

end \3\;

in STD_LOGIC; in STD_LOGIC; in STD_LOGIC; in STD_LOGIC; out STD_LOGIC; out STD LOGIC

- ■■■ |} En d of aut om a t i cal 1 y mai n ta i ned sect. i o n

architecture \3\ of \3\ is begin

y2<= ( x4 or not x3 or x2) and ( not x4 or not x2 or xl); yl<= ( not x4 and x2 and xl ) or ( x4 and not x3 and not xl

end \3\;

1

Wyszukiwarka

Podobne podstrony:

skanuj0005 File: e:projekty_vhdlpsdzsrczap.vhd 1 2 3 4 5 6 7 8 9 10

skanuj0030 (43) w projekcie tożsamości andragogów to dylemat: czy poprzestać na „byciu ekspertem”, c

skanuj0060 (46) Bryonia alba M.f. gutt. S. 3 x dz. 5 kropli C4 aa 5,0 19. Rp. (lek przeciwko przezię

skanuj0006(1) Temat projektu Określić wielkość ciśnienia statycznego górotworu na obudowę wyrobisk c

skanuj0006 Temat projektu Określić wielkość ciśnienia statycznego górotworu na obudowę wyrobisk chod

skanuj0001 (125) PROJEKTOWANIE PODZESPOŁÓW SAMOCHODÓW, Poznań, Dzienne, Inżynierskie, SiC, sem.6, 20

skanuj0001 (208) Projekt okładki, stron tytułowych i ilustracje Marcin Szczygielski Redakcja Jacek G

skanuj0132 (13) Projektowanie połączeń wymagających dokładnego obliczania siły Q i średnicy śrub wyk

więcej podobnych podstron