a1 2

Imię i NiwWrt.

Cmi iMMkww

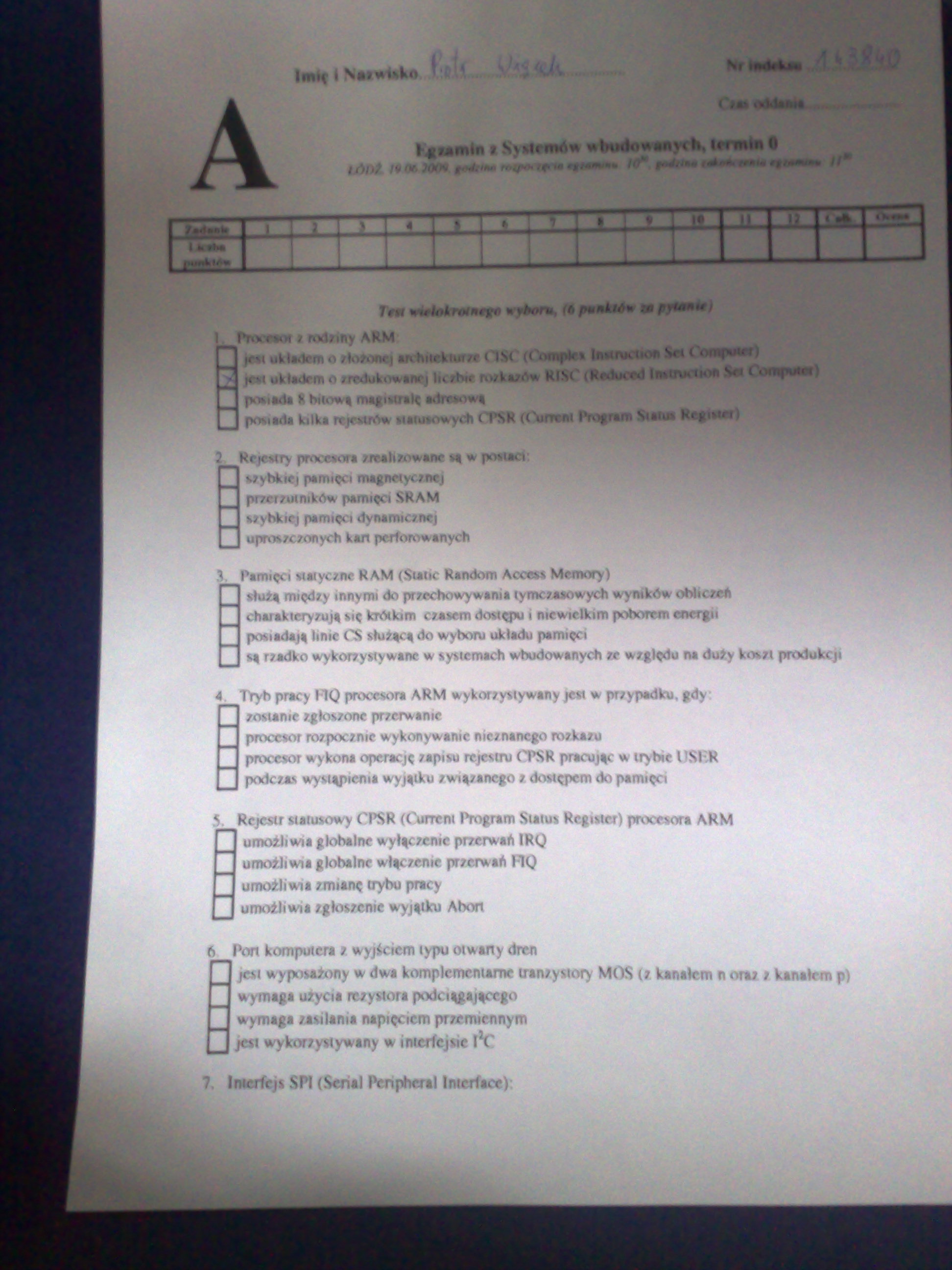

KgMmin a SyMaMśw wbudowanych, termin I

lAftt Itfó MO* f«<b!M Mifmtctn tftmnn Hf* f-*-’-- ------| )(•

|

Trn |

v rr |

♦ 1 7 1 • 1 « i ia |

Cafc | |||||

|

..latar |

- * * i ----1_; |

i J—: |

_J—L - 1 i |

Tm wIiUmmi* naftom, fi ymłn> m pytanie)

1

Nww t rodziny A RM

jest układem o rtanwj wckMura CISC (Comple* Instruction Set Computer)

jaat układem e zredukowanej liczbie rozkazów RISC (Reduced Instruction Sfl Comjwtar)

posiada 8 bilowi magistralę adresową

posiada kilka H)auM sinusowych CTSR (Ourrcnt Program Status Register)

2. Rejestry procesora zrealizowane «ą w posuci: szybkiej pamięci magnetycznej _ przerywników pamięci SRAM szybkiej pamięci dynamicznej uproszczonych kart perforowanych

3. Pamięci siaiycznc RAM (Stanc Random Access Memory)

abiżą między innymi do przechowywania tymczasowych wyników obliczeń charakteryzuję się krótkim czasem dostępu i niewielkim poborem energii posiadają linie CS służącą do wyboru układu pamięci

są rzadko wykorzystywane w systemach wbudowanych ar względu na duży koszt produkcji

4. Tryb pracy P1Q procesora ARM wykorzystywany jest w przypadku, gdy zostanie zgłoszone przerwanie procesor rozpocznie wykonywanie nieznanego rozkazu proocaor wykona operację zapisu rejestru CPSR pracując w trybie USER _ podczas wystąpienia wyjątku związanego z dostępem do pamięci

Rejestr statusowy CPSR (Current Program Status Register) procesora ARM umożliwia globalne wyłączenie przerwań IRQ umożliwia globalne włączenie przerwań F!Q umożliwia zmianę trybu pracy umożliwia zgłoszenie wyjątku Abort

6 Port komputera z wyjściem typu otwarty dren

_ jest wyposażony w dwa komplementarne tranzystory MOS (z kanałem n oraz z kanałem p) _ wymaga użycia rezystora podciągającego _ wymaga zasalania napięciem przemiennym _ jen wykorzystywany w interfejsie f*C

7. Interfejs SPI (Serial Peripheral Interface)

Wyszukiwarka

Podobne podstrony:

A1 3 (Imię, Nazwisko - Nr alb.)Tc jii a t A 1. Przeprowadzono badanie pracowników dwóch firm produkc

A1 4 Imię i nazwisko Indeks Prowadzący ćwicz. MATEMATYKA DYSKRETNA -Elektronika - Termin ekstra -GRU

a1 Imię i Na zniżko: ................................................ grupa:St. Inżynierskie sem.2

Hodowla Lasu pytania 2 termin Nazwisko i imię Egzamin z Hodowli Lnsu 24.11.2008 termin II ProSZf p

doc I SPRAWDZIAN WIADOMOŚCI ~ POWTÓRZENIOWY IMIĘ I NAZWISKO......{ ł—• KL.IYTH jzL GR.1 terminem 1.

zad 1 Nazwisko, Imię. Zaliczenie przedmiotu „Elektroniczna technika pomiarowa" II termin: 16.06

Zdjęcie007 stemy Wbudowane‘09 1 _ ,.*09 ► ouuy ► Mhci.m. J S,.

23. Imię i nazwisko z odpowiedziami.- dla grupy która miała termin

doc I SPRAWDZIAN WIADOMOŚCI ~ POWTÓRZENIOWY IMIĘ I NAZWISKO......{ ł—• KL.IYTH jzL GR.1 terminem 1.

b12 II u Egzamin z Systemów wbudowanych, termin 0 ŁÓDŹ. 19.06.2009. godzina rozpoczęcia egzaminu: 10

b1 2 u Egzamin z Systemów wbudowanych, termin u ŁÓDŹ. 19.06.2009, godzina rozpoczęcia egzaminu 10&qu

phoca thumb l slajd17 (5) Kanały sodowe w (A1 błonie neuronu mają f wbudowany

energoelektronika surtel A1 [A] Grupa IŚD 5 (Nazwisko i imię) 1. Prąd graniczny -1 cavm określa: a

GRUPY LABORATORYJNE GRUPA A Lp Grupa A1 Grupa A2 Nazwisko i imię Nazwisko i

a1 (22) Imię i nazwisko U4JU&, W.__________.UuJ A yf ł D 0 1 1

więcej podobnych podstron