5 (232)

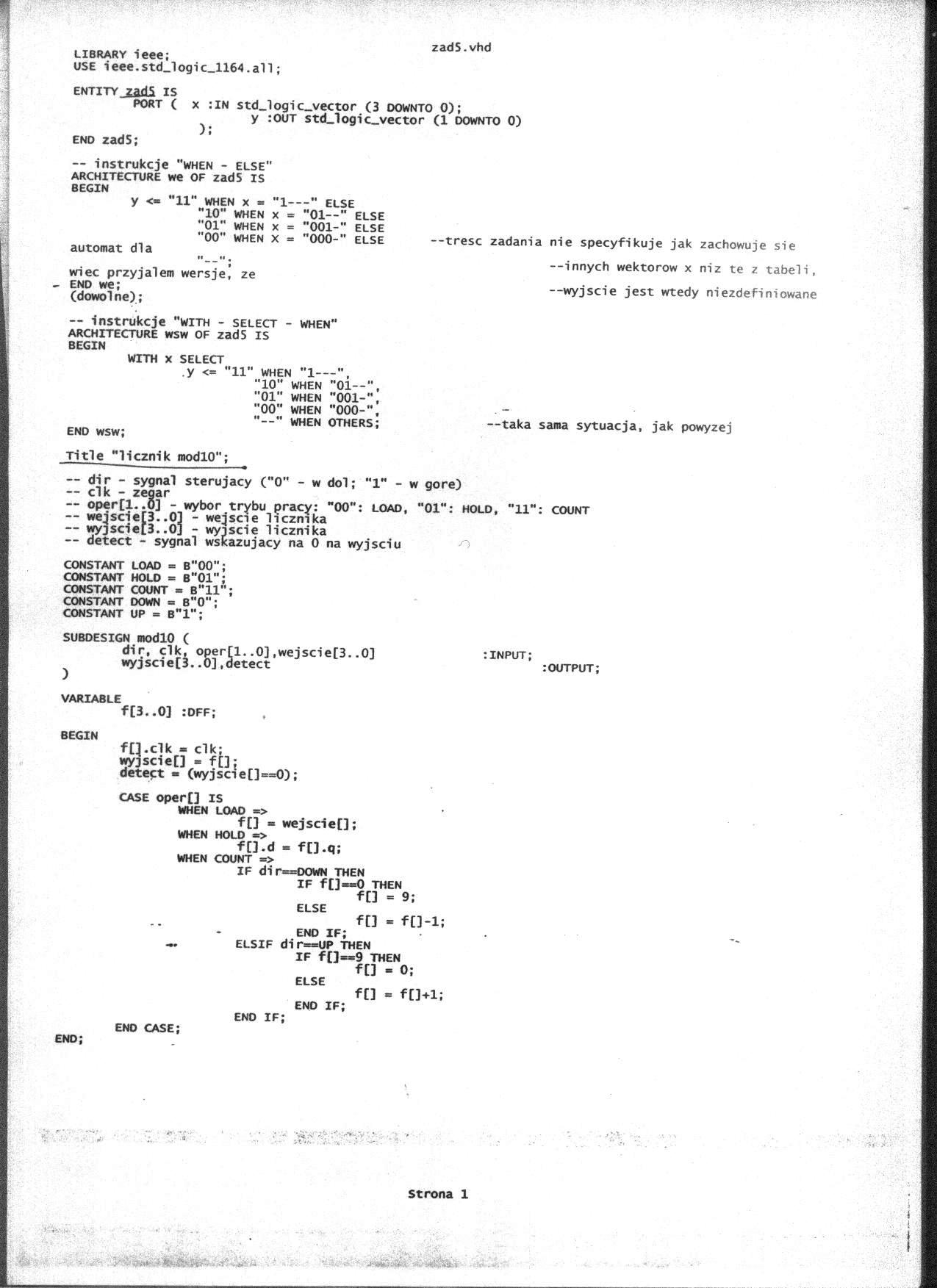

zadS.vhd

library ieee;

USE ieee.std_logic_1164.all;

ENTITY zadS is

PORT ( x :IN std_logic_vector (3 downto 0);

y :OUT std_logic_vector (1 downto 0)

^ J

END zadS;

— instrukcje "when - else"

ARCHITECTURE we OF Zad5 XS BEGIN

|

y <= |

"11" WHEN X = |

"1— |

ELSE | |

|

"10" |

WHEN |

X = |

"01—" ELSE | |

|

"01" |

WHEN |

X = |

"001-" ELSE | |

|

automat dla |

"00" |

WHEN |

X = |

"000-" ELSE |

wiec przyjąłem wersje, ze - END we;

(dowolne);

—tresc zadania nie specyfikuje jak zachowuje sie

—innych wektorów x ni z te z tabeli, —wyjście jest wtedy niezdefiniowane

— instrukcje "with - select - when"

ARCHITECTURE WSW OF Zad5 IS BEGIN

WITH X SELECT

y <= "11" WHEN "1- — ",

"10" WHEN "01—",

"01" WHEN "001-",

"00" WHEN "000-",

"—" WHEN OTHERS; —taka sama sytuacja, jak powyżej

END wsw;

Title "licznik modlO";

— dir - sygnał sterujący ("0" - w doi; "1" - w gore)

— clk - zegar

— oper[1..0] - wybór trybu pracy: “00": load, “01": HOŁD, "11": count

— wejście[3..0] - wejście licznika

— wyjscieL3..0] - wyiscie licznika

— detect - sygnał wskazujący na 0 na wyjściu

CONSTANT LOAD = B"00"; CONSTANT HOŁD = B"01"; CONSTANT COUNT = B"ll"; CONSTANT DOWN = B"0"; CONSTANT UP = B"l";

SUBDESIGN modlO (

dir, clk, operfl..0],wejscie[3..0] :INPUT;

wyjscie[3..0].detect :OUTPUT;

VARIABLE

BEGIN

END;

f[j.clk = clk: wyjsciet] = f[]: detect = (wyjscie[]==0);

case oper[] is

WHEN LOAD =>

f[] = wejscief];

WHEN HOŁD =>

f[].d = f[].q;

WHEN COUNT =>

IF dir==DOWN THEN

IF f[]==0 THEN

f[] = 9;

ELSE

f[] ■= f[]-i;

END IF;

ELSIF di r=UP THEN

IF f[]=9 THEN

f[] = 0;

ELSE

f[) = f[]+l;

END IF;

END IF;

END CASE;

*■ ■ Y:.-;

$ • -'V -

Wyszukiwarka

Podobne podstrony:

5 (232) zadS.vhd library ieee;USE ieee.std_logic_1164.all; ENTITY zadS isPORT ( x :IN std_logic_vect

5 (232) zadS.vhd library ieee;USE ieee.std_logic_1164.all; ENTITY zadS isPORT ( x :IN std_logic_vect

MG 66 Tryby portu library ieee; use ieee.std_logic_1164.all; a entity port_mode is port( a, b : in

IV SEMESTER HDL Lab 1) /HDL codę to realize all the logie gates library IEEE; use IEEE.STD_LOGIC_116

MG 82 H Mariusz RawskiDekoder priorytetu przerwań - inaczej llbrary ieee; use leee.std_loglc_1164.a

MG 88 I__ Mariusz Rawsld Hbrary library ieee; use ieee.stdJ(^<Ln64.a!l; entity latchjnodule

MG&04 t/hn t StftJFt; ~ ■ Realizacja pamięci RAM process llbrary leee; use ieee.stdJoglc_1164.all;

5 7 1 Informacje organizacyjne Zasadnicza zawartość dokumentu Norma ANSI IEEE Std 830-1993

Filtr FIR programowalny realizacja VHDL — It uses W1 signed bit data/coefficients bi LIBRARY Ipm; US

jff 119 GLOSSARY The use of Japanese terms has been kept to a minimum in this book. It is an imposit

FCE: Reading and Use of English (przykłady) Good preparation leads to success in ballet dancing Częś

It s a good idea to use metric units for aerodynamic calculations. The power (watts) in the wind blo

PUNKTY Connecl Ihe Dols 1o Dfscover a Thanksgfvfng Symbol Use Ihe łasi leller you eon necie d 1o fil

KING SKULTax Active Skill After use, the collection speed of all consuls in the Kingdom increased by

42. gift A present B natural ability C luckPAPER III. USE OF ENGLISH (28 points)PART 1 Put the

REMEWS 267 had madę use of iwo different MSS. of the same work in which ihe text of the verses was n

essent?rving?22 ESSENTIAL W O O D C A R VIN G T E C H N IQ U E S Fig 1.36 It is possible to use the

więcej podobnych podstron