138 139

138

Trójstanowe multipleksery 251, 253, 257, 258 aą realizowane według zasady z rys. 5.9, przy czy* bramki wyjściowa aą trójstanowe (ala należy Ich mylić ze a o ha ma tao z rys. 5»10b). Takie rozwiązanie umożliwia bezpośrednie połączenie kilku multiplekserów do wspólnej szyny.

Multiplekser 7*292 umożliwia dodatkowo zapamiętywanie czterech bitów wyjściowych pomiędzy kolejnymi impulsami strobująoyml. Realizują to wbudowane w układ * prserzutnlkl typu D - zatrzask.

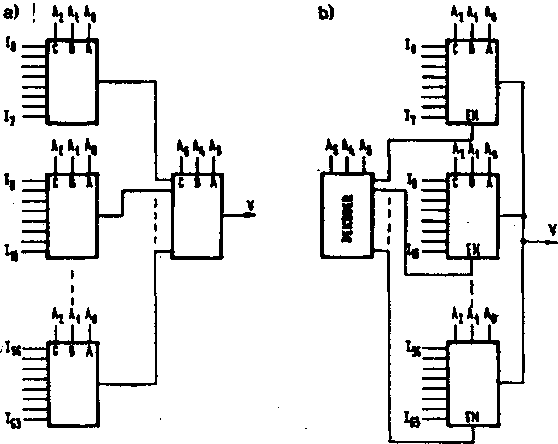

Maksymalna Ilość wejśó gotowych scalonyoh multiplekserów wynosi 16. Multipleksery można Jednak łączyć uzyskując układy o dowolnej ilości wejść. Ha rys. 5.11 podano przykłady konstrukcji multipleksera o 64 wejściach z dziewięciu 8-weJśclowych multiplekserów lub ośmiu 8-wejśoiowyoh multiplekserów trójstanowyoh 1 6-wyjśclowego dekodera (patrz też zad. 5-3 1 5.4).

Rys. 5.11. Multiplekser o 64 wejściach utworzony z multiplekserów 8-weJ-ściowych (a) oraz multiplekserów 8-wejśclowych trój stanowych i dekodera

8-wyJśolowego (b)

Synteza układów kombinacyjnych z multiplekserów

Oprócz zastosowania multiplekserów jako przełączników maggkone być. wykorzystywane do syntezy układów kombinacyjnych.

Runko Ja opisująca wyjście multipleksera o H wejściach adresowych 1 2^ ■■ wejściach informacyjnych ma postać

(5.1)

......... ... o

Z wzoru tego widać, że przy porno07 multipleksera o N wejściach adresowych nośna zrealizować dowolną funkcją logiczną N zmiennych podając Jej argumenty na wejścia adresowe 4, zaś wejścia Informacyjne I łącząc z 0 lub 1 zgodnie z tabelą funkcji. Punkcje o większej od H ilości zmiennych modna zrealizować podając N jej argumentów na wejścia adresowe A, zaś 211 odpowiednich funkcji pozostałych argumentów na wejścia informacyjne I.

Reasumując, multiplekser o N wejściach adresowych realizuje dowolną funkcją H zmiennych lub zmniejsza o H ilość zmiennych funkcji U zmiennych, gdy U > H.

Przykład 5.2

Zrealizować układ kombinacyjny opisany funkcją f(xr x2, x3) - £<3. 5. 6, 7)

stosując bramki oraz multiplekser o 4 wejściach informacyjnych 1 2 wejściach adresowych.

Przedstawiając daną funkcją w postaci ZNPS mamy

f(x1,x2,x3) » x1x2xJ ♦ X-]X2X} * X1X253 + X1X2X3

Przyjmijmy, ta na wejścia adresowe multipleksera podajemy argumenty x2 1 Xj. Aby wyznaczyć funkcje, które należy podać na 4 wejścia informacyjne, wyłączamy z postaci ZNPS zadanej funkcji, przed nawiasy, wszystkie iloczyny zmiennych x2 i . llamy

f(x1tx2,x3) = x25j(0) 4 x2xJ(x1) + x2xJ(x1) + x2xJ(x1+x1) =

= x2x3(0) + x2x3(x1) 4 + x2x3(1)

Porównując otrzymamy wzór ze wzorem (5.1) widzimy, że •Xq = Oj ^1 = ^2 = *3 = ^

Na rys. 3*12 przedstawiono schemat otrzymanego układu.

1.

h

h

In

0

*\

1

Rys. 3.12. Multiplekser realizujący funkcję logiczną z przykładu 3.2

Wyszukiwarka

Podobne podstrony:

138 139 138 Trójstanowa multipleksery 231. 253. 257. 258 są realizowane według zasady z rys. 5>9i

8111 16145Q 251 252 253 254 255 (255) 257 258 259 260

INDEX OF SUBJECTS act 9,11,270 action(s) 8-9, 11, 32-34, 39, 47-49, 158, 163-164, 231, 251, 253-255,

page0139 - 138 — podróży. Lecz jakież było jego zadziwienie, gdy nieznalazł ani jednego człowieka pr

page0453 Miedź, ceny hurtowe 251, 253* —, produkcja 147*, 149* —, przywóz, wywóz 175, 177, 182,

Dwudziestolecie międzywojenne Jerzy Kwiatkowski (138) OL han 1932-1939 / innymi dziełami lejo real

Rozdział 12-W PolsceGomułki (1956- 1970)-(Strony232,236,241,242,252,253, 257, 267, 268, 269, 270, 27

elektronika0002 138 Elektronika. Zbiór zadań ZADANIA 6.J. Dla układów przedstawionych na rysunkach o

skanuj0008 (253) 132 Rysunek techniczny8.2. Schematyczne rysowanie prętów i kształtowników’ Przy rys

2013-11-251. Praca powinna zawierać: - stronę tytułową według ustalonego wzoru, -

page0110 100 CHALDEA około swoich podwórzy (ryc. 257 i 258). Zabudowania te służyły jako mieszkania

CCF20100515�008 257. 258. 259. 260. 261. 262. Błąd standardowy Odchylenie standardowejty y = IM

Bibliografia 253 Gołębiowska J. Metoda badania zespołów mikroflory glebowej, czynnej przy przemianac

image087 p. 97, 257-258, 312). We can assume that the name of the peak resulted from the ritual of w

255 256 257 258 259 260

więcej podobnych podstron