152 153

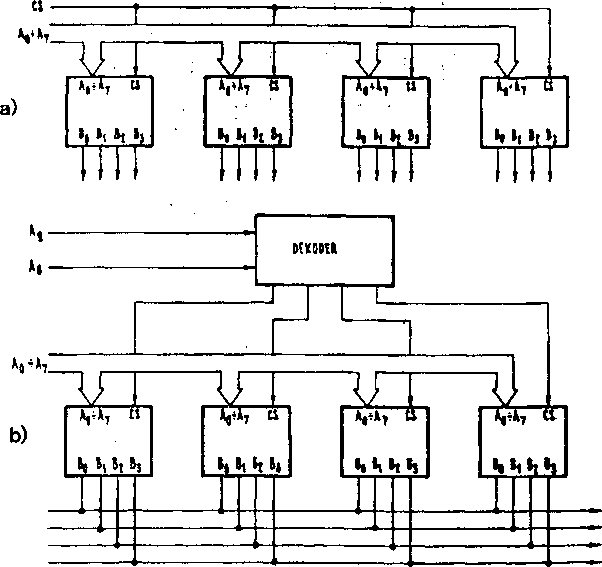

Rys. 5-27. Połączenie czterech ROM-ów 256*4 w zespół o organizacji 256*16 (a) oraz 1024*4 (b)

Według danych z lipca 79 produkuje się scalone pamięci stałe o pojemnościach dochodzących do 8k w technice bipolarnej oraz 32k w technice MOS; Układy o największych pojemnościach przeznaczone są głównie do współpracy z mikroprocesorami. Pamięci mniejsze, o pojemności rzędu 1k, są często programowane przez producentów dla pełnienia ściśle określonych, typowych funkcji, jak np.: konwersja kodów, generacja znaków alfanumerycznych, zapamiętywanie tablic funkcji (sin, arctg, itp.) itd. Pozostałą grupę stanowią pamięci przeznaczone do realizacji dowolnych, złożonych zespołów funkcji logicznych. Uależy przy tym pamiętać, te ROM nie jest - ze względu na swą strukturę - najlepiej przystosowany do tej roli. Ponieważ ROM realizuje wszystkie pełne iloczyny, więc wymagana pojemność Jego matrycy pamięciowej (zależna wykładniczo od liczby wejść i liniowo od liczby wyjśó nie zmienia się w wyniku minimalizacji funkcji, o ile minimalizacja nie prowadzi do całkowitego wyeliminowania niektórych zmiennych (eliminacja każdej zmiennej zmniejsza wymaganą pojemność ROM-u o połowę). W praktyce oznacza to, te pojemność ROM-u o wymaganej liczbie wejść i wyjść nie jest wykorzystywana w pełni, a przez to koszt realizacji danego zespołu funkcji logicznych Jest zawyżony.

5.5.2. Programowane matryce logiczne (PIA)

Jak pamiętamy z rozdziału poświęconego syntezie układów kombinacyjnych, każdą funkcję logiczną można przedstawić w postaci sumy jej impllkantów (w szczególności impllkantów prostych) 1 zrealizować za pomocą trójwarst-wowej sieci funktorćw: w 1-szej warstwie inwertory wytwarzają potrzebne negacje zmiennych wejściowych, w 2-ej funktory NAHD obliczają odpowiednie iloczyny, sumowane w warstwie 3-ej również za pomocą NAND-u.

Pamiętamy także, że matryca z rys. 5*240 jest zespołem NAND-ów.

Pamięć stałą typu PIA (patrz rys. 5«23b) można więc utworzyć przez połączenie dwu matryc z rys. 5.24c, (nazywanych, od pełnionych przez nie funkcji, matrycą AND i matrycą OR) 1 uzupełnienie ich inwertorami wejściowymi - dla obliczenia negacji oraz buforami wyjściowymi - dla umożliwienia łączenia PIA w większe zespoły.

PIA scharakteryzowana jest liczbą wejść, liczbą obliczanych iloczynów tych wejść oraz liczbą wyjść. Dla przykładu, PIA DU 7575 lub DM 7576 (National Semiconductor) ma 14 wejść, 96 iloczynów! 8 wyjść, na których może pojawiać się suma wybranych iloczynów lub jej negacja (niektóre funkcje są prostsze w postaci zanegowanej). Hoże ona realizować większość zespołów 8-miu funkcji 14-tu zmiennych, mianowicie te, które po minimalizacji (całkowitej lub częściowej) dają się wyrazić poprzez nie więcej niż łącznie 96 różnych impllkantów.

Gdyby 8 funkcji 14-tu zmiennych realizować za pomocą ROM-u, to pojem-ność jego matrycy musiałaby wynosić aż 2 x 8 = 16kx8 = 128 k bitów.Natomiast pojemność matrycy OR w PIA wynosi tylko 96 x 8 = 768 bitów. Ponadto zwróćmy uwagę, że matryca AND w PLA Jest też znacznie prostsza od dekodera adresów w ROM-ie. Wprawdzie ROM byłby w stanie realizować wszystkie, a nie tylko większość funkcji 14-tu zmiennych, ale jak widać z porównania, Jego pojemność byłaby około 170 razy większa.

Dla bliższego zapoznania się z metodyką programowania PLA i stosowaną konwencją oznaczeń, rozpatrzmy następujący, prosty przykład.

Przykład 5.5

Przy pomocy PLA o 5 wejściach, 12 iloczynach i 4 wyjściach z możliwością negacji, zrealizować następujące cztery funkcje pięciu zmiennych:

f^A.B.C.D.E) = £ (2,3,4,5,8,9,12,13,15,18,19,24,25,29,31) f2(A,B,C,D,E) = £ (4,5,6,7,12,14,16,17,20,21,22,23,28,30) f5(A,B,C,D,E) = £ (O,1,7,10,11,14,15,16,17,23,26,27,30,31)-f4(A,B,C,D,E) = X (0,1,4,5,6,10,11,14,20,21,22,26,27,30)

Minimalizując każdą funkcję otrzymujemy - . .. .

f ^ = A CE + TsUD +■ BCE + BCE

Wyszukiwarka

Podobne podstrony:

152 153 Rys. 5.27. Połączenie czterech ROM-ów 256** w zespół o organizacji 256x16 (a) oraz 1024

skanuj0019 (153) Rys. 2-15. Połączenie ścian z przekryciem: a), b) monolityczne, c), d) przesuwne, c

P1110732 W czasie pracy ciągnika rozdzielacz 6 ustawiony jest w położeniu pokazanym na rys. 27 i stw

IMG 80 (3) UKŁADY POŁĄCZEŃ STACJI średnio do szyn zbiorczych. Układ podany na rys. 2.27 jest rozwiąz

new 75 1 . 1 . 152•W- 7. Zasady obliczeń wytrzymałościowych śrub Rys. 7.27. Półprzestrzeń obciążona

f. nr**Rys. 3.27 J> 4 Schemat montażowy zasilacza Mi n Radiator 4 i /Schemat połączeń

iui Rys. 5.27. Schemat pomiarowy do badania odbiornika połączonego w trójkąt Pomiaru mocy czynnej dl

24912 instalacje087 2. KONSTRUKCJA I WŁAŚCIWOŚCI SILNIKÓW SKOKOWYCH Rys. 2.27. Schemat połączeń i kr

Strona�28 Rys. 2 5 Węzeł połączenia płyty balkonowej ze stropem ukazuje rysunek 27. Karta kat. T/B -

DSC00837 (3) L

Obsługa i naprawa Audi (27) Rys. 2.3. MIEJSCA POŁĄCZEŃ PRZEWODÓW Rys. 2.4. MIEJSCA

IMG 80 (3) UKŁADY POŁĄCZEŃ STACJI średnio do szyn zbiorczych. Układ podany na rys. 2.27 jest rozwiąz

więcej podobnych podstron