3462402917

Pamięć

podręczna

Most/

sterownik

pamięci

Pamięć

DRAM

Magistrala PCI

|

LA |

lN |

Podstawowe urządzenia wejścia-- wyjścia

Magistrala rozszerzenia

|

;- |

-s |

|

nn/u |

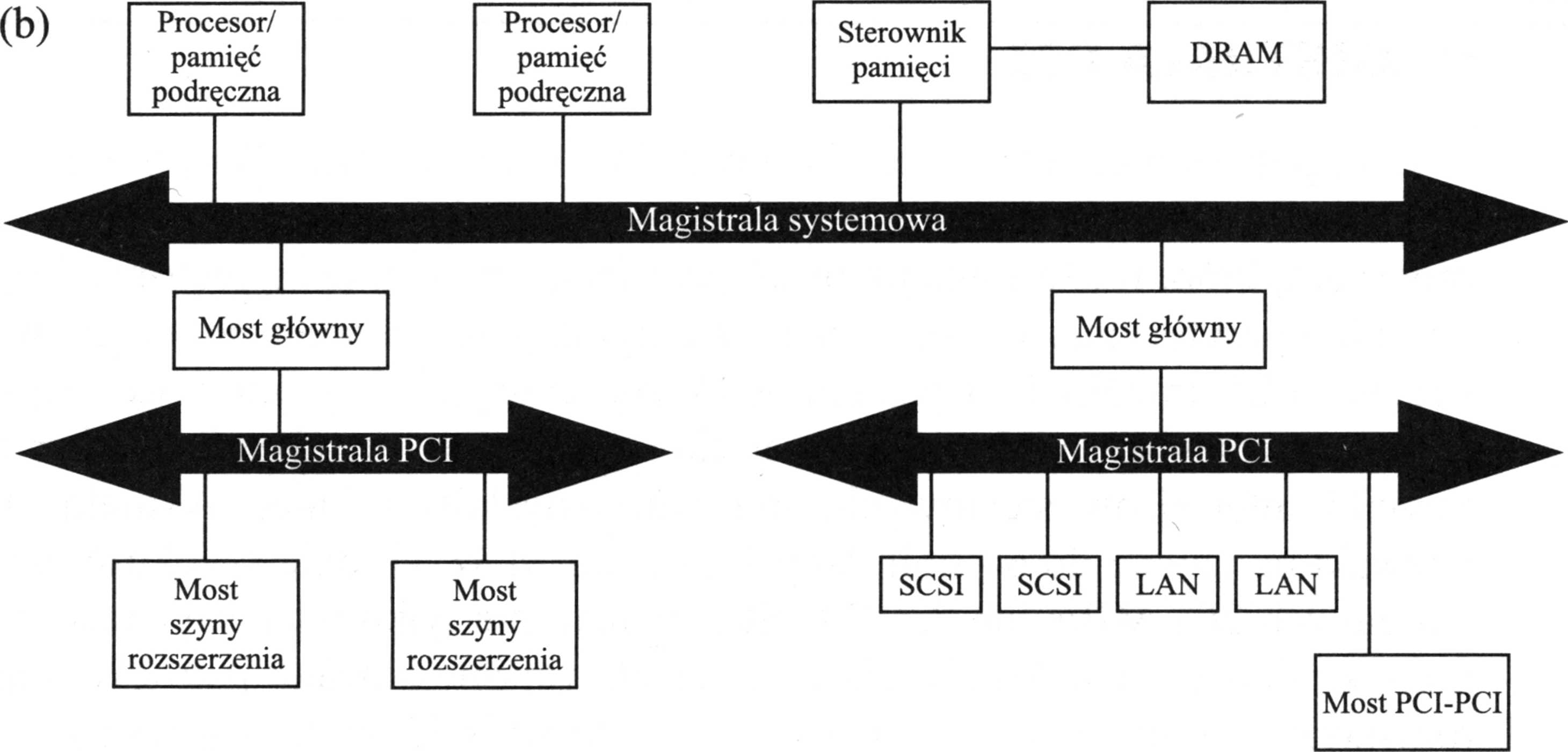

Rysunek 3.21. Przykładowe konfiguracje magistrali PCI: (a) typowy system stołowy; (b) typowy system serwera

Wyszukiwarka

Podobne podstrony:

I. Pamięć RAMBudowa matrycy pamięci DRAM -CE -WE -RAS -CAS Q) T3 Dane <

I. Pamięć RAMOdświeżanie pamięci DRAM Definicja: Czas, jaki upływa od momentu podania prawidłowego

odczytDRAM rys. 3.3. Cykl odczytu pamięci DRAM

rys 3 10a Rysunek 3.10a. Praca pamięci DRAM w trybie stronicowania

rys 3 6a Adres RAS# CAS# WE# OE# CE#Rysunek 3.6a. Wyprowadzenia pamięci DRAM

rys 3 7 O dla aktywnego sygnału RAS Rysunek 3.7. Układ konwersji adresu systemowego na adres dla pam

rys 6 1 CPU Podsystem pamięci Mikroprocesor ^ Magistrala lokalna Pamięć

ROZDZIAŁ 7 U Pamięć operacyjna7.1.1. Pamięć DRAM DRAM (ang. Dynamie RAM — dynamicz

7.2. Typy pamięci DRAM ■ przeciwieństwie do DRAM pamięć SRAM nie wymaga odświeżania (jest statycz-i.

1.2. Typy pamięci DRAM 1.2. Typy pamięci DRAM SDR : sfer ! wcyklu ^Terowym Częstotliwość zegar

DSCN5322 (2) Synchroniczna pamięć DRAM (SDRAM) * dane / rozkazy sterujące przesyła

DSCN5323 (2) Synchroniczna pamięć DRAM (SDRAM) • dane / rozkazy sterujące przesyła

DSCN5325 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawcie cykle pracy transfer danych

DSCN5327 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawowe cykle pracy:

więcej podobnych podstron