Układ wykonawczy, instrukcje

i adresowanie

Dariusz Chaberski

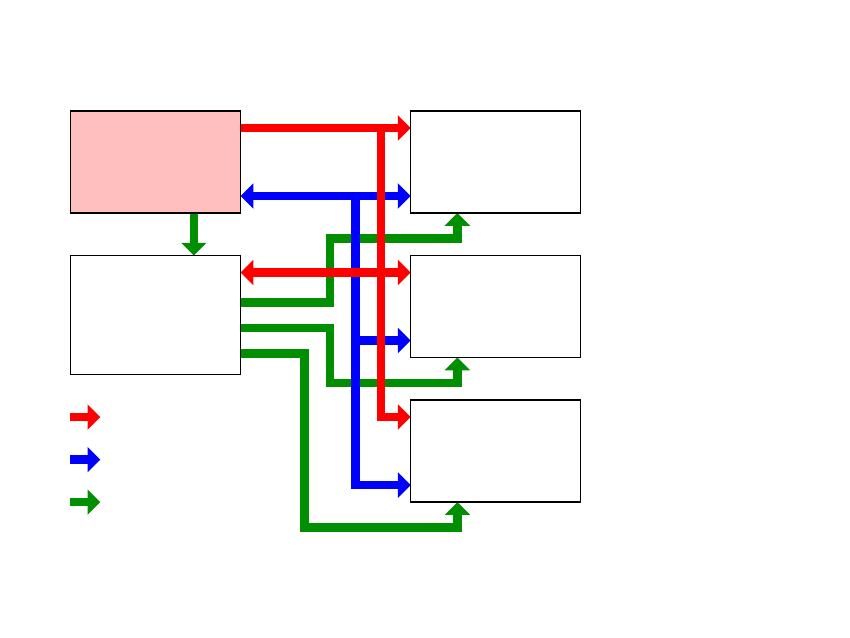

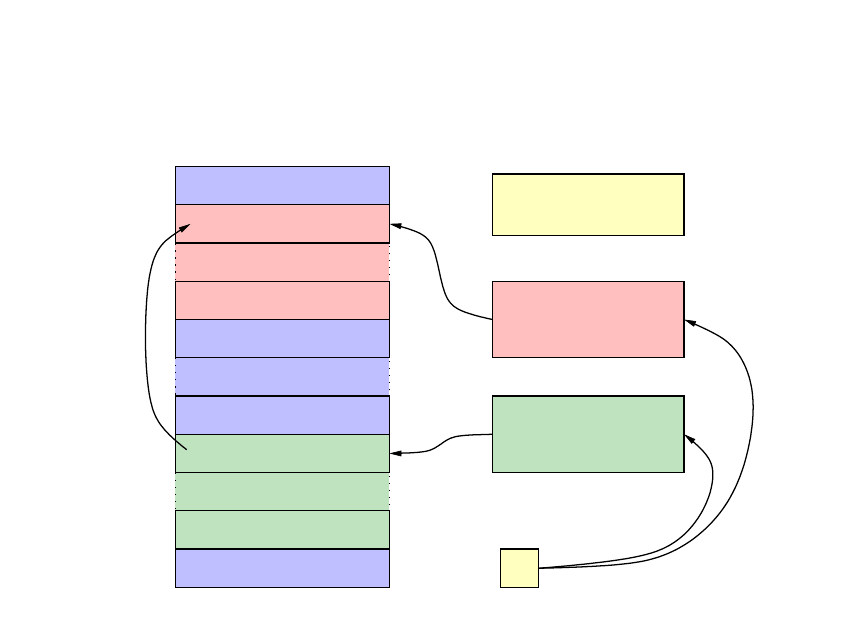

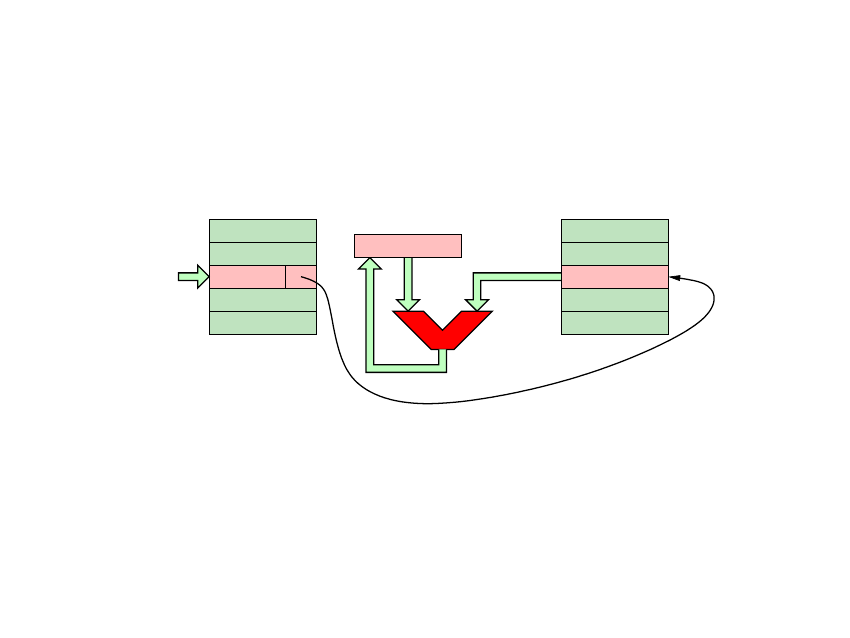

System mikroprocesorowy

mikroprocesor

D

A

A

C

C

C

C

C

2

C

3

C

1

dekoder

adresów

pamięć

programu

pamięć

danych

układy wejścia

wyjścia

A

D

D

D

A

A

magistrala adresowa

magistrala danych

sygnały sterujące

BIOS

pamięć operacyjna

mysz

karta graficzna

klawiatura

stacja dyskietek

2

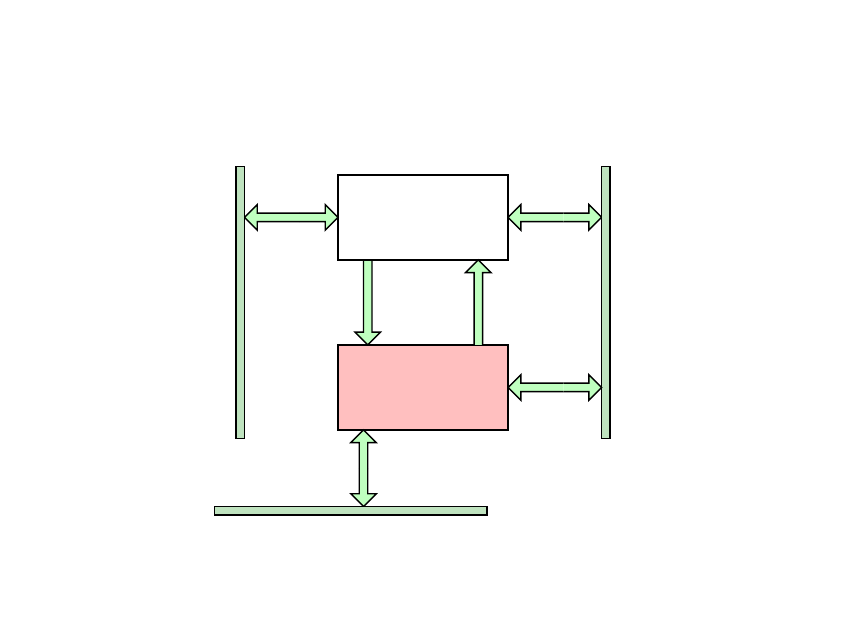

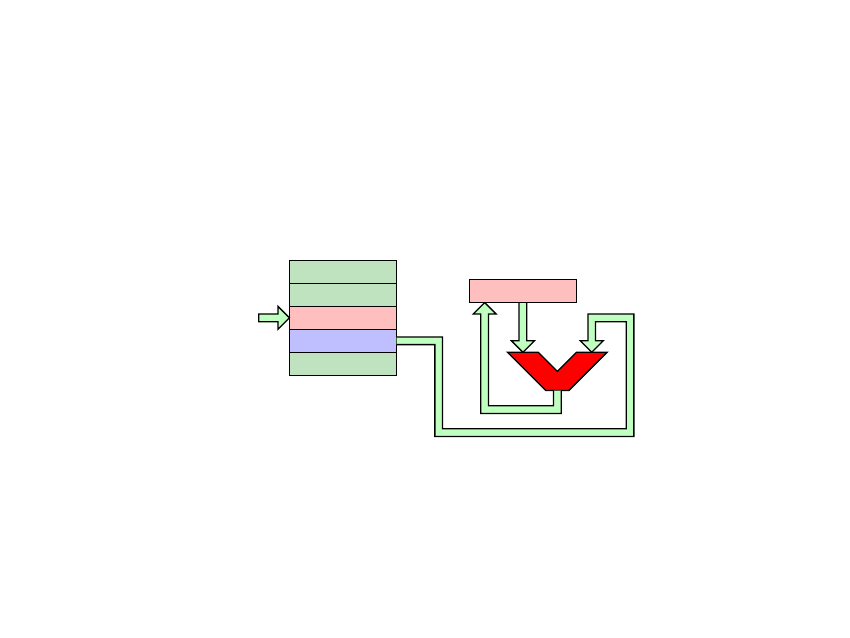

Jednostka centralna

układ

wykonawczy

układ

sterowania

sygnały

sterujące

sygnały

stanu

sz

y

n

a

sy

g

n

a

ło

w

st

er

o

w

a

n

ia

wewnętrzna

szyna adresowa

w

ew

n

ęt

rz

n

a

sz

y

n

a

d

a

n

y

ch

3

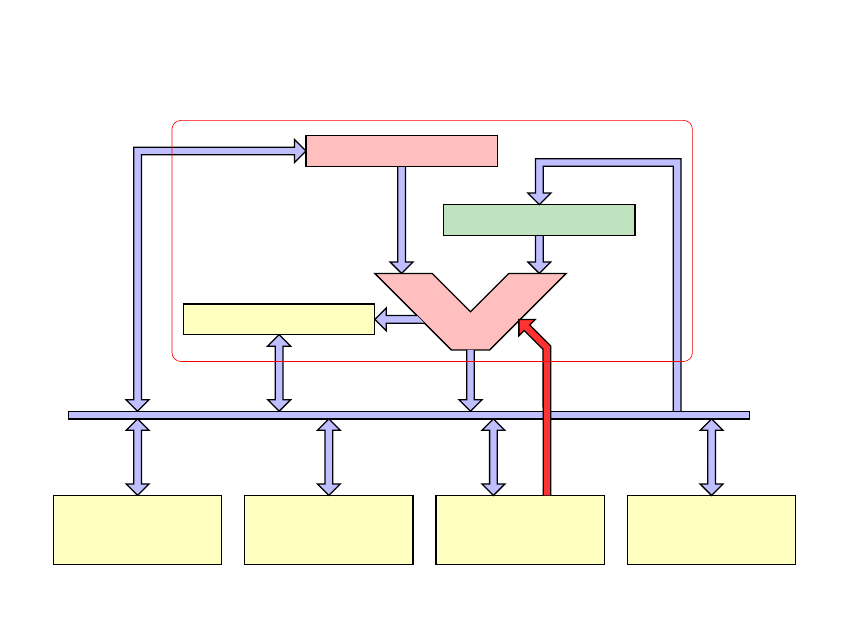

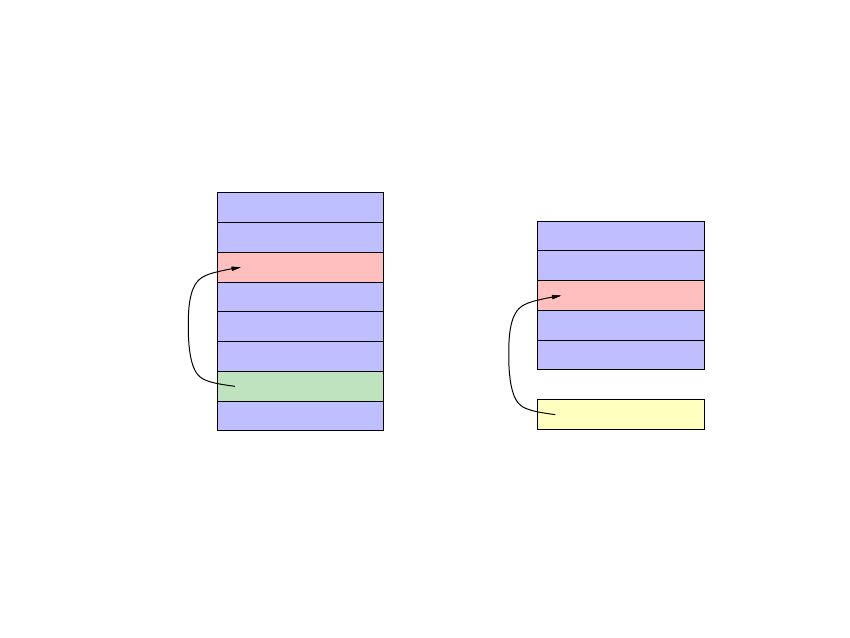

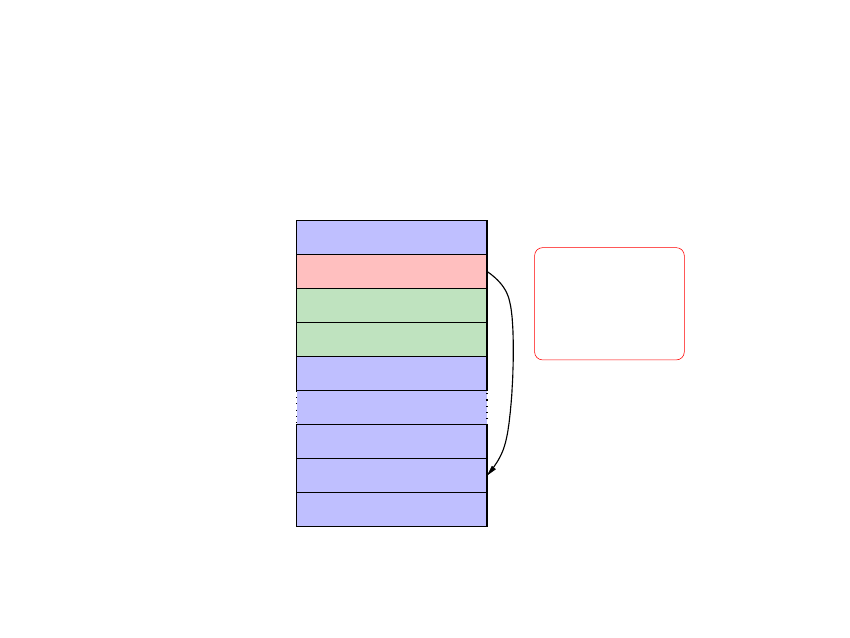

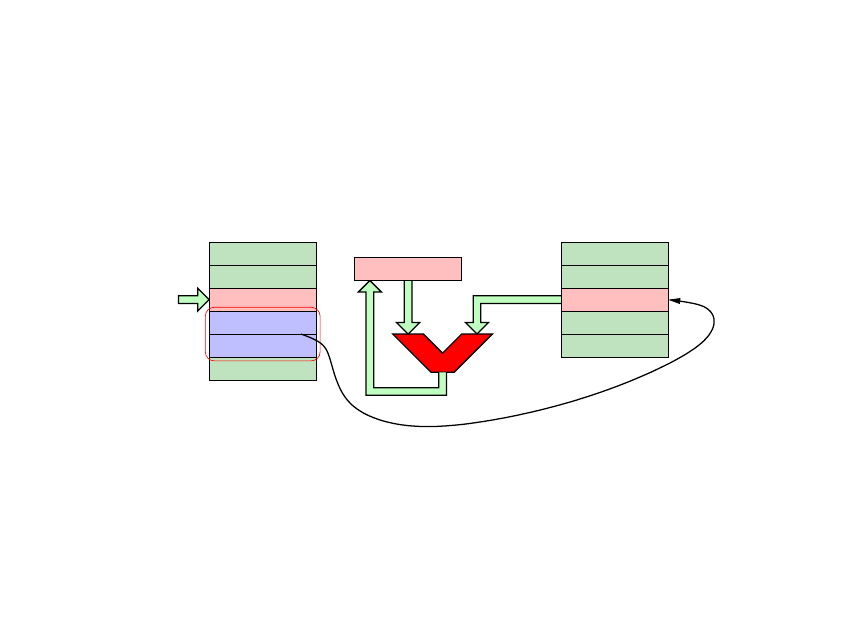

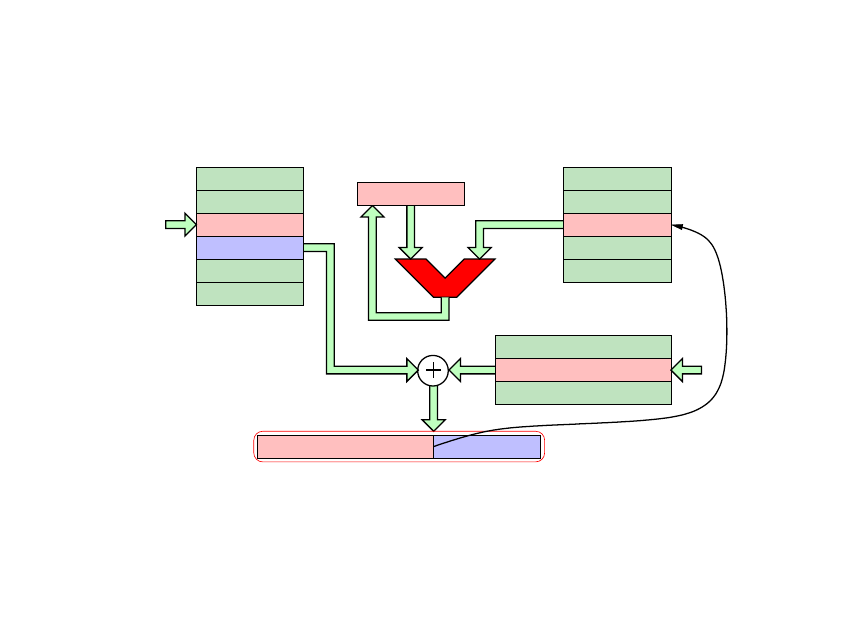

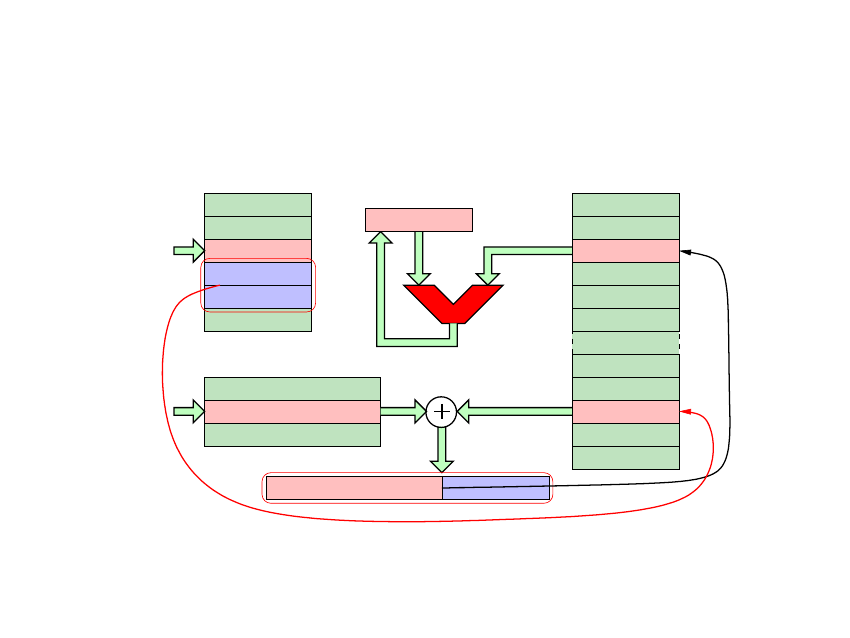

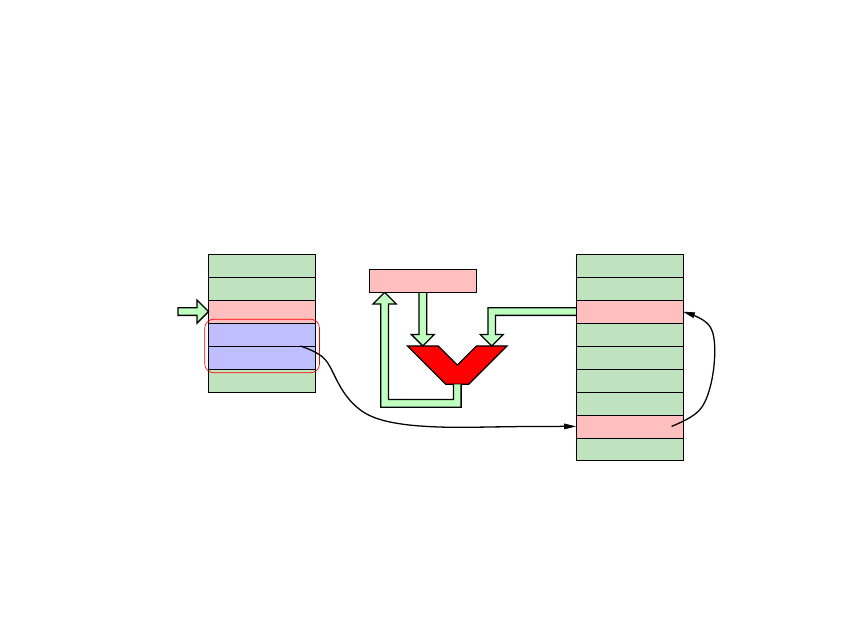

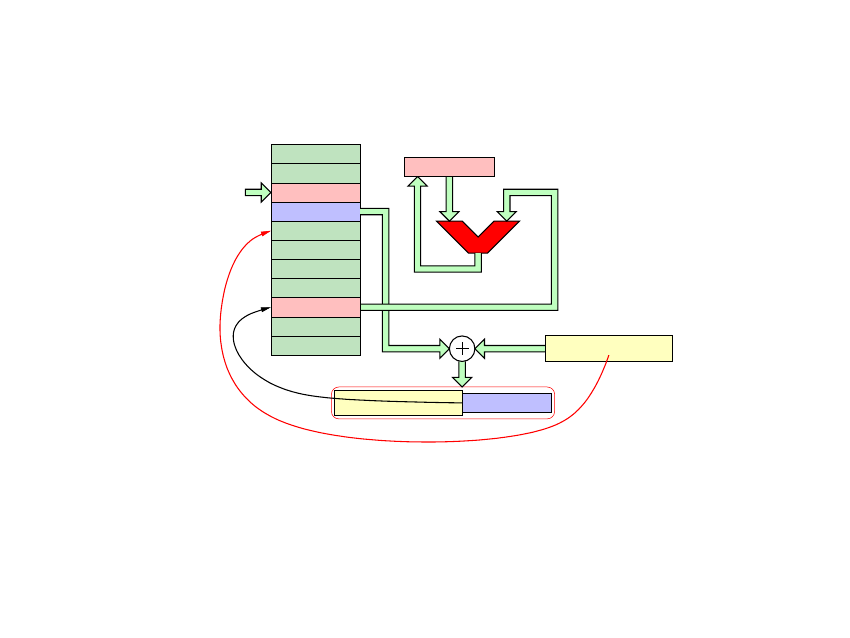

Układ wykonawczy

rejestr tymczasowy

akumulator

rejestr znaczników

rejestry ogólnego

przeznaczenia

licznik programu

wskaźnik stosu

rejestr rozkazów

4

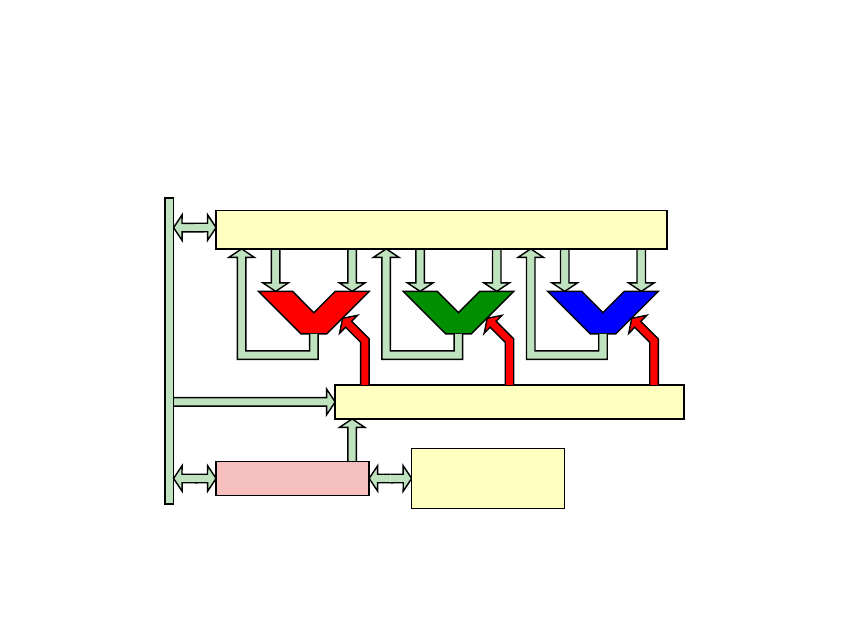

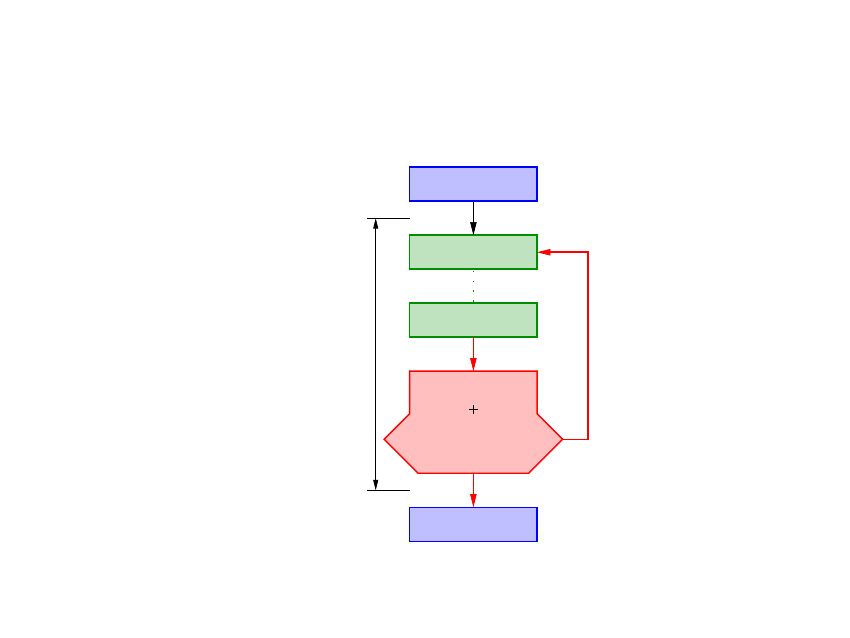

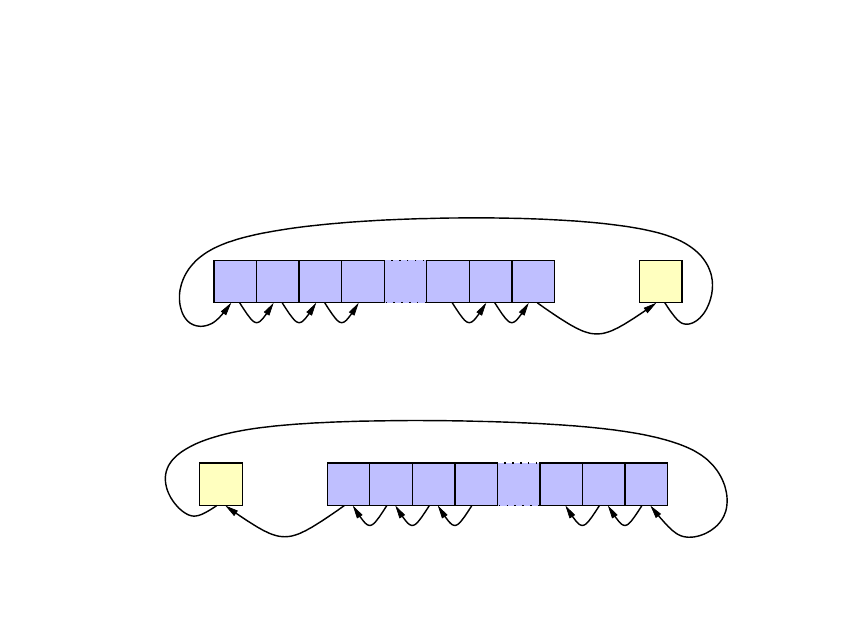

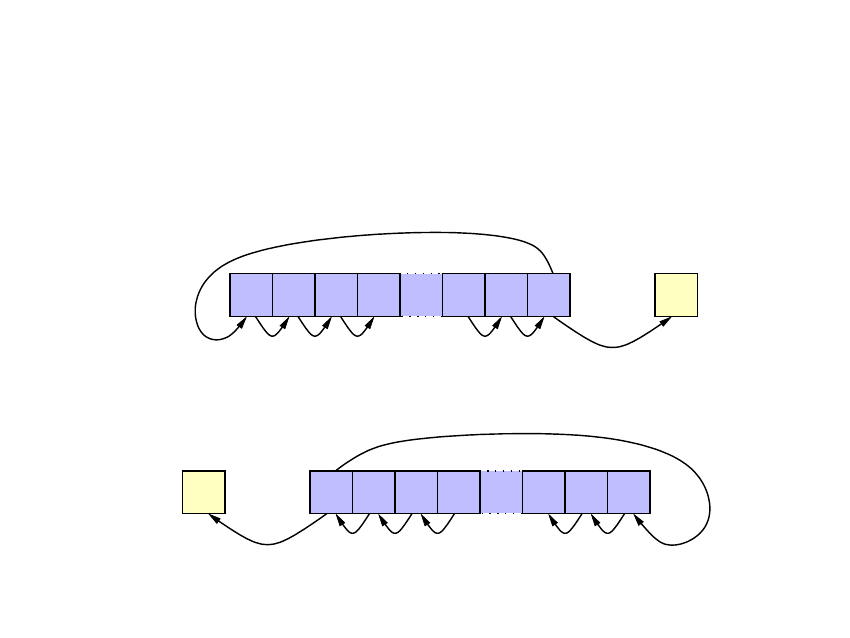

§ architektura superskalarna

rejestry ogólnego przeznaczenia

FIFO

sekwenser

licznik

programu

5

Instrukcje

§ format 4

r

k−1

o

′

m−1

R

:

O

′

:

drugi operand

rodzaj operacji

pierwszy operand

o

0

O

:

W

:

wynik

w

0

o

′

0

w

n−1

r

0

o

l−1

R(W, F) = R(O, O

0

, F)

F - rejestr znaczników

+ przykłady

F ◦ [W] = [O] † O

0

F ◦ W = O † [#O

0

]

† - dowolny operator

6

§ format 3

r

k−1

R

:

rodzaj operacji

pierwszy operand

o

0

O

:

o

′

m−1

O

′

:

drugi operand

o

′

0

r

0

o

l−1

R(A/O, F) = R(O, O

0

, F)

A - rejestr specjalny - akumulator

+ przykłady

F ◦ O = O

0

F ◦ [#O] = O † #O

0

F ◦ A = O † [#O

0

]

7

§ format 2

r

k

−

1

R

:

rodzaj operacji

operand

o

0

r

0

O

: o

l

−

1

R(A/O, F) = R(A, O, F)

+ przykłady

F ◦ O = †O

F ◦ A = O

F ◦ A = [A † O]

8

§ format 1

r

k

−

1

R

:

rodzaj operacji

r

0

R(A, F) = R(A, F)

+ przykłady

F ◦ A = †A

F ◦ [A] = 0

F ◦ A = [A]

9

§ podział

+ pełniona funkcja

3 przesłań

3 arytmetyczne

3 logiczne

3 sterujące

3 warunkowe

3 specjalne

+ typ danych

3 stałoprzecinkowe

3 zmiennoprzecinkowe

3 bitowe

3 blokowe

3 DSP - Digital Signal Processing

3 SIMD - Single Instruction Multiple Data

+ poziom uprzywilejowania

10

§ przesłania n bitowe międzyrejestrowe

przeznaczenie

źródło

rejestry

ogólnego

przeznaczenia

przeznaczenie

rejestry

ogólnego

przeznaczenia

akumulator

D = S

D = A

D, S -rejestr przeznaczenia, źródła

11

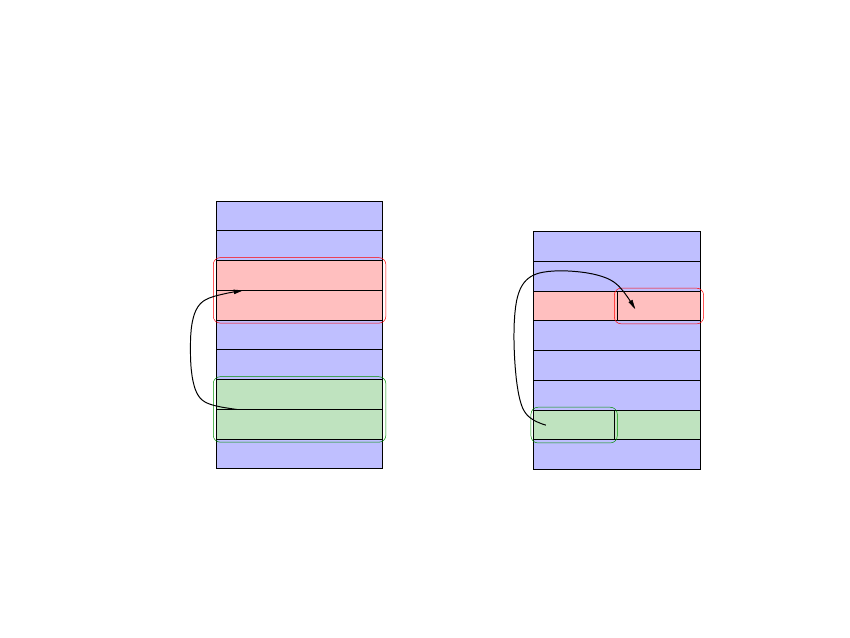

§ przesłania 2n bitowe międzyrejestrowe

rejestry

ogólnego

przeznaczenia

S

1

S

2

D

1

D

2

rejestry

ogólnego

przeznaczenia

D

H

D

L

S

L

S

H

D

2

◦D

1

= S

2

◦S

1

D

L

= S

H

12

§ przesłania pamięć-rejestr, rejestr-pamięć (kolejność bajtowa)

RS

RD

H

RD

L

AD

:

AS

:

AS

+1:

pamięć

rejestry ogólnego przeznaczenia

[AD] = RS

RD

H

◦ RD

L

= [AS] ◦ [AS + 1]

13

Kolejność bajtowa

§ Big Endian - najbardziej znaczący bajt umieszczany jest w pamięci jako pierwszy

pod najniższym adresem (na przykład procesory POWER)

+ przykład

0x6FC9D (Big Endian, 32 bitowe rejestry)

adres(przesunięcie)

0

1

2

3

zawartość

0x00

0x06

0xFC

0x9d

§ Little Endian - najmniej znaczący bajt umieszczany jest w pamięci jako pierwszy

(na przykład procesory Intel x86)

14

Instrukcje

§ przesłania blokowe pamięć-pamięć

DI

:

pamięć

SI

:

licznik

przesłań

rejestr

indeksowy

przeznaczenia

rejestr

indeksowy

źródła

DIR

DI

:

SI

:

CNT

:

znacznik

kierunku

15

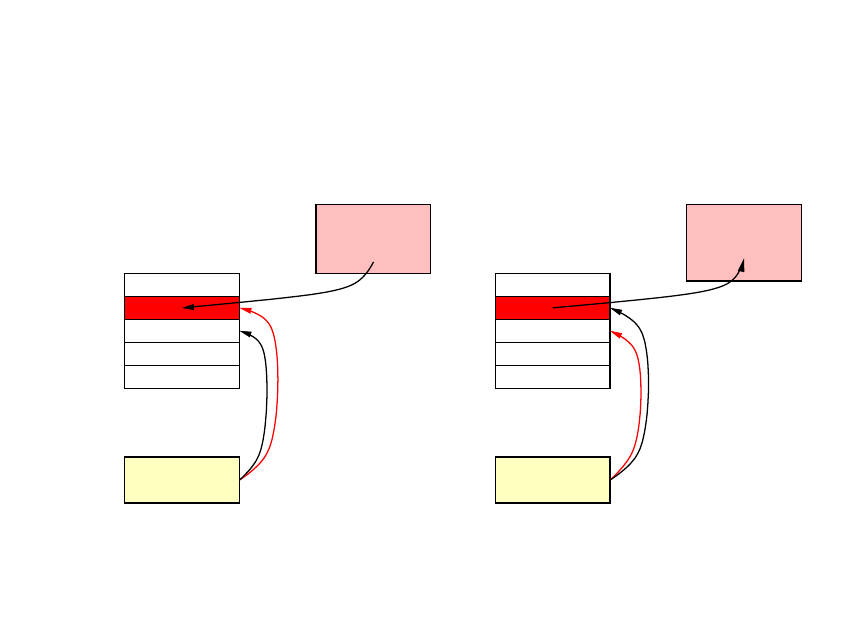

§ przesłania na stos i ze stosu (ochrona rejestru)

n+3

n+2

wskaźnik

stosu

n+1

n

n+4

LIFO

chroniony

rejestr

n+3

n+2

wskaźnik

stosu

n+1

n

n+4

LIFO

chroniony

rejestr

16

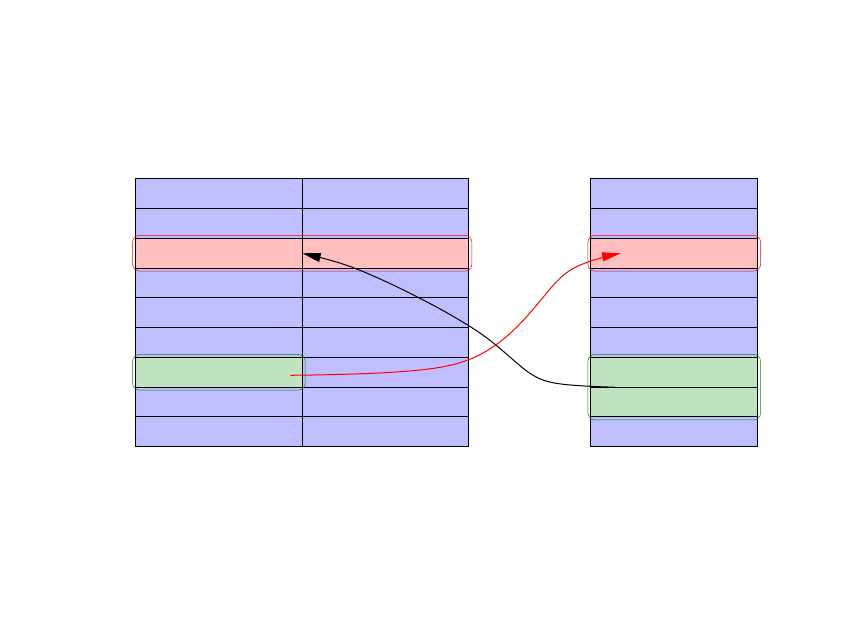

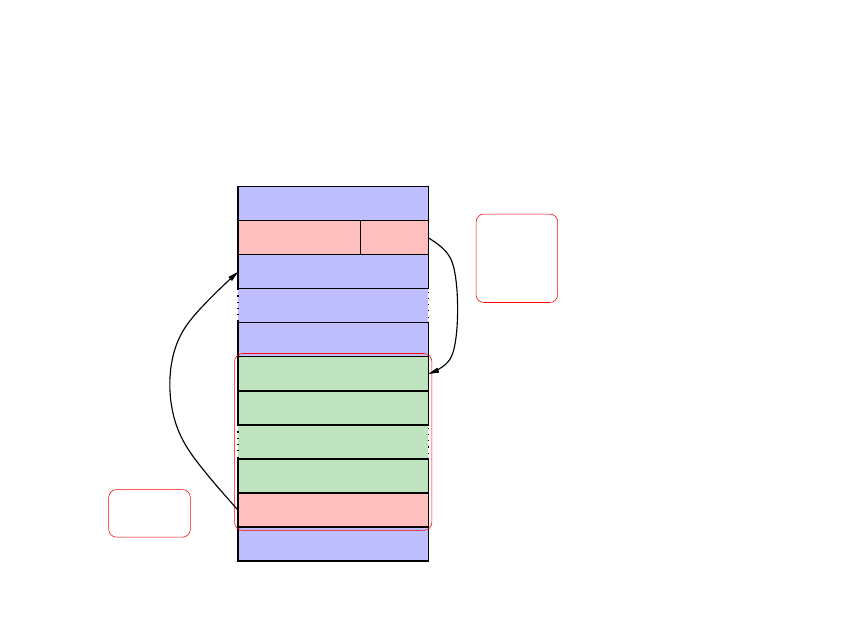

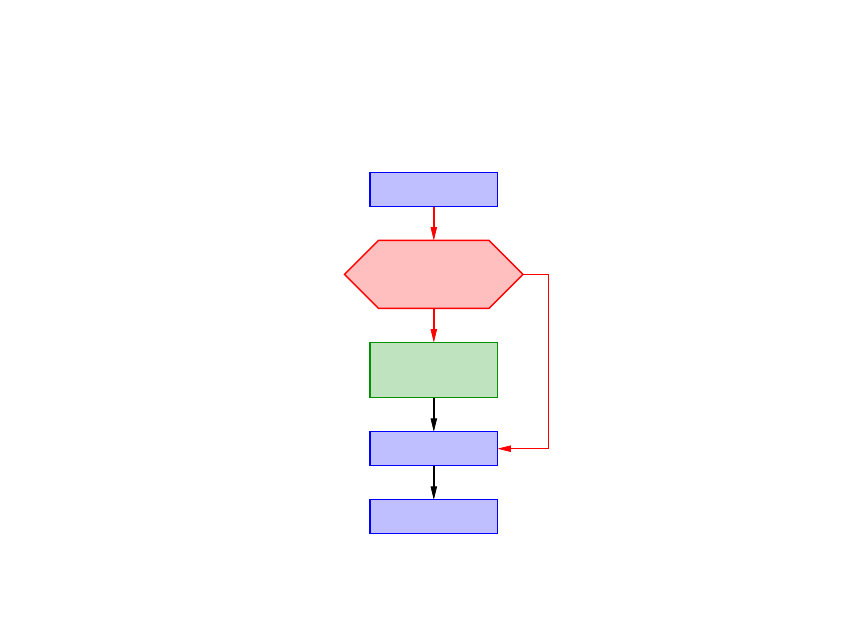

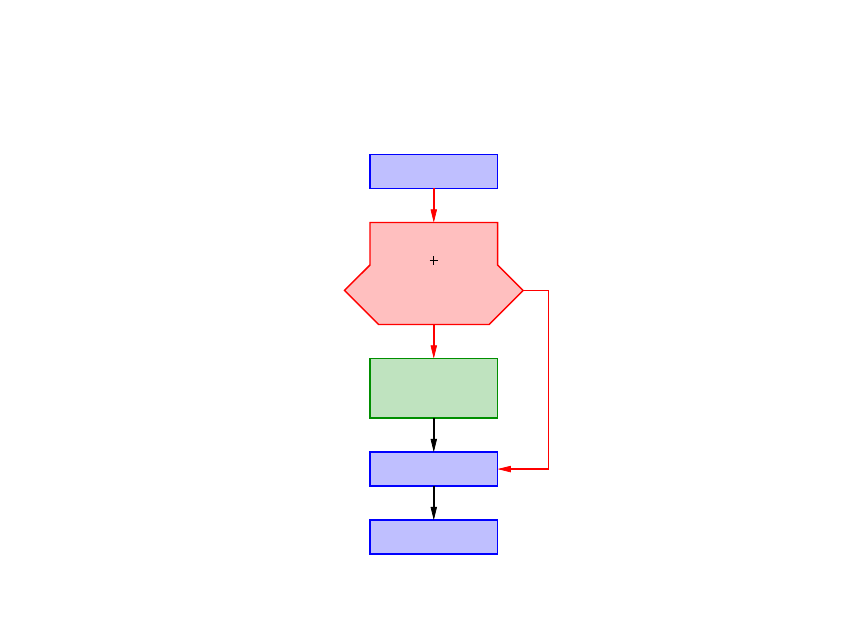

§ sterujące - wywołanie podprogramu

PC

- licznik programu

SP

- wskaźnik stosu

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

powrót

pamięć

programu

SUB

:

PC

+1:

SUB

wywołanie

PC

:

SP

=SP-1

PC

=[SP]

PC

=PC+1

SP

=SP+1

[SP]=PC

PC

=SUB

17

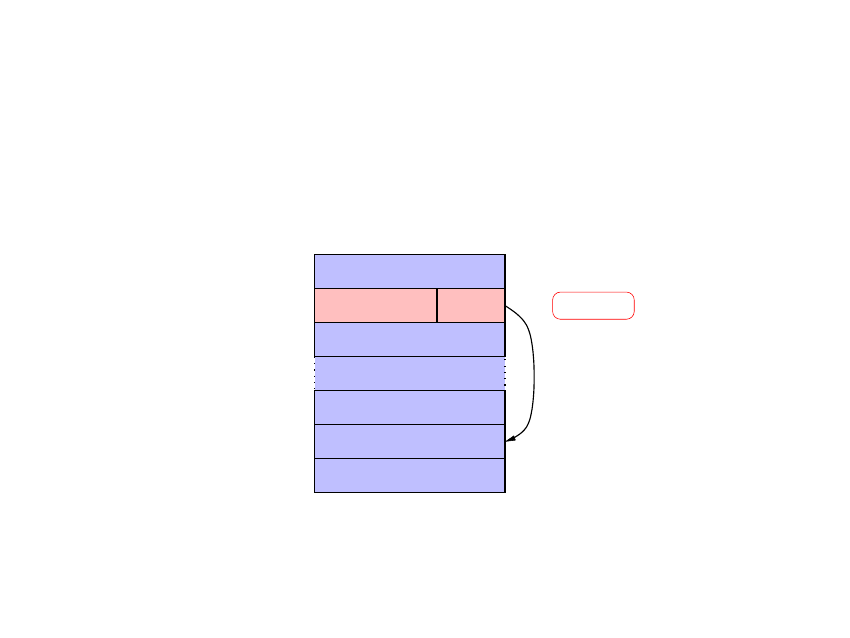

§ sterujące - skok bezwarunkowy

PC

=ADDR

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

pamięć

programu

ADDR

:

PC

+1:

ADDR

skok

PC

:

18

§ sterujące - skok bezwarunkowy względny

ADDR

L

instrukcja

instrukcja

instrukcja

instrukcja

pamięć

programu

PC

+1:

PC

:

PC

= PC + 1

skok

instrukcja

ADDR

H

L

= [PC]

H

= [PC]

PC

= PC + 1

PC

+ H ◦ L:

PC

= PC + H ◦ L

19

§ warunkowe typu SKIP

instrukcja

instrukcja

warunkowa

instrukcja

pomijana

instrukcja

instrukcja

20

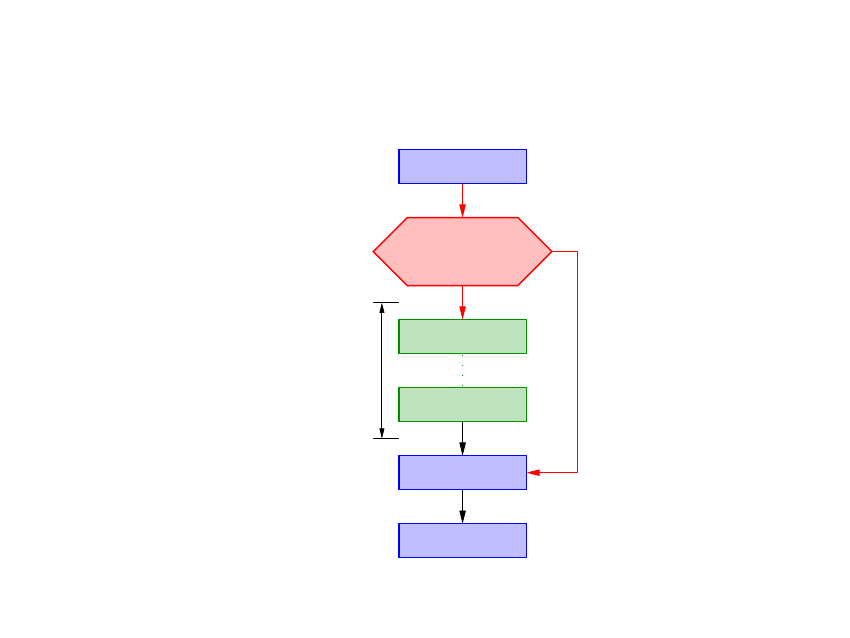

§ warunkowe typu BRANCH (zastosowanie SKIP)

instrukcja

instrukcja

warunkowa

instrukcja

instrukcja

instrukcja

instrukcja

in

st

ru

k

cj

e

p

o

m

ij

a

n

e

21

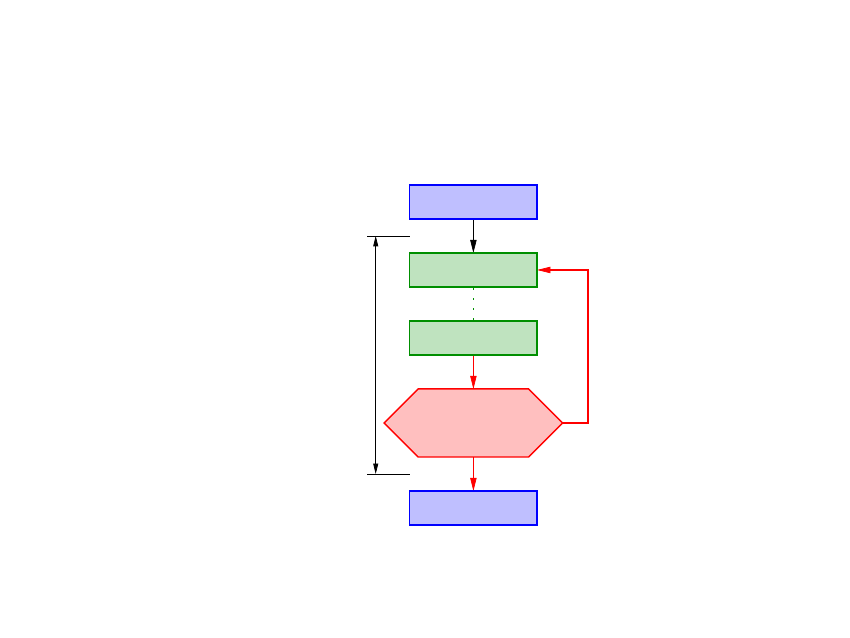

§ warunkowe typu BRANCH (zastosowanie do tworzenia opóźnień)

instrukcja

warunkowa

instrukcja

instrukcja

instrukcja

instrukcja

za

p

ęt

la

n

e

in

st

ru

k

cj

e

22

§ warunkowe typu instrukcja+BRANCH

instrukcja

instrukcja

instrukcja

instrukcja

warunkowa

instrukcja

za

p

ęt

la

n

e

in

st

ru

k

cj

e

instrukcja

23

§ warunkowe typu instrukcja+SKIP

instrukcja

instrukcja

instrukcja

instrukcja

warunkowa

instrukcja

instrukcja

pomijana

24

§ specjalne

+ zatrzymanie procesora

+ oczekiwanie przerwania

+ operacja pusta

+ obniżenie poboru energii

25

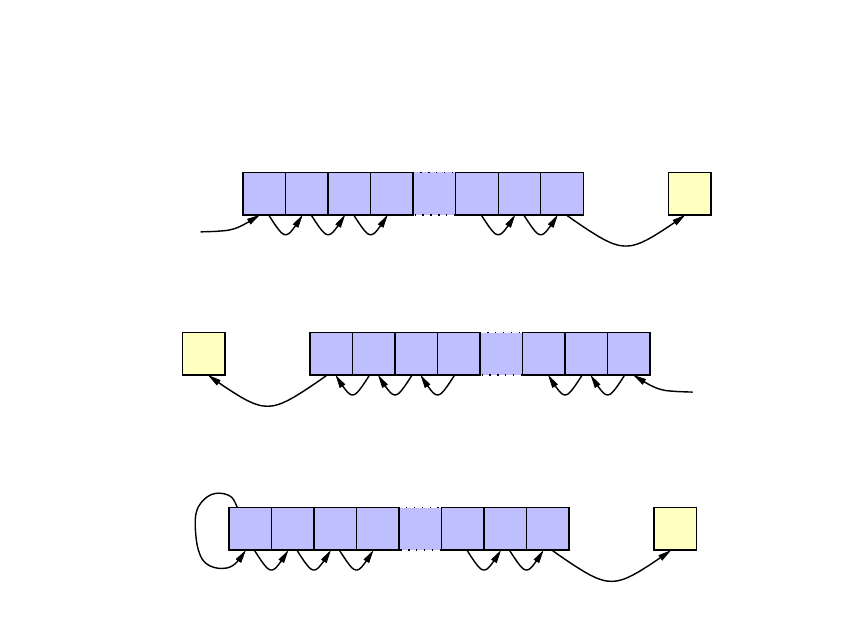

§ bitowe

+ przesunięcie logiczne w prawo

b

N

−

1

b

0

C

0

+ przesunięcie logiczne / arytmetyczne w lewo

C

b

N

−

1

b

0

0

+ przesunięcie arytmetyczne w prawo

b

N

−

1

b

0

C

26

§ bitowe

+ przesunięcie cykliczne w prawo przez znacznik przeniesienia

b

N

−

1

b

0

C

+ przesunięcie cykliczne w lewo przez znacznik przeniesienia

C

b

N

−

1

b

0

27

Instrukcje

§ bitowe

+ przesunięcie cykliczne w prawo

b

N

−

1

b

0

C

+ przesunięcie cykliczne w lewo

C

b

N

−

1

b

0

28

§ bitowe

+ ustawianie bitu k w słowie B

b

N

−

1

b

0

1

k

B

:

N-1

0

B = B ∨ (1 << k)

+ zerowanie bitu k w słowie B

b

N

−

1

b

0

0

k

B

:

N-1

0

B = B ∧ (1 << k)

29

§ bitowe

+ negowanie bitu k w słowie B

b

N

−

1

b

0

k

B

:

N-1

0

b

k

B = B ⊕ (1 << k)

30

§ poziom uprzywilejowania

0

1

2

3

0 - jądro systemu operacyjnego (zarządzanie pamięcią, przełączanie zadań)

1 - system operacyjny (dostęp do danych, obsługa wejść / wyjść)

2 - rozszerzenie systemu operacyjnego przez użytkownika

3 - programy użytkowe

31

§ podział mikroprocesorów według typu listy instrukcji

+ RISC (ang. Reduced Instruction Set Computer)

3 zbiór instrukcji jest ortogonalny

3 mała liczba instrukcji

+ CISC (ang. Complex Instruction Set Computer)

3 rozbudowana liczba instrukcji

3 wysoka specjalizacja instrukcji

32

Tryby adresowania

§ implikowane

rejestry

ogólnego

przeznaczenia

pamięć

programu

akumulator

A = A † R

† - dowolny operator

A - rejestr specjalny - akumulator

R - wybrany rejestr ogólnego przeznaczenia

33

§ natychmiastowe

pamięć

programu

akumulator

A = A † #D

34

§ bezpośrednie

rejestry

ogólnego

przeznaczenia

pamięć

programu

akumulator

A = A † [D1 ◦ D2]

D1, D2 - dwa kolejne słowa po kodzie rozkazu

35

§ (pre, post) indeksowe

akumulator

rejestry

indeksowe

pamięć

programu

rejestry ogólnego

przeznaczenia lub

pamięć

A = A † [I + D]

D - słowo po kodzie rozkazu

I - zawartość wybranego rejestru indeksowego

36

§ indeksowe z przesunięciem bezpośrednim

akumulator

pamięć

programu

rejestry ogólnego

przeznaczenia lub

pamięć

rejestry indeksowe

A = A † [I + [D1 ◦ D2]]

37

§ pośrednie

akumulator

pamięć

programu

rejestry ogólnego

przeznaczenia lub

pamięć

A = A † [[D1 ◦ D2]]

38

§ względne

akumulator

pamięć

programu

licznik programu

adres następnej

instrukcji

A = A † [PC + D]

PC - licznik programu

39

Wyszukiwarka

Podobne podstrony:

02-elektrotechnika samochodowa, Instrukcje BHP, XV - MECHANIKA I LAKIERN. SAMOCH

02 Doświadczenie Reynoldsa, 02 Doświadczenie Reynoldsa instrukcja

02. Doświadczenie Reynoldsa 02. Doświadczenie Reynoldsa, instrukcja

układ wykonawczy budżetu (10 str), Ekonomia

02 K układ podnoszenia

02 Odwołanie?rowizny wykonanej

02 K układ podnoszenia, WÓZKI WIDŁOWE WIADOMOŚCI TESTY 2009 NA EGZAMIN, DOKUMENTY UDT

02. Test motywacji instrukcja Schneider(1), Terapia

24 02 2014 r wykonanie i nienależyte wykonanie świadczenia

02 strategia jako instrument zs

77 Nw 02 Uklad SI

02. Układ krążenia, MEDYCYNA NATURALNA - O. ANDRZEJ CZESŁAW KLIMUSZKO, Wróćmy do ziół leczniczych -

02 cechy fizyczne instrukcja 2i Nieznany (2)

02-klucz elektr, Instrukcje BHP, XIV -MECHANIKA

więcej podobnych podstron