35

4. Komputerowe projektowanie uk³adów cyfrowych.

4.1. Uk³ady cyfrowe.

Projektowanie systemów cyfrowych mo¿e byæ oparte na standardowych,

uniwersalnych elementach wielkiej skali integracji, uzupe³nionych elementami ma³ej i

œredniej skali integracji. System cyfrowy zbudowany z nich sk³ada siê z wielu odrêbnych

uk³adów, przez co czêsto realizowany projekt stawa³ siê bardzo drogi.

W tej sytuacji opracowano now¹ filozofiê projektowania systemów cyfrowych. Idea nowej

technologii polega na mo¿liwoœci realizacji ca³ego, nawet bardzo z³o¿onego systemu

cyfrowego w jednym, wyspecjalizowanym uk³adzie cyfrowym ASIC (Application Specific

Integrated Circuits). Najnowsze badania, konferencje, liczne wyk³ady wykazuj¹ , ¿e najbli¿sze

lata bêd¹ er¹ uk³adów programowalnych.

W niniejszym podrozdziale postaram siê przedstawiæ podzia³ tych uk³adów oraz krótko je

scharakteryzowaæ.

4.1.1. Klasyfikacja uk³adów ASIC.

Uk³ady specjalizowane ASIC – uk³ady produkowane na zamówienie klienta dziel¹ siê na:

Ø Uk³ady na zamówienie z pe³nym cyklem projektowania od podstaw (ang. full-

custom). Zamawiaj¹ cy nie uczestniczy w procesie wytwarzania, jego rola

ogranicza siê do przedstawienia za³o¿eñ projektowych. Zajmuj¹ siê tym

wyspecjalizowane przedsiêbiorstwa przy wykorzystaniu zaawansowanych i

drogich narzêdzi. Uk³ady te s¹ zwykle najszybsze i najwiêksze pod wzglêdem

z³o¿onoœci realizowanych funkcji. Ze wzglêdów ekonomicznych produkowane

s¹ w bardzo du¿ych seriach.

Ø Uk³ady z ograniczonym cyklem projektowania (ang. semi-custom).

Zamawiaj¹ cy osobiœcie bierze udzia³ w projektowaniu uk³adu, wykorzystuj¹ c

do tego prostsze i ³atwo dostêpne narzêdzia. Z tego powodu w uk³adach tych

zastosowano technologiê matryc makrokomórek lub bramek. Projektowanie

polega na sk³adaniu uk³adu z gotowych elementów takich jak: bramki,

przerzutniki, multipleksery, liczniki. Zaprojektowany uk³ad przesy³any jest do

producenta, który korzystaj¹ c z biblioteki masek wyró¿nionych elementów

wytwarza fizyczny uk³ad. W przypadku wytwarzania systemu cyfrowego z

36

wykorzystaniem tych uk³adów czas projektowania jest znacznie krótszy.

Uk³ady te ze wzglêdu na cechy struktury wewnêtrznej dzieli siê na: uk³ady

wykorzystuj¹ ce komórki standardowe (Standard Cells) oraz uk³ady na p³ytkach

wstêpnie przygotowanych, jak np. matryce bramek (Gate Arrays).

Ø Uk³ady programowane przez u¿ytkownika.

Projektant sam programuje uk³ad wykorzystuj¹ c dostarczone przez producenta

„prefabrykaty”. Uk³ady tego typu s¹ ³atwe w u¿ytkowaniu. W porównaniu z

wczeœniej opisanymi s¹ wolniejsze i mniej pojemne. Mimo to maj¹ istotne

zalety. Opracowanie i programowanie uk³adu trwa od kilku godzin do kilku

dni, a koszty ma³ych serii s¹ niewielkie. Poza tym istnieje bogate

oprogramowanie wspomagaj¹ ce proces projektowania, przez co staje siê ono

³atwiejsze i dostêpne dla szerokiego grona u¿ytkowników.

Uk³ady te ze wzglêdu na cechy struktury wewnêtrznej dzieli siê na:

programowalne uk³ady logiczne PLD (Programmable Logic Devices) oraz

uk³ady FPGA (Field Programmable Gate Array).

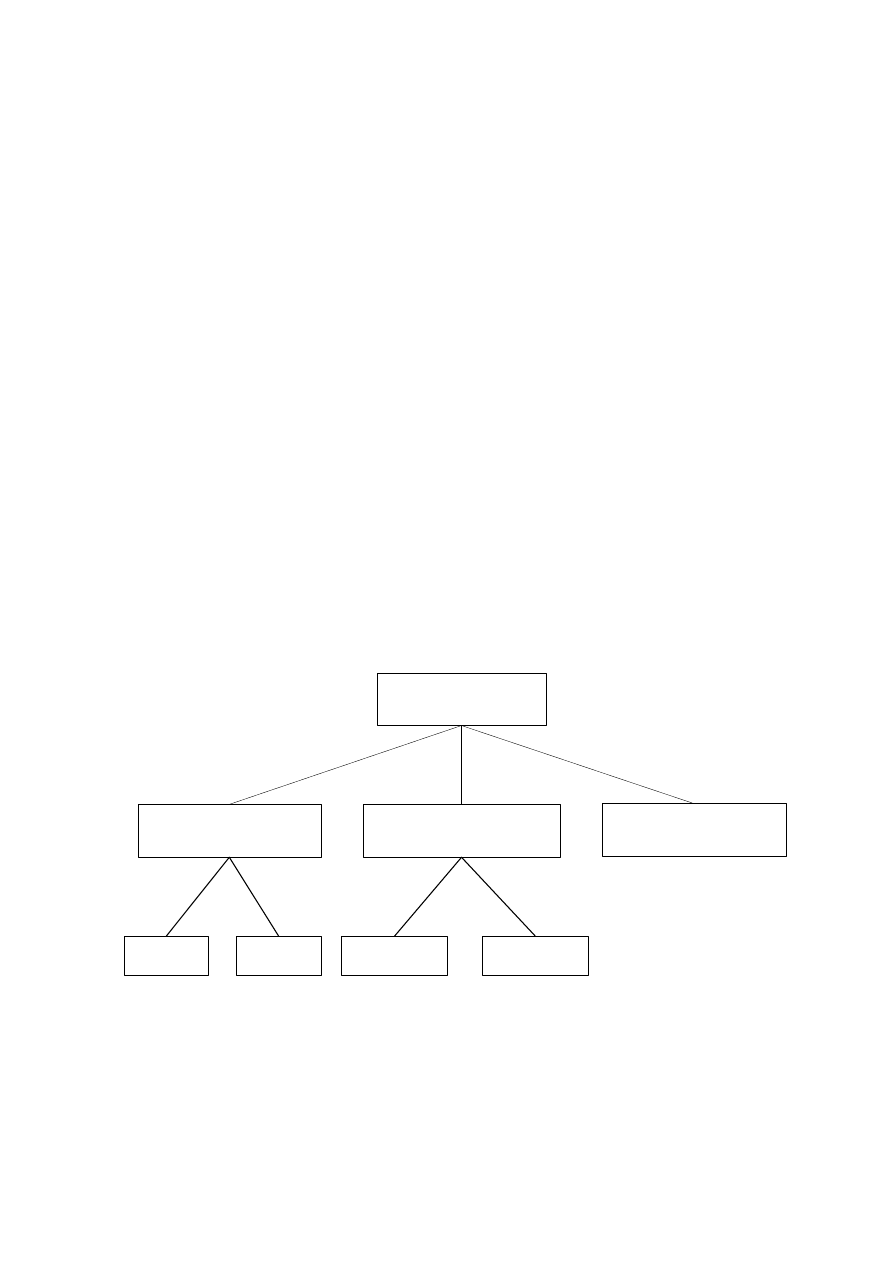

Podzia³ uk³adów ASIC pokazany zosta³ na rysunku 1.1.

Rys. 4.1. Podzia³ uk³adów ASIC.

UK£ADY ASIC

UK£ADY

PROGRAMOWANE

PRZEZ U¯YTKOWNIKA

UK£ADY PROJEKTOWANE

PRZEZ U¯YTKOWNIKA

(SEMI-CUSTOM)

UK£ADY ZAMAWIANE

PRZEZ U¯YTKOWNIKA

(FULL-CUSTOM)

PLD

FPGA

GATE

ARRAY

STANDARD

CELL

37

4.1.2. Struktury uk³adów PLD i FPGA.

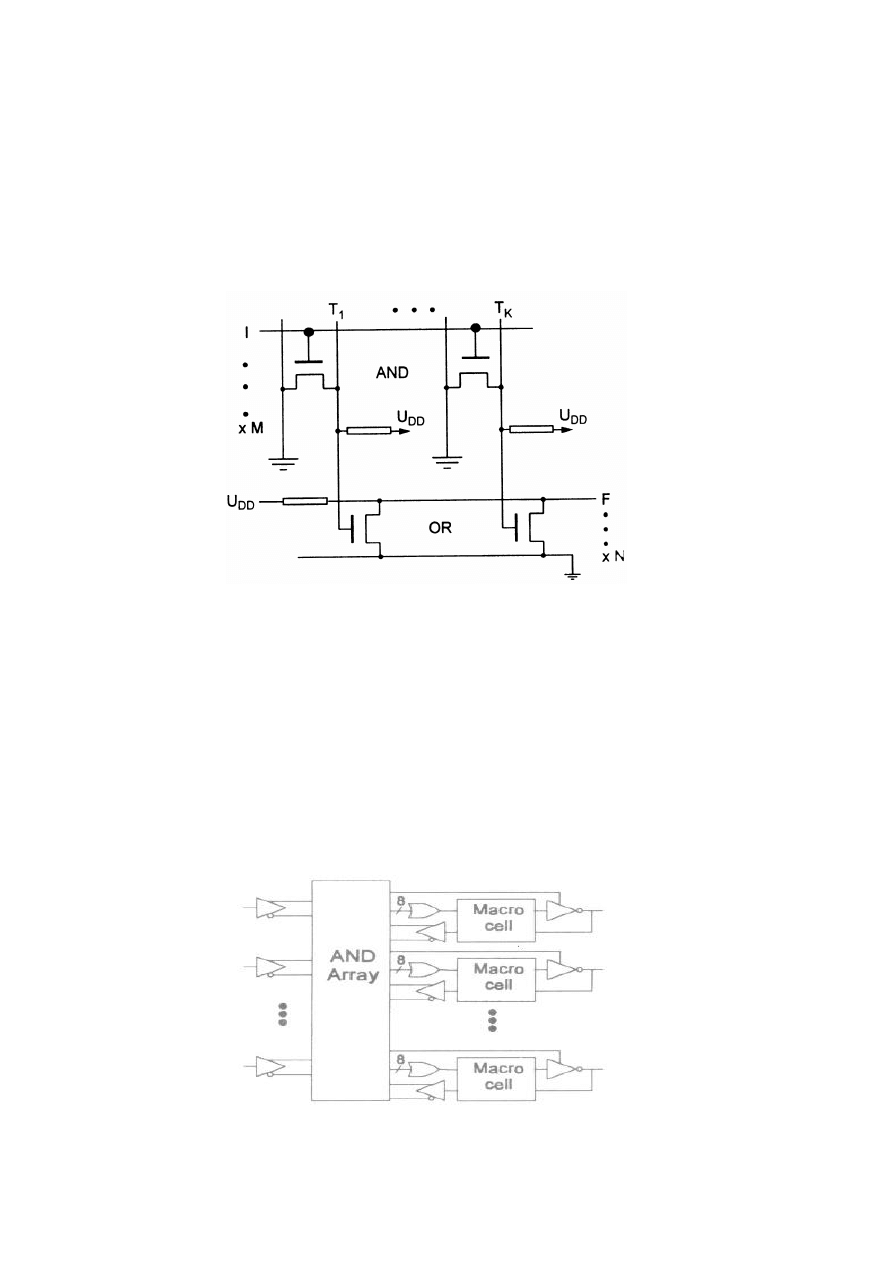

Podstawowym elementem konstrukcyjnym programowalnych modu³ów logicznych

jest matryca tranzystorów (w zale¿noœci od technologii s¹ to tranzystory bipolarne TTL lub

typu MOS). W uk³adach PLD tranzystory te s¹ u³o¿one w formie dwóch matryc: matrycy

AND i matrycy OR (rys 4.2).

Rys. 4.2. Matryca tranzystorów.

Elektrody tranzystorów s¹ do³¹ czone: bramka do poziomych linii wejœciowych (I), Ÿród³o do

linii wyjœciowych (F), a tak¿e do poziomych lub pionowych linii doprowadzaj¹ cych napiêcie

zasilania. Po³¹ czenia odpowiednich linii z bramkami tranzystorów (tzw. punkty

programowania), s¹ zrealizowane w postaci cienkich tytanowo-wollframowych

bezpieczników. Umo¿liwiaj¹ one programowanie matryc prosta metod¹ przepalenia.

W uk³adach tych wystêpuj¹ tak¿e zespo³y elementów wyjœciowych: przerzutniki i trójstanowe

bufory wyjœciowe lub w bardziej rozbudowanych uk³adach multipleksery i bramki OR, zwane

makrokomórkami (ang. macrocell).

Rys. 4.3. Struktura prostych uk³adów programowalnych PLD.

38

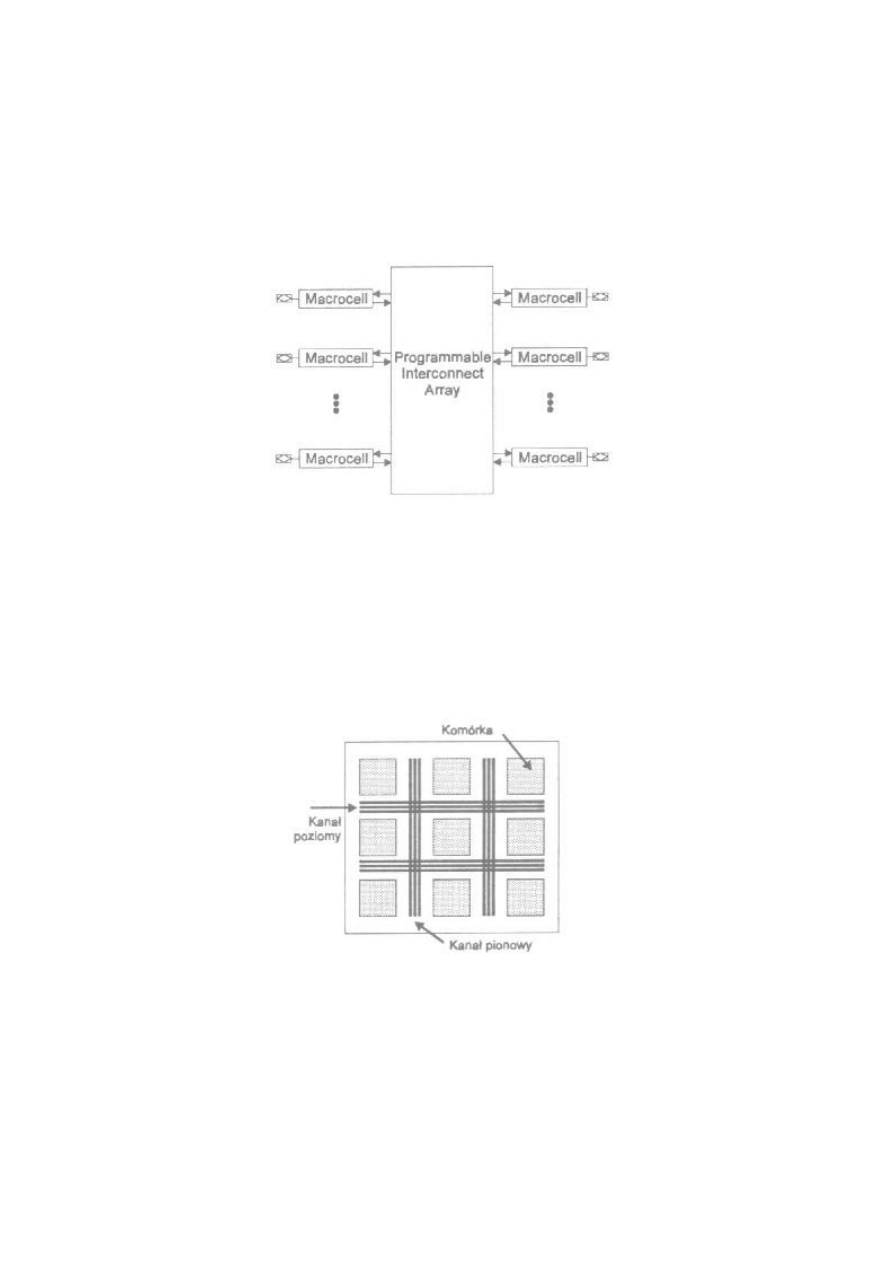

W bardziej z³o¿onych uk³adach PLD, tzw. CPLD (Complex PLD) zastosowano

programowaln¹ matrycê po³¹ czeñ (Progammable Interconnect Array) otoczon¹

makrokomórkami. W sk³ad takiej makrokomórki wchodz¹ : programowalne przerzutniki,

bramki OR, XOR, multipleksery oraz bufory trójstanowe (rys. 4.4).

Rys. 4.4. Struktura z³o¿onych uk³adów programowalnych CPLD.

Drugim typem struktury uk³adów programowanych przez u¿ytkownika s¹ uk³ady FPGA.

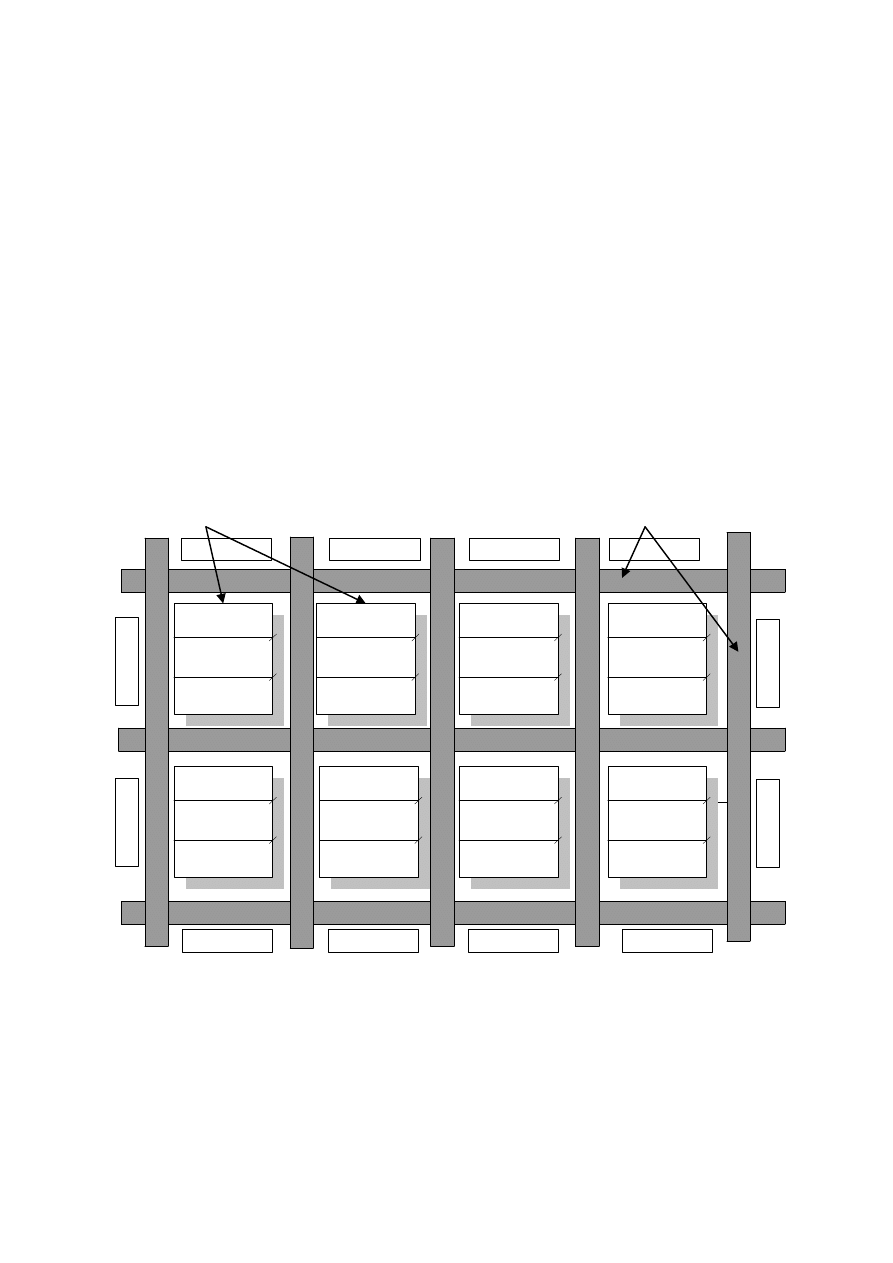

Typowa struktura tych uk³adów to prostok¹ tna macierz elementów logicznych, zwanych

komórkami, zwi¹ zanych ze sob¹ programowalnymi po³¹ czeniami (rys. 4.5).

Rys. 4.5. Architektura uk³adów FPGA.

4.1.3. Uk³ady EPLD firmy ALTERA.

Uk³ady EPLD (Erasable PLD) to uk³ady w pe³ni programowalne, tzn. kasowalne i

programowalne sygna³ami elektrycznymi. Jednym z producentów tych uk³adów jest firma

39

ALTERA. Oferuje ona dziewiêæ rodzin uk³adów: CLASSIC+, MAX 5000, MAX 3000, MAX

7000, MAX 9000, FLEX 6000, FLEX 8000 i FLEX 10K i APEX 20K. Ró¿ni¹ siê struktur¹

wewnêtrzn¹ , pojemnoœci¹ i szybkoœci¹ dzia³ania. Wszystkie uk³ady poszczególnych rodzin s¹

wykonane w technologii CMOS. Dziêki temu uzyskano zmniejszony pobór mocy, wiêksz¹

niezawodnoϾ.

Niniejszy podrozdzia³ zawiera krótk¹ charakterystykê poszczególnych rodzin

uk³adów, g³ównie pod wzglêdem architektury wewnêtrznej. Celowo wiêcej miejsca

poœwiêci³em dwóm ostatnim rodzinom, a to z uwagi na fakt, ¿e szyfrowanie i deszyfrowanie z

wykorzystaniem algorytmu Rijndael implementowany bêdzie w dwóch oddzielnych uk³adach

rodziny FLEX 10K, zaœ rodzina APEX 20K nale¿y do najnowszej technologii opracowanej

przez firmê ALTERA. Warto zatem przyjrzeæ siê nowym rozwi¹ zaniom konstrukcyjnym,

gdy¿ uk³ady te stan¹ siê najprawdopodobniej najbardziej popularne w ci¹ gu najbli¿szych

kilku lat i mo¿na by³oby w przysz³oœci zaimplementowaæ szyfr Rijndael w jednym uk³adzie z

tej rodziny. Obecnie nie jest to jeszcze mo¿liwe ze wzglêdu na niedostêpnoœæ narzêdzia do

projektowania tych uk³adów o nazwie Quartus.

CLASSIC+ to rodzina uk³adów produkowana w technologii CMOS. Kasowanie i

programowanie odbywa siê poprzez nieulotne elementy konfiguracyjne oparte na pamiêciach

EPROM. Architektura tych uk³adów sk³ada siê z pojedynczych macierzy makrokomórek

po³¹ czonych globaln¹ szyn¹ danych jak na rys. 4.6.

Rys. 4.6. Globalna szyna po³¹ czeñ uk³adów serii CLASSIC+.

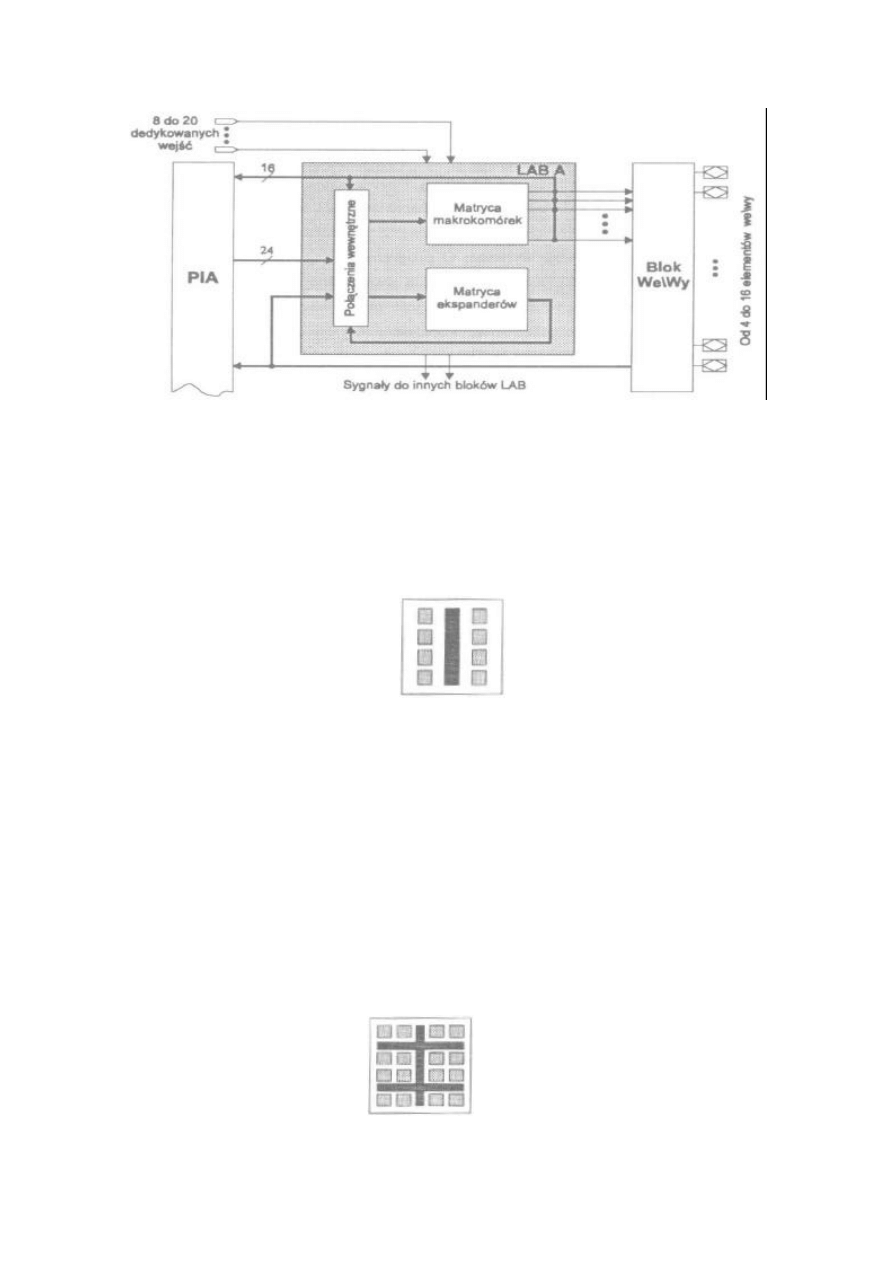

Uk³ady typu MAX 5000 (Multiple Array MatriX) realizowane s¹ w technologii

CMOS/EPROM. Makrokomórki tych uk³adów po³¹ czone s¹ w grupy zwane LAB (rys. 4.7).

40

Rys. 4.7. Architektura uk³adów MAX 5000.

Matryce makrokomórek LAB s¹ po³¹ czone poprzez programowaln¹ matrycê po³¹ czeñ PIA

(rys. 4.8). Matryca ta realizuje po³¹ czenia dla sygna³ów wejœciowych oraz sygna³ów z wyjœæ

makrokomórek.

Rys. 4.8. Programowalna sieæ po³¹ czeñ uk³adów serii MAX 5000.

Rodzina MAX 5000 zawiera od 1 do 12 bloków LAB.

Uk³ady MAX 7000 nale¿¹ do drugiej generacji uk³adów MAX. S¹ one produkowane

w technologii CMOS EEPROM. Uk³ady te dostarczaj¹ od 600 do 5000 bramek logicznych,

zawieraj¹ od 32 do 256 makrokomórek po³¹ czonych w grupy po szesnaœcie makrokomórek,

zwane blokami LAB. Po³¹ czenia pomiêdzy blokami oraz z elementami we/wy s¹

zrealizowane za pomoc¹ programowalnej szyny po³¹ czeñ PIA, przedstawionej na rys. n.

Ka¿dy blok LAB ma swój blok we/wy za pomoc¹ którego wysy³a sygna³y na zewn¹ trz

uk³adu.

Rys. 4.9. Programowalna matryca po³¹ czeñ uk³adów serii MAX 7000.

41

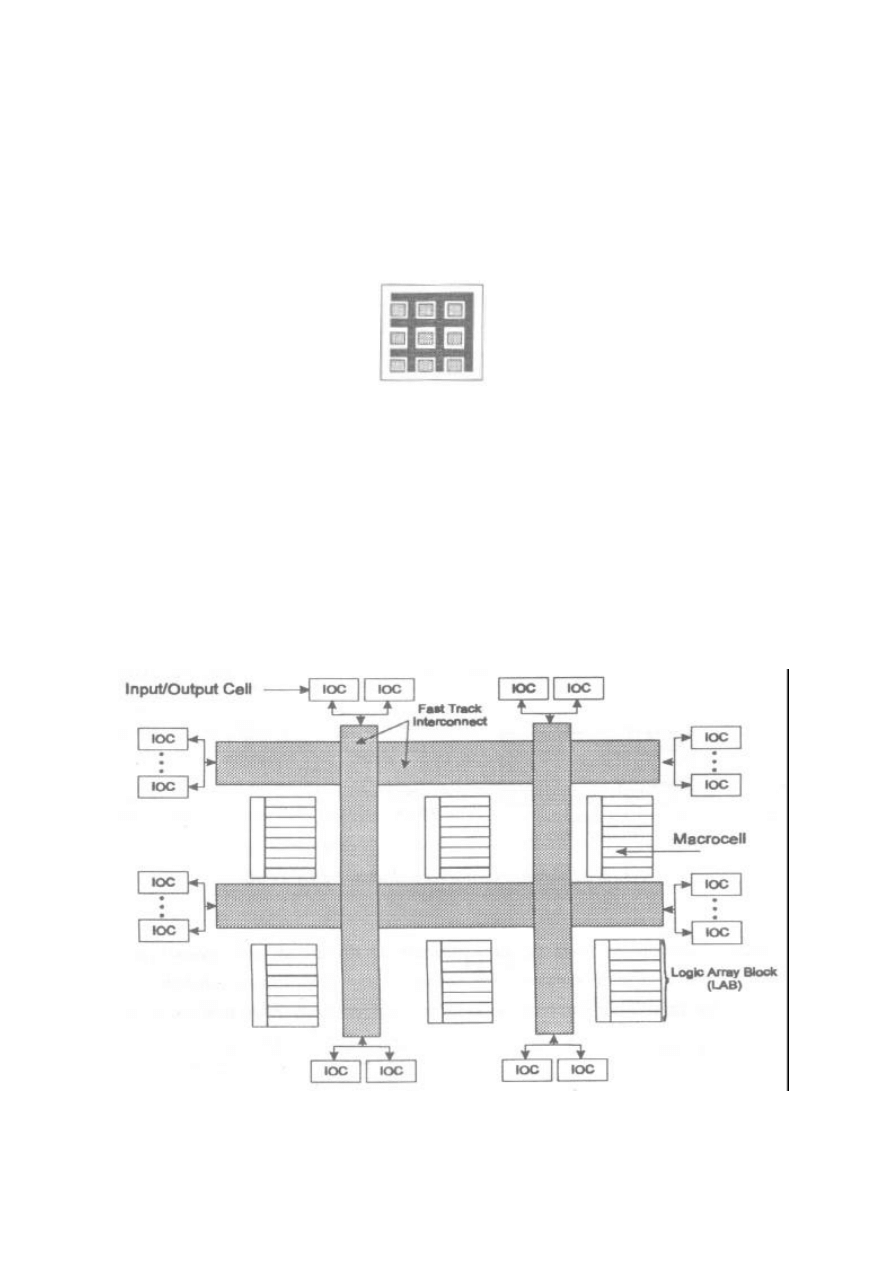

Uk³ady MAX 9000 nale¿¹ do najnowszych i najnowoczeœniejszych uk³adów trzeciej

generacji rodziny MAX. Produkowane s¹ w zaawansowanej technologii CMOS EPROM.

Zawieraj¹ od 6000 do 12000 bramek u¿ytkowych i od 320 do 560 makrokomórek. W

architekturze wewnêtrznej najwa¿niejsz¹ zmian¹ jest wprowadzenie nowej struktury po³¹ czeñ

wewnêtrznych, zwanych Fast Track Interconnect (rys. 4.10).

Rys. 4.10. Szybkie po³¹ czenia typu „Fast Track Interconnent”.

Po³¹ czenia wewnêtrzne sk³adaj¹ siê z kolumn i wierszy magistral danych. Przechodz¹ one

wzd³u¿ i wszerz ca³ego uk³adu. Magistrale te ³¹ cz¹ poszczególne bloki LAB miêdzy sob¹ oraz

³¹ cz¹ bloki LAB z elementami we/wy. Nowa technologia ca³kowicie zmienia sposób

rozmieszczenia logiki w uk³adzie. W ten sposób rozwi¹ zano problem tzw. „w¹ skiego gard³a”

w procesie projektowania, poniewa¿ po³¹ czenia wewnêtrzne typu Fast Track dostarczaj¹

wystarczaj¹ co du¿o zasobów, aby sprawnie po³¹ czyæ wszystkie elementy LAB,

makrokomórki, elementy we/wy itp. Schemat blokowy uk³adów MAX 9000 przedstawiony

jest na rys. 4.11.

Rys. n. Schemat blokowy uk³adów MAX 9000.

42

Zmianie uleg³a tak¿e struktura LAB i makrokomórki. Zmiana polega na tym, ¿e matryca

wejœciowa jest wspólna dla wszystkich makrokomórek w danym bloku LAB.

Cech¹ charakterystyczn¹ uk³adów serii FLEX 10K jest to, ¿e uk³ady te jako pierwsze

posiadaj¹ strukturê logiczn¹ z wbudowan¹ programowaln¹ logik¹ specjalnego przeznaczenia.

Dziêki tej technologii mo¿liwe jest implementowanie funkcji pamiêci ROM i RAM, a

wielkoœæ realizowanych projektów mo¿e przekraczaæ 250000 bramek logicznych.

Struktura wewnêtrzna uk³adów serii FLEX 10K sk³ada siê z bloków matryc wbudowanych,

bloku matryc logicznych oraz szybkich po³¹ czeñ typu Fast Track, co zosta³o pokazane na rys.

4.12.

Rys. 4.12. Schemat blokowy architektury FLEX 10K.

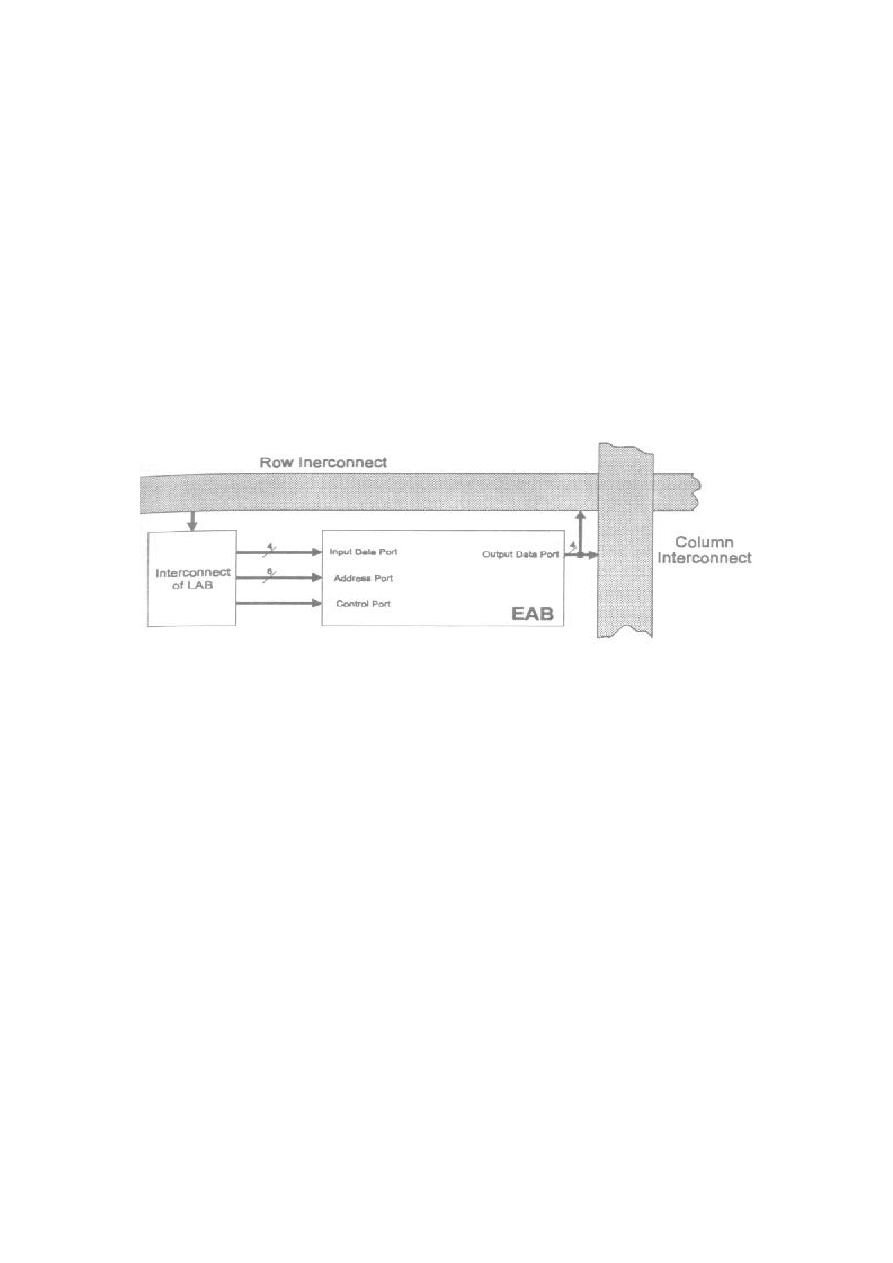

Wbudowana matryca (ang. embedded array) s³u¿y do emulowania pamiêci i

specjalizowanych funkcji logicznych o wielu wejœciach i wielu wyjœciach. Jest umieszczona

w blokach wbudowanych matryc EAB (ang. Embedded Array Block).

Ka¿dy EAB jest oddzielnym blokiem logicznym, który mo¿e pracowaæ niezale¿nie, lub mo¿e

byæ po³¹ czone z innymi w celu stworzenia wiêkszych struktur. Wejœcia do bloków EAB

pochodz¹ od wiersza po³¹ czeñ lokalnych, wyjœcia natomiast mog¹ byæ pod³¹ czone zarówno

do wiersza jak i do kolumny. Szybkie po³¹ czenia „Fast Track” pozwalaj¹ pod³¹ czyæ wejœcia i

wyjœcia EAB do zewnêtrznych wyjœæ uk³adu, do innego EAB lub do bloku LAB. Bloki EAB

mog¹ byæ u¿yte do:

Embedded

Array

Block

Embedded

Array

Block

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

Blok wbudowanych

matryc EAB

Elementy

wejœcia/wyjœcia

Element

logiczny

LE

Szybkie magistrale

wewnêtrzne

Blok matryc

logicznych

LAB

43

Ø emulacji funkcji pamiêci o pojemnoœci 2048 bitów (2KB) w nastêpuj¹ cych

konfiguracjach: 256 x 8 bitów, 512 x 4 bity, 1024 x 2 bity lub pojedyncze

2048 bitów (oprócz uk³adów rodziny FLEX 10KE, dla których konfiguracja ta

przedstawia siê nastêpuj¹ co: 256 x 16 bitów, 512 x 8 bitów, 1024 x 4 bity,

2048 x 2 bity lub pojedyncze 4096 bitów). Ka¿da z tych konfiguracji ma czas

cyklu dostêpu ok. 20 ns.;

Ø implementacji funkcji pamiêci RAM. Ka¿dy EAB zawiera jeden port

adresowy, danych wejœciowych, danych wyjœciowych oraz port steruj¹ cy, które

s¹ po³¹ czone kolumnami i wierszami szybkich po³¹ czeñ jak na rys. 4.13.

Rys. 4.13 . EAB jako blok pamiêci RAM.

Ø implementacji funkcji pamiêci ROM. Do bloku EAB wpisywane s¹ bity

pamiêci wed³ug specyfikacji projektanta. EAB w tej konfiguracji dzia³a tak

samo jak przy konfiguracji jako RAM, z ta ró¿nica, ¿e port danych

wejœciowych nie jest u¿ywany, a bity kontrolne ustawione s¹ na „czytaj”;

Ø implementacji dzia³ania pamiêci jako stos „FIFO”. Blok EAB jest ³¹ czony z

dodatkowym uk³adem logicznym utworzonym w matrycy logicznej.

Ø realizacji specjalizowanych funkcji logicznych takich jak uk³ady mno¿¹ ce,

konwertery danych, procesory sygna³owe, uk³ady arytmetyczne.

Matryce logiczne (ang. Logic Array) s¹ wykorzystywane do tworzenia podstawowej logiki

uk³adu. Sk³adaj¹ siê z szeregu bloków matryc logicznych LAB. Ka¿dy blok LAB zawiera

osiem elementów logicznych LE i zwi¹ zane z nimi po³¹ czenia lokalne. Element logiczny

sk³ada siê z czterowejœciowej komórki LUT, z programowalnego przerzutnika oraz ze œcie¿ek

sygna³ów carry, cascade, tri-state. Ka¿dy blok LAB mo¿e byæ u¿yty do zaprogramowania

œredniej wielkoœci bloków logicznych.

44

Wyjœcia poszczególnych matryc EAB i LAB s¹ po³¹ czone poprzez system szybkich magistral

wewnêtrznych biegn¹ cych poprzez ca³y uk³ad.

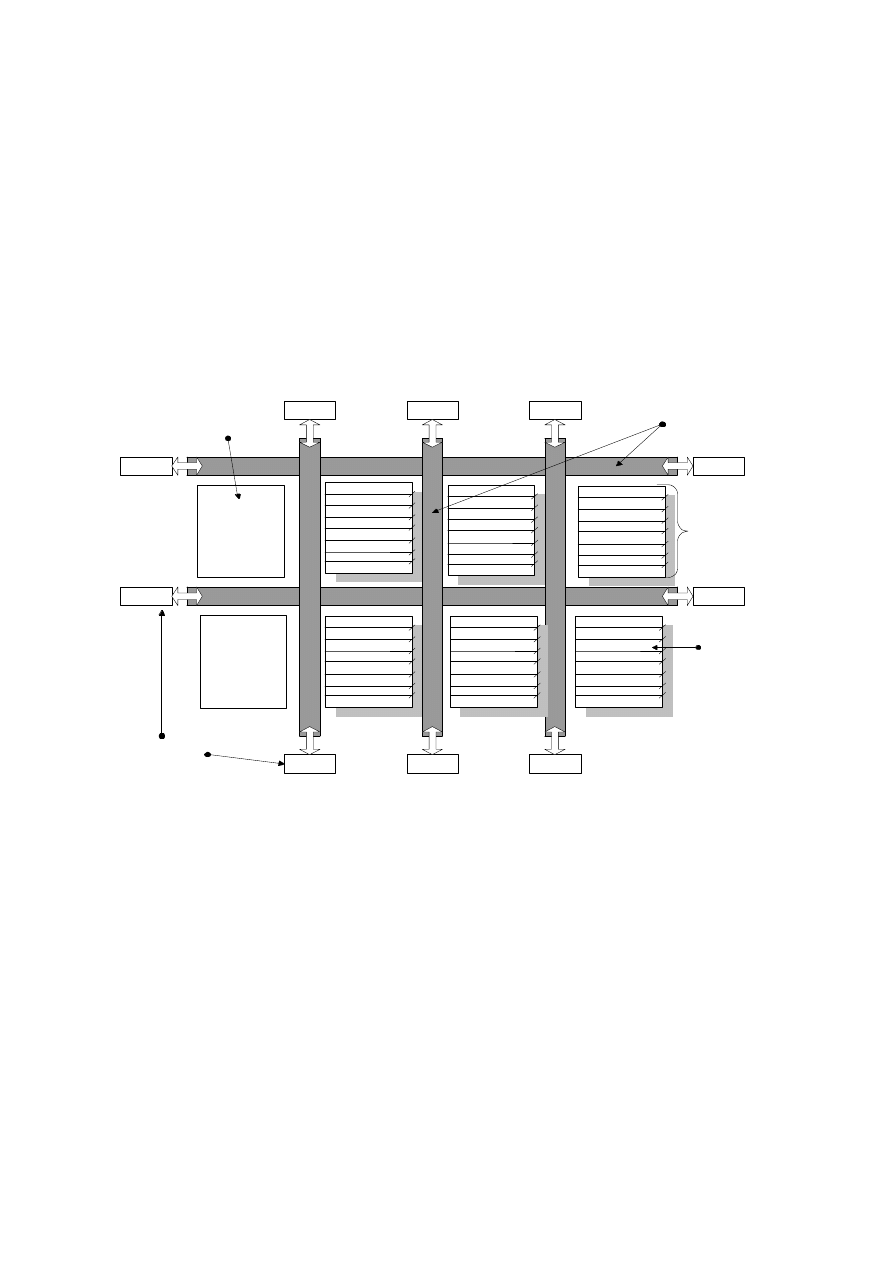

Uk³ady APEX 20K to najnowsze, a jednoczeœnie najnowoczeœniejsze uk³ady

programowalne firmy ALTERA. W obecnej chwili nale¿¹ równie¿ do najwiêkszych uk³adów

programowalnych produkowanych na œwiecie. Przewiduje siê, ¿e uk³ady te stan¹ siê bardzo

popularne i bêd¹ zastêpowa³y uk³ady „semi-custom”.

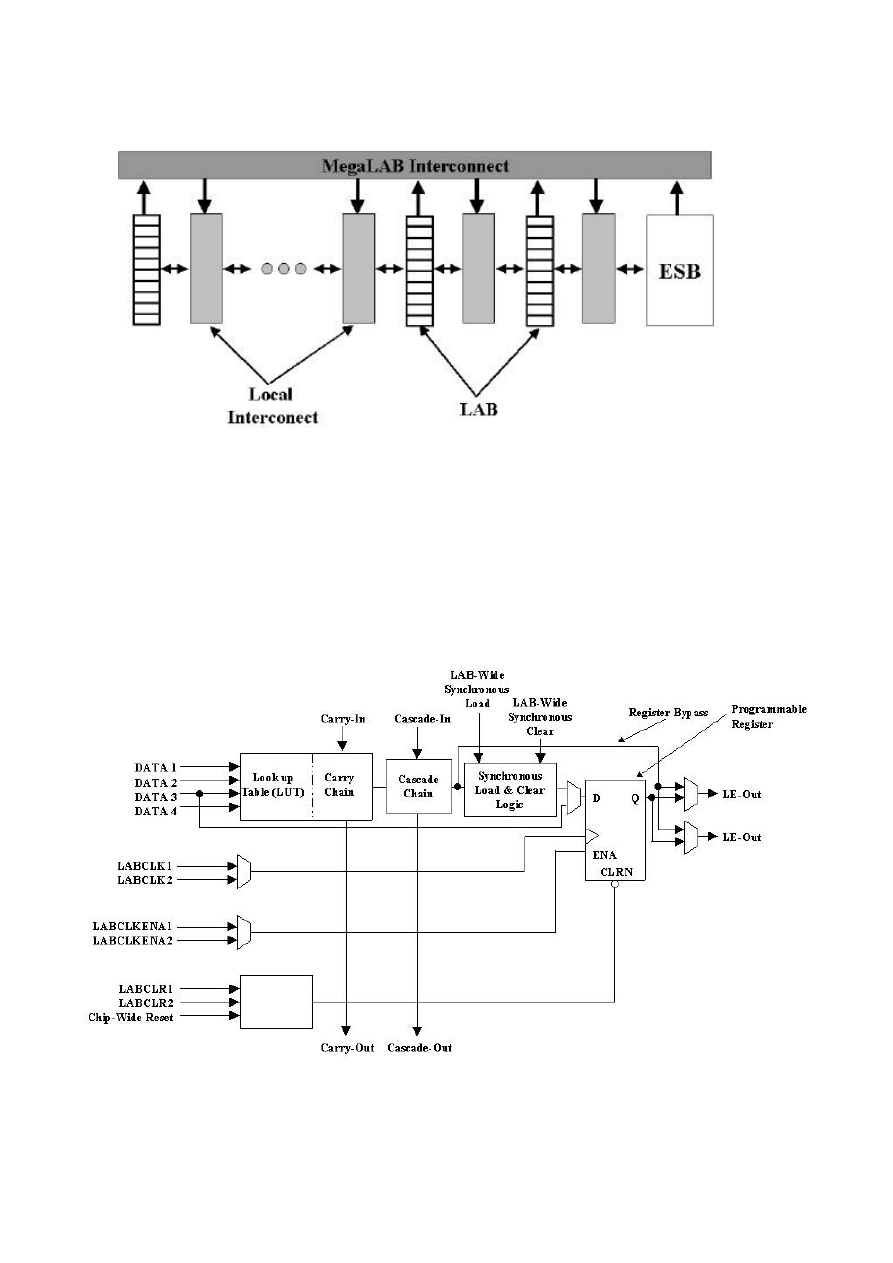

Struktura wewnêtrzna uk³adów tej rodziny posiada wiele cech wspólnych z architekturami

omawianych poprzednio rodzin. W sk³ad struktury tych uk³adów wchodz¹ MegaLAB-y

sk³adaj¹ ce siê z: 16-tu LAB-ów (Logic Array Bock), bloków pamiêci ESB (Embedded

System Block) oraz szybkich magistral wewnêtrznych w ka¿dym megalabie. Strukturê ogóln¹

uk³adów przedstawia rys. 4.14.

Rys. 4.14. Struktura wewnêtrzna uk³adów APEX 20K.

Struktura MegaLaba pokazana jest na rysunku 4.15.

IOE

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

LUT

przerzutniki

ESB

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

IOE

MEGA LAB-y

Szybkie drogi ³¹czeniowe

45

Rys. 4.15. Struktura MegaLAB.

Ka¿dy LAB zawiera 10 elementów LE (Logic Element), co daje w sumie 160 elementów LE

w MegaLAB. Logic Element stanowi podstawow¹ komórk¹ programowaln¹ . Jej strukturê

przedstawia rysunek 4.16.

Rys. 4.16. Struktura bloku LE.

46

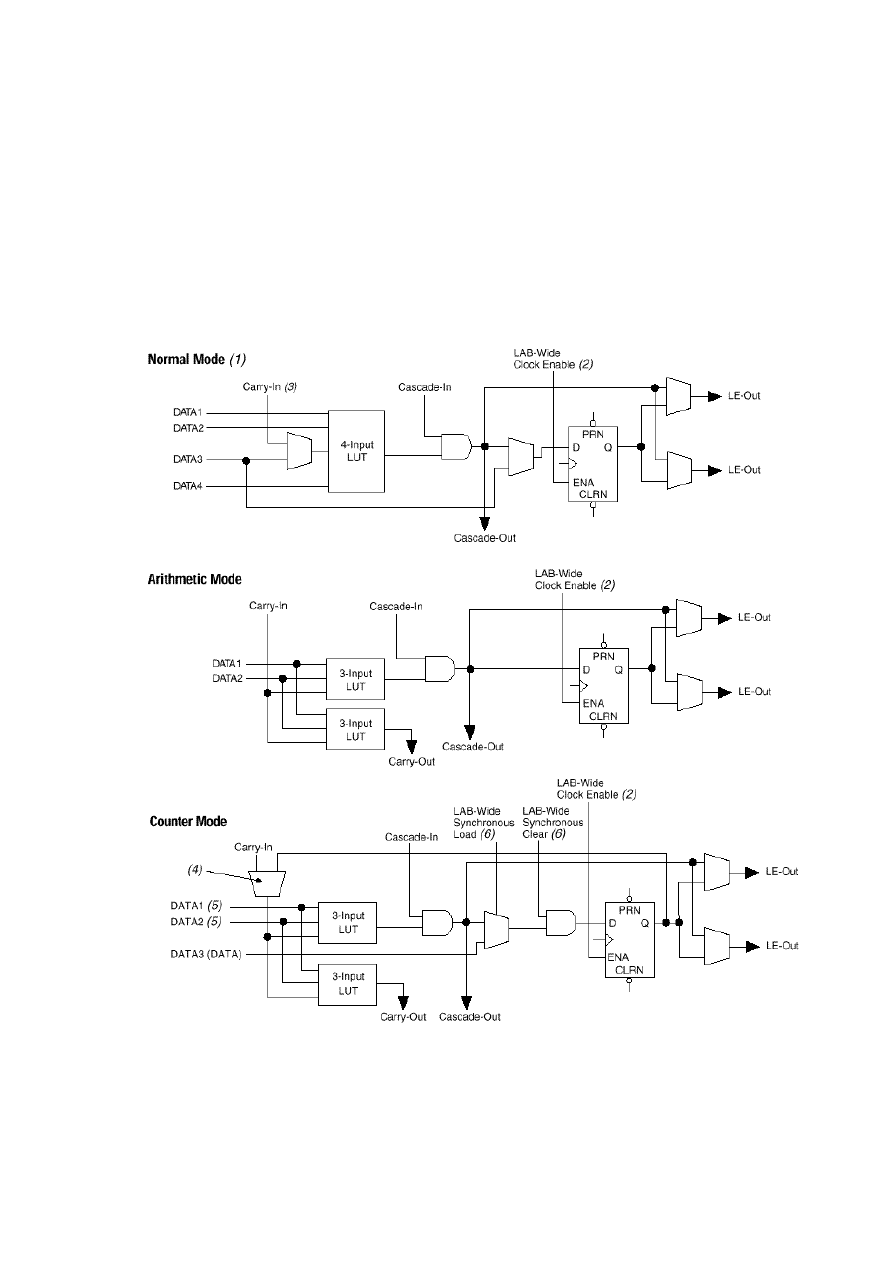

Ka¿dy blok LE posiada przerzutnik, który mo¿e byæ definiowany jako przerzutnik typu D, T,

JK lub RS. Istnieje mo¿liwoœæ pominiêcia zarówno przerzutnika jak i funkcji LUT. Komórki

takie mo¿na konfigurowaæ w trzech podstawowych trybach:

Ø

tryb normalny (Normal Mode);

Ø

tryb arytmetyczny (Arithmetic Mode);

Ø

tryb licznika (Coounter Mode).

Tryby pracy komórek przedstawia rysunek 4.17.

Rys. 4.17. Tryby pracy komórek logicznych.

Blok ESB (Embedded System Block) mo¿e implementowaæ ró¿ne typy bloków pamiêci:

Ø blok pamiêtaj¹ cy w konfiguracji: 128 x 16, 256 x 8, 512 x 4, 1024 x 2,

2048 x 1;

47

Ø pamiêæ RAM;

Ø pamiêæ ROM;

Ø pamiêæ FIFO;

Ø pamiêæ kontekstowa (dla uk³adów APEX20KE).

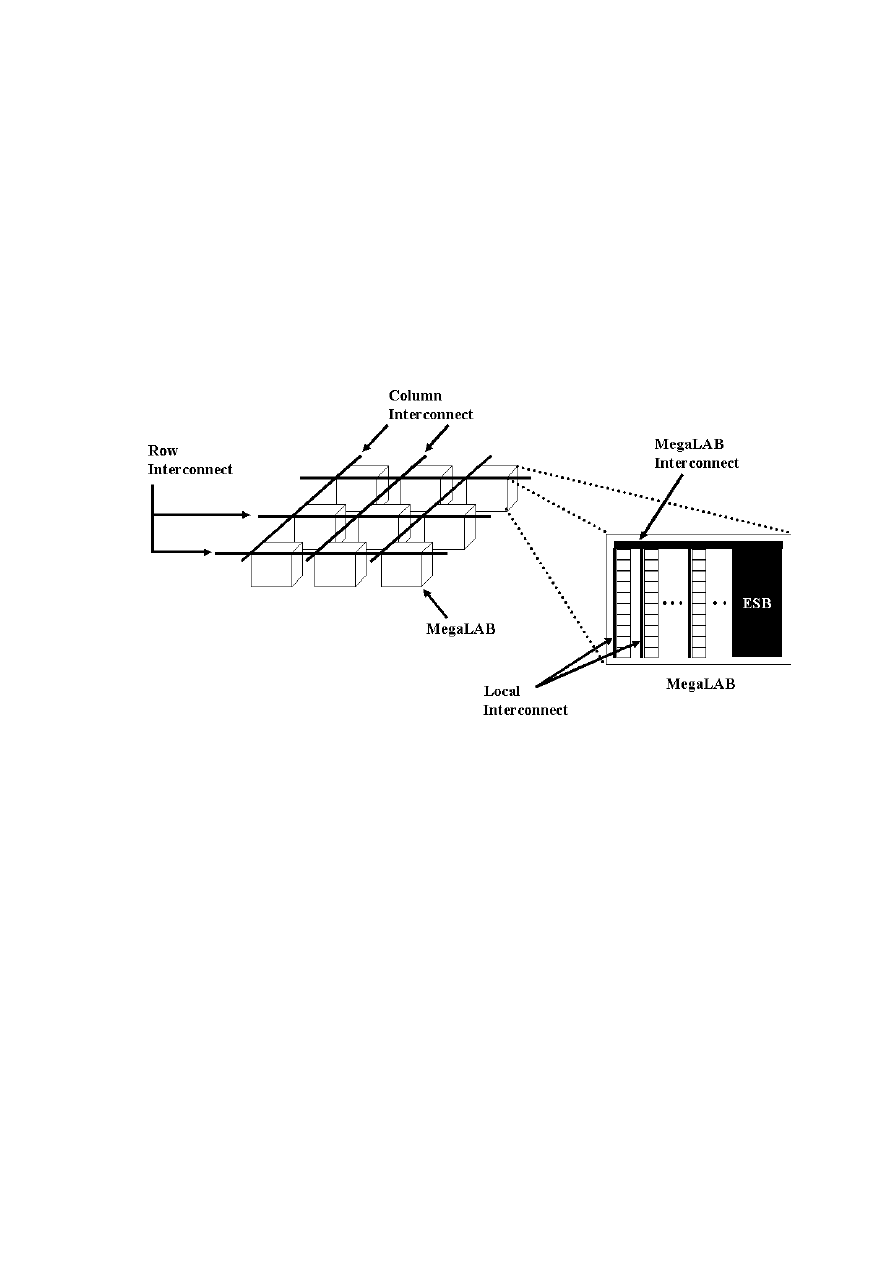

Struktura dróg ³¹ czeniowych w uk³adach rodziny Apex 20K jest trójstopniowa (rys. 4.18) :

œcie¿ki ³¹ czeniowe wewn¹ trz LAB (Local Interconnect);

- œcie¿ki ³¹ czeniowe wewn¹ trz MegaLAB (MegaLAB Interconnect);

-

globalne œcie¿ki ³¹ czeniowe (Row Interconnect, Column Interconnect ).

Rys. 4.18. Struktura dróg ³¹ czeniowych uk³adów APEX 20K.

4.2. Zasady specyfikacji sprzêtu w systemach projektowania uk³adów

FPLD

Projektowanie uk³adów PLD dzieli siê na trzy etapy:

Ø wprowadzenie specyfikacji projektu;

Ø przetwarzanie wprowadzonego projektu;

Ø weryfikacja i programowanie opracowanych struktur.

W pierwszym etapie formu³owany jest opis dzia³ania projektowanego uk³adu za pomoc¹

schematu logicznego, opisu tekstowego lub wykresów czasowych.

Edytor graficzny (ang.Graphic Editor) s³u¿y do konstruowania schematów logicznych i

blokowych. Pozwala wykorzystywaæ do tego celu bibliotekê standardowych bloków

48

funkcjonalnych TTL i makrofunkcji oraz stosowaæ globalne oznaczenia sygna³ów i linii

po³¹ czeniowych.

Edytor tekstowy (ang. Text Editor) umo¿liwia przygotowanie formalnego opisu uk³adu w

odpowiednim jêzyku specyfikacji sprzêtu, np. AHDL (Altera Hardware Description

Langguage), VHDL (Very High Speed Integrated Circuits Hardware Description Language).

Dodatkowym sposobem opisu dzia³ania projektowanego uk³adu jest w najnowszych

systemach opis behawioralny (okreœla zale¿noœci miêdzy sygna³ami wejœciowymi i

wyjœciowymi). Tê formê specyfikacji umo¿liwia edytor wykresów czasowych (ang.

Waveform Editor).

Tworzenie specyfikacji uk³adu u³atwia mo¿liwoœæ stosowania wielopoziomowej struktury

hierarchicznej i dowolnego ³¹ czenia dostêpnych œrodków opisu.

Drugi etap funkcjonowania systemu obejmuje weryfikacjê formaln¹ projektu i przetworzenie

danych (kompilacjê). Wynikiem jest szczegó³owa konstrukcja funkcjonalna i rozmieszczenie

jej elementów w wybranej strukturze uk³adu programowalnego. Proces kompilacji projektu

polega na optymalizacji jego struktury logicznej i dekompozycji na mniejsze czêœci tak, aby

mog³y one byæ rozmieszczone i odpowiednio po³¹ czone ze sob¹ w zadanej strukturze

programowalnej. Podczas kompilacji projektu tworzone s¹ dane dotycz¹ ce modelu fizycznego

funkcjonowania uk³adu programowalnego i mapy punktów po³¹ czeñ niezbêdnych do

symulacji uk³adu.

Trzeci etap to weryfikacja i programowanie. Ma ona na celu zbadanie poprawnoœci

opracowanej konstrukcji pod wzglêdem funkcjonalnym i zachowania siê w czasie. Taka

weryfikacja polega na przeprowadzeniu eksperymentów symulacyjnych, które s¹

formu³owane w jêzyku przebiegów czasowych (Waveform Editor). W trakcie dzia³ania

procedur symulacyjnych informacje podane na wejœcie uk³adu zostaj¹ przetworzone na

informacje pojawiaj¹ ce siê na wyjœciu uk³adu. W rezultacie otrzymuje siê opis dzia³ania

uk³adu wyra¿ony za pomoc¹ wykresów czasowych. Koñcowym etapem jest realizacja

projektu w uk³adzie programowalnym w procesie programowania.

Do projektowania uk³adów firmy Altera (oprócz uk³adów rodziny Apex 20K) s³u¿y system

MAX+PLUS II wykorzystuj¹ cy jêzyk specyfikacji nazywany AHDL. Do projektowania

uk³adów rodziny Apex 20K s³u¿y system QUARTUS.

49

4.3. Charakterystyka systemu MAX+PLUS II.

W podrozdziale tym krótko przedstawiê system MAX+PLUS II, w którym

realizowa³ bêdê projekt implementacji algorytmu blokowego Rijndael. S³u¿y do

projektowania uk³adów rodzin: CLASSIC, MAX 5000, MAX 3000, MAX 7000, MAX 9000,

FLEX 6000, FLEX 8000, FLEX 10K. W sk³ad systemu wchodzi 11 programów u¿ytkowych:

Ø

edytor tekstowy (ang. Text Editor) – s³u¿y do wprowadzania i redagowania

tekstowych zbiorów projektowych AHDL z rozszerzeniem .tdf oraz VHDL z rozszerzeniem

.vhd w jêzyku VHDL. Edytor ten umo¿liwia równie¿ wprowadzanie i edytowanie dowolnych

zbiorów w formacie ASCII;

Ø

edytor graficzny (ang. Graphic Editor) – s³u¿y do tworzenia schematów logicznych.

Podstaw¹ do tworzenia schematów s¹ biblioteki funkcji elementarnych: prymitywów,

makrofunkcji, megafunkcji, biblioteki funkcji parametryzowanych LPM (ang. Library of

Parametrized Modules).

Ø

edytor przebiegów czasowych (ang. Waveform Editor) – s³u¿y do opisu projektu, a

przede wszystkim jako narzêdzie do wprowadzania wektorów testowych w postaci

przebiegów czasowych do obserwowania wyników symulacji. Pozwala tworzyæ zbiory

projektowe za pomoc¹ przebiegów czasowych (Waveform Design File) z rozszerzeniem .wdf

oraz zbiory symulacyjne (ang. Simulator Channel Files) z rozszerzeniem .scf.;

Ø

edytor symboli (ang. Symbol Editor) – s³u¿y do ogl¹ dania, tworzenia i edytowania

symboli, reprezentuj¹ cych uk³ady logiczne;

Ø

edytor planu zasobów (ang. Floorplan Editor) – s³u¿y do wprowadzania i modyfikacji

planu zasobów fizycznego uk³adu oraz do ogl¹ dania rezultatów syntezy topologicznej;

Ø

kompilator (ang. Compiler) – sk³ada siê z modu³ów i aplikacji, które sprawdzaj¹

projekt pod wzglêdem poprawnoœci formalnej i wykrywaj¹ w nim ewentualne b³êdy,

przeprowadzaj¹ syntezê logiczn¹ , przydzielaj¹ projekt do jednego lub wiêcej uk³adów i

generuj¹ modele do symulacji, analizy czasowej oraz fizycznego programowania uk³adów w

programatorze;

Ø

symulator (ang. Simulator) – podstawow¹ rol¹ symulatora jest testowanie funkcji i

zachowanie siê w czasie projektowanego uk³adu, umo¿liwia badanie funkcjonalnej

poprawnoœci projektu oraz sprawdzenie przebiegów czasowych w wybranych wêz³ach

projektu po jego kompilacji;

50

Ø

analizator czasowy (ang. Timing Analyzer) – to narzêdzie s³u¿¹ ce do badania czasów

propagacji sygna³ów na drodze pomiêdzy wybranymi wêz³ami w projekcie oraz do okreœlenia

maksymalnych czêstotliwoœci dla sygna³ów zegarowych w projekcie.

Ø

programator (ang. Programmer) – s³u¿y do programowania uk³adów w systemie

MAX+PLUS II. Podstawowym sposobem programowania uk³adów w systemie MAX+PLUS

II jest programowanie z u¿yciem konwencjonalnego programatora. Programator sk³ada siê z

karty do komputera i g³ównego modu³u programuj¹ cego MPU (ang. Master Programming

Unit) wraz z zestawem adapterów, które dopasowuj¹ elektrycznie i funkcjonalnie modu³

MPU do obudów uk³adów programowalnych. Inn¹ metod¹ jest tzw. programowanie w

systemie (ang. ISP – In-System Programming). S³u¿y do tego celu szeregowy interfejs

programuj¹ cy Byte-Blaster, który ³¹ czy system z programowanym uk³adem za

poœrednictwem portu równoleg³ego komputera. Istot¹ tego sposobu jest programowanie

uk³adu w jego œrodowisku aplikacyjnym (np. na pakiecie w urz¹ dzeniu, którego jest on

integraln¹ czêœci¹ ), przy u¿yciu bardzo prostego sprzêtu ( w postaci interfejsu do

standardowego portu komputera PC). Zarówno programowanie konwencjonalne, jak te¿

programowanie w systemie odbywa siê za poœrednictwem modu³u Programatora. Programator

tworzy sekwencje elektrycznych sygna³ów programuj¹ cych fizyczne struktury na podstawie

zbiorów do programowania, które zosta³y wygenerowane przez kompilator;

Ø

prezenter hierarchii (ang. Hierarchy Display) – wykorzystywany jest w

opracowywaniu z³o¿onych projektów o wielopoziomowej architekturze, jako narzêdzie do

œledzenia projektu;

Ø

procesor komunikatów (ang. Message Processor) – wspó³pracuje z wszystkimi

aplikacjami, kontroluje ich dzia³anie i rejestruje ewentualne b³êdy i defekty w przetwarzanym

projekcie.

Do sprawnej obs³ugi systemu MAX+PLUS II s³u¿y program zarz¹ dzaj¹ cy – menager, którego

okno otwiera siê automatycznie po za³adowaniu systemu. Korzystaj¹ c z g³ównego menu

menagera mo¿na uruchomiæ ka¿d¹ z 11 aplikacji oraz modu³ pomocy.

Pomoc (MAX+PLUS II Help) stanowi Ÿród³o kompletnej i aktualnej dokumentacji

oprogramowania. Pomoc dostarcza wszelkiej niezbêdnej wiedzy o podstawowych

narzêdziach aplikacji oraz danych o wszystkich uk³adach dostêpnych kompilatorowi i

potrzebnych do ich zaprogramowania adapterów. Dostêp do poszczególnych tematów

pomocy jest mo¿liwy z ka¿dej aplikacji systemu i na wiele sposobów. Œwietnie

zaprojektowany interfejs pozwala u¿ytkownikowi skupiæ uwagê na projekcie, nie zaœ na

szczegó³ach pos³ugiwania siê systemem.

51

4.4. Opis jêzyka AHDL.

Altera Hardware Descryption Language (AHDL) jest jêzykiem wysokiego poziomu

ca³kowicie zintegrowanym z systemem MAX+PLUS II. Jêzyk ten zosta³ stworzony do

specyfikowania projektów realizowanych w uk³adach programowalnych firmy ALTERA.

Jego sk³adnia pozwala szybko realizowaæ kombinacyjne operacje logiczne, tablice prawdy

czy uk³ady sekwencyjne. Program w AHDL mo¿e byæ pisany w jakimkolwiek pliku

tekstowym, lecz musi posiadaæ rozszerzenie .tdf (ang. text design file). Nastêpnie mo¿na go

skompilowaæ i przesymulowaæ oraz u¿yæ do zaprogramowania uk³adów firmy Altera.

Najwa¿niejsz¹ cech¹ jest mo¿liwoœæ konstruowania projektów hierarchicznych. Tworzenie

hierarchii jest bardzo proste. Edytor symboli automatyczne generuje symbol, który

reprezentuje plik z rozszerzeniem .sym. Jest on reprezentowany jako prostok¹ t z

zaznaczonymi wejœciami i wyjœciami. Nastêpnie w³¹ cza siê wygenerowany symbol do pliku

.gdf. W ten sposób mo¿na po³¹ czyæ wiele plików .sym w wiêksz¹ ca³oœæ, realizuj¹ c¹ bardziej

skomplikowan¹ funkcjê. W podobny sposób mo¿na w³¹ czaæ do zbiorów .tdf dowolne, w³asne

funkcje i ponad 300 makrofunkcji zdefiniowanych przez Alterê. Ka¿da makrofunkcja zawarta

jest w pliku o rozszerzeniu .inc w bibliotece makrofunkcji. Plik tekstowy ASCII .inc (Include

File) mo¿e byæ do³¹ czony do pliku .tdf poprzez instrukcjê Include. System MAX+PLUS II

pozwala te¿ sprawdziæ sk³adniê AHDL lub przeprowadziæ pe³n¹ kompilacjê. Wszystkie b³êdy

zostan¹ zlokalizowane przez Message Processor i podœwietlone w oknie edytora tekstu.

4.4.1. Elementy sk³adowe projektu.

Poni¿ej wymieniê najwa¿niejsze elementy jêzyka AHDL w kolejnoœci w jakiej powinny

wystêpowaæ w ka¿dym zbiorze TDF. Niektóre z nich s¹ sta³e, inne opcjonalne.

Ø

Ø

instrukcja TITLE (opcjonalnie) – s³u¿y do redagowana komentarzy w zborze

wynikowym Report File;

Ø

Ø

instrukcja INCLUDE (opcjonalnie) – s³u¿y do specyfikacji zbioru w³¹ czanego

Include File;

Ø

Ø

instrukcja CONSTANT (opcjonalnie) – s³u¿y do specyfikacji symbolicznych nazw,

którymi s¹ zastêpowane sta³e;

Ø

Ø

instrukcja DEFINE (opcjonalnie) – s³u¿y do zdefiniowania funkcji numerycznych,

których obliczone wartoœci s¹ argumentami innych funkcji;

Ø

Ø

instrukcja OPTIONS (opcjonalnie) – s³u¿y do okreœlenia porz¹ dku bitów w projekcie;

52

Ø

Ø

sekcja podprojektu SUBDESIGN – s³u¿y do deklarowania wejœæ, wyjœæ i portów

dwukierunkowych. Mog¹ byæ nastêpuj¹ ce typy portów: INPUT – wejœcie, OUTPUT –

wyjœcie, BIDIR - port dwukierunkowy, MACHINE INPUT, MACHINE OUTPUT.

Definiuj¹ c port jako MACHINE INPUT lub MACHINE OUTPUT mo¿emy pobieraæ lub

wysy³aæ stany urz¹ dzenia sekwencyjnego;

Ø

Ø

sekcja zmiennych VARIABLE (opcjonalna) – s³u¿y do deklarowania zmiennych,

które reprezentuj¹ i przechowuj¹ informacjê wewnêtrzn¹ . Zmienne mog¹ byæ deklarowane

dla wêz³ów zwyk³ych lub trójstanowych, prymitywów, makrofunkcji, megafunkcji. Sekcja

VARIABLE mo¿e zawieraæ tak¿e deklaracjê: NODE, REGISTER, STATE MACHINE,

MACHINE ALIAS;

Ø

Ø

sekcja logiczna LOGIC – s³u¿y do okreœlenia operacji logicznych w zbiorze TDF.

Operacje te definiuje siê za pomoc¹ równañ boolowskich, warunków logicznych i tablic

prawdy. Zawarte s¹ w niej wszelkie kombinacje na wartoœciach sygna³ów oraz sposoby ich

przep³ywu. Sekcja ta zaczyna siê s³owem BEGIN a koñczy END. W sekcji tej wystêpuj¹

operatory logiczne i arytmetyczne, instrukcje warunkowe IF, instrukcje wyboru CASE oraz

tablice prawdy. Pozwalaj¹ one na realizacjê praktycznie ka¿dego zadania.

Wyszukiwarka

Podobne podstrony:

EiZI Projekt GiG4 2012 id 15450 Nieznany

Projekt KD remik id 398914 Nieznany

Projekt badan czII id 400460 Nieznany

cw7 ukl 2skl id 123759 Nieznany

ProjektKKa 01 Koncepcja id 4003 Nieznany

projekt stropu akermana id 3996 Nieznany

Projekt Luku Poziomego id 39852 Nieznany

PROJEKT nr 1 STUDENT id 399181 Nieznany

projekt mechanizm nac id 399063 Nieznany

Projekt KKa Wrzesinski id 40012 Nieznany

cw7 ukl 2skl 2 id 123760 Nieznany

PROJEKT Z FIZYKI BUDOWLI id 399 Nieznany

projekt sumator 8bit id 399618 Nieznany

projekt wymiennika ciepla id 39 Nieznany

Projektowanie filtrow FIR id 40 Nieznany

ProjektRys KKa Wrzesinski id 40 Nieznany

Projekt przejsciowy naped id 83 Nieznany

bad przed pod ukl kraz id 76070 Nieznany (2)

Osc an i cyfr id 293334 Nieznany

więcej podobnych podstron