Wydział Matematyki i Informatyki

UWM w Olsztynie

Ćwiczenie 4

III rok Informatyki

Technika

cyfrowa

Pracownia

[

BRAMKA NAND TTL

]

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

2

Cel ćwiczenia:

Poznanie zasady działania bramki NAND oraz wyznaczenie jej wybranych charakterystyk

pracy.

Wprowadzenie:

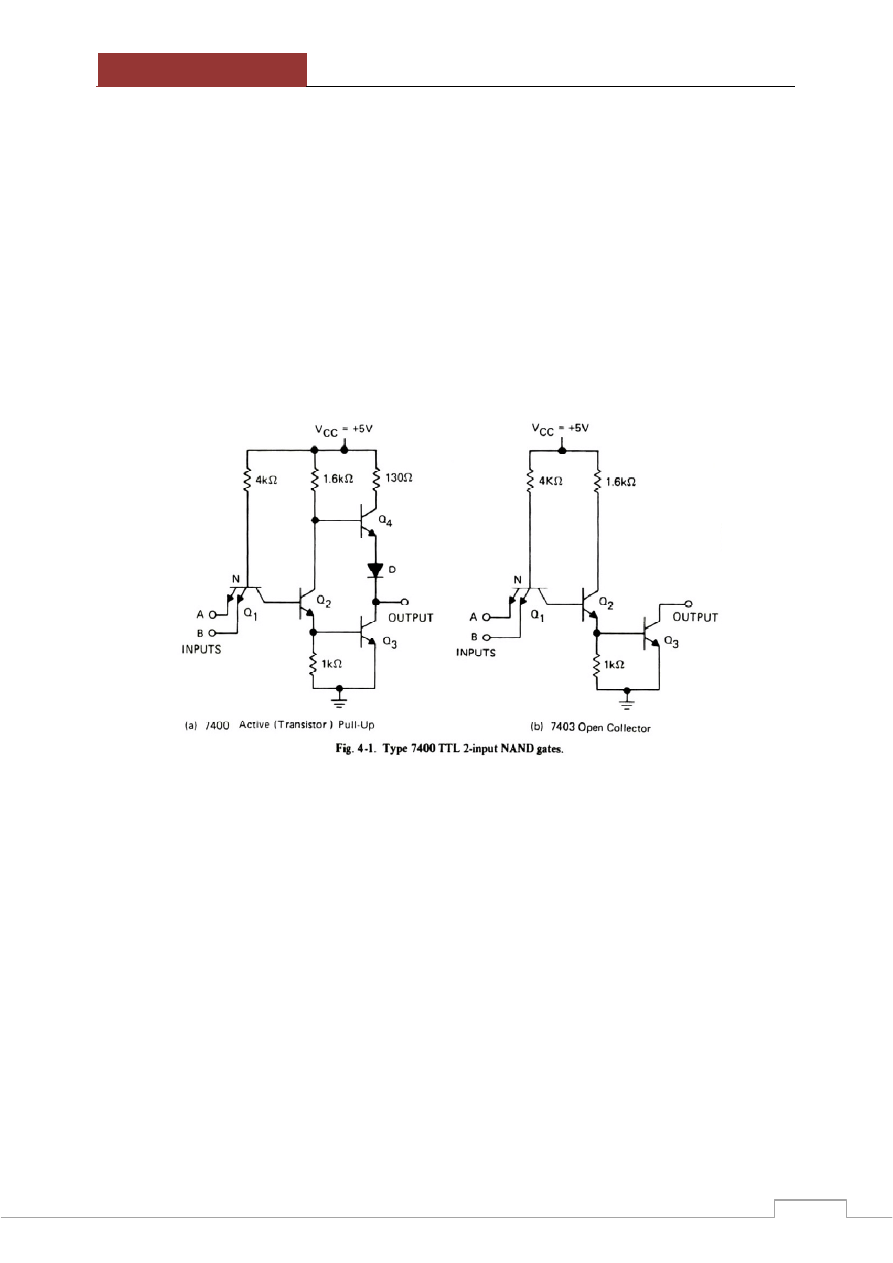

Znajomość wewnętrznej konstrukcji oraz wartości poszczególnych komponentów wewnątrz

bramki nie jest niezbędna, by móc z nich korzystać. Bardzo często cyfrowe układy scalone

traktowane są jako czarne pudełka realizujące określone funkcje logiczne. Rysunek 4-1

przedstawia dwa typy dwuwejściowych bramek NAND wykonanych w technologii TTL

(Transistor-Transistor Logic): (a) standardowa z aktywnym wyjściem (7400), (b) z otwartym

kolektorem (7403).

Działanie standardowej bramki NAND można wyjaśnić w następujący sposób. Jeśli do

którekolwiek z wejść A lub B jest dołączone napięcie mniejsze niż ok. 0.7 V, to złącze baza-

emiter tranzystora wieloemiterowego Q1 przewodzi i w punkcie N ustala się napięcie ok.

0.7 V, co nie wystarcza do wysterowania tranzystorów Q2 oraz Q3. W takiej sytuacji

przewodzi tranzystor Q4, który pracuje jako wtórnik emiterowy i na wyjściu powstaje

napięcie o ok. 1.4 V niższe od napięcia zasilania (spadek napięcia na diodzie D oraz złączu BE

tranzystora Q4 i pomijając zależny od obciążenia układu niewielki spadek napięcia na

rezystorze 1,6kΩ), czyli ok. 3.6 V. Widać zatem, że niski poziom napięcia na dowolnym

wejściu wytwarza na wyjściu wysoki poziom napięcia.

Sytuacja zmienia się, gdy jedno z wejść jest spolaryzowane napięciem wyższym niż ok. 2.1 V.

Tranzystor Q1 pracuje w trybie inwersyjnym (rola końcówek emitera i kolektora ulega

zamianie), a tranzystory Q2 i Q3 wchodzą w stan nasycenia. Tranzystor Q4 jest odcięty, więc

napięcie wyjściowe bramki wynosi ok. 0.2 V. Dioda D zapewnia odcięcie tranzystora Q4, gdy

Q2 oraz Q3 są w stanie nasycenia.

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

3

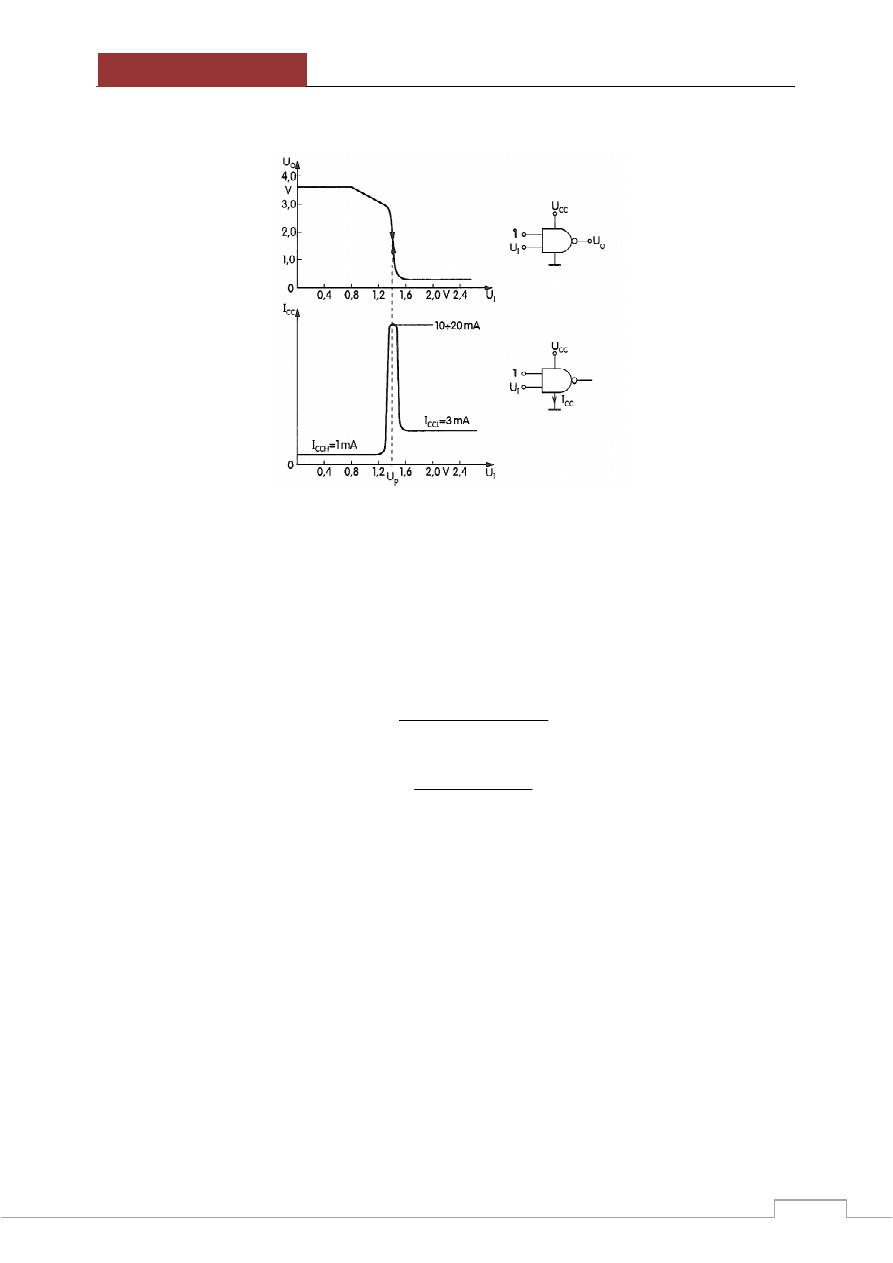

Dwie typowe charakterystyki przełączania bramki NAND przedstawiono na rys. 4-2.

Rys. 4-2. Charakterystyka przełączania bramki NAND (góra) oraz charakterystyka poboru

prądu zasilania podczas przełączania (dół).

Bramka z otwartym kolektorem 7403 (OC – ang. Open Collector) różni się od standardowych

bramek tym, że w jej stopniu wyjściowym znajduje się zwykły inwerter. Gdy wyjście Y

zostanie dołączone do napięcia U

CC

przez dołączany rezystor R

L

, wówczas układ realizuje

funkcję NAND. Wartość rezystora R

L

dobiera się w zależności od liczby dołączonych wejść i

wyjść bramek:

2.6

Lmax

IHmax

OHmax

N I

M

I

R

=

⋅

+

⋅

min

4.6

L

OLmax

ILmax

I

N I

R

=

−

⋅

Gdzie: N – liczba wejść dołączonych bramek, M – liczba wyjść dołączonych bramek, I

I

– prąd

wejściowy bramki, I

O

– prąd wyjściowy bramki.

Jedną z zalet bramek z otwartym kolektorem jest możliwość łączenia ze sobą ich wyjść. Z

bramkami standardowymi nie wolno tak postępować. Bramki z otwartym kolektorem

oznacza się kółeczkiem umiejscowionym wewnątrz podstawowego symbolu bramki.

Istotnym parametrem układu scalonego jest jego odporność na zakłócenia, określona dla

każdego stanu logicznego na wejściu. Wartość odporności na zakłócenia w określonym stanie

na wejściu to maksymalna amplituda sygnału, która oddziałując na to wejście nie spowoduje

niepożądanej zmiany stanu wyjściowego.

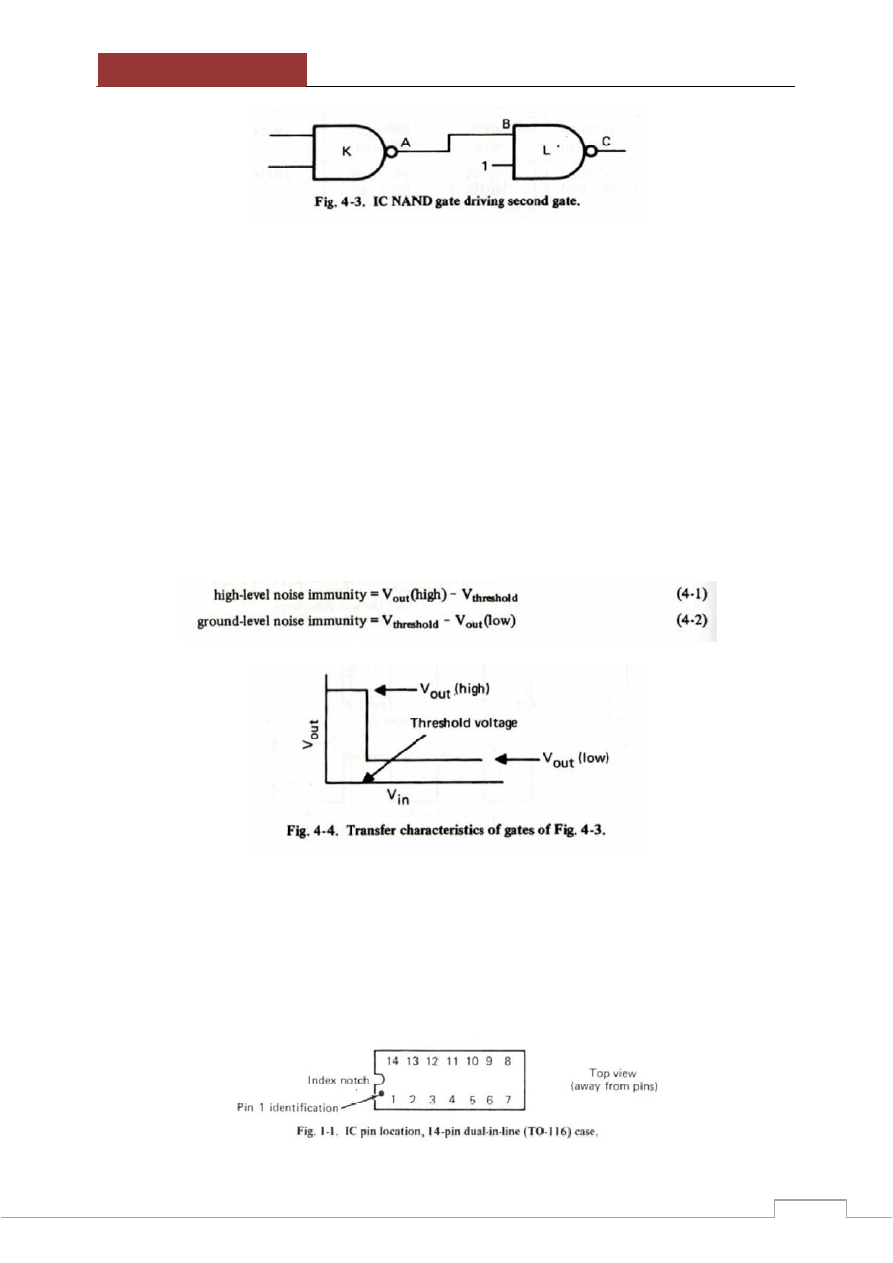

Rozważmy przypadek w którym bramka K steruje bramką L, obie należą do tej samej rodziny

układów logicznych (Rys. 4-3).

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

4

Zakładamy, że na wyjściu bramki K tj. w pkt. A mamy stan 1, to spowoduje, że na wyjściu

bramki L, w pkt. C pojawi się stan 0. Oczekujemy, że szum w formie (1)

elektromagnetycznego sprzężenia ‘’wire AB” lub (2) elektrostatycznego zmieni napięcie na

wejściu B. Jak duża zmiana napięcia może być tolerowana przez bramkę L zanim wpłynie na

jej działanie? Napięcie w pkt. B może zmienić się w chwili, gdy bramka L zmieni swój stan

logiczny. Jednak najpierw należy ustalić wartość napięcia wejściowego, przy którym bramka

zmienia swój stan od jednego do drugiego poziomu logicznego, wartość tą nazwiemy

wartością progową napięcia (Threshold voltage). Podobny czynnik musi być rozważony

kiedy na wyjściu bramki K (pkt. A) jest niskie napięcie (logiczne 0), w tym przypadku

najmniejszy wzrost napięcia powyżej wartości progowej spowoduje na wyjściu bramki L

niepożądaną zmianę. Rysunek 4-4 przedstawia charakterystykę przejściową obu bramek z

zaznaczoną wartością progową napięcia. Charakterystyka ta pozwala wyznaczyć odporność

na szumy, która wyraża się następującymi wyrażeniami:

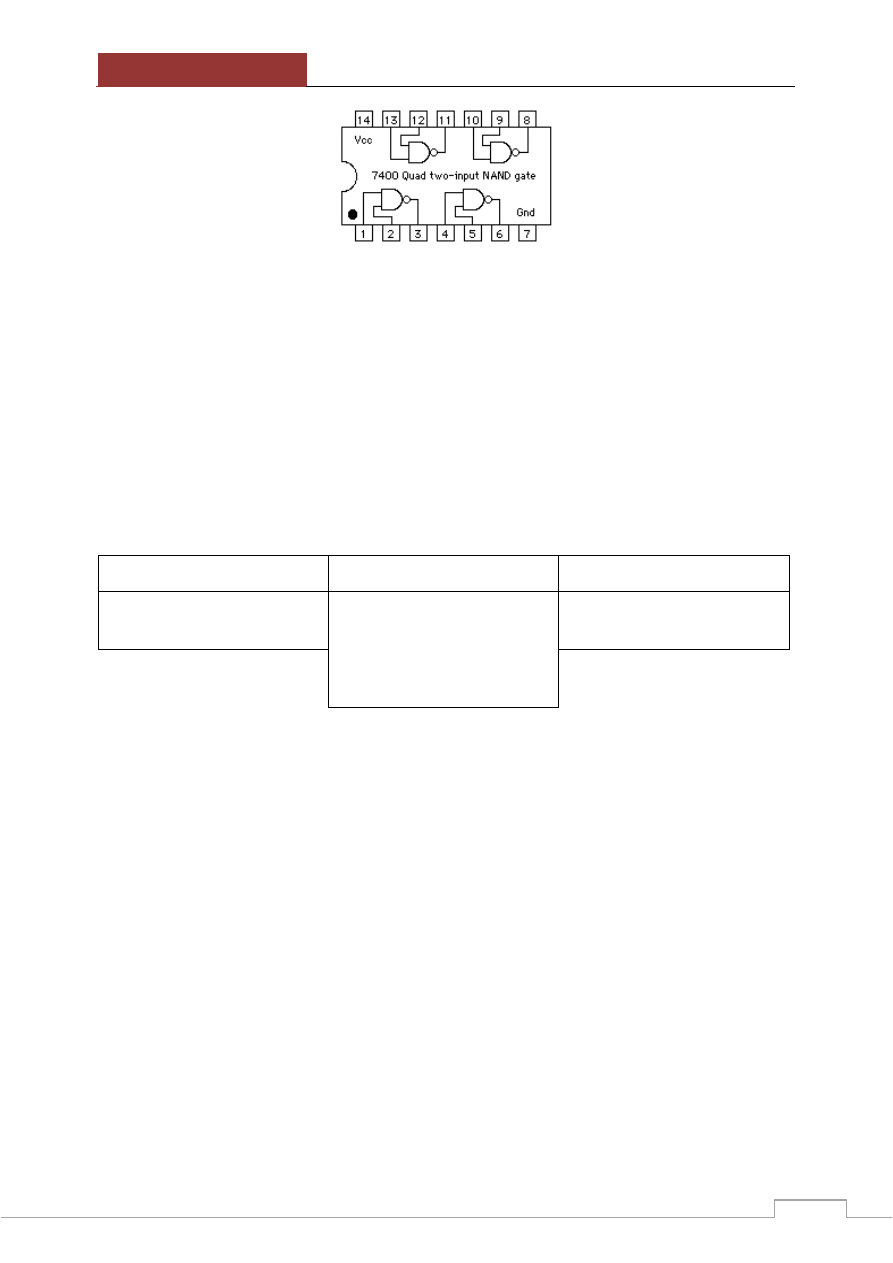

UWAGA:

Używane w ćwiczeniu układy scalone wykonane są w technologii TTL, zasilane są napięciem

stałym +5V (pin 14), działają w logice dodatniej tj. sygnał TTL jest niski (logiczne 0 lub L), gdy

potencjał ma wartość od 0 V do 0,8 V w odniesieniu do masy (pin 7), wysoki (logiczna 1 lub

H) przy wartości potencjału między 2 V a 5 V.

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

5

UCY 7400

POMIARY i DYSKUSJA WYNIKÓW

OPIS ĆWICZENIA

Zadanie 1

Charakterystyka przejściowa i poboru prądu bramki NAND

Charakterystyka przejściowa jest krzywą przedstawiającą wykres napięcia wyjściowego

(U

OUT

) w funkcji napięcia wejściowego (U

IN

). Ze względu na charakter krzywej pomiary należy

wykonywać bardzo dokładnie i z możliwe małym krokiem pomiarowym (0.05 - 0.1 V), tak by

otrzymać jak najwięcej punktów pomiarowych w obszarze, w którym następuje zmiana stanu

logicznego bramki – patrz rys. 4-2.

Charakterystyka poboru prądu jest krzywą przedstawiającą zmiany natężenia prądu

pobieranego ze źródła zasilania (I

CC

) w funkcji napięcia wejściowego (U

IN

).

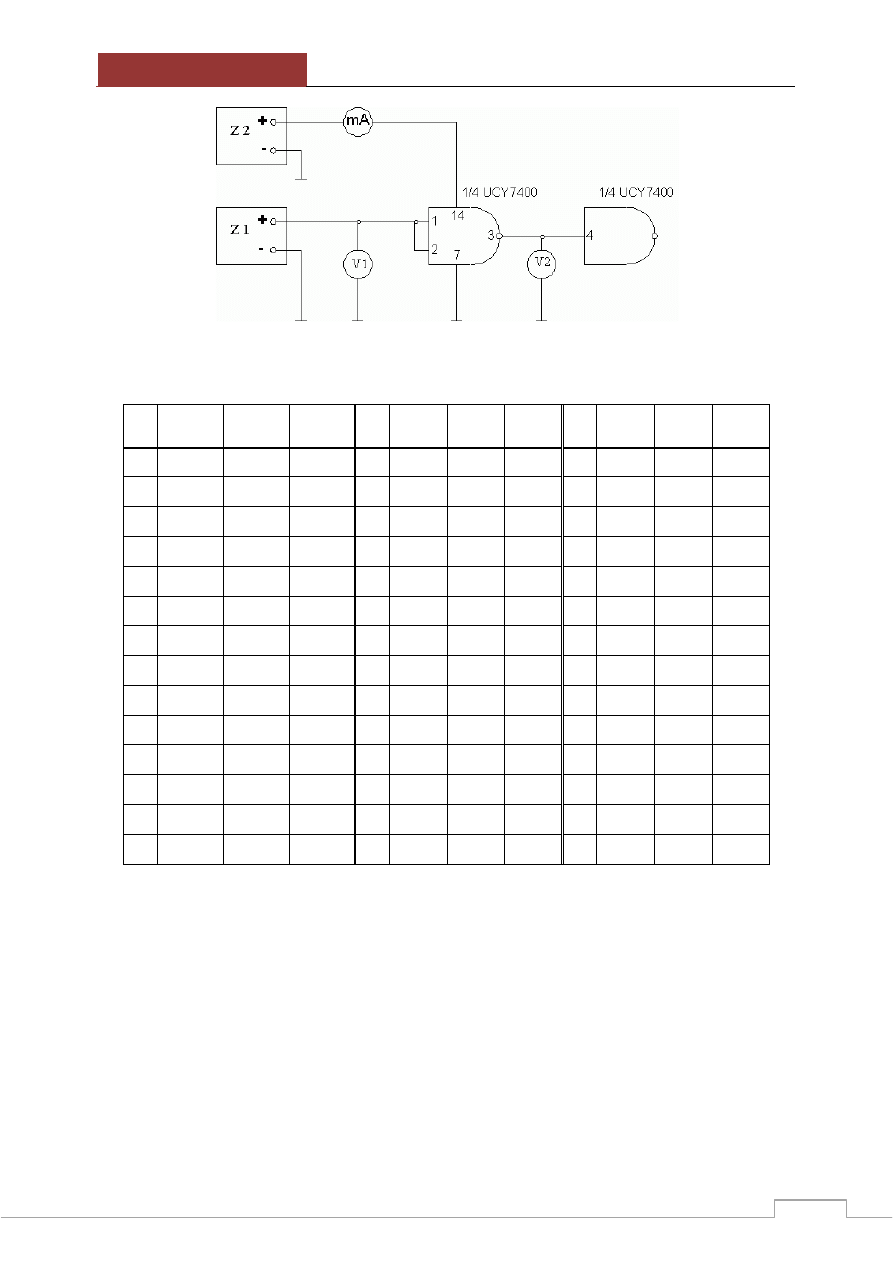

Układ pomiarowy obu charakterystyk przedstawia rys. 4-5.

Imię i Nazwisko

Data

Ocena

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

6

Rys. 4-5. Schemat układu do badania charakterystyk bramki NAND TTL.

Tabela pomiarowa:

U

IN

[V]

U

OUT

[V]

I

CC

[mA]

U

IN

[V]

U

OUT

[V]

I

CC

[mA]

U

IN

[V]

U

OUT

[V]

I

CC

[mA]

1

15

29

2

16

30

3

17

31

4

18

32

5

19

33

6

20

34

7

21

35

8

22

36

9

23

37

10

24

38

11

25

39

12

26

40

13

27

41

14

28

42

DYSKUSJA WYNIKÓW

Na podstawie danych z tabeli pomiarowej należy sporządzić charakterystykę przejściową

bramki NAND (wkleić wykres na papierze milimetrowym lub wydruku komputerowym):

Ćwiczenie nr 4

[

BRAMKI TTL: NAND

]

7

Charakterystyka poboru prądu bramki NAND:

Na podstawie sporządzonych wykresów proszę odczytać:

1) maksymalne napięcie wejściowe w stanie niskim U

ILmax

:

2) minimalne napięcie wejściowe w stanie wysokim U

IHmin

:

3) maksymalne napięcie wyjściowe w stanie niskim U

OLmax

:

4) minimalne napięcie wyjściowe w stanie wysokim U

OHmin

:

5) Maksymalny prąd zasilania I

CCmax

:

6) Maksymalną moc pobieraną z zasilania P

max

:

Wyszukiwarka

Podobne podstrony:

Cwiczenie nr 04 Uklady dyspersy Nieznany

Cwiczenia nr 10 (z 14) id 98678 Nieznany

Cwiczenia nr 13 RPiS id 124686 Nieznany

Cwiczenia nr 13 (z 14) id 98681 Nieznany

Cwiczenia nr 10 RPiS id 124684 Nieznany

Cwiczenia nr 12 (z 14) id 98680 Nieznany

Cwiczenia nr 11 (z 14) id 98679 Nieznany

Cwiczenie nr 4 Telex cz2 id 125 Nieznany

Cwiczenia nr 10 (z 14) id 98678 Nieznany

Cwiczenia nr 13 RPiS id 124686 Nieznany

Cwiczenia nr 13 (z 14) id 98681 Nieznany

Cwiczenie nr 2 Rysowanie precyzyjne id 99901

Laboratorium nr 4 funkcje cd id Nieznany

Cwiczenie nr 6 Polaczenia srubowe id 99945

Finanse publiczne 2006 04 26 id Nieznany

Ćwiczenie nr 04

Cwiczenie nr 4 Modyfikacja elementow id 99934

ĆWICZENIE NR 04 - Skład granulomeryczny gruntu, Mechanika Gruntów

Cwiczenie nr 2 Rysowanie precyzyjne id 99901

więcej podobnych podstron