1

g

1. Sposoby taktowania rdzeni i układów peryferyjnych mikrokontrolerów rodziny Cortex-

Mx.

Rdzen taktowany jest poprzez uklady zegarowe zalezne od danego producenta. Uklady peryferyjne moga

miec swoje oddzielne zegary, z dodatkowymi dzielnikami.

Generalnie pytanie jest malo precyzyjne i powinno dotyczyc raczej konkretnego mikrokontrolera, gdyz

sam rdzen cortex m nie posiada ukladow zegarowych, a jedyne peryferia wbudowane w ten rdzen to

SysTick i kontrolerprzerwan NVIC.

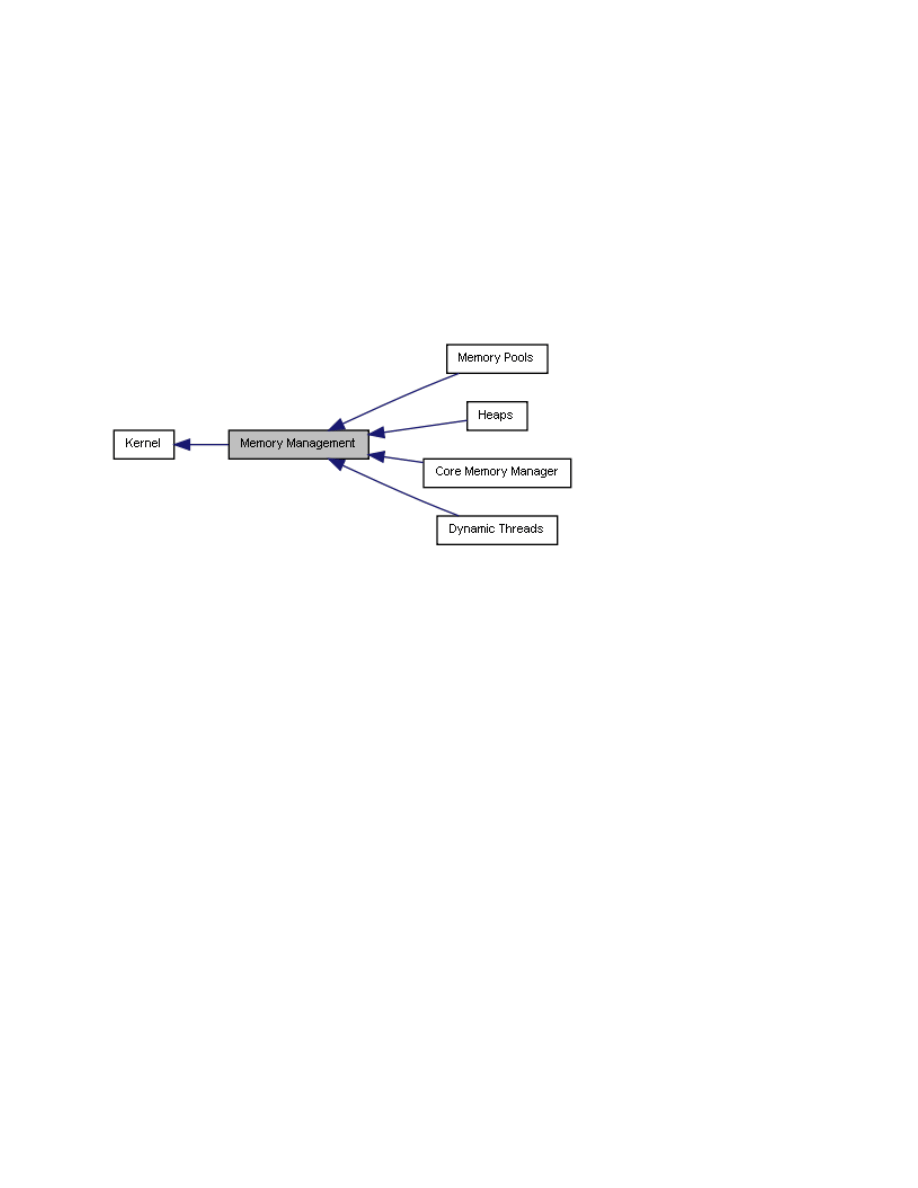

2. Mechanizmy alokacji i

dostępu do zmiennych w mikrokontrolerach rodziny Cortex-Mx.

The core memory manager is a simplified allocator that only allows to allocate memory blocks

without the possibility to free them.

This allocator is meant as a memory blocks provider for the other allocators such as:

● C-Runtime allocator (through a compiler specific adapter module).

By having a centralized memory provider the various allocators can coexist and share the main

memory.

This allocator, alone, is also useful for very simple applications that just require a simple way to get

memory blocks.

The heap allocator implements a first-fit strategy and its APIs are functionally equivalent to the usual

malloc() and free() library functions. The main difference is that the OS heap APIs are guaranteed to

be thread safe.

By enabling the CH_USE_MALLOC_HEAP option the heap manager will use the runtime-provided

malloc() and free() as back end for the heap APIs instead of the system provided allocator.

The Memory Pools APIs allow to allocate/free fixed size objects in constant time and reliably without

memory fragmentation problems.

Memory Pools do not enforce any alignment constraint on the contained object however the objects

must be properly aligned to contain a pointer to void.

3. Dostęp do struktur bitowych (Bit-Banding), zasady adresowania, wady i zalety.

Bit-

band, czyli obszary o dostępie atomowym

Podtytuł z pewnością wymaga wyjaśnienia: co to bowiem znaczy „obszar o dostępie atomowym”? Kiedyś

uważano, że atom jest najmniejszą, niepodzielną cząstką materii. Rozwój nauki wykazał błędność tego

2

założenia, ale w celu wytłumaczenia określenia dostęp atomowy, trzymajmy się starszej wersji poglądu

na temat budowy materii.

Analogią do atomu w systemach cyfrowych jest bit. Po tym porównaniu łatwo już zrozumieć istotę

obszarów o dostępie atomowym. Są to obszary pamięci, gdzie jest możliwy dostęp do pojedynczych

bitów, a nie jak to jest zazwyczaj do całych bajtów.

W przestrzeni adresowej rdzenia Cortex M3 znajdują się dwa obszary bit-band. Pierwszy w regionie

pamięci RAM, a drugi w regionie urządzeń peryferyjnych.Dla pamięci RAM obszar, w którym jest możliwy

dostęp atomowy rozpoczyna się od adresu 0x20000000, natomiast dla urządzeń peryferyjnych jest to

adres 0x40000000. Pomysł obszarów bit-band jest efektem dążenia do maksymalnej optymalizacji pracy

rdzenia. Często zdarza się, że aplikacja musi zmienić stan tylko jednego bitu w danym miejscu w pamięci.

Standardowo odbywa się to za pomocą trzech elementarnych operacji:

– odczytu komórki pamięci do rejestru,

– ustawienia interesującego bitu,

– przepisania zmodyfikowanej wartości z rejestru do komórki pamięci.

<-

wyjęte z kontekstu i w tym

przypadku błędne bo bit-banding właśnie tak nie działa, pozdrawiam

TO MOŻE NAPISZ JAK DZIAŁA <- lubie to

-

po prostu wpisuje pojedynczy bit, bez odczytu i operacji logicznych, tak jak to jest napisane powyżej ;D w

całym kontekście te 3 punkty dotyczyły zamiany bitu BEZ bit-bandingu

Podoba mi się to tłumaczenie, łopatologiczne

Zazwyczaj pamięć w systemach cyfrowych jest podzielona na komórki o pojemności

8 bitów. Każda z komórek ma określony adres, dzięki któremu można jednoznacznie

określić, do której z nich chcemy się odwołać. Taka organizacja nie pozwala jednak

uzyskać dostępu bezpośrednio do pojedynczych bitów słowa danych. By móc

zmodyfikować wartość pojedynczego bitu, należy odczytać zawartość całej komórki

pamięci, zmienić wartość interesującego nas bitu i ponownie zapisać w pamięci całe

słowo. Rozwiązaniem ułatwiającym operowanie na pojedynczych bitach są obszary

bit-

band, w których każdy bit ma swój własny adres. Jest to szczególnie ważne

i przydatne w systemach zbudowanych z wykorzystaniem mikrokontrolerów, gdyż

tego typu operacje są tam bardzo częste. Oprócz dostępu bitowego, do obszarów bit-

-band

można się oczywiście odwołać także według normalnych zasad adresowania.

Wyjaśnienia wymaga jeszcze sposób adresowania bitów w obszarze o dostępie atomowym.

W tym celu stosuje się następujący wzór:

adres_bitu = poczatek_obszaru_bitband + przesuniecie_bajtu×32 + numer_bitu× 4,

1.3. Architektura rdzenia ARM Cortex-M3 19

gdzie:

adres_bitu

– adres, pod jakim należy zapisywać i spod którego

można odczytywać bit,

poczatek_obszaru_bitband

– 0x20000000 dla obszaru bit-band w pamięci SRAM

oraz 0x40000000 dla obszaru bit-band w segmencie

urządzeń peryferyjnych,

przesuniecie_bajtu

– przesuniecie (offset) w stosunku do początku regionu

bit-band,

numer_bitu

– pozycja bitu w słowie, do którego chcemy uzyskać

3

dostęp.

Na przykład, jeśli chcemy ustawić bit 6 komórki o adresie 0x2000001 (offset = 1),

to zgodnie z przedstawionym wzorem, powinniśmy dokonać zapisu nowej wartości

bitu pod adresem 0x22000038:

adres_bitu = 0x22000000 + 0x01 × 0x20 + 0x06 × 0x04 = 0x22000038.

W

zrozumieniu powyższych zależności pomocny może być także rysunek 1.5.

Przeglądając mapę pamięci warto zwrócić uwagę, że zawiera one nie tylko adresy

typowych obszarów pamięci, ale również obszar adresów przeznaczony dla urządzeń

peryferyjnych. W obszarze t

ym znajdują się rejestry danych i rejestry sterujące

poszczególnych układów peryferyjnych mikrokontrolera. Na przykład w zakresie

adresów od 0x40010800 do 0x40010BFF znajdują się rejestry portu GPIOA,

a w obszarze od 0x40005400 do 0x400057FF

– rejestry układu pierwszego kontrolera

interfejsu I2C. Dzięki takiej organizacji pamięci, dostęp do tych rejestrów jest,

z punktu widzenia programisty, taki sam jak dostęp do dowolnej komórki pamięci.

Jest to więc rozwiązanie bardzo wygodne.

Mikrokontrolery ARM są układami 32-bitowymi. Oznacza to, że podstawową długością

słowa, na jakiej operują, jest słowo 4-bajtowe. Potrafią one, oczywiście,

operować również na słowach 1- i 2-bajtowych. Ponieważ pamięć jest podzielona

na bloki 1-

bajtowe, w przypadku, gdy słowo danych zajmuje więcej niż 1 bajt,

powstaje problem, w jakiej kolejności zapisane są w pamięci kolejne jego bajty.

4. Struktura, przeznaczenie rejestrów mikrokontrolerów rodziny Cortex-Mx.

Rdzeń Cortex-M3 wyposażono w szesnaście rejestrów podstawowych (R0 do R15), przy

czym trzynaście z nich (od R0 do R12) jest rejestrami ogólnego przeznaczenia.

Większość instrukcji 16-bitowych może operować tylko na ośmiu młodszych rejestrach z

zakresu R0 do R7, a tylko niektóre z instrukcji 16-bitowych mogą pracować na rejestrach

„starszych”. Rejestr R13 jest wskaźnikiem stosu. Podzielono go na dwa oddzielne rejestry

bankowane, co oznacza, że w danym momencie jest widoczny tylko jeden. Rejestr R13

składa się z:

–MSP –MainStackPointer– domyślnego rejestru używanego przez przerwania i jądra

systemów operacyjnych, pracujących w trybie uprzywilejowanym,

–PSP –ProcessStackPointer– używanego przez program użytkownika uruchomionym „pod

skrzydłami” systemu operacyjnego.

Pozostałe rejestry: R14 – tzw.LinkRegister – zawiera w sobie adres powrotu,

a R15 – licznik rozkazów – zawiera adres aktualnie wykonywanej instrukcji. Może być

zapisywany w celu sterowania wykonywaniem programu.

Oprócz wyżej wymienionych rejestrów rdzenie Cortex-M3 wyposażono także

w rejestry specjalne:Program Status Register, Interrupt Mask Register, Control Register.

Służą one do sterowania pracą rdzenia i sposobem wykonywania programu, a ich zawartość

może być modyfikowana tylko za pomocą instrukcji specjalnych, nie mogą być

modyfikowane podczas normalnej pracy rdzenia.

5. Tryby pracy mikrokontrolerów rodziny Cortex-Mx.

– tryb uprzywilejowany,

4

– tryb użytkownika

Po zerowaniu jednostka centralna zawsze uruchamia się w trybie uprzywilejowanym, a do

jego zmiany służy najmłodszy bit rejestru specjalnego CONTROL. Praca w tym trybie

umożliwia nieograniczony dostęp do zasobów rdzenia. Gdy program jest wykonywany w

trybie użytkownika, niektóre zasoby rdzenia nie są dostępne, dzięki czemu aplikacja

użytkownika nie ma dostępu do kluczowych – ze względu na niezawodność – elementów

systemu, takich jak m.in. niektóre obszary pamięci.

6. Struktura plików: StartUp.s oraz LPC11xx.h.

LPC11xx.h:

Zawiera definicje struktur i symboli:

-

rejestrów i pól bitowych

-

adresy i ID peryferiów

-

definicje portów PIO

-

nr przerwań itd.

Dostarczone przez producenta procesora (nie projektanta rdzenia!)

Opis z komentarzy pliku LPC11xx.h

StartUP.s

UWAGA

Potrzebna pomoc w t

łumaczeniu

-

definicje przerwań i wektory przerwań

-

konfiguracja źródła zegara

-

konfiguracja zewnętrznego kontrolera magistrali

-

inicjalizacja peryferiów niższych poziomów

- rezerwacja miejsca i inicjalizacja stosu

- Reserves the heap. (?) znowu stos? sterta...

-przechowuje wektory ROM-

> Ram dla systemów z remapowaniem pamięci (?)

-

kontrola przesyłu do funkcji main.c (?)

Link:

http://www.keil.com/support/man/docs/gsac/gsac_strtupcodearm7.htm

Plik dostarczony przez ARM

7. Instrukcje blokowe (If-

Then) mikrokontrolerów rodziny Cortex-Mx, funkcje (intrinsic)

kompilatora środowiska µVision.

Intrinsic:

● __enable_fiq

● __disable_fiq

● __nop

● __wfi

● __wfe

● __sev

● __isb(0)

● __dsb(0)

● __dmb(0)

5

● __rev

8. Adresowanie układów peryferyjnych mikrokontrolerów.

Przestrzeń adresowa układów peryferyjnych rodziny Cortex-Mx wynosi 0.5 GB

adresy od 0x40000000 do 0x5FFFFFFF

9. Deklaracje struktur układów peryferyjnych w pliku LPC11xx.h na przykładzie GPIO.

typedef struct

{

union {

__IO uint32_t MASKED_ACCESS[4096]; /*!< Offset: 0x0000 (R/W) Port data Register for

pins PIOn_0 to PIOn_11 */

struct {

uint32_t RESERVED0[4095];

__IO uint32_t DATA; /*!< Offset: 0x3FFC (R/W) Port data Register */

};

};

uint32_t RESERVED1[4096];

__IO uint32_t DIR; /*!< Offset: 0x8000 (R/W) Data direction Register */

__IO uint32_t IS; /*!< Offset: 0x8004 (R/W) Interrupt sense Register */

__IO uint32_t IBE; /*!< Offset: 0x8008 (R/W) Interrupt both edges Register */

__IO uint32_t IEV; /*!< Offset: 0x800C (R/W) Interrupt event Register */

__IO uint32_t IE; /*!< Offset: 0x8010 (R/W) Interrupt mask Register */

__I uint32_t RIS; /*!< Offset: 0x8014 (R/ ) Raw interrupt status Register */

__I uint32_t MIS; /*!< Offset: 0x8018 (R/ ) Masked interrupt status Register */

__O uint32_t IC; /*!< Offset: 0x801C ( /W) Interrupt clear Register */

} LPC_GPIO_TypeDef;

10. Struktura i programowanie rejestrów portów GPIO, bitowe adresowanie (maskowanie)

portów.

11. Liczniki mikrokontrolera (LPC1114)

– implementacja sprzętowa, zasady

programowania, spr

zętowe generowanie impulsów.

12. Modulacja szerokości impulsów (PWM/PDM) w mikrokontrolerach rodziny Cortex-Mx.

LPC_SYSCON->SYSAHBCLKCTRL |= (1<<16);

// IOCON clock enable

LPC_IOCON->R_PIO0_11 = 3;

// R_PIO0_11 MAT2 B0

LPC_SYSCON->SYSAHBCLKCTRL |= (1<<9);

// Timer32B0 clock enable

LPC_TMR32B0->PR

= 48000-1;

// Timer32B0 clock = 100 kHz

LPC_TMR32B0->MCR = (1<<4);

// Reset on MR1: the TC will be reset if MR1 matches it.

LPC_TMR32B0->EMR |= (3<<10);

// Toggle MR3

6

LPC_TMR32B0->PWMC = 3;

//set channel 3 to PWM mode

LPC_TMR32B0->MR3 = 1;

//set duty

LPC_TMR32B0->MR1 = 18;

//set value for period

LPC_TMR32B0->TCR = 2;

// Reset prescaler and Timer32B0

LPC_TMR32B0->TCR = 1;

// enable Timer32B0

13. Bezszczotkowe sil

niki prądu stałego (BLDC motors) – zasada działania i sterowania,

problemy przełączania napięć/prądów sterujących (dead time).

Urządzenie to składa się z wirnika z magnesami stałymi oraz stojana z uzwojeniami. Uzwojenia

stojana mogą być połączone w układzie trójkąta lub gwiazdy. Moment obrotowy powstaje w

wyniku oddziaływania pól magnetycznych wytwarzanych przez te komponenty. Aby uzyskać

większy moment obrotowy, na wirniku montuje się magnesy ziem rzadkich, na przykład

neodymowe lub samaro-kobaltowe.

Typy sterowania:

a) czujnikowe

-

wykorzystując czujnik Halla, wykrywający konkretny poziom indukcji magnetycznej

wokół czujnika

-

wykorzystując czujniki optyczne umieszczone w dodatkowej ruchomej pokrywie silnika

b) bezczujnikowe

-

wykor

zystując siłe elektromotoryczną

-

wykorzystując pomiary prądów i napięć

-

wykorzystując sterowanie rozmyte i sieci neuronowe

c) sprzętowe

14. Układy szeregowej transmisji danych (RS232, I2C-Bus), protokoły transmisji, zasady

programowania kontrolerów (UART).

15. Struktura, zasady programowania wyjątków i przerwań, sprzętowa i programowa

obsługa wyjątków i przerwań.

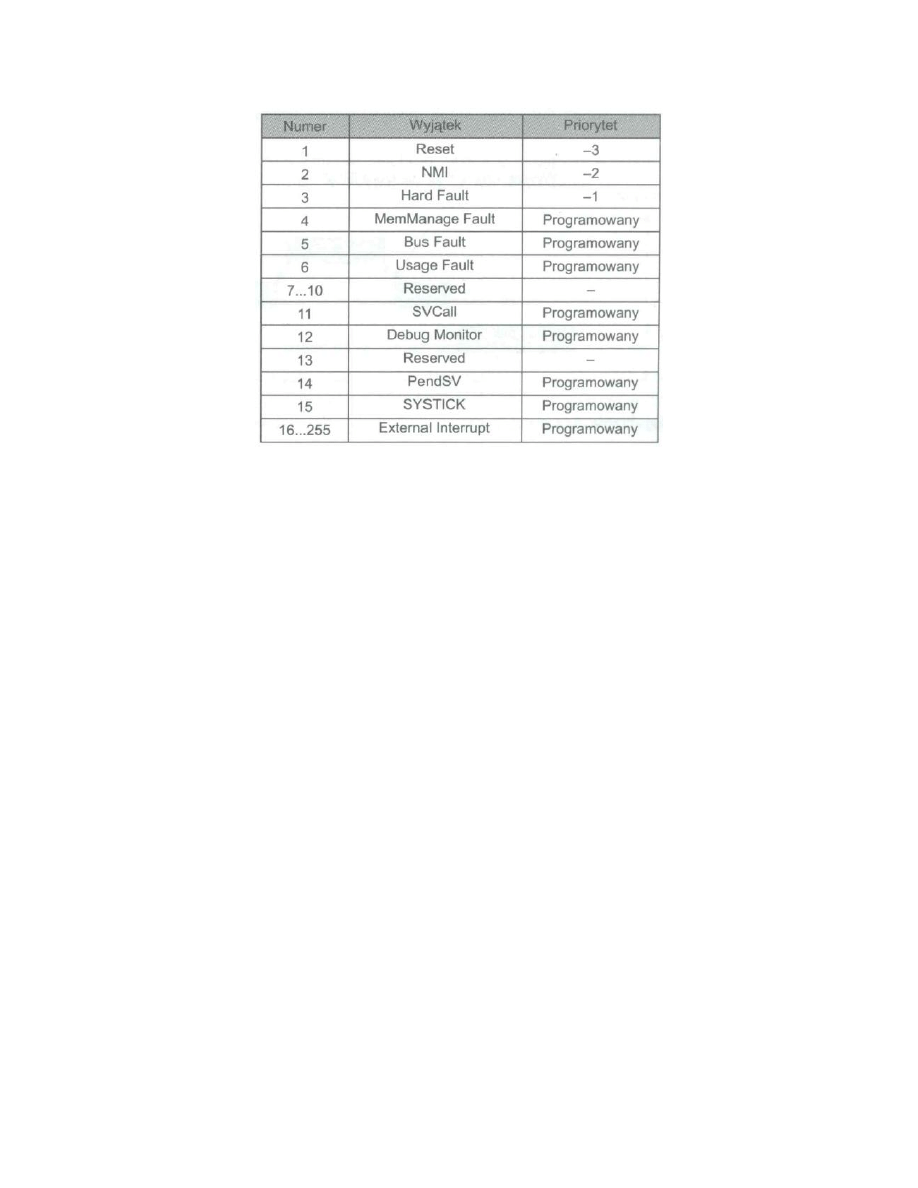

Struktura:

7

Zasady programowania:

Warto korzystać z kontrolera do obsługi przerwań NVIC, ponieważ:

-

upraszcza obsluge przerwań

-

skraca opóźnienia w obsłudze przerwań

-

umożliwia obsłuę przerwań zagnieżdżonych poprzez nadanie przerwaniom priorytom*

-

możliwe sa dynamiczne zmiany priorytetów przerwań nawet w trakcie pracy

mikrokontorlera

-

daje możliwość maskowania przerwań

*mamy (w Rdzeniu Cortex-

M3) do 15 przerwań(wyjątków) systemowych i do 240 przerwan

zewnetrzych (ile faktycznie to zalezy od fizycznego układu). Na uwagę zasługują 3 pierwsze

wyjatki, ponieważ nie są programolne, czyli nie można zmieniać ich priorytetów! (Są

najważniejsze w systemie).

sprzetowa i programowa obsluga przerwan:

Programowe:

kiedy mikrokontroler wykryje przerwanie ustawia bit przyjęcia przerwania (pending bit) oznacza

to ze aby wywołać programowo przerwanie wystarczy ten bit ustawić na 1, Mozna tego dokonac

zapisując do rejestru STIR(Software Trigger Interupt Register) numer interesujacego

przerwania. Wykorzystujac biblioteki firmy ST w celu programowego wygenerwoania przerwania

nalezy uzyc funcji NVIC_SetPendingIRQ().

16. Tryby redukcji mocy w mikrokontrolerach rodziny Cortex-Mx.

Tryb uśpienia (Sleep mode) - w trybie tym tylko procesor zostaje zatrzymany. Wszystkie

urządzenia kontynują operacje i mogą obudzić procesor za pomocą przerwania.

8

Tryb pracy niskiego poboru mocy (Low power run mode) - RC oscylator ustawiony na

minimalny zegar 65 kHz, wykonany z SRAM lub pamięcią Flash oraz wewnętrzny regulator jest

ustawiony w tryb niskiego poboru mocy by zminimalizować prąd pracy regulatora. W trybie tym

częśtotliwość zegara oraz liczba włączonych peryferiów jest ograniczona.

Tryb uśpienia niskiego poboru mocy (Low power sleep mode) - tryb ten osiąga się poprzez

wejście w tryb uśpienia z wewnętrznym regulatorem napięć ustawionym w tryb oszczędzania

energii aby zminimalizować prąd pracy regulatora. W trybie tym częstotliwość zegara i liczba

włączonych peryferii jest ograniczona. Wyzwalany jest przez zdarzenie lub przerwanie.

Tryb zatrzymania z włączonym zegarem czasu rzeczywistego (Stop mode with RTC) - tryb

ten osiąga najniższe zużycie mocy przy jednoczesnym zachowaniu pamięci RAM oraz

zawartości rejestru. Wewnętrzny regulator napięcia jest wyłączony. PLL, MSI RC, HSI RC i HSE

oscylator są wyłączone. LSE i LSI są włączone. Urządzenie może się obudzić z trybu

zatrzymania przez którąkolwiek z linii EXTI.

Tryb zatrzymania z wyłączonym zegarem czasu rzeczywistego (Stop mode without RTC) -

właściwie to to samo co wyżej :)

Tryb gotowości z włączonym zegarem czasu rzeczywistego (Standby mode with RTC) -

służy do osiągnięcia najniższego zużycia energii. Wewnętrzny regulator napięcia jest

wyłączony. PLL, MSI RC, HSI RC i HSE oscylator są wyłączone. LSE i LSI są włączone. Po

przejściu w ten tryb zawartość pamięci RAM i rejestrów jest tracona z wyjątkiem rejestrów

IWDG, RTC, LSI, LSE oscylator, RCC_CSR. Budzi się za pomocą zewnętrznego resetu(NRST

pin) zboczem narastajacym na jednym z trzech WKUP pins.

Tryb gotowości z wyłączonym zegarem czasu rzeczywistego (Standby mode without RTC)

-

to co powyżej :)

17. Standard AAPCS

– specyfikacja, wady i zalety.

AAPCS definuje w jaki sposób podprogramy mogą być pisane oddzielnie, oddzielnie

kompilowane cz

y asemblowane tak by mogły pracować wspólnie. Opisuje oddziaływania

poleceń programu wywołującego oraz wywoływanego:

-

wzywający program określa w kodzie kiedy wywoływany program zaczyna działać

-

wywoływany program dba o możliwość powrotu do porzedniego podprogramu w odpowiedniej

lini kodu

-

wywoływany program musi mię prawo do zmian w poprzednim podprogramie

http://infocenter.arm.com/help/topic/com.arm.doc.ihi0042e/IHI0042E_aapcs.pdf

AAPCS is the ARM Architecture Procedure Calling Standard. It is a convention which allows high level

languages to interwork.

9

Rn

Name

Usage under AAPCS

R0..3

A1..4

Argument registers. These hold the first four function arguments on a function call

and the return value on a function return. A function may corrupt these registers

and use them as general scratch registers within the function.

R4..8

V1..5

General variable registers. The function must preserve the callee values of these

registers.

R9

V6 SB

General variable register. The function must preserve the callee value of this

register except when compiling for read-write position independence (RWPI). Then

R9 holds the static base address. This is the address of the read-write data.

R10

V7 SL

General variable register. The function must preserve the callee value of this

register except when compiling with stack limit checking. Then R10 holds the stack

limit address.

R11

V8 FP

General variable register. The function must preserve the callee value of this

register except when compiling using a frame pointer. Only old versions of armcc

use a frame pointer.

R12

IP

A general scratch register that the function can corrupt. It is useful as a scratch

register for function veneers or other intra-procedure call requirements.

R13

SP

The stack pointer, pointing to the full descending stack.

R14

LR

The link register. On a function call this holds the return address.

R15

PC

The program counter.

Zgodnie za standardem AAPCS (ARM Architecture Procedure Call Standard) rejestry procesora mają

przypisane konkretne znaczenie,

● Rejestry r0 – r3 (a1-a4) przeznaczone są do przekazywania parametrów do procedur lub

zwracania rezultatów funkcji (wartości mogą być również przekazywane przez stos).

● Rejestry r4-r8, r10, r11 przeznaczone są do przechowywania zmiennych lokalnych procedur,

● Rejestry r12-r15 mają zawsze przypisane specjalne przeznaczenie: IP, SP, LR, PC.

● Stos powinien być wyrównany do granicy 8 bajtów.

10

18. Standard CMSIS

– specyfikacja, zastosowania.

Standard CMSIS jest to uniwersalny interfejs programowy, stworzony przez firmę ARM, który

umożliwia komunikację w peryferiami i rdzeniem Cortex za pomocą ustandaryzowanych funkcji.

CMSIS dostarcza mech

anizmy do obsługi układów peryferyjnych, systemów operacyjnych

czasu rzeczywistego oraz aplikacji wykorzystujących interfejsy komunikacyjne: Ethernet, UART,

SPI. Standard CMSIS został podzielony na dwie podstawowe warstwy: Core Peripheral Access

Layer oraz

Middleware Access Layer. Pierwsza warstwa zawiera definicje nazw oraz umożliwia

dostęp do rejestrów rdzenia oraz urządzeń peryferyjnych, natomiast druga udostępnia

mechanizmy do współpracy z interfejsami komunikacyjnymi. Dodatkowo, wymienione wyżej

warstw

y zostały rozszerzone przez producentów mikrokontrolerów, którzy współpracowali przy

tworzeniu CMSIS, o dwie „warstwy”: Device Peripheral Access Layer oraz Access Functions for

Peripherals.

Literatura

1.

The definitive guide to the ARM Cortex-M3 Joseph Yiu.

2.

Pytania kolokwium:

1.Parametry transmisji UART

2.W jakim celu stosuje się CMSIS/AAPCS

3.Co to jest stacking/unstacking i kiedy się wykorzystuje? (jakoś tak)

4.Opisać dostęp aligned i unaligned

5.Pytanie o SysTick

+1. W jaki spos

ób jest taktowany rdzeń (core) i układy peryferyjne Cortex M?

R

dzen taktowany jest poprzez uklady zegarowe zalezne od danego producenta. Uklady

peryferyjne moga miec

swoje oddzielne zegary, z dodatkowymi dzielnikami.

- Generalnie pytanie jest malo precyzyjne i powinno dotyczyc raczej konkretnego

mikrokontrolera, gdyz sam

rdzen cortex m nie posiada ukladow zegarowych, a jedyne peryferia wbudowane w ten rdzen to

SysTick i

kontroler przerwan NVIC.

2. Co oznacza poj

ęcie „bit-band operation”?

mo

żliwość manipulacji bitami w RAM i peryferiach, np portach Możesz traktować dany pin jak

zmienn

ą (i np.

przekazywa

ć pin jako parametr funkcji), bez używania do tego rejestrów

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/Behcjiic.html

11

3. Jak jest cel wprowadzenia kolejki FIFO w porcie szeregowym LPCxx(CORTEX

M)?

(Przemek) Hmm

… pytanie odnosi się do mikrokontrolera LPCxx, tego co mamy na laborkach

(chyba).

Kolejkowanie FIFO w porcie szeregowym(USART/UART) ma na celu odci

ążyć rdzeń

mikrokontrolera.

Dzi

ęki czemu zapis/odczyt z portu szeregowego odbywa się sprzętowo.

4. Na czym polega arbitra

ż w standardzie I2C-BUS?

W systemie I2CBUS mo

że dojść do sytuacji, że więcej niż jedno urządzenie zechce przejąć

kontrol

ę nad łączem

(by

ć masterem). Zdefiniowano więc specjalną procedurę arbitrażową, która wyłania jednego

mastera spo

śród

urz

ądzeń rywalizujących o sterowanie transmisją. Arbitraż oparto na zasadzie kontroli

zgodno

ści stanu linii

SDA z warto

ścią logiczną bitu wyprowadzanego przez dane urządzenie. Odczyty stanu linii

SDA odbywaj

ą

si

ę w ściśle określonych momentach wyznaczanych sygnałem zegarowym. Trzeba pamiętać, że

podczas ]

arbitra

żu dwa lub więcej urządzenia wyprowadzają swoje bity na linię danych i może się

zdarzy

ć, że gdy

jedno wyprowadza jedynk

ę, to drugie wyprowadza zero. Na linii SDA w takim przypadku ustali

si

ę stan niski,

poniewa

ż dla podłączonych do tej linii urządzeń realizuje ona funkcję „iloczynu na drucie”.

Urz

ądzenie, które

chcia

ło wyprowadzić jedynkę, po stwierdzeniu, że na linii SDA jest zero, wypada z arbitrażu

(wy

łącza swoje

wyj

ście). Widać więc, że przedstawione rozwiązanie preferuje urządzenie, które w czasie

arbitra

żu wysyła

najni

ższa wartość binarną. Dla poprawnego przeprowadzenia arbitrażu konieczna jest

synchronizacja sygna

łów

zegarowych urz

ądzeń, które walczą o sterowanie transmisją. Wszystkie urządzenia generują

swoje w

łasne

sygna

ły zegarowe na linii SCL umożliwiając przesył danych oraz potwierdzenia. Dane na linii

SDA s

ą ważne

tylko dla wysokiego stanu linii zegara. Synchronizacj

ę przesyłu danych uzyskuje się poprzez

wykorzystanie

funkcji

„iloczynu na drucie”, tym razem realizowanej na linii SCL. Linia SCL będzie tak długo w

stanie niskim,

a

ż wszystkie urządzenia nie zwolnią tej linii. Długość stanu wysokiego na linii SCL jest zatem

okre

ślona przez

czas trwania najkr

ótszego okresu spośród sygnałów zegarowych, a długość stanu niskiego

przez czas trwania

najd

łuższego okresu spośród sygnałów zegarowych. Urządzenie master, które utraciło kontrolę

nad magistral

ą,

mo

że generować tylko sygnały zegarowe do końca bajtu, przy którym utraciło kontrolę. Arbitraż

nie jest

dozwolony w trakcie powtarzanego warunku START lub STOP.

5 Jak interpretowa

ć pojęcie „wyjątek” w CortexM

Jest to przerwanie z najwy

ższym możliwym (ujemnym) priorytetem, którego nie można

ustawi

ć programowo. Przykładem takiego przerwania jest HardFault

12

6 Jakie typy przerwa

ń występują w Cortex M i co jest ich źrodlem?

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0497a/BABBGBE

C.html

Exception priorities and preemption

– Lower numbers take higher precedence

– If multiple exceptions have the same priority

number, the pending exception with the lowest

exception number takes precedence.

– Only exceptions with a higher priority (lower

priority number) can preempt an active exception.

7 Jakie jest przeznaczanie i w

łaściwości układu SisTick w Coretx M

SysTick to timer wbudowany w NVIC. 24-bitowy licznik zliczaj

ący w dół odmierza, określone

przez programist

ę,

interwa

ły czasowe. Przejście przez zero powoduje wygenerowanie przerwania (jeśli włączone).

(Przemek) Cz

ęsto wykorzystwany przez sytemy operacyjne do odmierzania czasu.

bez blokowania i bez timeout

’u, więc d

C - j

ądro posiadać musi, cała reszta jest opcjonalna choć scheduler jest potrzebny do systemu

operacyjnego.

a

11.

--------------------------------------------------------------------

(Olek) U=50/150+30/90+40/160=0,917 > 0,779 PORPRAWKA, jest planowalna, po

rozrysowaniu wykresu daje

sie zauwazyc ze grupa jest planowalna

(Ada) To rozrysuj :)

(mateusz)

https://suw.biblos.pk.edu.pl/resources/i5/i9/i9/i4/r5994/JamrozL_SzeregowanieZadan

Cyklicznych.pdf

(W

ładek) Example z wikipedi - Punkt dla Ady

Process Execution

Time

Period

P1 1 8

P2 2 5

P3 2 10

The utilization will be:

The sufficient condition for processes, under which we can conclude that the system is

schedulable is:

Since the system is surely schedulable.

But remember, this condition is not a necessary one. So we cannot say that a system with

higher utilization is not

schedulable with this scheduling algorithm

.

Aczkolwiek po rozrysowaniu potwierdzam,

że planowalna

-----------------------------------------------------------------------------------------------

DODATKOWE PYTANIA Z WYK

ŁADU U DR. PĘKALI (zaznaczył, że większą wagę ma część

St

ępnia ze

wzgl

ędu na ilość godzin)

Zablokowanie tasku wykonuj

ącego wysyłanie komunikatu do kolejki następuje gdy:

- kolejka jest pe

łna

Obiekt j

ądra rywalizujący o czas procesora to:

- task

13

Szeregowanie priorytetowe z wyw

łaszczaniem to:

- podstawowa regu

ła szeregowania

Czas zmiany kontekstu:

- czas za

ładowani tasku… (ktoś kto był na wykładzie mógłby uzupełnić)

Podstawowa regu

ła szeregowania tasków o tym samym priorytecie to:

- algorytm rotacyjny

Priorytet tasku, kt

óry objął… mutex:

- mechanizm zapobiegania inwersji priorytetu

Pytanie z dzisiaj:

Najwa

żniejsze elementy architektury mikrokomputera wykorzystane do budowy usług

czasomierzy:

- programowalny uk

ład PIT (PID to sterownik rozniczujaco całkujacy ;) mateusz)

/// dorzucam cos od siebie ;) /mateusz

CMSIS - Cortex Microcontroller Software Interface Standard

Strategia ARM, polegaj

ąca na ułatwieniu przenoszenia oprogramowania pomiędzy

mikrokontrolerami r

óżnych

producent

ów, opiera się na dwóch elementach: sprzęcie i oprogramowaniu. Od strony

sprz

ętowej w architekturze

Cortex-Mx zintegrowano wi

ęcej bloków zwiększających ich możliwości funkcjonalne niż w

architekturze

wcze

śniejszych rdzeni ARM7. Na przykład układy Cortex-Mx od różnych producentów mają nie

tylko tak

ą

sam

ą część procesorową (CPU), ale także taki sam wektorowy kontroler przerwań z

zagnie

żdżeniami (NVIC –

Nested Vectored Interrupt Controller), taki sam rdze

ń timera systemowego (SysTick) i taki sam

modu

ł logiczny

do wykrywania b

łędów w programie (debugowania).To gwarantuje, że każde oprogramowanie

standardowe

(firmware) b

ędzie miało te same właściwości funkcjonalne po uruchomieniu na wszystkich

mikrokontrolerach

wyposa

żonych w rdzeń Cortex-Mx.

Architektura Cortex M

-Architektura 32-bitowa

-RISC

-mno

żenie 32x32bit

-rozkazy thumb i thumb2

-instrukcje 16 i 32 bitowe

-13-stage pipelining

-sprz

ętowe mnożenie i dzielenie stało i zmiennoprzecinkowe (w zależności od rodzaju cortex’a)

-SysTick Timer

-Bit Banding

-Memory Protection Unit (MPU)

RCC (Reset and Clock Control) to rejestry odpowiedzialne za konfiguracj

ę zegarów (od wyboru

źródła sygnału

zegarowego do konfiguracji cz

ęstotliwości pracy poszczególnych bloków procesora). NVIC

(Nested Vectored

Interrupt Controller) to kontroler przerwa

ń sprzętowych. Odpowiada m.in. za priorytety

przerwa

ń, ich konfigurację,

sterowanie trybami poboru mocy, blokowanie przerwa

ń (to znaczy programista sobie to

dopasowuje pod siebie).

14

SysTick to timer wbudowany w NVIC. 24-bitowy licznik zliczaj

ący w dół odmierza, określone

przez programist

ę,

interwa

ły czasowe. Przejście przez zero powoduje wygenerowanie przerwania (jeśli włączone).

Plik startup:

-tablica wektor

ów przerwan-tablica wektorów jest zbiorem ważnych dla działania programu

adres

ów. Zawiera

adres pocz

ątku stosu, wektor resetu (czyli adres od którego zaczyna się program), także adresy

funkcji obs

ługi

wyj

ątków i adresy funkcji obsługi przerwań.

-Adresy w reprezentacji symbolicznej (wg CMSIS)

-procedury obs

ługi wyjątków (przykładowe procedury)

-procedur obs

ługi przerwań

Taktowanie

-

AHBCLKCTRL odpalamy taktowanie dla poszczeg

ólnych zasobow/peryferiow procka.

-kwarc 12MHz zwielokratniany w petli PLL do 48MHZ (procek z laborek)

-dzielniki o dowolna warto

ść

Wyj

ątki systemowe

trzy wyj

ątki systemowe, dostępne w architekturze Cortex. Docelowym ich zadaniem jest

praca pod kontrol

ą

systemu operacyjnego, aczkolwiek w aplikacjach bez OS r

ównież można je

wykorzysta

ć do zapewnienia większej

kontroli i stabilno

ści pracy.

Do cyklicznego prze

łączania kontekstu zadań stworzono systemowy, 24–bitowy, timer

SysTick. Jego zadaniem

jest generowanie w okre

ślonych odstępach czasu przerwania, a funkcja jego obsługi

mo

że zajmować się właśnie

prze

łączaniem kontekstu zadań.

Wyj

ątek SVC (System serVice Call)

W dobrze zaprojektowanym systemie operacyjnym, uruchomiona w nim aplikacja nie

mo

że bezpośrednio odwołać

si

ę do sprzętu. Odnosząc to zdanie do konkretnego przypadku można powiedzieć, że

aplikacja u

żytkownika nie ma

mo

żliwości operowania na portach wejścia/wyjścia inaczej, niż za pośrednictwem

systemu operacyjnego. Takie

ograniczenia w stosunku do aplikacji uruchamianych w systemie operacyjnym maj

ą

bardzo istotne znaczenie

ze wzgl

ędu na ograniczone zaufanie do programów użytkownika. W związku z tym musi

istnie

ć mechanizm

pozwalaj

ący na bezpieczne korzystanie ze sprzętu przez uruchomiony w systemie

operacyjnym program

u

żytkownika. Do realizacji tego zadania przeznaczono wyjątek SVC.

Je

śli program użytkownika chce skorzystać ze sprzętu, to musi wywołać funkcję SVC, a

dopiero ta realizuje

zadanie z u

życiem wymaganego sprzętu.

Wyj

ątek PendSV

Jak napisano wcze

śniej, w najprostszym systemie operacyjnym, za przełączanie

kontekst

ów uruchomionych

15

zada

ń odpowiada timer SysTick. Podczas pracy takiego systemu może powstać prosty,

cho

ć nie zawsze oczywisty

problem.

Podczas realizacji zadanie (program u

żytkownika) może zostać zgłoszone przerwanie,

kt

óre wywłaszczy

dotychczasowy proces. Je

śli podczas obsługi zgłoszonego przerwania timer SysTick

przerwie je i system

operacyjny rozpocznie prze

łączanie kontekstów zadań, to wychodząc z funkcji obsługi

przerwania od timera

SysTick, OS b

ędzie próbował zmusić mikrokontroler do rozpoczęcia realizacji nowego

zadania. Jest to rzecz jasna

zachowanie b

łędne, ponieważ obsługa pierwszego przerwania zostanie znacznie

op

óźniona.

Rozwi

ązaniem tego problemu jest zastosowanie wyjątku PendSV. Jego programowalny

priorytet jest ustawiany na

najni

ższy możliwy, dzięki czemu przerwanie to nigdy nie wywłaszczy innych

obs

ługiwanych przerwań.

Przeanalizujmy teraz zachowanie systemu z zaimplementowan

ą obsługą PendSV.

Za

łóżmy, że zadanie

realizowane w systemie nie ma aktualnie nic do zrobienia. Generuje wyj

ątek SVC,

kt

órego zadaniem jest

przygotowanie do prze

łączenia kontekstu zadań i wywołanie przerwania PendSV.

Dopiero to ostatnie przerwanie

wykonuje w

łaściwe przełączenie kontekstów tak, że gdy mikrokontroler powraca do

normalnego wykonywania

programu, to w

ówczas podejmowane już jest wykonywanie następnego zadania.

Je

śli w trakcie przełączania kontekstów zadań w funkcji obsługi przerwania PendSV

system zarejestruje inne

przerwanie, to prze

łączanie kontekstów zostaje wstrzymane przez wywłaszczenie

PendSV (pami

ętajmy, że jego

priorytet jest najni

ższy).

PendSV i SysTick

Podobnie ma si

ę sprawa wtedy, gdy system operacyjny przygotowuje przełączanie kontekstów

zada

ń przy

pomocy przerwania od timera SysTick. W takiej sytuacji, zak

ładając, że przerwanie od SysTick

ma wysoki

priorytet, a chwil

ę wcześniej był obsługiwany jakiś inny wyjątek, nastąpi wywłaszczenie tego

ostatniego na rzecz

SysTick.

W zwi

ązku z tym, że obsługa wywłaszczonego przerwania jest zdecydowanie ważniejsza od

wykonywania

uruchomionych w systemie zada

ń, to funkcja obsługi przerwania od timera SysTick (podobnie

jak SVC) tylko

przygotowuje system do prze

łączenia kontekstu zadań i generuje wyjątek PendSV. Teraz, skoro

PendSV ma

najni

ższy priorytet, mikrokontroler wraca do obsługi wywłaszczonego wcześniej przerwania.

Gdy czynno

ści

16

obs

ługi przerwania zostaną zakończone, to oczekujący wyjątek PendSV zaczyna być

realizowany, konsekwencj

ą

czego jest prze

łączenie kontekstu i rozpoczęcie obsługi kolejnego zadania uruchomionego w

systemie

Na czym polega 'Unaligned Word Data Transfer' w procesorach Cortex-M3?

Tradycyjnie, procesory ARM (takie jak ARM7/ARM9/ARM10) pozwalaj

ą jedynie na transfer

wyr

ównany (aligned

transfer).Przekazywanie s

łowa muszą mieć adres bitu[1] i bitu [0] równe 0 - dane mogą być

zlokalizowane w

0x1000 lub 0x1004, ale nie mog

ą być usytuowane in0x1001, 0x1002 lub 0x1003. Przeniesienie

po

łowy słowa

musz

ą mieć adres bitu[0] równy 0 - dane mogą znajdować się w adresie 0x1000 lub 0x1002, ale

nie mog

ą być

0x1001.

Cortex-M3 wspiera transfer niewyr

ównany (unaligned transfer) na pojedynczych przejściach,

pami

ęć dostępu do

danych mo

że być zdefiniowana jako wyrównana lub niewyrównana.

Na czym polega i kiedy jest stosowany 'Stacking' w procesorach Cortex-Mx?

Kiedy wyst

ąpi wyjątek wrzucane jest 8 rejestrów do stosu:

-PC (program counter)

-PSR (program status register)

-R0-R3

-R12

-LR (link register)

Je

śli uruchomiony kod używa PSP (process stack pointer) stos procesu będzie użyty

Je

śli uruchomiony kod używa MSP (main stack pointer) główny stos będzie użyty

Potem g

łówny stos zawsze będzie używany podczas obsługi, więc wszystkie zagnieżdżone

przerwania b

ędą

korzysta

ć z głównego stosu

Zagadnienia, które były poruszane na początkowych wykładach:

-biblioteka CMSIS

-

architektrua Cortexów

-taktowanie

-porowanie Cortex z STM

-SysTic Timer

-GPIO

No i omawiał pliki startup

Miałam takie hasła w notatkach zapisane. Więcej

1. Jakie kroki należy wykonać w kompilatorze C dla procesora ARM 7 w środowisku Keil, aby

obsłużyć przerwanie IRQ?

• Ustawienie odpowiednich rejestrów, obsługa przerwania (skasowanie flagi,

uaktualnienie priorytetów wpisaniem dowolnej wartości do VICVectAddr)

2. Dlaczego przy zagnieżdżeniu przerwań IRQ w procesorze ARM7 konieczne są dodatkowe

makro-procedury?

17

• Aby nie stracić LG R14

3. Co należy wykonać w środowisku Keil Real View dla procesora ARM7, aby obsłużyć

przerwanie FIQ?

• Ustawienie rejestrów, obsługa przerwania, startup (stos, import, handler)

4. W których wyjątkach w procesorze ARM7 blokowane są przerwania IRQ, a w których FIQ?

• IRQ wszędzie, FIQ w restet i FIQ

5. Co trzeba zrobić, żeby w kompilatorach arm zrobić wstawkę asm

• __asm(„nop”)

6. Zainicjalizować przerwanie niewektoryzowane od EINT1

• Kodzik w C

7. Kiedy występuje abort i jakie są konsekwencje.

• Odczyt lub zapis do niedozwolonej pamięci, konsekwencja jest wyjątek, jeśli MMU to

nic

8. Jak w programie w kompilatorze keil można umieścić zmienną na stałe w pamięci.

• Zmienna globalna

9. Jakie ma funkcje PSR w ARM (czyli cpsr i spsr)

• CPSR ma flagi, blokowanie przerwan, tryb T, tryby.

User nie można zmienic CPSR, reszta może CPSR, SPSR można zmieniać wiec user

i system nie bo nie maja

10. Skoki w arm7 (chodziło o napisanie co i jak z R15 i R14 jak są wykorzystywane itd)

• Zapisanie adresu powrotu w R14 z R15 (plus minus ile?)

11.

Tryb Thumb co to jest i do czego służy.

• Tryb 16bitowy, do zaoszczędzenia pamieci (coś mało tych jego plusów:/)

12. Po co w arm są pseudo-instrukcje.

• Ułatwiają pisanie kodu i skracaja jego długość, np. instrukcja LDR

13. Wyjaśnić różnice w przyjęciu przerwania IRQ i FIQ dla procesorów ARM7.

• Bankowanie rejestrów, brak skoku do obsługi, najwyższy priorytet, w praktyce

stosowane tylko jedno

14. Jak przygotować i jak zareaguje ARM7 na zadanie przerwania tylko od licznika T0?

• Napisać kod dla Timera, i kiedy wystapi przerwani

15. Opisać VIC Vector Address

• VIC wpisuje tu adres przerwania, który wpisywany jest do PC (strona38), Na koniec

wpisujemy żeby VIC zaktualizował priorytety

16. Adresowanie stosu

• Ostatni tryb uzytkownika, nie wszystkie stosy musza być zainicjalizowane

17. Jak w procesorze ARM7 poradzono sobie z wolną pamięcią Flash (jak pogodzono

czestotliwosc pracy rdzenia i duzo wolniejszej pamieci)?

• ładowanie krytycznych części programu do RAM i uruchamianie ich z RAMu,

używanie cache,

MAM - Memory Accelerator Module -

pojedyńczy dostęp do Flash za pomocą MAM,

pobiera cztery instrukcje ARM lub 8 THUMB

18. Dlaczego rejestry DLL i DLM są 8 bitowe?

• Bo zostało to skopiowane z C51

19. Dlaczego we wzorze na prędkość transmisji UART występuje 16?

18

• Dzięki temu maksymalna prędkość transmisji wynosi 1/16 cyklu. Jest to

zabezpieczenie które gwarantuje poprawne wykrycie bitu startu

20. Do czego wykorzystywane sa w ARMie rejesty R8-R15.

• R8-R12 ogolnego przeznaczenia bankowane w fiq,

R9 zaleznie od platformy może być bazą stałą (SB) lub Thread register (TR) lub do

przekazywania zmiennych v6,

R12 IP może być uzywany przez linker jako scratch register miedzy procedura

i jej podprocedura lub jako rejestr przekazujacy zmienne miedzy podprocedurami, R13

SP, R14 LR, R15 PC

21. W jakich warunkach można zmieniać a w jakich nie rejestry PSR w ARMie

• CPSR można modyfikowac we wszystkich trybach uprzywilejowanych, w USERZE

można zmieniać flagi pośrednio,

SPSR można zmieniac tylko w trybie wyjątków ponieważ tylko tam wystepują.

Dla potomnych:

1. Co startup ustawia jeśli chodzi o taktowanie.

2. Opisać PSR.

3. Co trzeba zrobić, żeby obsłużyć przerwanie IRQ od timera0

4. Dlaczego FIQ jest szybsze niż IRQ

5. Konsekwencje zastosowania standardu AAPCS dla przerwań FIQ

6. Co trzeba zrobić, żeby ustawić taktowanie UART-a.

Zebrane odpowiedzi na pytania:

1. Co startup ustawia jeśli chodzi o taktowanie.

ustawia pracę pętli PLL (parametry M i P), która zmienia Ci częstotliwość oscylatora na

częstotliwość taktującą rdzeń. Ustawia też dzielinik dla magistrali APB (dla peryferii).

<MrSaturday>

2. Opisać PSR.

nie chce mi się tego wszystkiego pisać ;p

3. Co trzeba zrobić, żeby obsłużyć przerwanie IRQ od timera0

VICIntSelect = 0; lub VICIntSelect &= ~(1 << 4);

VICIntEnable = 1<<4;

VICVectAddr3 = (unsigned int)T1_IRQ;

VICVectCntl3 = 0x20 | 4;

napisać obsługę przerwania:

__irq void T1_IRQ(void)

{

(...)

VICVectAddr = 0;

19

}

4. Dlaczego FIQ jest szybsze niż IRQ

-

FIQ jest niewektoryzowane (nie ma priorytetów)

-

w FIQ bankowane są rejestry R8-R12 przez co nie trzeba tracić cykli na zrzucenie ich na stos

-

najwyższy priorytet (nie wiem czy to trzeba pisać)

-

brak zagnieżdzeń

5.

Konsekwencje zastosowania standardu AAPCS dla przerwań FIQ

standard AAPCS wymaga, żebyś przy wejściu do przerwania zrzucił na stos rejestry R0 i R1. W

przerwaniach FIQ to jest w większości przypadków bez sensu, bo po to masz bankowane

rejestry R8-

R14, żeby niczego na stos nie zrzucać. Powoduje to że przerwanie działa wolniej

(najpierw push, potem pop). <MrSaturday>

6. Co trzeba zrobić, żeby ustawić taktowanie UART-a.

UnLCR = 0x8x; // DLAB = 1 (0x80);

UnDLL = y;

UnDLM = z;

// ewentualnie bity w

UnFDR odpowiadające za MULVAL i DivADDVal

UnLCR = 0x0x; // DLAB = 0;

1. opisać rejestry od R0-R15

2. Co zrobić żeby na portach p1.13-24 na wyjściu było logiczne 0

3. zrobić sprzętowo sygnał prostokątny o wypełnieniu 1/2

4.dlaczego w startupie ustawiany jest usermode na koncu pliku

5.coś w stylu dlaczego jest problem z zagnieżdżeniami przerwań w armie

6. dlaczego trzeba wpisać w UxLCR0=x080 żeby można było zmienić UxDLL i UxDLM

1. NA czym polega Aligned Word Data Transfer w procesorach Cortex M3

2. W jakim celu ejst stosowany standard AAPCS?

3. Co oznacza skrót xPSR w procesorach Cortex M0 i jakie jest jego przeznaczenie ?

4. Jakie tryby(rodzaje) pracy maja procesory Cortex M3? Jakie typy stosu wykorzystują te tryby

?

5. W jaki sposób sa adresowane wezły magistrali I2C BUS?

6. Na czym polega ki keidy ejst stosowany Unstracking?

Wyszukiwarka

Podobne podstrony:

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

LTC1729 id 273494 Nieznany

D11B7AOver0400 id 130434 Nieznany

analiza ryzyka bio id 61320 Nieznany

pedagogika ogolna id 353595 Nieznany

Misc3 id 302777 Nieznany

cw med 5 id 122239 Nieznany

D20031152Lj id 130579 Nieznany

mechanika 3 id 290735 Nieznany

więcej podobnych podstron