CELLAR

www.circuitcellar.com

CIRCUIT

®

# 1 2 7 F E B R U A R Y 2 0 0 1

SIGNAL PROCESSING

DSP Application with the SHARC

Build a Remote-Control A/V Switch

A Digital Altimeter Project

All About the AVR

T H E M A G A Z I N E F O R C O M P U T E R A P P L I C A T I O N S

CIRCUIT CELLAR

®

Issue 127 February 2001

3

www.circuitcellar.com

ISSUE

INSIDE

127

127

Quirks and SHARCs

Michael Smith

An Altimeter for the Traveling Man

Radek Vaclavik

Enabling the Couch Potato

Building a Remote-Controlled AV Switch with S-Video

Jerry Wasinger

Working with AVR Microcontrollers

A Design Logic 2001 Primer

Stuart Ball

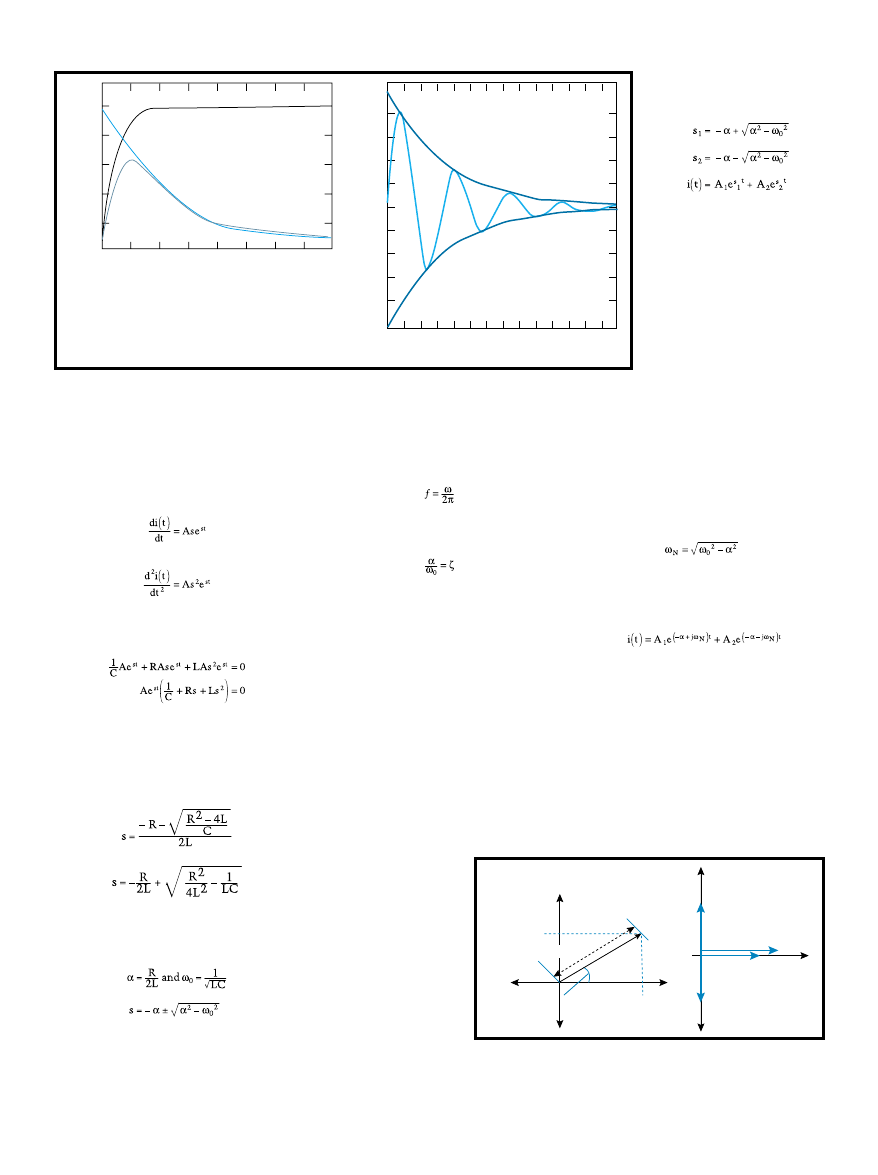

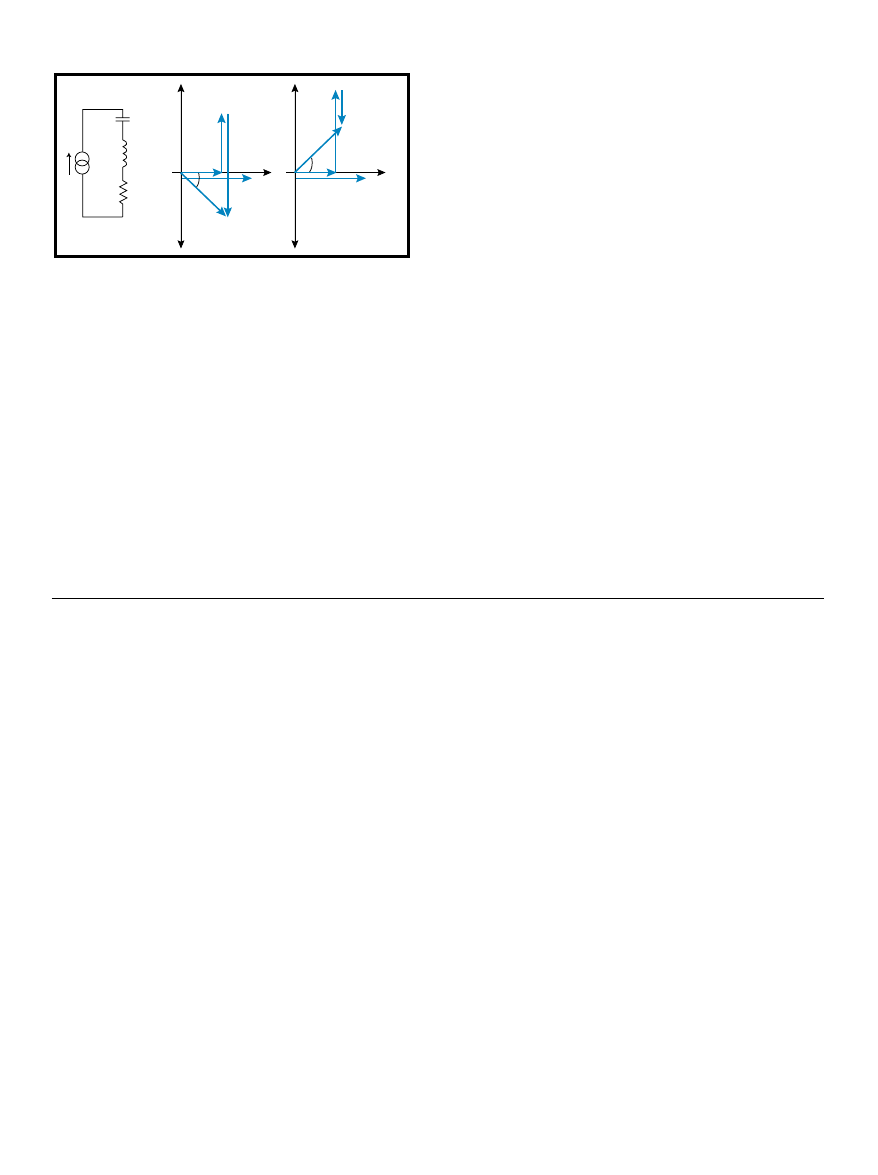

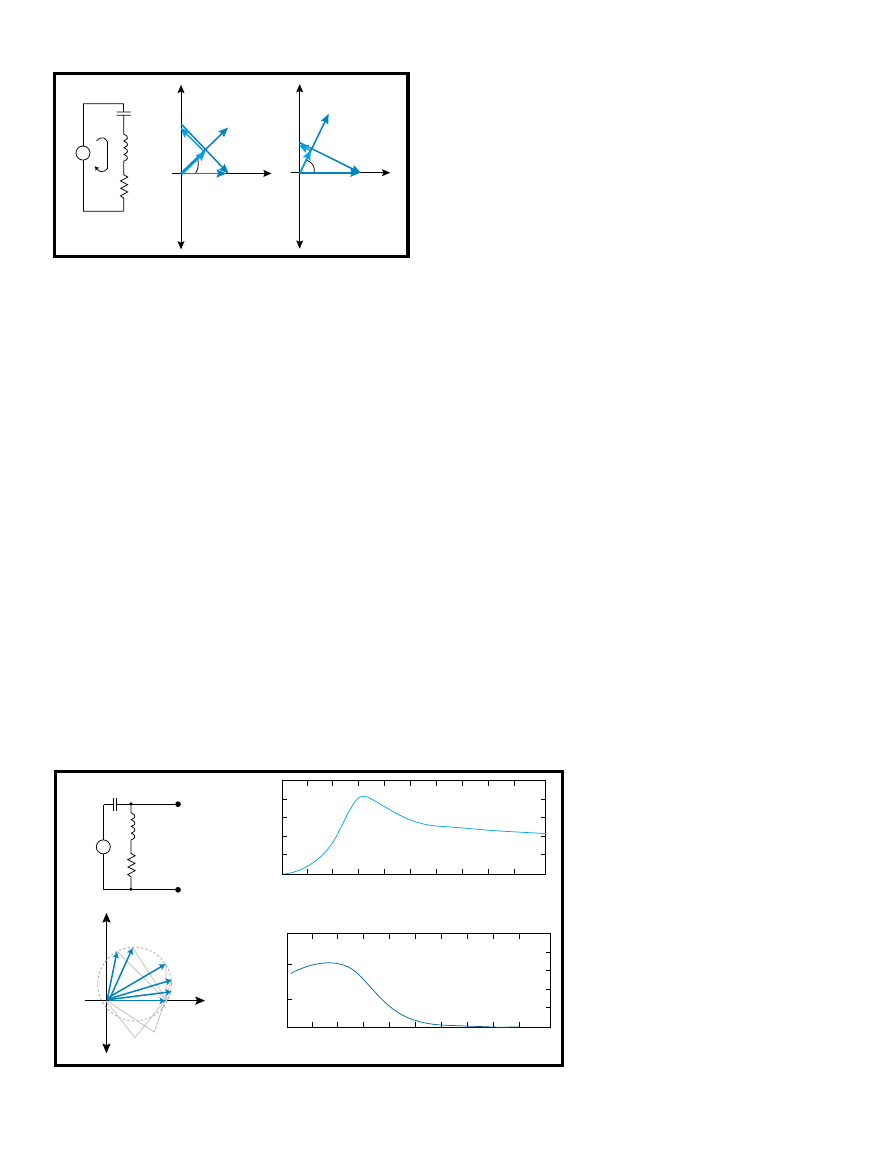

Micro Series: Fundamentals of Second-Order Systems

Part 2: The Tools of the Trade

David Tweed

Above the Ground Plane

Bring the Noise!

The Analog Side of X10

Ed Nisley

From the Bench

Car 54, Where (Exactly) Are You?

Adding E-Mail Capabilities to Your Project

Silicon Update

’51 Soldiers On

Tom Cantrell

6

9

11

83

95

96

E

MBEDDED

PC

Real-Time PCs

A Cup of Java

Part 3: Embedded and Real-Time Solutions

Ingo Cyliax

Applied PCs

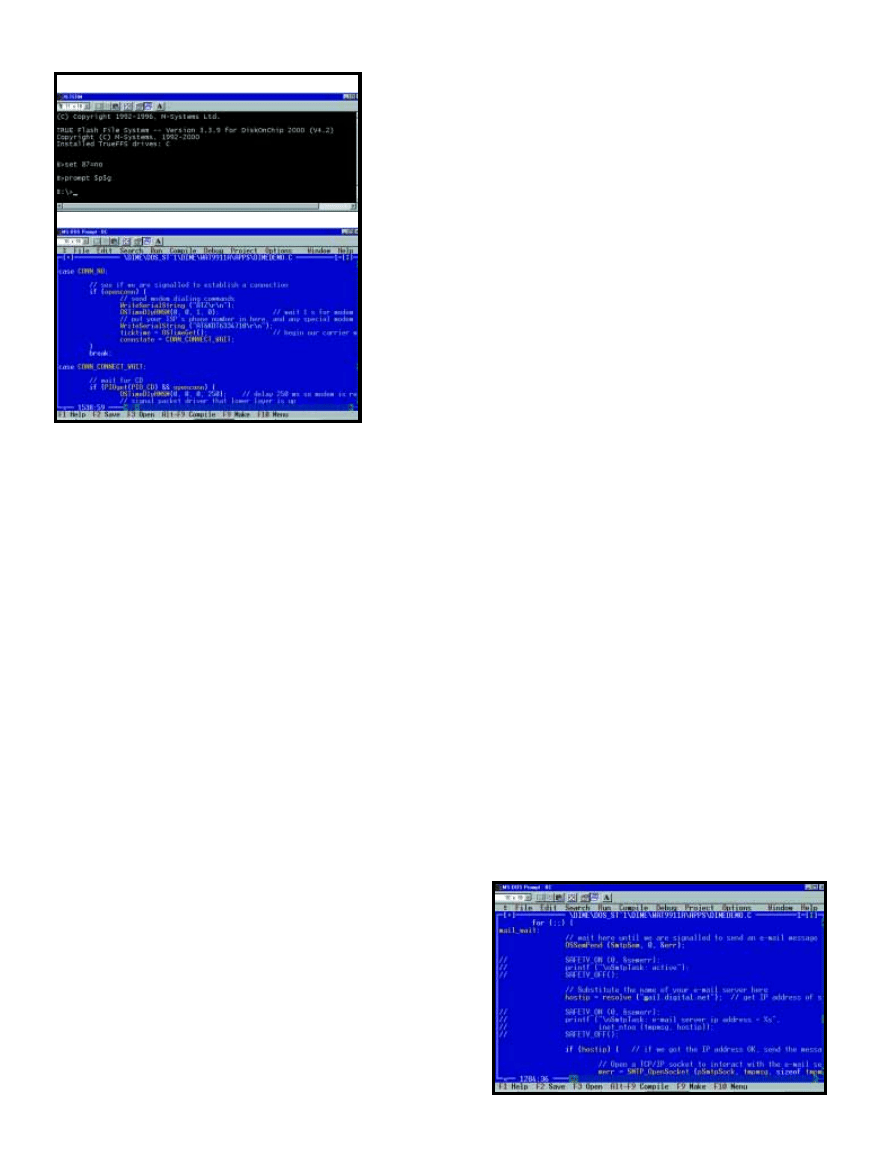

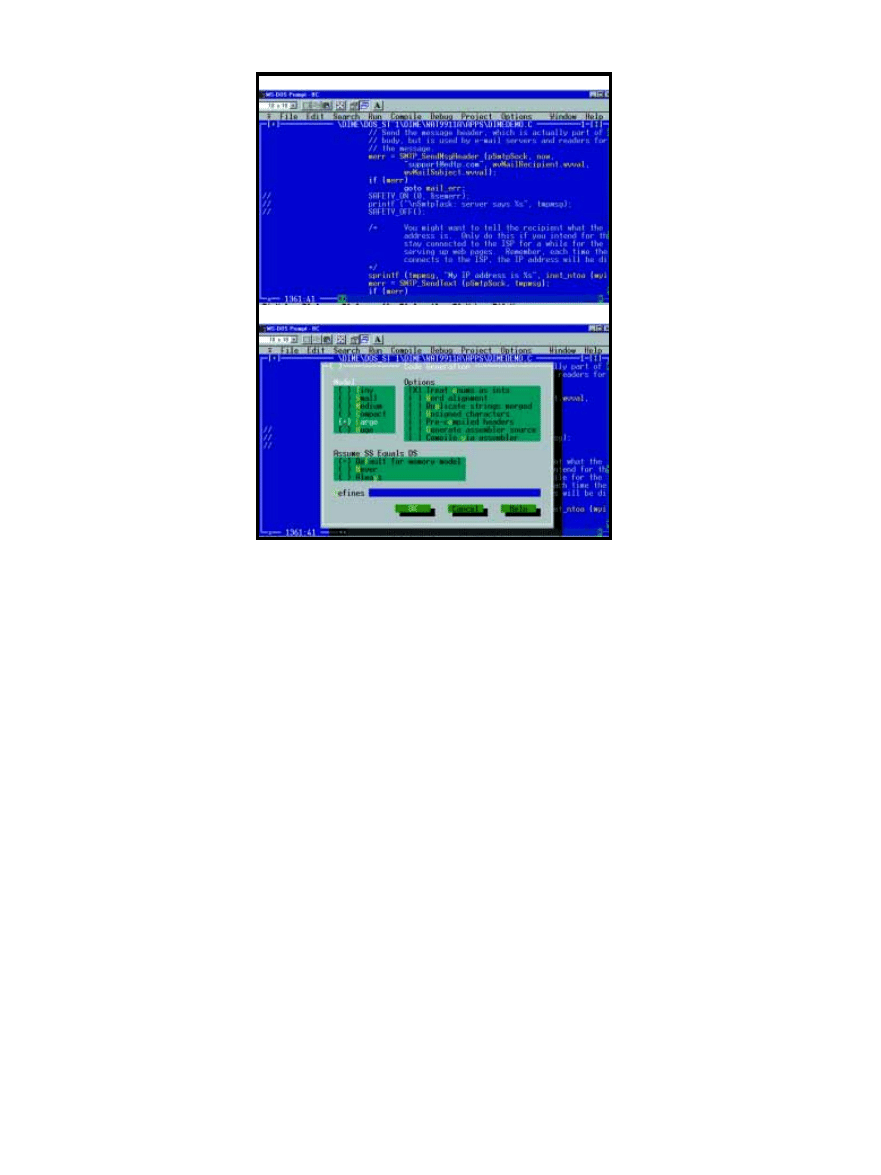

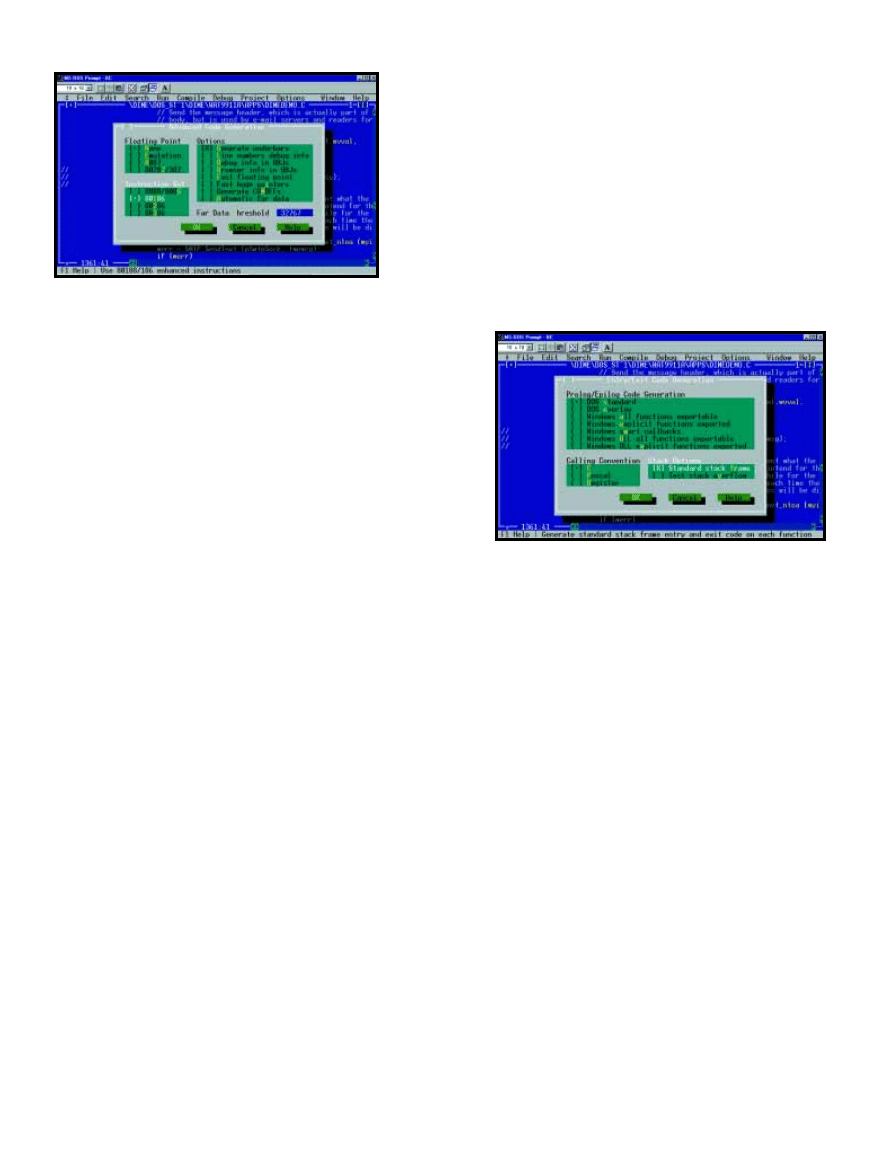

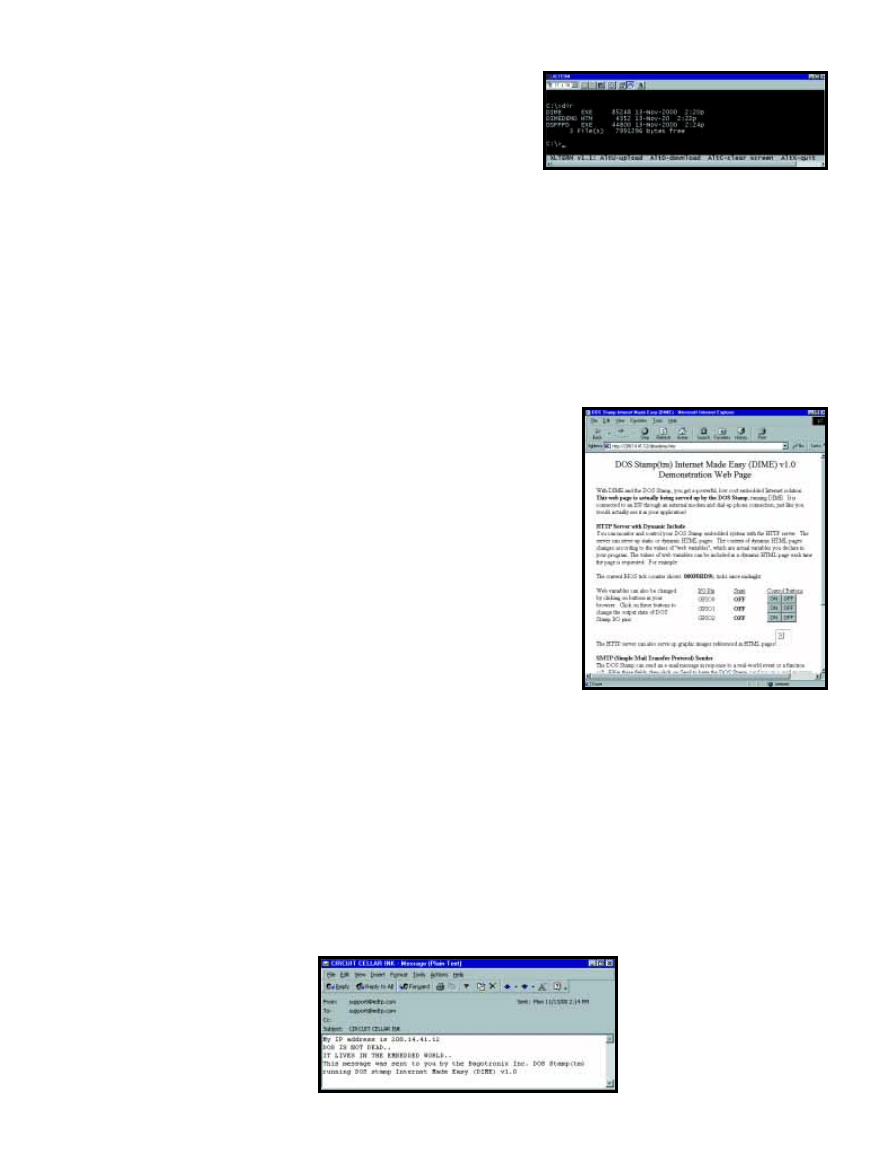

One Thin DIME—Getting on the ’Net with DOS

Fred Eady

ASK

ASK

ASK

ASK

ASK

US

US

US

US

US

THE ENGINEERS

TECH-HELP

RESOURCE

Let us help keep your

project on track or sim-

plify your design deci-

sion. Put your tough

technical questions to the

ASK US team.

The ASK US research

staff of engineers has

been assembled to share

expertise with others.

The forum is a place

where engineers can

congregate to get some

tough questions an-

swered, or just browse

through the archived

Q&As to broaden their

own intelligence base.

★★★★★★★★★★

★★★★★★★★★★

★★★★★★★★★★

★★★★★★★★★★

★★★★★★★★★★

Test Your EQ

8 Additional Questions

RESOURCE LINKS

• Magnets

Bob Paddock

• Webcam’s

Rick Prescott

• 1 Ghz Chips

Brant Schroeder

HIGH-TEMPERATURE ELECTRONIC DESIGN

Part 1: What Are Your Options?

by George Novacek

Design options for temperatures beyond 125°C have been scarce in the past, but this month

George shows us that there are ways to get around the technical problems and risk and still

create state-of-the-art designs. Electronics from the common to the complex can benefit

from finding new alternatives geared for elevated temperatures. If you’re successful,

the result could be simpler designs that are more robust, economical,

and reliable.

January 2000

MONITORING THE REVOLUTIONS

A Pedal Cadence Counter

by Matt Meerian

Staying physically fit is a way of life for most today. To get an optimum workout, Matt

creates a design that combines two of his favorite hobbies, electronics and mountain biking,

to reach the ultimate workout goal. By combining low-level programming with high-level

language, you can tailor the cadence barometer for whatever activity suits your

interest. Any way you cut it, you can gauge for accuracy while doing the

exercises you enjoy.

January 2000

AN S-7600A/PIC16F877 JOURNEY

Part 1: Laying Out the Tools

by Fred Eady

Depending on the tools of the trade as well as the skill of the craftsman, Fred embarks on

an Internet engine journey this month. As he takes you through this series, you’ll see the

end result of a functional Internet communications device that speaks many

languages and interfaces. Laying out the tools seems a good place to start.

Skill is sure to follow.

January 2000

DESIGNING WITH VHDL

Learning the Ropes

—by Ingo Cyliax

Once something becomes mainstream, you better think about jumping on board. Such is

the case with hardware description languages (VHDL) for designing FPGAs and CPLDs.

Even if it’s new to you, Ingo explains that Xilinx’s WebPack makes digital design under-

standable. The benefits far outweigh the chore of having to learn the language. And,

because it’s at no cost to you, what more could you ask for?

January 2000

BEHIND THE SCENES

Lessons From the Trenches—by George Martin

A Comprehensive Look at ColdFire

George puts on a stage show of sorts with this installment, as he explores the PC/Internet

combination and, in particular, Motorola’s ColdFire processor. Taking its place as a

standard CPU model, the ColdFire design is outlined on Motorola’s web site, where all

manner of datasheet and manual information is made available. If you’re still not

convinced that the needed support is there, the addition of an extensive

discussion group should seal the sale for you.

January 2000

BEING MERRY WITH USB

Silicon Update Online—

by Tom Cantrell

Tom tries to stay positive as he reminds us of the familiar grief of the three-finger salute (Ctrl

+ Alt + Delete) and the agony of rebooting. Negativity aside, he looks for solutions to his

problem of two printers on a single parallel port in everything from calling tech support to

calling an exorcist. A USB interface helped to remedy the situation.

January 2000

www.circuitcellar.com

6

Issue 127 February 2001

CIRCUIT CELLAR

®

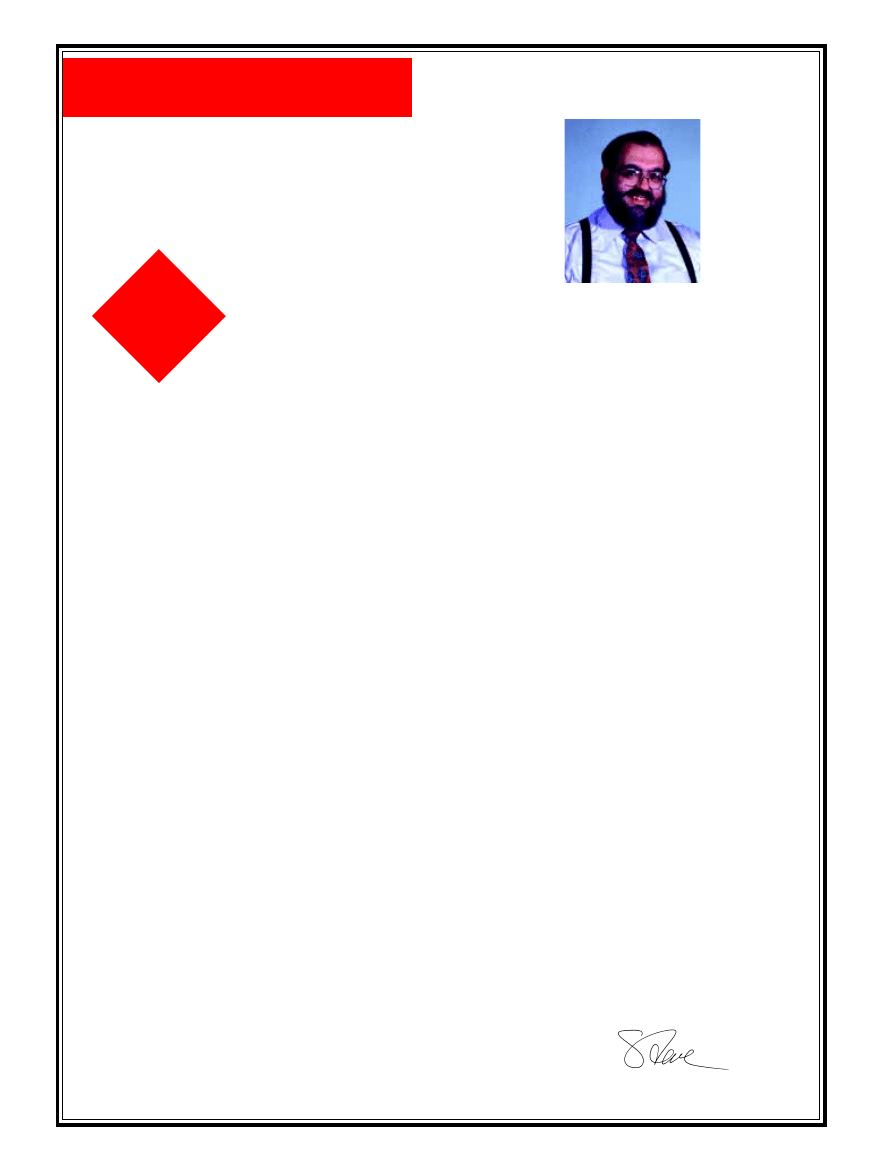

TASK

MANAGER

EDITORIAL DIRECTOR/PUBLISHER

Steve Ciarcia

MANAGING EDITOR

Rob Walker

TECHNICAL EDITORS

Jennifer Belmonte

Rachel Hill

Jennifer Huber

WEST COAST EDITOR

Tom Cantrell

CONTRIBUTING EDITORS

Mike Baptiste

Ingo Cyliax

Fred Eady George Martin

George Novacek

NEW PRODUCTS EDITORS

Harv Weiner

Rick Prescott

PROJECT EDITORS

Steve Bedford Bob Paddock

James Soussounis

David Tweed

ASSOCIATE PUBLISHER

Joyce Keil

CHIEF FINANCIAL OFFICER

Jeannette Ciarcia

CUSTOMER SERVICE

Elaine Johnston

ART DIRECTOR

KC Zienka

GRAPHIC DESIGNERS

Naomi Hoeger

Mary Turek

STAFF ENGINEERS

Jeff Bachiochi

John Gorsky

QUIZ MASTER

David Tweed

EDITORIAL ADVISORY BOARD

Ingo Cyliax

Norman Jackson

David Prutchi

Cover photograph Ron Meadows—Meadows Marketing

PRINTED IN THE UNITED STATES

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

CONTACTING CIRCUIT CELLAR

SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com

TO SUBSCRIBE: (800) 269-6301, www.circuitcellar.com/subscribe.htm, or subscribe@circuitcellar.com

PROBLEMS: subscribe@circuitcellar.com

GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 FAX: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com

EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066

AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article.

CIRCUIT CELLAR

®

, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) and Circuit Cellar Online are published

monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon,

CT and additional offices.

One-year (12 issues) subscription rate USA and possessions $21.95, Canada/Mexico $31.95, all

other countries $49.95. Two-year (24 issues) subscription rate USA and possessions $39.95, Canada/Mexico $55, all other

countries $85.

All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check

drawn on U.S. bank.

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH

03755-5650 or call (800) 269-6301.

Postmaster:

Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

ADVERTISING

ADVERTISING SALES REPRESENTATIVE

Kevin Dows

Fax: (860) 871-0411

(860) 872-3064

E-mail: kevin.dows@circuitcellar.com

ADVERTISING COORDINATOR

Valerie Luster

Fax: (860) 871-0411

(860) 875-2199

E-mail: val.luster@circuitcellar.com

ADVERTISING CLERK

Sally Collins

rob.walker@circuitcellar.com

Signal Corps

s

ignal processing is going on all around us, and

I don’t just mean in a technological sense. Almost

everything we say or do gives off some kind of signal.

Open any textbook for Sales 101 and you’ll find at least

one section on how to “read” the customer. You’ll also find a section or two

about how the sales representative’s body language can influence a poten-

tial customer in either a positive or negative way. If it seems like there could

be a lot riding on the blink of an eye or the twitch of a nose, you’re right.

But, the same could be said about the publishing business. There are a

lot of little variables that can influence someone’s opinion about a maga-

zine. In that sense, the staff at

Circuit Cellar is a lot like a division of the

signal corps. Every word we choose and every adjustment we make to the

magazine must be carefully considered because it’s a message that is

going to be interpreted by an audience of readers around the world.

One of the easiest ways for us to make sure

Circuit Cellar is sending the

right signals is by tracking the reader responses that come in. It’s an inter-

esting (and encouraging) fact that the majority of the feedback we get, even

when it’s about an error that was made, either begins or ends by saying

how much that reader enjoys the magazine. That’s not to say we let a few

positive words go to our heads. From time to time we have to stand up and

take some “Hey, idiot” feedback about an error that gets by.

Another way for us to make sure that

Circuit Cellar is sending the right

signals is by asking for our readers input, which is why we post surveys on

our web site. That’s also why we put together a reader survey every couple

of years. It’s been two years since our last reader survey, so this spring

we’ll be randomly choosing a number of subscribers who will receive our

reader survey.

Unlike most magazine surveys, we don’t do this so we can get more

information about you to sell to someone else. The answers to our reader

survey provide information that allows us to find out why you read

Circuit

Cellar and what interests you—for the sole purpose of keeping Circuit Cellar

by engineers, for engineers. Knowing what projects and technologies our

readers are interested in means that we can continue to provide you with

the editorial content you want.

So, if you receive one of our reader surveys, please don’t be confused

about our motives. The signal we’re trying to send is that your opinion

matters at

Circuit Cellar.

As for this month’s cover, don’t be confused about the signals we are

trying to send (er, not send) with our choice of signal flags. We don’t have a

man overboard, you are not running into danger, and this issue is not taking

in, discharging, or carrying dangerous cargo!

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the

consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-

assembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from

plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to build

things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or

operate any of the devices described herein under the relevant patent or other intellectual property law of the reader’s jurisdiction. The reader

assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright © 2001 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of

Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

READER

I/O

Editor’s note: In the December issue (125), there

were errors made in the following schematics:

• Figure 1 in “The QuizWiz: A Hand-Held Scoring

Device” by Paul Kiedrowski, pg. 33.

• Figure 4 in “Using a T6963 Controller-Based

Graphics LDC Panel” by Brian Millier, pg. 62.

• Figure 1 in “Sharing Technology with Mother

Nature: Out of State with an Internet-Compat-

ible Cell Phone” by Jeff Bachiochi, pg. 75.

The corrected schematics are available for

downloading at ftp.circuitcellar.com. We apolo-

gize for any inconvenience this may have caused.

WHAT MORE COULD YOU NEED?

I liked Steve’s editorial in the November

2000 (124) issue. I am continually amazed at

what the computer-buying public will put up

with these days. No one really needs a 500-

MHz computer unless they are creating detailed

animations or such. You are correct, the only

thing that demands a fast computer these days

is a sloppy operating system. I still do every-

thing I want on the 25-MHz Amiga 3000 that I

bought in 1992.

I wonder what would happen if the govern-

ment decreed that there should only be one

computer design and one operating system and

then demanded a $1000 hardware upgrade tax

each year. There would be rioting in the streets.

When Bill Gates does the same thing, people

throw money at him. Strange world!

Tom Napier

12

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

w

hen developing

or using a new

embedded system, it

is important for the de-

veloping team to remember Murphy’s

Law. What is really happening when

things appear to be going well in the

early stages? Simple, the development

team doesn’t understand the project

well enough to recognize that things

are already going astray! This article is

a personal story about one such situa-

tion. I learned things the hard way, but

you can benefit from my experience.

Several years ago, I had to switch

from an advanced RISC processor

(AMD29050) to Analog Devices’

ADSP21061 SHARC processor for DSP

applications. There was an initial

learning curve associated with the new

SHARC architecture, particularly its

super-scalar instruction

capability and indepen-

dent data address-gener-

ating ALUs. But, many

of the ’29050 features

are present in the

ADSP21061.

The first year of

teaching my applica-

tions-oriented advanced

microprocessor course

on the ’21061 went well.

The C-like assembly

code syntax meant

fewer simple errors were generated

than with the 29k RISC assembly syn-

tax. The SHARC EZ-Lite evaluation

boards have an onboard CODEC,

which allows the development of in-

teresting audio projects. That first

year, I used the 21k’s floating-point

capability for developing DSP algo-

rithms without having to worry about

the overflow protection needed in

integer applications.

I became more adventuresome by

the second year of teaching with the

SHARC board. Certain items from the

initial course were dropped, leaving

more time for other concepts. The

class started exploring using the

’21061 processor’s integer capabilities

to demonstrate DSP programming

techniques for processors without

floating-point instructions.

It didn’t take a difficult algorithm

involving integers to cause a situation

where things didn’t work as expected!

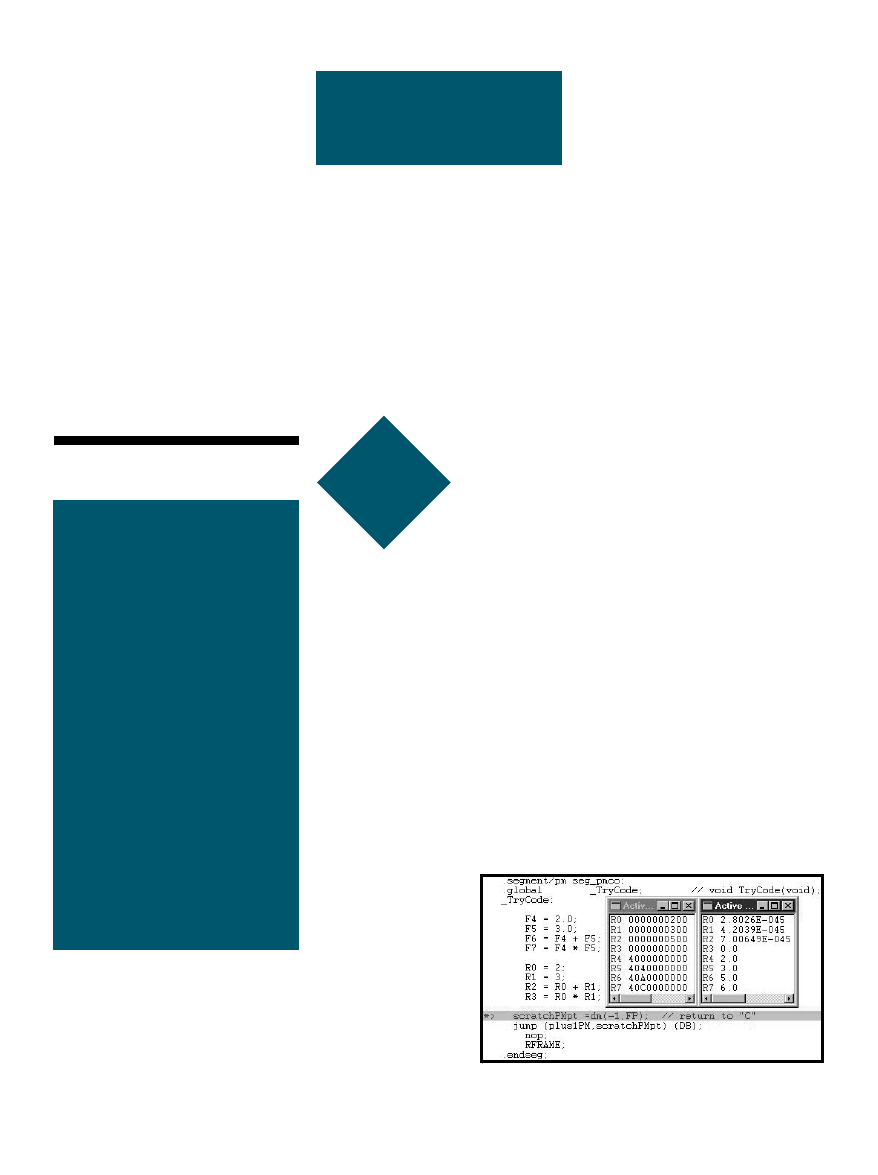

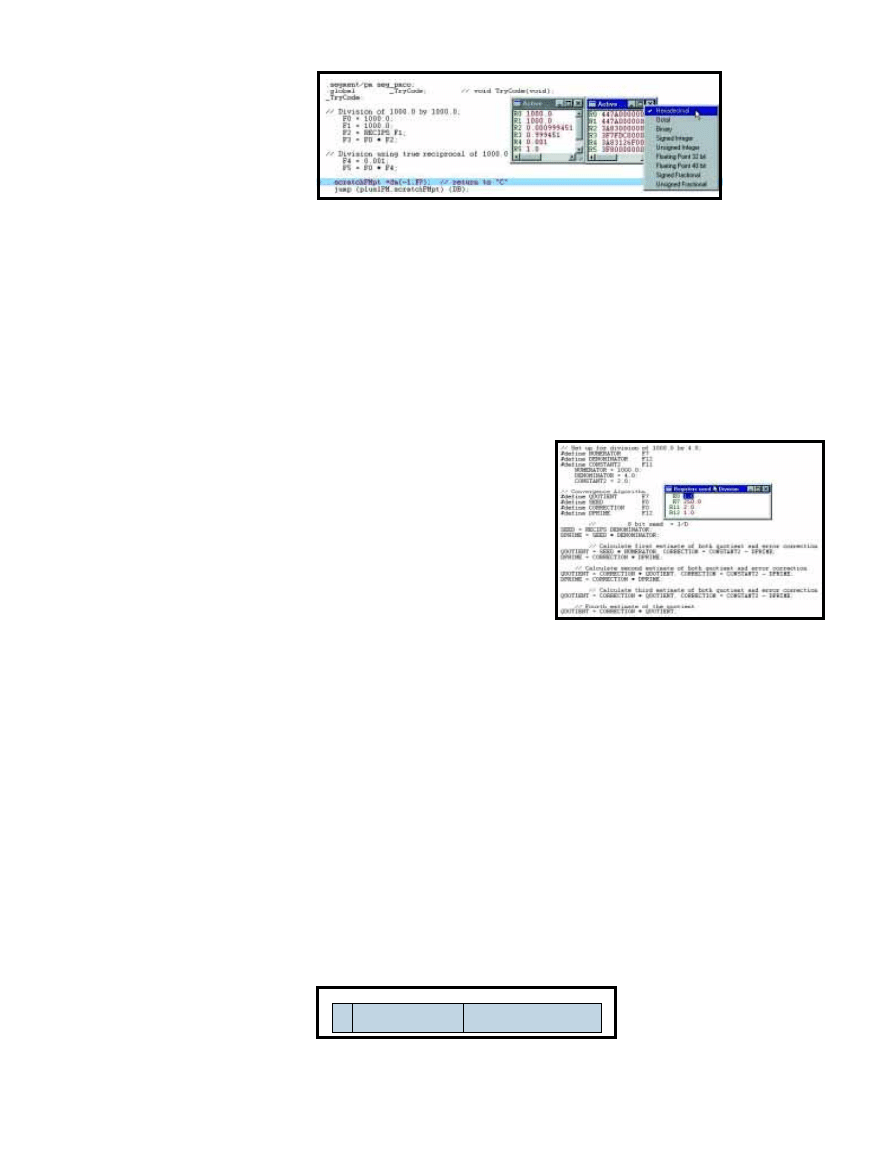

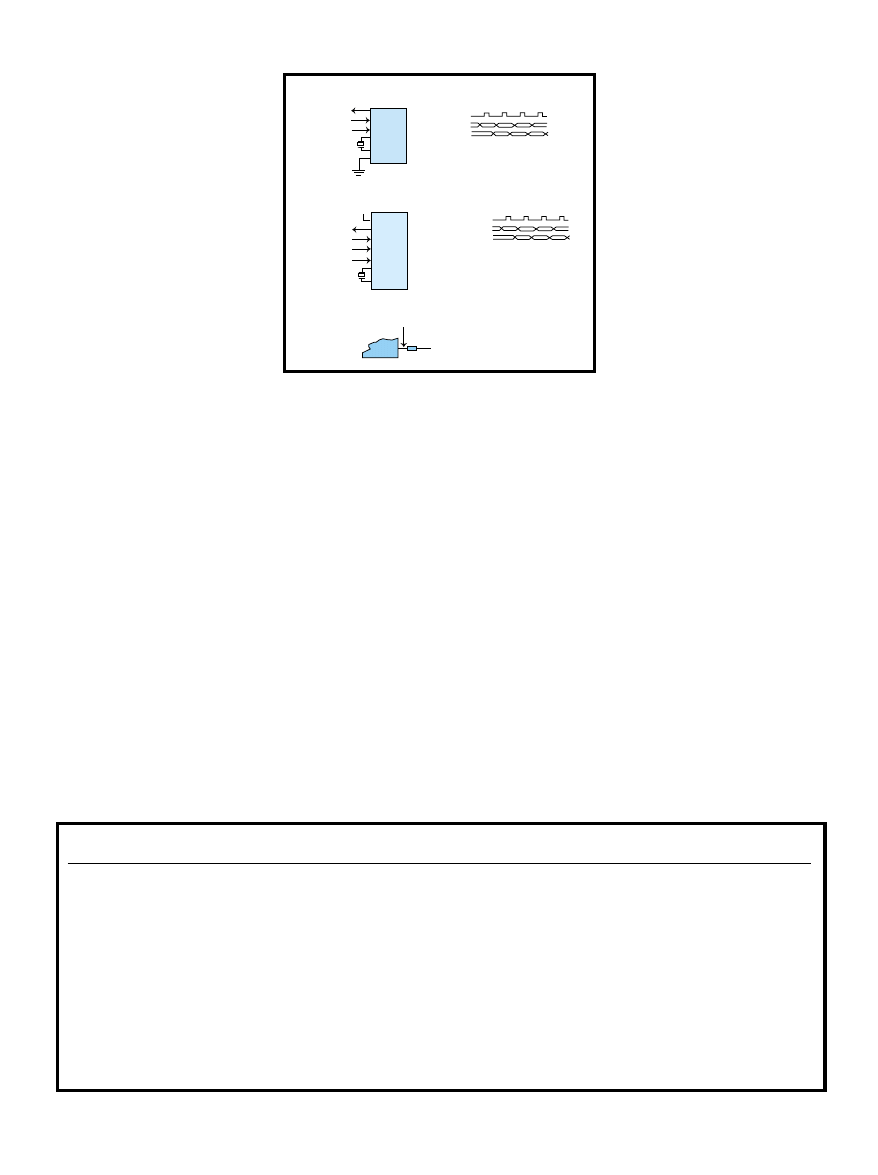

Photo 1 shows the White Mountain

VisualDSP SHARC simulator environ-

ment. The results are shown for several

basic assembly code operations. The

bit patterns in the data registers have

been interpreted using both integer

and floating-point formats.

Photo 1’s floating-point results

make sense (2 + 3 = 5 and 2 × 3 = 6).

But, the integer addition 2 + 3 = 5 has

been scaled by 0x100 to become:

0x200 + 0x300 = 0x500

Although unexpected, the addition

operation makes sense, unlike the 21k

integer multiplication operation,

which implies:

0x200 × 0x300 = 0

FEATURE

ARTICLE

Michael Smith

Just when you

thought it was safe to

continue on to the

later stages of DSP

application develop-

ment, Michael shows

us how quickly simple

problems can multiply

if left unresolved. The

right information can

be a lifesaver when

working with SHARCs.

Quirks and SHARCs

Photo 1—

Basic floating-point addition and multiplication operations on

the SHARC processor work as expected. However, even the simplest

integer addition and multiplication operations give incorrect results.

CIRCUIT CELLAR

®

Issue 127 February 2001

13

www.circuitcellar.com

As soon as you realize that there is one

thing about a processor that you don’t

understand, the floodgates open.

The AMD29k processor has a float-

ing-point instruction for division cal-

culations. It may be 11 times slower

than other 29k instructions, but it

exists, which is not true for the 21k

floating-point division instruction!

The 21k instruction set includes a

reciprocal instruction, but it doesn’t

appear to work as expected either.

The next issue involves fancy foot-

work with the internal operations of

the 21k processor to do something

neat—fast, single-cycle, floating-point

division. With any integer processor,

you can get fast division by powers of

two by using correct arithmetic shift

operations as shown by the following

68K instruction:

ASR #4, D0

gives D0 / 16

By understanding the bit representa-

tion of floating-point numbers, you can

perform comparable tricks to make

fast division (scaling) occur with float-

ing-point powers of two. This knowl-

edge could be particularly useful for

algorithms involving the FFT (fast

Fourier transform) algorithm. The

output from an inverse N-point FFT

requires scaling by a factor of N.

This fast division operation requires

checking and manipulating the float-

ing-point number’s binary component

bits. It’s more complicated to achieve

this on the 21k than on the AMD 29k

and Motorola 96000 processors (see

“Fast-Scaling Routine for Floating-

Point RISC and DSP Processors,” Cir-

cuit Cellar

52). The deep 21k instruc-

tion pipeline means there are several

cycle-stealing, delayed branch instruc-

tions associated with each

program decision (conditional

JUMP instruction). Some of

the problems can be overcome

by using the 21k super-scalar

and conditional compute in-

structions.

To get the most out of any

processor, you have to prop-

erly understand the conse-

quences of all aspects of that

processor’s architecture. De-

spite the apparently contradic-

tory characteristics of the 21k

architecture, they make sense.

There is a valid design decision

underlying every one of these

apparent ADSP SHARC processor

quirks.

MAKING 0X2 APPEAR AS 0X200

Because of the characteristics of the

68K processor architecture, a data

register showing bit pattern

0x800070FF can be interpreted in

different ways. For BYTE (8-bit)

operations, the register contains

the negative value 0xFF. The regis-

ter also can be considered as con-

taining the positive value 0x70FF

(16-bit word) or the negative value

0x800070FF (32-bit word).

In Photo 1, integer 0x2 appears

as the hexadecimal number 0x200

as a direct consequence of the in-

ternal architecture of the SHARC’s

data registers and ALU. Data regis-

ters are 40-bits wide to allow storage

of numbers in both the IEEE 754/854

standard 32-bit, single-precision, float-

ing-point format and an extended-

precision version of the same format.

Unlike the 68K processor, the sig-

nificant bits on the 21k data values are

at the high end of the register bit pat-

tern. This means that the last two

nibbles stored in a data register should

be ignored during interpretation or

when the value is written out to 32-bit

memory. The SHARC internal

memory architecture can be software

configured to handle both 32- and 40-

bit data memory operations.

GETTING 2 × 3 TO EQUAL 6

Because there are 32 significant bits

at the top of every 40-bit SHARC

register, it’s easy to understand why:

0x2 + 0x3 = 0x5

appears as operations using the values:

0x200 + 0x300 = 0x500

when the register contents are exam-

ined. But, it doesn’t explain why:

0x2 × 0x3 = 0x0

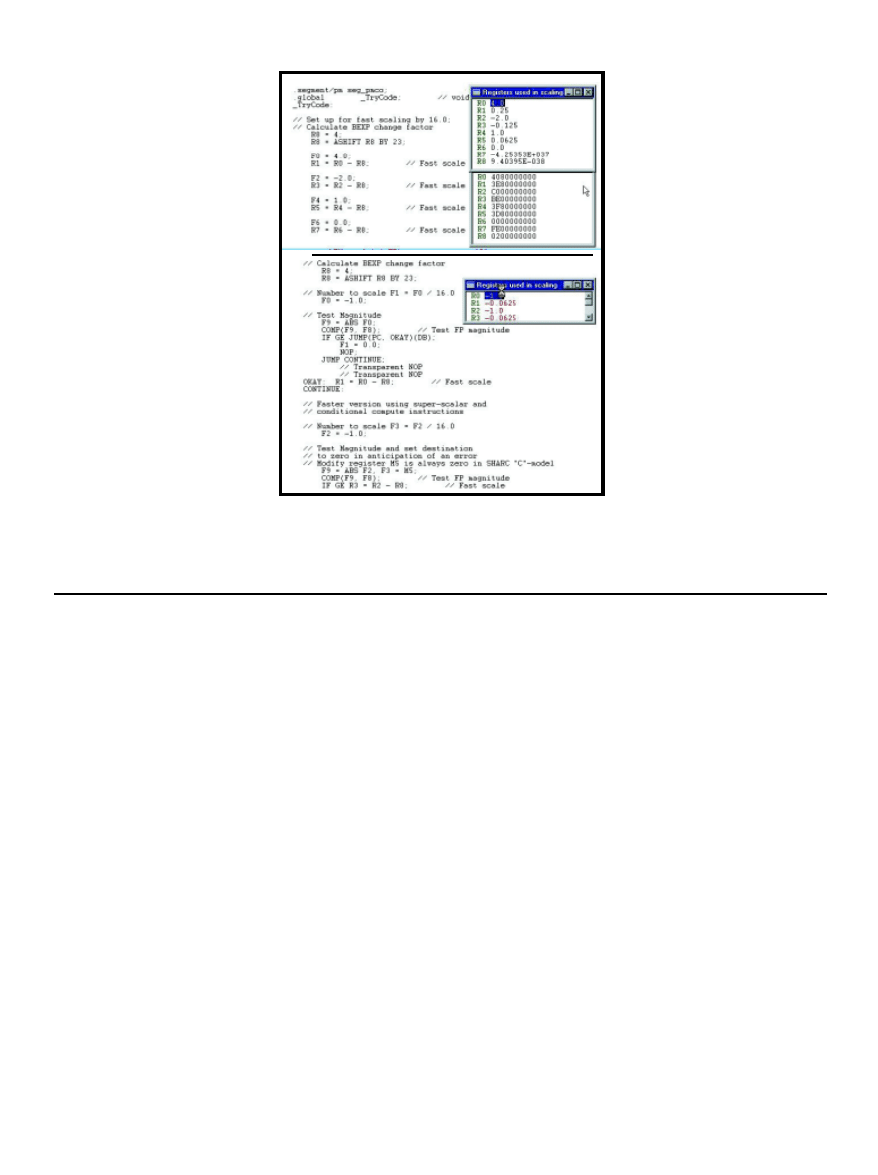

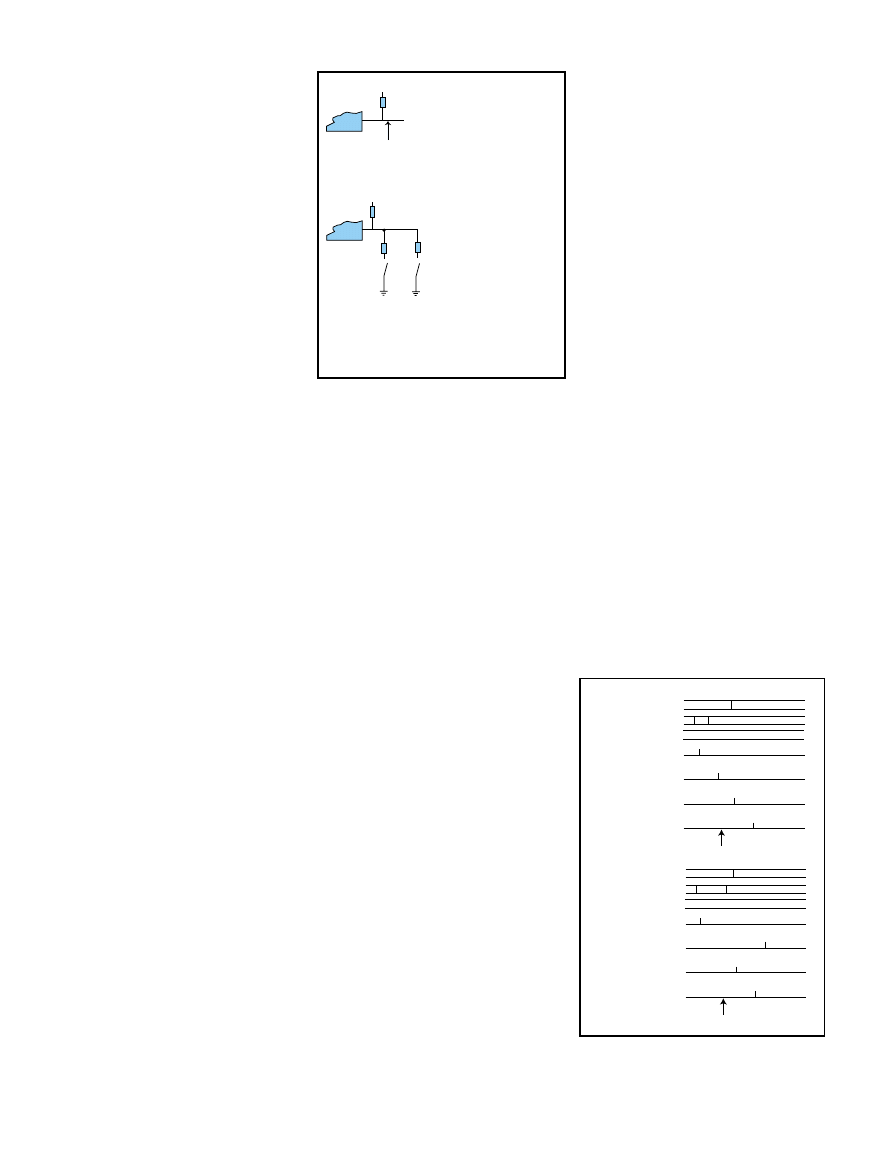

Photo 2 shows the program from

Photo 1. But, in this case, the display

mode for the VisualDSP development

environment is set to Mixed mode

rather than Source. During Mixed

mode, you see what you want to do

(source) and the bit patterns (assembly

code) associated with how the proces-

sor is interpreting those requests!

Photo 2—

The result of basic SHARC operations can be found in

the upper 32 bits of the 40-bit data register. Using the VisualDSP

development environment mixed mode display format, it can be

seen that the default SHARC integer multiplication instruction

expects a signed-signed fractional (SSF) number representation

rather than the standard two’s complement integer format.

Photo 3—

The SHARC processor starts acting like any

other processor after activating the signed-signed integer

multiplication operation rather than the default signed-

signed fractional format.

Photo 4—

Activating the

signed fractional inter-

pretation of the bit

patterns stored in the

integer data registers

shows that signed-

signed fractional opera-

tions are internally

consistent, even if they

don’t give the antici-

pated results.

14

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

Let me explain why multiplication

operations appear to always give zero

or equivalent answers. Instead of per-

forming the intended standard multi-

plication operation R0 × R1, you

unintentionally activated R0 × R1

(SSF). SSF stands for the signed-signed

fractional form of the integer multipli-

cation instruction. [1]

The fact that an instruction comes

in both signed and unsigned forms is a

familiar concept. The 68K processor

has two types of multiplication opera-

tions, MULS (signed) and MULU (un-

signed). Many processors have three

forms of addition operations. The 29k

processor has ADDU and ADDS in-

structions, which cause exceptions to

the rules when the unsigned and signed

number representations overflow dur-

ing addition. And, ADD works when

you’re not worried about overflows.

The concept of a fractional repre-

sentation within an integer format

probably will send many overworked

developers back to old course notes.

But, it’s not what you need anyway, so

turn it off by using an explicit signed-

signed integer form of the 21k multi-

plication instruction, R0 × R1 (SSI).

Now the 21k processor is behaving

normally (see Photo 3). The 32-bit

operations 2 + 3 = 5 and 2 × 3 = 6 work,

even if the direct interpretation of the

32-bit values are distorted by storage

in the 40-bit SHARC data registers.

FLOAT OPERATIONS VIA INTE-

GER INSTRUCTIONS

In Photos 2 and 3, floating-point

operations of F4 = 2.0 are implemented

with the integer assignment that states

R4 = bit pattern for the constant.

Op-code bits aren’t used to describe

a floating-point assignment instruction

when the assembler can use an integer

assignment in conjunction with gener-

ating the bit pattern needed to repre-

sent a floating-point number.

This can cause a nasty consequence.

Suppose you write F4 = 2, where 2 is

an integer rather than a float (2.0). A C

language compiler would do the

equivalent of automatically casting

this expression as F4 = (float) 2 to give

F4

= 2.0. However, there is no equiva-

lent checking of context in the White

Mountain 21k assembler. The result is

R4 = bit pattern of integer 2. That

would give F4 a floating-point value

around 10

–45

, which wasn’t intended

(see Photos 1, 2, and 3).

This problem is more insidious

when initializing floating-point arrays

for filter coefficients with syntax:

.var array[3] = {1.0, 2.0, 3};

Two coefficients will be correctly

initialized, but the third coefficient

will be unintentionally too small. A

changed assembler operation would be

helpful so that warning messages are

issued. Perhaps a language extension

could be added to allow automatic

type casting, adding values 1.0, 2.0, and

3

to the array:

.var float array[3] = {1.0, 2.0, 3};

EXPERIMENTS WITH FRACTIONS

Don’t ignore this fractional integer

format. It must be useful within the

concept of DSP applications, otherwise

it wouldn’t be the default mode of 21k

multiplication operations.

The user manual for Analog De-

vices’ ’2106X indicates that the proces-

sor can support two 32-bit fixed point

formats. But, unless you have a text-

book to help you understand the mate-

rial, it’s best to experiment.

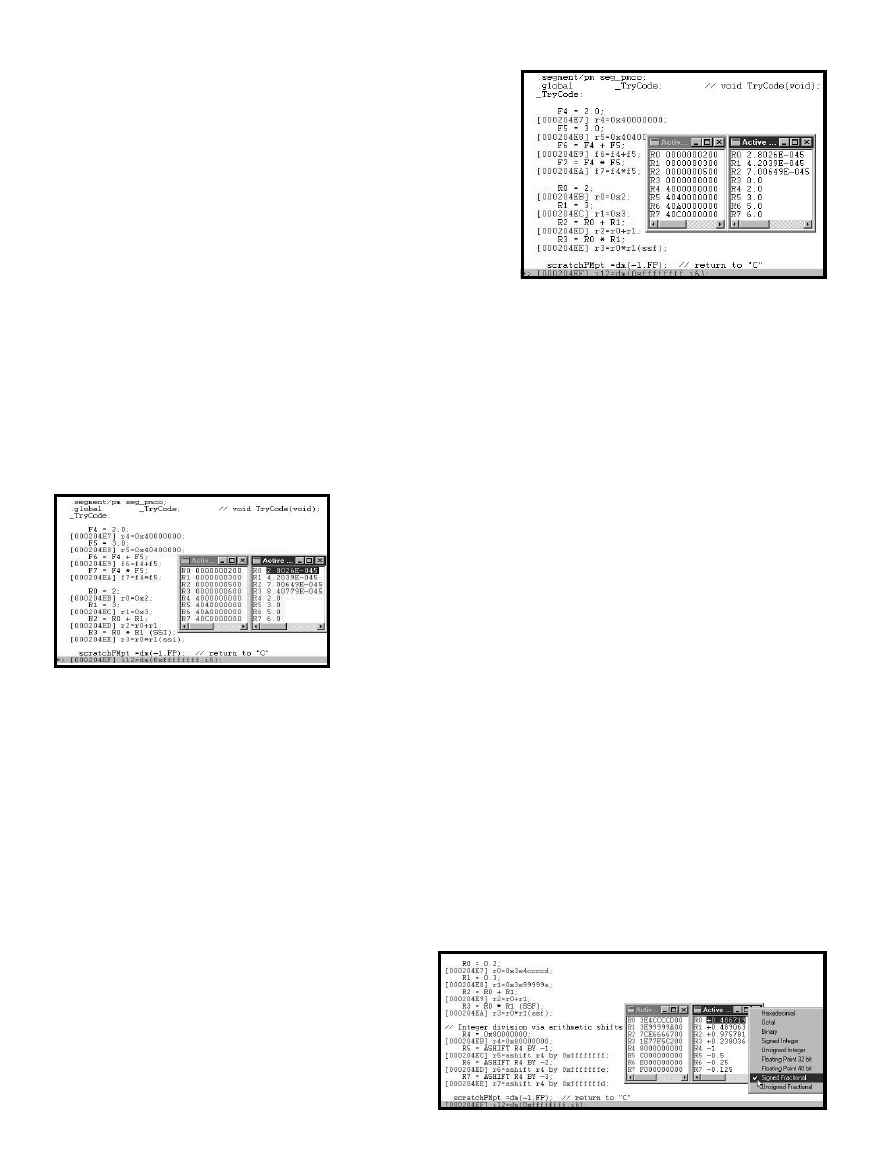

In Photo 4, an attempt has been

made to put fractional numbers into

integer registers and perform basic

addition and fractional multiplication

operations. The results in the data

registers are interpreted using the

signed fractional format available in

the VisualDSP development tool.

Now you’re heading in the right

direction. When compared to the ini-

tial signed fractional contents of the

registers, the final contents of the reg-

isters correctly indicate that:

0.4867 + 0.4890 = 0.9757

0.4867 × 0.4890 = 0.2380

The problem is that you were trying to

convince the processor to perform the

fractional operations:

0.2 + 0.3 = 0.5

0.2 × 0.3 = 0.06

FRACTIONAL INTEGERS

Setting the integer registers to frac-

tional values (R0 = 0.2 and R1 = 0.3)

doesn’t lead to the corresponding

signed fractional integer values (see

Photo 4). It’s strange that there isn’t a

built-in assembler directive to gener-

ate the bit patterns for fractional inte-

ger values. Miscalculating the

necessary hexadecimal bit patterns for

fractional values has been a constant

source of errors in my group.

But, a sensible relationship among

fractional integer values and their

hexadecimal representations has ap-

peared. Registers R5 to R7 contain the

results of applying a series of arith-

metic shifts (ASHIFT) to the greatest

negative 32-bit integer value

32-bit hex value

Fractional value

0x80000000

–1.0

0xC0000000

–0.5

0xE0000000

–0.25

0xF0000000

–0.125

Table 1—

Look at the relationship between the

internal hexadecimal representation and the 32-bit

integer value expressed as a signed fractional

value.

12-bit

Fraction of full-

hex value

scale A/D voltage

0x800

–1.0

0xC00

–0.5

0xE00

–0.25

0xF00

–0.125

0x000

0.0

0x100

0.125

…

…

Table 2—

The integer value from a 12-bit A/D

converter can be expressed as a signed value that

represents a fraction of the full-scale A/D converter.

Photo 5—

Most signed-signed

fractional multiplication operations

lead to the anticipated result.

However, the signed-signed frac-

tional multiplication of –1 and –1

would lead to the invalid result of

–1. The problem often can be

solved in an algorithm by using the

SHARC 80-bit accumulator associ-

ated with the integer multiplier.

16

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

(0x80000000) in register R4. Using a

negative value with the 21k ASHIFT

operator produces an arithmetic right

shift, which is equivalent to signed

integer divisions by two (see Table 1).

A similar pattern of bits will be

familiar to developers who have spent

time hooking up a 12-bit A/D to the

data bus of a processor (see Table 2).

This equivalence suggests that one

way of looking at fractional signed

integers is to interpret the bit pattern

as a fraction of the magnitude that

can be represented in a signed, two’s

complement number representation.

Photo 5 shows that this is a con-

sistent interpretation with:

–0.5 × –0.5 (SSF) = 0.25

–0.5 × 0.5 (SSF) = –0.25

–1.0 × 0.5 (SSF) = –0.5

Photo 5 also hints that a deeper

understanding of fractional integer

representation is needed for proper

algorithm development because:

–1.0 × –1.0 (SSF) = –1.0

Fixing this problem in an algorithm

by using the 80-bit accumulator associ-

ated with the SHARC integer multi-

plier is the subject for another article.

21K FLOATING-POINT DIVISION

The AMD ’29050 processor has an

11-cycle, floating-point division in-

struction, FDIV. But, that instruction

complicates 29k assembly coding,

because it is slower than other 29k

floating-point operations and more

difficult to pipeline efficiently.

The majority of the 21k processor’s

instructions complete in a single cycle,

leaving no place for a slow, floating-

point division operation. The presence

of the 21k reciprocal instruction,

RECIPS, suggests a two-stage division

operation. First, the reciprocal of the

denominator is calculated in one cycle,

then the numerator is multiplied by

this reciprocal in a second cycle.

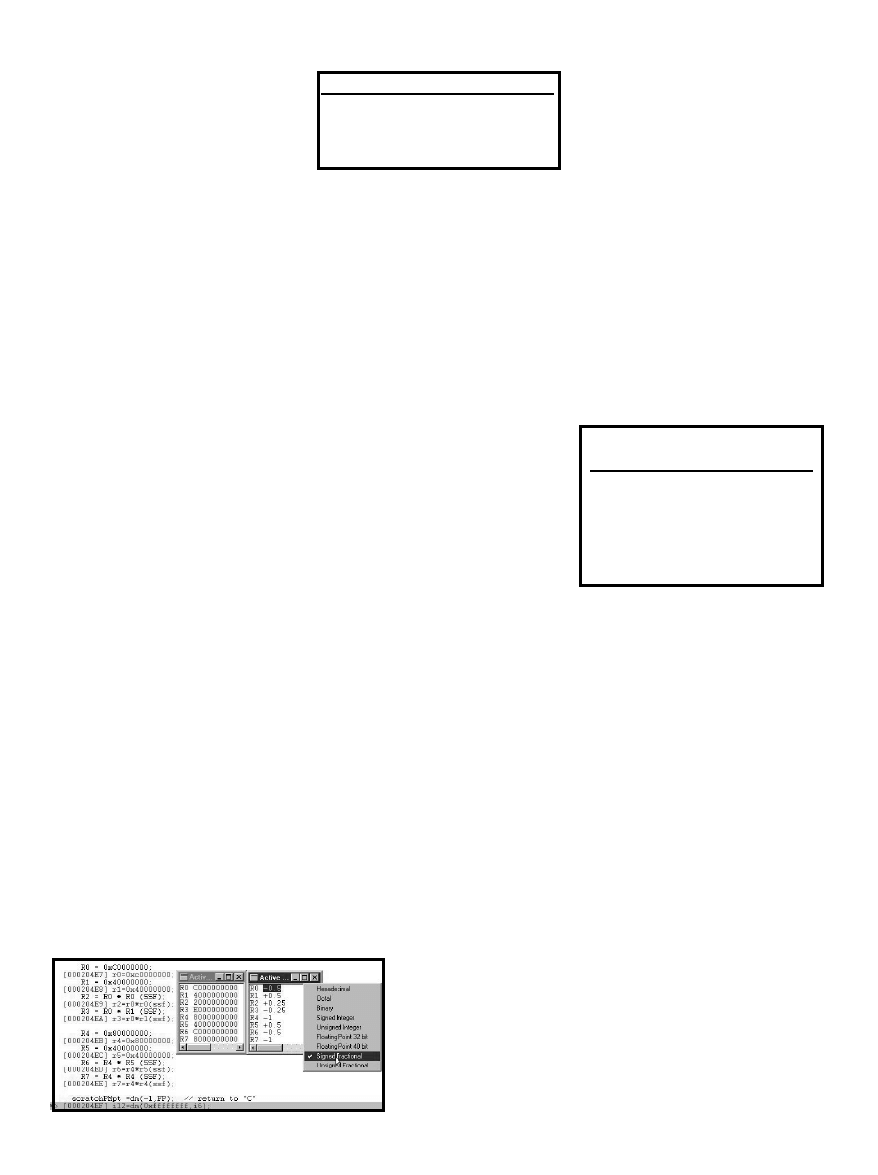

This approach doesn’t seem to work

using the RECIPS instruction (see

Photo 6). The approach, however, does

work if the reciprocal is directly evalu-

ated by hand.

This behavior is a result of the fact

that a ROM look-up table is needed for

reciprocals to be calculated in a single

cycle. High-accuracy reciprocals re-

quire an enormous amount of silicon.

Instead, a limited accuracy approxima-

tion (seed) of the reciprocal is calcu-

lated. For more information, read the

users manual. Comparing the hexadeci-

mal representations of the reciprocal

seed (F2) and the true reciprocal (F4)

reveals the limited accuracy of the

result from the RECIPS operation.

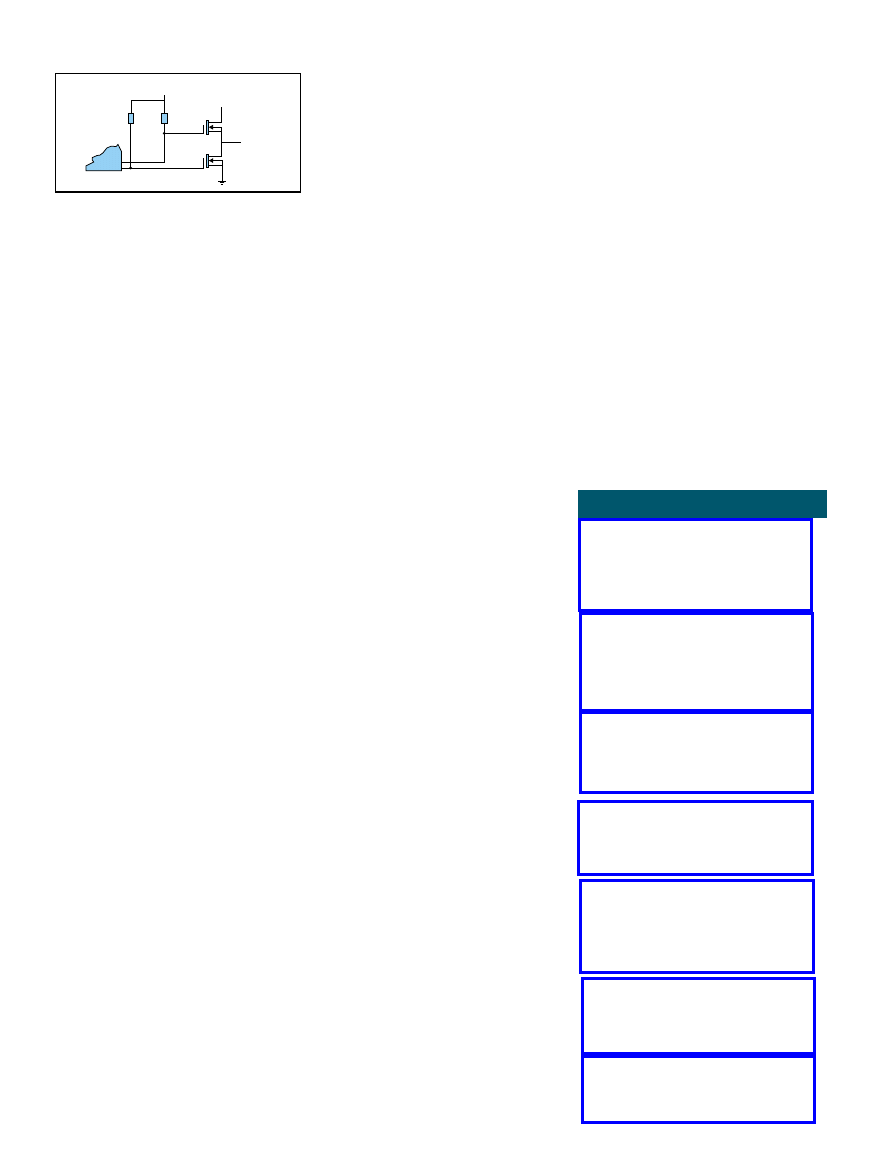

Photo 7 shows how a float-

ing-point division can be ob-

tained in eight cycles using the

super-scalar capability of the

SHARC processor and an itera-

tive convergence algorithm. [2]

A ±1-LSB accurate, single-preci-

sion quotient can be obtained

s

bexp—biased exponent

frac—fractonal field

31 30

23 22

0

Photo 6—

The

SHARC RECIPS

instruction provides

a limited accuracy

reciprocal seed

value in a single

cycle from a ROM

look-up table.

Photo 7—

A convergence algorithm is used to calculate

a floating-point division in eight cycles using the super-

scalar SHARC instructions.

Figure 1—

The representation of an IEEE standard floating-point

number takes 33 bits: one bit for the sign, 8 bits for the biased

exponent, and 23 bits for the fractional field. The thirty-third

normalization bit is hidden, not stored. s is the sign field, bexp

is the biased exponent field, and frac is the fractional field.

CIRCUIT CELLAR

®

Issue 127 February 2001

17

www.circuitcellar.com

after only six cycles. The choice

of data registers for the algorithm

is a consequence of the SHARC

architecture, which only allows

super-scalar operations among

certain banks of data registers.

CUSTOM DIVISION INTEGER

AND FLOATING POINT

As discussed, a fast, accurate

division instruction requires a

considerable amount of silicon.

Because most algorithms involve

only a few divisions, a compro-

mise is to have a slow instruction

(AMD 29k) or an iterative proce-

dure available (ADSP 21k).

One exception to this rule is

that division by powers of 2 (4, 8,

16…) happens frequently. Such

operations are needed to scale

integer inputs to ensure that the

algorithm does not overflow its

number representation, as

Laurence Turner and I discussed

in “Make Your Data Comfortable,

Get Bit Cushions,” (Circuit Cellar

125). Floating-point scaling by

Photo 8a—

Fast floating-point division by a factor of 2 can be imple-

mented via a single-cycle integer subtraction rather than an eight-

cycle iterative division. However, additional checks must be added

for accuracy.

b—

If the checks are incorrectly handled, the code

takes six or eight cycles as the SHARC’s instruction pipeline stalls.

a)

b)

powers of 2.0 is necessary for

outputs from algorithms such as

the inverse Fourier transform.

On the integer side, single-

cycle 21k arithmetic left and

right shifts can handle scaling by

powers of 2 (see Photo 4):

// Fast integer division R0 =

R1 / 16

R0 = ASHIFT R1 BY –4

However, floating-point numbers

are represented in a more com-

plex manner using three different

bit fields within a 32-bit register.

So, the shift approach for integers

must be changed to an equivalent

but different operation to achieve

floating-point scaling. This opera-

tion requires detailed under-

standing of the IEEE floating-

point number representation.

Figure 1 shows the 32-bit

representation of the three fields

of a floating-point number. Every

valid floating-point number can

be represented using format:

CIRCUIT CELLAR

®

Issue 127 February 2001

19

www.circuitcellar.com

SOURCE

ADSP21061 SHARC processor,

Analog Devices, Inc.

(800) 262-5643

(781) 329-4700

www.analog.com

REFERENCES

[1] Analog Devices, ADSP-2106x

SHARC User’s Manual

, 2d ed.,

1996.

[2] J. Cavanagh, Digital Computer

Arithmetic

, McGraw-Hill, New

York, NY, 1984.

Michael Smith is a professor at Uni-

versity of Calgary, Canada where he

teaches and researches introductory

and advanced microprocessor topics.

You can reach him at smithmr@

ucalgary.ca.

(–1)

s

× 1.frac × 2

(bexp – 127)

Figure 2 illustrates the transformation

of the decimal number 34.0 until it’s

stored as an floating-point value in

hexadecimal format.

Check out Table 3, which shows the

IEEE standard representation of pairs

of floating-point numbers. When bro-

ken into the three floating-point fields,

it’s easy to understand why pairs of

floating-point numbers that are scaled

by a factor of 16.0 differ by a fixed

value of four in their biased exponent.

With this information, a fast float-

ing-point scaling operation can be

handled through a single-cycle, sub-

traction integer operation that directly

adjusts the bexp bits of a floating-point

number (see Listing 1).

In principle, floating-point scaling

via integer operations can be imple-

mented on any processor, but does it

work? Photo 8a shows the code and

results for a series of floating-point

numbers divided by 16.0 in a single

cycle, rather than the eight cycles for a

standard SHARC division. The opera-

tion works well for scaling 4.0, –2.0,

and 1.0, but has a problem scaling 0.0.

The problem with 0.0 is that its

biased exponent is too small to allow a

valid floating-point number to be gen-

erated after four is subtracted to per-

form the fast scaling operation. This

problem didn’t occur with the integer

scaling operation using arithmetic

shifts. If the scaling factor was too

large, the significant bits were shifted

out of the value to leave zero. Some-

thing equivalent needs to happen for

the fast, floating-

point operations.

The scaling

approach works

when you can guar-

antee that every

number used has a

magnitude greater

than 2

(p –127)

, where

p

is the power of 2

by which you are

scaling. Photo 8b

shows two versions of a modified scal-

ing operation incorporated in the tests.

The first algorithm is slow (six cycles)

as the SHARC’s instruction pipeline is

exposed by the conditional jumps. The

second algorithm uses the SHARC’s

conditional compute and super-scalar

statements to avoid pipeline stalls

(three cycles).

You have now implemented an

accurate floating-point scaling opera-

tion that works faster at three cycles

than the standard eight-cycle SHARC

division. Was it worth the effort?

Nope! It’s just a neat party trick. If

you want to scale floating-point regis-

ters F0, F2, F4, and F6 by 16.0, the

simplest algorithm involving single-

cycle operations is:

F8 = 0.0625; // reciprocal of 16.0

F1 = F0 × F8;

F3 = F2 × F8;

F5 = F4 × F8;

F7 = F6 × F8;

WRAP UP

In this article, I discussed a number

of the characteristics of the Analog

Devices ’21061 SHARC processor.

These included internal representation

of integers, an unexpected default

setting for integer multiplication op-

erations, and a brief introduction to

fractional integers.

On the floating-point side, a tech-

nique was discussed for performing a

floating-point division in the absence

of a fast FDIV instruction. Details of a

faster, custom, floating-point scaling

operation were demonstrated using

conditional compute and super-scalar

instructions.

I

Author’s Note:

I thank Con Korikis of

Analog Devices University Support

and Tony Moosey of SHARC DSP

tools support.

Number

Internal hex

s

FP fields

FP representation

bexp

frac

1

0x3F80 0000

0

0x7F

0x00 00 00

16

0x4180 0000

0

0x83

0x00 00 00

–1

0xBF80 0000

1

0x7F

0x00 00 00

–16

0xCF80 0000

1

0x83

0x00 00 00

63.9625

0x427FD99A

0

0x84

0x7F D9 9A

1023.4

0x447FD99A

0

0x88

0x7F D9 9A

Table 3—

Floating-point numbers that differ by a scaling factor of 16.0 have

32-bit representations with biased exponent fields (bexp) that differ by 4. All

the other fields remain the same.

Conversion to binary value

34.0 = %100010

Conversion to 1.frac binary format

%100010 = %1.00010 × 25

Conversion to biased exponent format

%1.00010 × 25 = %1.00010 × 2(132 -127)

Identification of the 3 IEEE FP fields

s = %0 = 0x0

bexp = 132 = 0x84 = %1000 0100

frac = %000 1000 0000 0000 0000 0000

= 0x100000

Representation of 34.0 in 32-bits

= %0 1000 0100 000 1000 0000 0000 0000 0000

= %0100 0010 0000 1000 0000 0000 0000 0000

= 0x42080000

Figure 2—

The decimal number 34.0 goes through a

series of stages to identify the three floating-point

bit fields before being stored as the 32-bit value

0x42080000.

// Setup of BEXP adjustment factor

R0 = 4;

R0 = ASHIFT R0 BY 23

F4 = 1023.4;

// Integer operation to perform

// a single cycle FP division by 16.0

R4 = R4 – R0;

Listing 1—

Single-cycle FP division implements using integer operations.

20

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

a

n altimeter is a

useful tool, espe-

cially for the outdoor

enthusiast. The

altimeter’s capabilities make it ideal

for trips, hiking, biking, and other

hobbies. In this article, I’m going to

describe an easy and inexpensive al-

timeter that includes a thermometer

and barometer.

This altimeter operates according

to the physical law that states atmo-

spheric pressure decreases with in-

creasing altitude. Both ambient

temperature and actual pressure can be

measured by the altimeter.

In addition, it has memory for 9 h of

data. So, when you return from a trip,

you can download the accumulated

data to a PC and read a profile of your

trip. The resolution

of the altimeter is

around 1 meter. It

recognizes if you lift

it from the floor to

your desktop! The

timing to make a

calculation is better

than with GPS tech-

niques, and it does

not need signals

from satellites.

One possible disadvantage is that

the altimeter can be affected by a baro-

metric pressure change. However,

experience shows it’s not a problem.

The altimeter is based on a P89C52

microcontroller, which collects and

calculates data from the temperature

and pressure sensors. Table 1 lists the

technical parameters.

CIRCUIT DESCRIPTION

The altimeter (see Figure 1) uses a

basic natural law that says atmo-

spheric pressure decreases with in-

creasing altitude. The basic formula is:

[1]

Three variables, T, p

0

, and p, have to be

measured. The first, T, is the ambient

temperature in Kelvins. p

0

is the atmo-

spheric pressure at zero level. And p is

the atmospheric pressure at the current

level. The remaining values are fixed

constants; R is the universal gas con-

stant (286 Joule/Kg/K) and g is the

gravitational acceleration (9.81 m/s

2

).

The altimeter measures T and p and

then recalculates actual pressure,

which is measured directly. Altitude

(based on Equation 1) is recalculated.

The ambient temperature could be

replaced by a standard value with

0.8

°

C decrease per 100 meters, but it’s

useful during a trip. Moreover, the A/D

converter has eight inputs available.

A similar principle can be used in

airplanes to measure speed using a

Pitot tube, but that was not the pur-

pose of this design.

The basic component in the altim-

eter is an MPX4115 absolute pressure

sensor. It provides calibrated output

voltage directly proportional to atmo-

spheric pressure. [1] Output voltage is

determined by:

FEATURE

ARTICLE

Radek Vaclavik

Whether you’re on

the road again or just

out to climb every

mountain, you’ll find

Radek’s digital altim-

eter project to be

quite practical. The

Design2K judges liked

it enough to award

him second place, so

take a look at what

went into the project.

An Altimeter for the

Traveling Man

Resolution of altimeter

1 meter

Usable altitude

0 to 2000 m

Barometer range

700 to 1100 hPa

Thermometer range

–30 to 30°C

Thermometer accuracy

1°C

Memory

10 h of data

Power supply

2.4 to 3.0 V, AAA batteries

Power consumption at 5 V

26 mA, 15 mA, 9 mA

DC/DC converter efficiency

70 to 80%

Table 1—

The basic parameters of the altimeter demonstrates a stable

resolution of 1 m.

CIRCUIT CELLAR

®

Issue 127 February 2001

21

www.circuitcellar.com

Value from altimeter

± difference

Absolute altitude

255

–1

368

1

1

369

0

0

369

0

0

369

2

2

371

253

–3

368

0

0

368

V

out

= V

s

(0.009 × P – 0.095) [2]

where V

s

is the supply voltage and P is

pressure in kilopascals (kPa).

The component’s sensitivity helps

determine the resultant resolution of

the altimeter. It is about 4.9 mV/hPa

for the MPX4115. Using Equation 1

and elementary mathematics, you can

determine that at a normal tempera-

ture, a 1-hPa drop is equal to about 8

meters. Conversely, a 1-meter change

in altitude causes about a 0.6-mV

change in output voltage.

All that remains is to determine the

necessary resolution of the A/D con-

verter. For a reference voltage of 5 V

and 1-meter resolution, you need:

[3]

This can be provided by a 13-bit con-

verter because 2

13

= 8192.

Many inexpensive 12-bit converters

are available. I used the AD7888 from

Analog Devices. If you use a 16-bit A/D

converter, theoretically you’ll get 14-

cm resolution. Remember that there

are more strict requirements for the

reference voltage stability, grounding,

blocking, and so on. Also, these convert-

ers are more expensive.

Another solution for better resolu-

tion is to amplify a signal from the

sensor using an op-amp. I use this

method in the altimeter.

The available power

supply limits this solu-

tion. With a 5-V power

supply and the required

altitude range, you can

use a maximum amplifi-

cation factor of 2.2.

Think about the

whole range of common

atmospheric pressure

(750 to 1100 hPa) and its

drop at an altitude of 2000 meters (see

Figure 2). The final range is from 600,

the lowest pressure at 2000 meters

with low atmospheric pressure, to

1100 hPa, the highest pressure at

0 meters with high atmospheric pres-

sure. When using Equation 2, you need

to process voltages from 2.3 to 4.6 V.

A complete diagram is shown in

Figure 3. The altimeter uses an

MC33502 op-amp IC6b. It is a

rail-to-rail type with a high-

input impedance. Its output

voltage can swing within 50 mV

of each power supply rail. Ampli-

fication is given by:

[4]

The input and output of IC6b

are measured relative to the

3.1625 VDC offset from the R3,

R2 divider at its non-inverting input.

The output is inverted, but isn’t a factor

because Equation 1 can be modified.

The resolution of the A/D converter

is increased by repeated measurement

and averaging of all values. The current

program version uses 256 cycles. Low-

pass filter R14 and C5 decreases the

noise of the sensor and maintains the

stability of the displayed value. [2]

The output is connected to the first

input of A/D converter IC2. The con-

verter uses a reference voltage equal to

4.6 V. The 4.6-V level

is a result of the altim-

eter’s power supply

level. Because you need

a few millivolts above

the reference voltage to

ensure good stabiliza-

tion, a 2.5-V program-

mable reference TL431

(D1) is used with am-

plifier IC6a.

The second input of the A/D con-

verter measures temperature. I used

the KTY81 (R13) sensor that forms a

divider with R12. R13’s resistance is

2000

Ω

at 25

°

C. The voltage reference

biases the divider. The output voltage

is proportional to ambient tempera-

ture. The basic resistance dependence

on temperature is approximated by a

second-order polynomial that’s calcu-

lated by microprocessor IC1. [3]

The third input is used for sensing

the 2.4-V power supply voltage. If the

battery voltage goes too low, then the

5-V power supply voltage will also

drop below 5 V. Values less than 5 V

will distort all measured data. If the

voltage is less than this limit, the al-

timeter will display a battery warning.

The A/D converter sends data

through a four-wire bus to the

microcontroller IC1 (P89C51), which

processes and calculates all formulae.

Equation 1 is easy to process on a cal-

culator, but not on a microcontroller;

programming is difficult if you use

only an assembler. Fortunately, com-

pilers can convert C language to binary

code, thereby making implementation

of a logarithmic function easier.

For the main program, I also used C

language in combination with assem-

bler routines for communication with

the display, memory, and A/D con-

verter. Figure 4 shows the flowchart.

All calculated data is displayed on

IC8, a 1 × 16 character display, which

is controlled via a 4-bit data bus and a

two-wire control bus. These wires are

shared with the A/D converter bus.

The display is the largest component

in the altimeter and could be replaced

by similar smaller types. The advan-

tage of using a common 1 × 16 display

is its availability and price.

Pressure

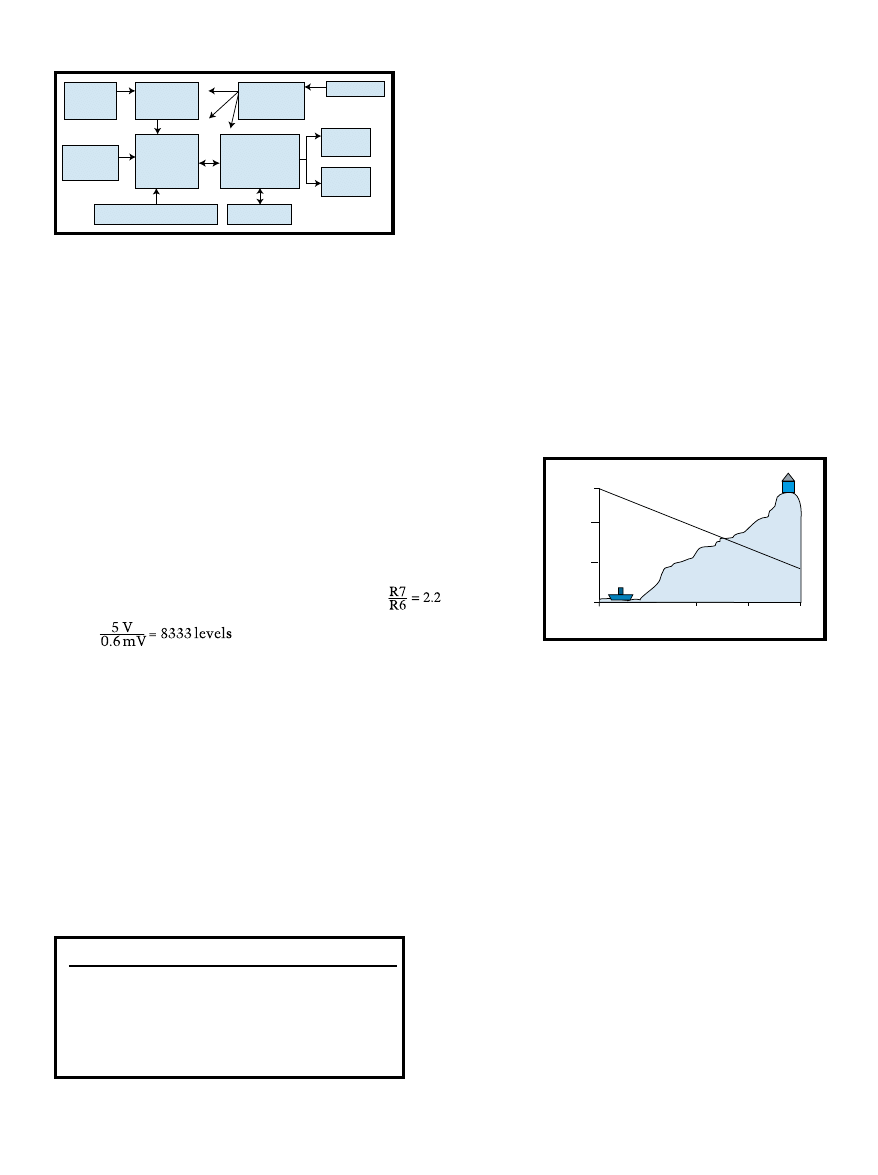

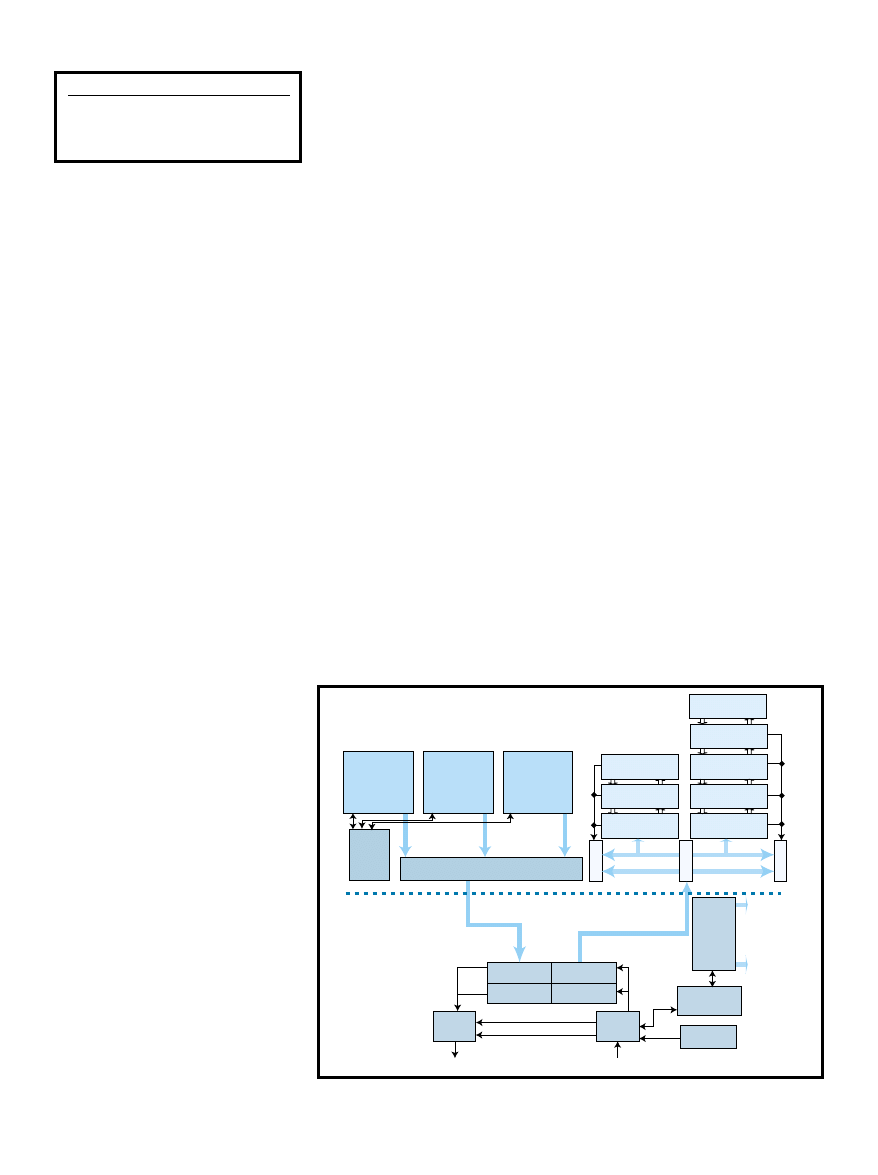

sensor

MPX4115

Amplifier

low-pass filter

DC/DC

Converter

MC33463

Battery

Display

1 × 16

RS-232

Interface

EEPROM

Microcontroller

P89C51UBPN

8-Channel

12-bit A/D

converter

AD7888

Reference and amplifier

Temperature

sensor

KTY81

5 V

2.4 V

4.6 V

0

500

1000

1500

2000

Sea level

1000

900

800

700

Pressure

Pressure (hP

a)

Altitude (m)

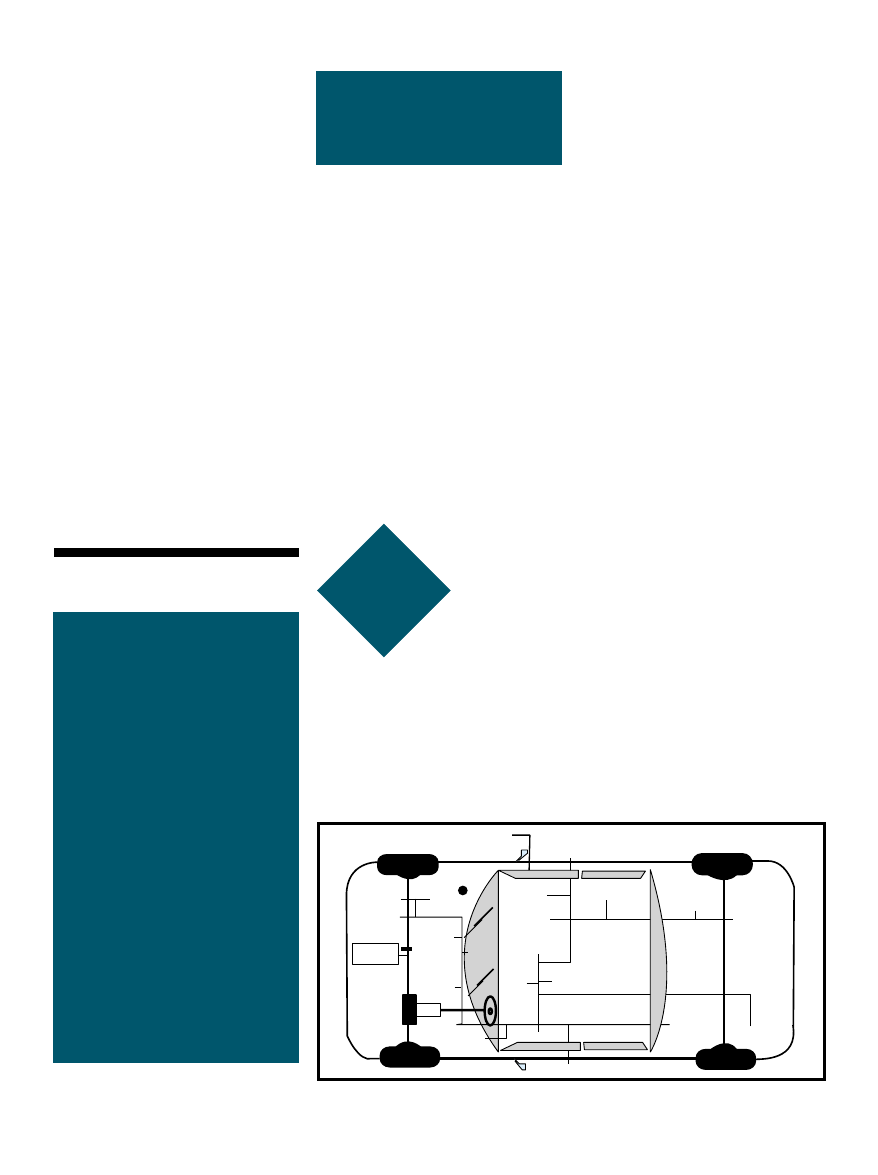

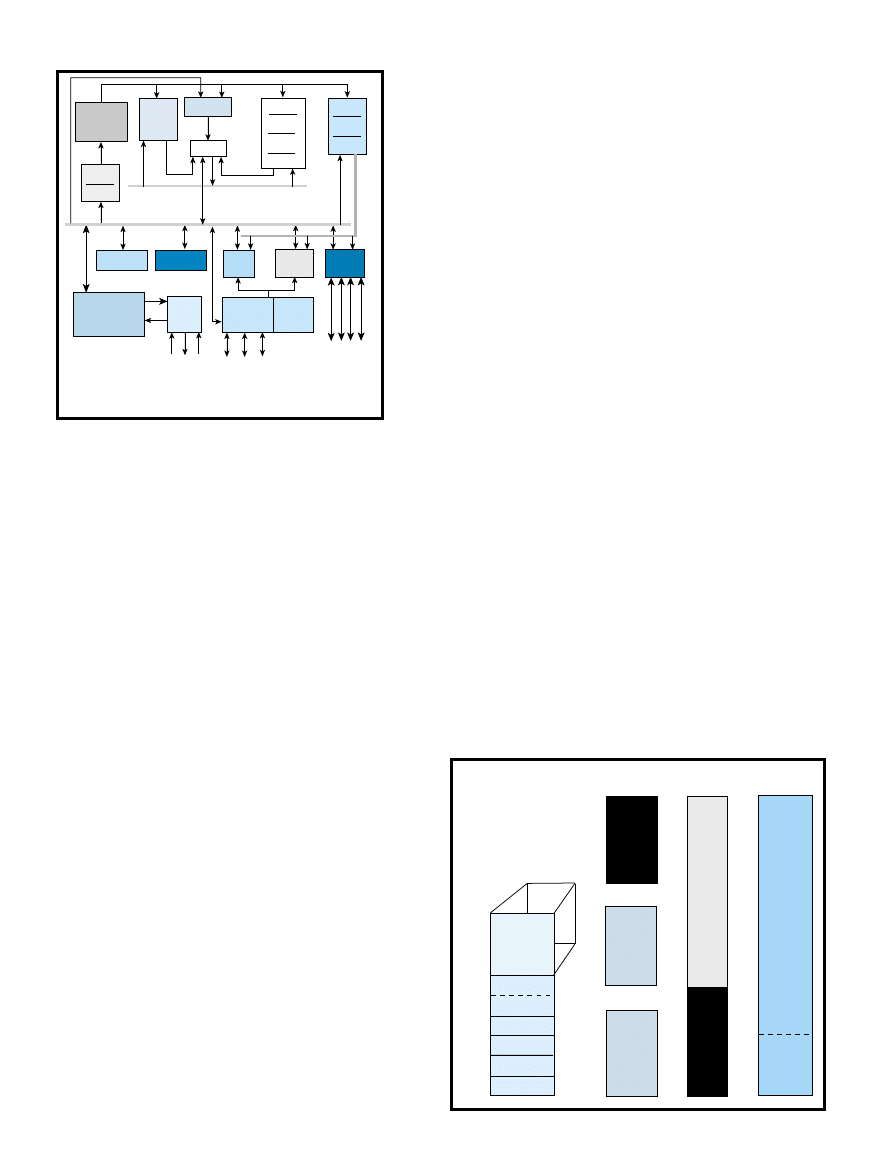

Figure 1—

The altimeter and Philips’s P89C51 microprocessor control

the display, memory, A/D converter, and RS-232.

Figure 2—

This illustrates the value of the pressure de-

crease with increased altitude based on Equation 1.

Table 2—

An example of data shows input value from the altimeter,

recalculated difference, and recalculated altitude.

22

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

The altimeter provides the follow-

ing values: actual temperature, actual

atmospheric pressure, altitude, free

memory (as a percentage), and trip

duration in minutes. These outputs are

measured every 2 s and can be changed

periodically by pressing the Mode

button. Pressing the Set button while

any value is displayed sets a zero alti-

tude. Then, the altimeter switches to

show altitude (see Figure 5).

The altimeter also stores altitude

information and can download data to

your PC. Data is stored in EEPROM

memory IC9, which is controlled via

the I

2

C bus. Altitude data is stored

every 16 s; and with 2 KB of memory,

it can store 9 h of trip data. The sample

rate can be changed to a shorter period

of time, decreasing the capacity but

providing better resolution.

The Mem button is used to start

storing data in EEPROM memory. At

any time, you can interrupt or stop

storing data by pressing Mem again. If

data is being stored, an apostrophe is

shown in the display’s last position.

Also shown is the amount of free

memory. After exceeding maximum

memory capacity, the microprocessor

automatically stops storing data.

Data can be transferred simply to a

PC. T2 inverts the serial output from

the microprocessor. All common serial

ports are able to receive data with

levels of 5 or 0 V instead of ±12 V.

Importantly, this saves one integrated

circuit (i.e., MAX232).

Pressing the Mem button during

powerup initiates transfer of data to

the PC. After termination of the trans-

fer, the altimeter switches to its com-

mon function. Data format and data

processing will be described later.

There are two displayed values that

need calibration. First, you need to

calculate the correct value of R12 for

temperature. And, the atmospheric

pressure needs to be calibrated because

sensor IC7 varies from unit to unit.

The altimeter offers a special calibra-

tion menu that is started by pressing

Mode during powerup.

The calibration constants are in

integer format. You can increase or

decrease values by pressing the Mode

(+1) or Set (–1) buttons. When the cor-

rect value appears, pressing the Mem

button will switch to pressure calibra-

tion. Pushing it again will save data in

EEPROM memory and switch the

altimeter to common operation.

These constants are reloaded after

each start and are used for all calcula-

tions. The advantage of using EEPROM

is that you don’t need to modify the

master program or program the

EEPROM in a special programmer.

The best way to determine constant

values is to set them to zero, switch on

the altimeter, and write down the

difference between displayed values

and correct values. Then switch power

off and on and store these values in the

altimeter’s memory.

The altimeter can be powered by

2.4 to 3.0 V. IC3 is a DC/DC converter

MC33463 with a variable frequency.

[4] It uses accumulating coil TL1 and

filtering capacitor C6. This converter

doesn’t function with input voltages

greater than 5 V.

I use two rechargeable AAA, NiMH

batteries, but you can use AA depend-

ing on box size. Now, these batteries

have capacities as high as 550 mAh.

TL1’s resistance determines final

efficiency. A common SMCC choking

coil could be used. It gives about 75%

efficiency, but some special coils with

low resistance give about 80% effi-

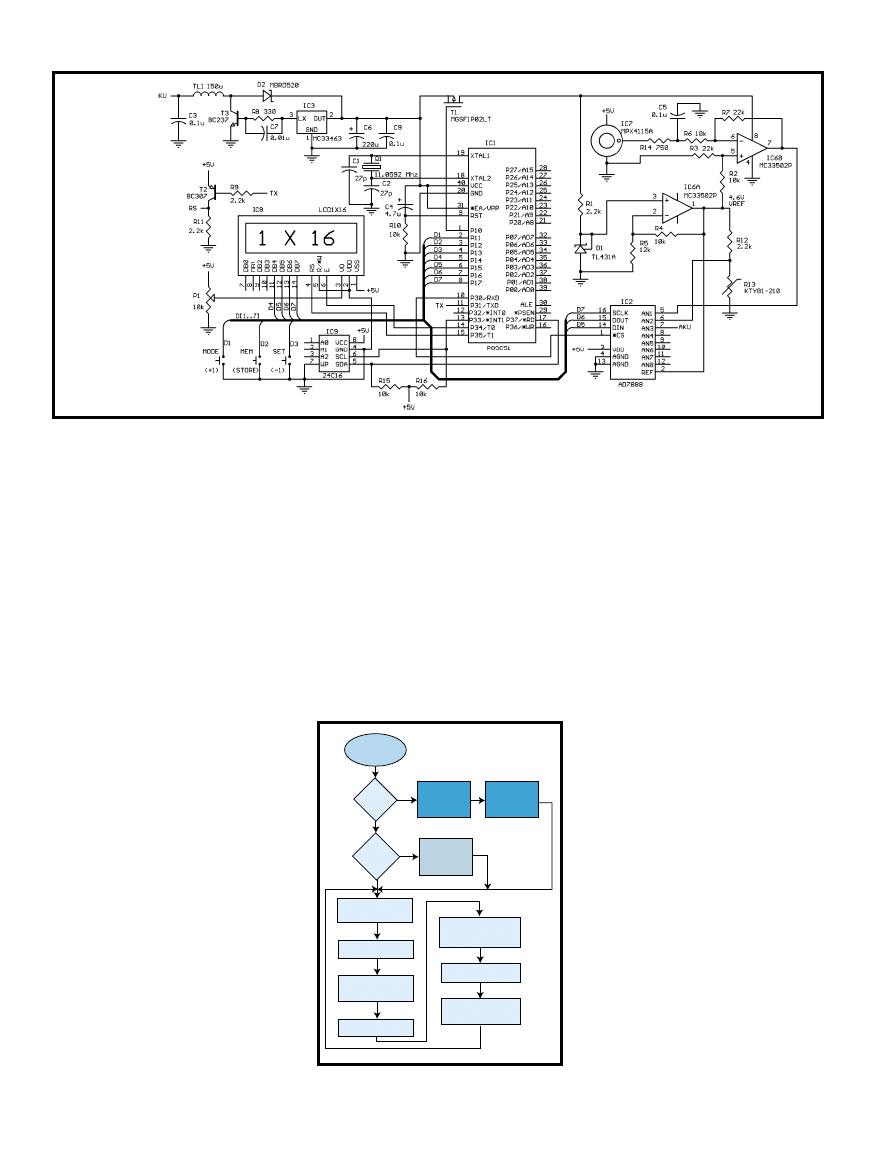

Figure 3—

This

detailed schematic

of the altimeter

clearly shows the

architecture from

Figure 1.

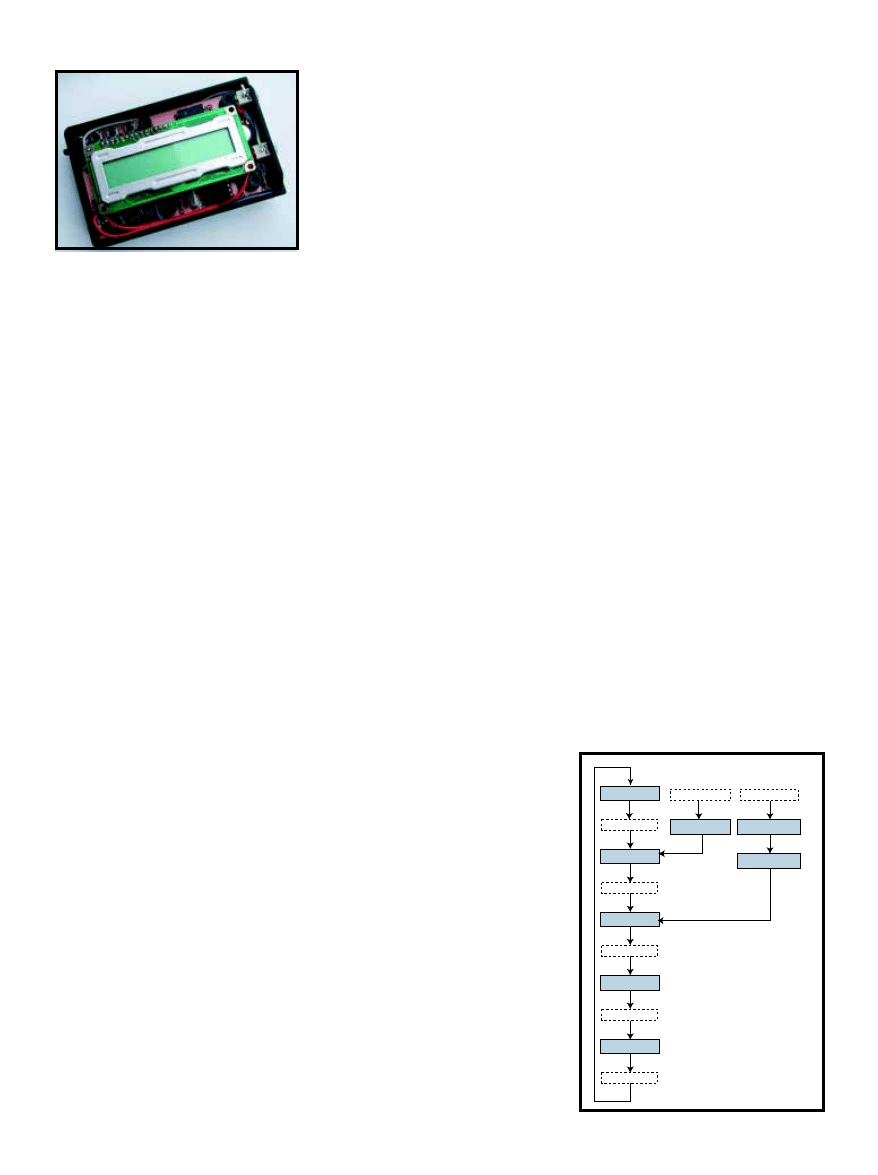

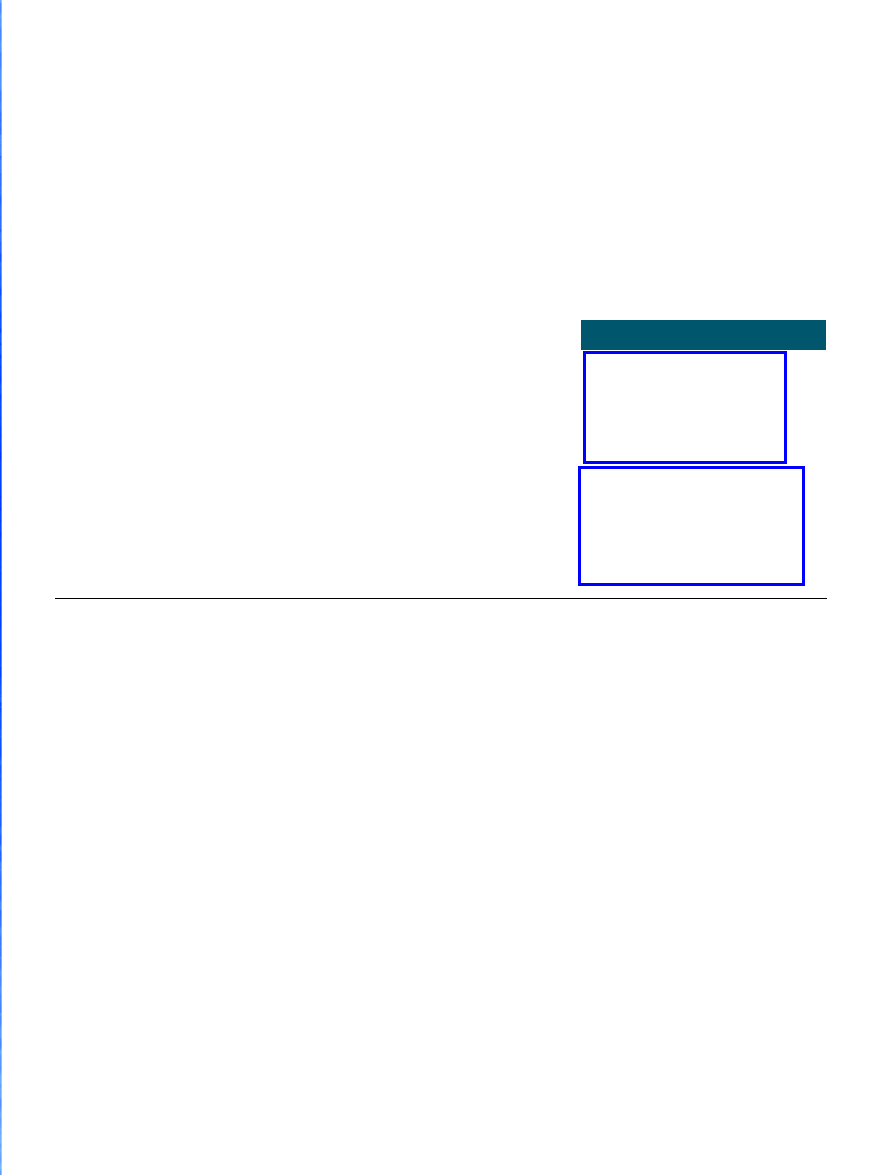

Start

Set?

Memory?

Input

calibration

data

Send

data to PC

Store

data to

EEPROM

Switch on

sensor BIAS

Measure data

Switch off

sensor BIAS

Calculate values

Display values and

store to memory

Idle mode

Wait 2 s

Figure 4—

The flowchart of the altimeter shows the

main tasks of the microcontroller. Tasks include

control of the power for the sensor and Idle mode.

24

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

These short spikes are not visible in

Figure 6. Note that the current con-

sumption is about 9 mA. The cycle is

repeated every 2 s.

DATA PROCESSING

The altimeter sends data to the

serial port in standard format 8N1 (8

bits, no parity, 1 stop bit) at 9600 bps.

Any terminal program can receive

data; I use Hyperterminal from Win-

dows. The altimeter sends data sepa-

rated by a CR char (ASCII code 13). Set

the terminal to add an LF (ASCII code

10) so that data will be separated in

lines. Then, save the data.

The altimeter stores only the differ-

ence between the current value and the

last measurement because it saves

memory. Each value is 7-bits long and

the eighth bit is the sign. This means

that the altimeter can recognize a

change between the last two measure-

ments from –127 to 127 meters.

As I mentioned, I use Microsoft

Excel to process all of my data. Cur-

rently, I’m working on a macro that

will automatically process data and

create a chart. Soon it will be available

for free on my web site. For now, you

have to do it manually.

Now let’s look at an example of

data from my first trip. Two easy for-

mulae are implemented in the columns

of Table 2:

± Difference = IF(A1>127, (YES) A1-

256, (NO) A1)

where A1 is the cell with value from

the altimeter. The second formula is:

Absolute altitude = C0 + B1

where C0 is the previous altitude and

B1

is calculated difference.

You can use Table 2’s last column

to prepare a chart. Figure 7 is an ex-

ample of a profile of my first trip with

the altimeter.

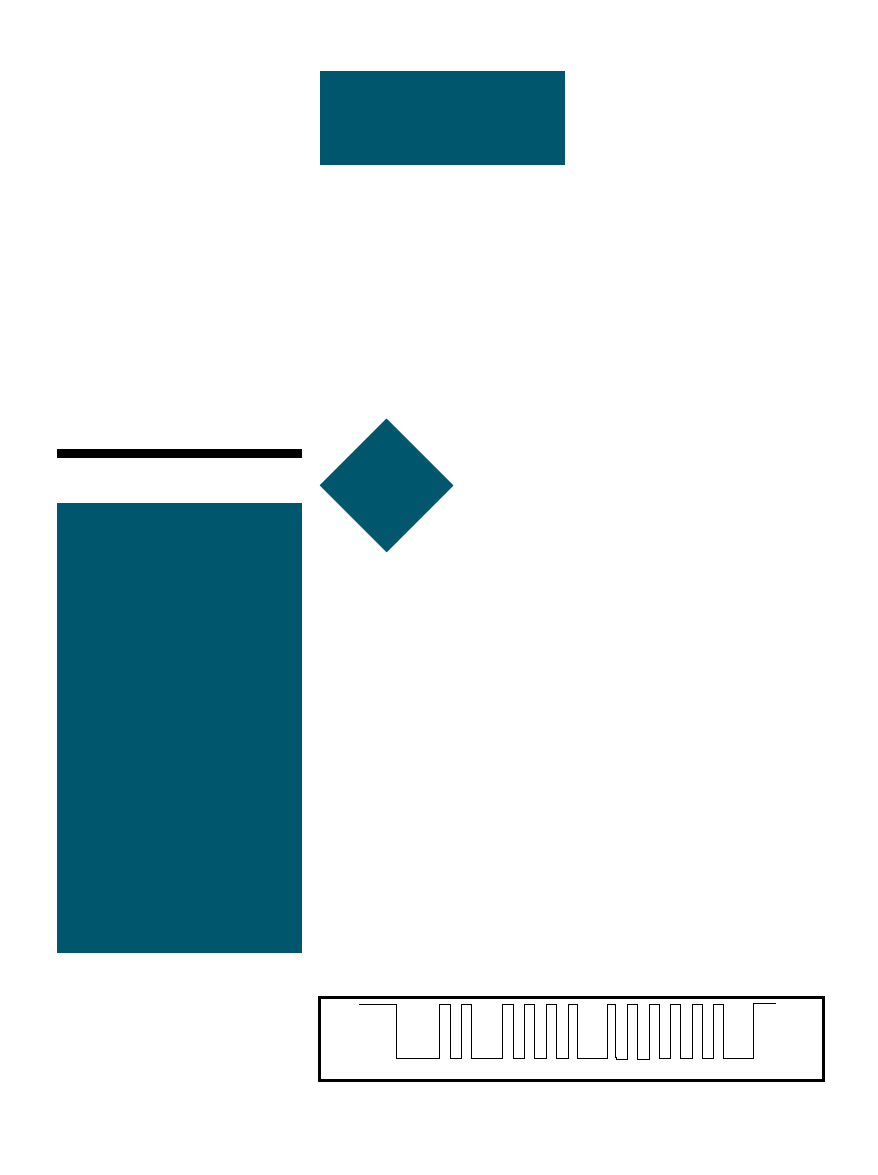

BATTERY CHARGER

I also developed an easy-to-con-

struct fast charger for NiCd and NiMH

batteries used in the altimeter. I

looked for the simplest solution (see

Figure 8). The charger is based on an

MC33340, which was designed for

quick charges. This device uses nega-

tive slope detection for the end of

charging. Nickel cadmium and NiMH

batteries show a small drop in the

output voltage when they are 100%

charged. The MC33340 controls charg-

ing by detecting this decrease.

There is a backup solution to stop

charging in case the batteries are dam-

aged. The solution is an independent

timer that’s controlled by pins T1, T2,

and T3 and can be set up to 283 min.

Another possibility of how to stop fast

charging is detecting a high tempera-

ture of the battery.

The charger has two operating

modes. The first one is a Fast Charging

mode that is terminated by the meth-

ods just described. A blinking LED

diode signals this mode. The charger is

switched to the second mode, Main-

tain, when the batteries are powered

with a low current and the LED glows

steadily. This current covers self-dis-

charging of batteries so that they are

always ready for use.

The MC33340 can control the

LM317 voltage regulator, which is

useful because you don’t need a stabi-

lized power supply with an exact out-

put voltage. A power supply that

provides up to 18 V is enough.

You need to perform a few calcula-

tions to determine the values of the

resistors. These calculations are simple

and can be used for other applications,

as well.

Mode

Mode

Mode

Mode

Mode

Set

Mem

Temperature

Altitude

Altitude = 0

Start recording

Add to display

Free money

Pressure

Trip duration

Figure 5—

Three buttons,

Mem, Set, and Mode,

enable you to use all of

the altimeter’s functions.

The latest version of the

software offers more

capability.

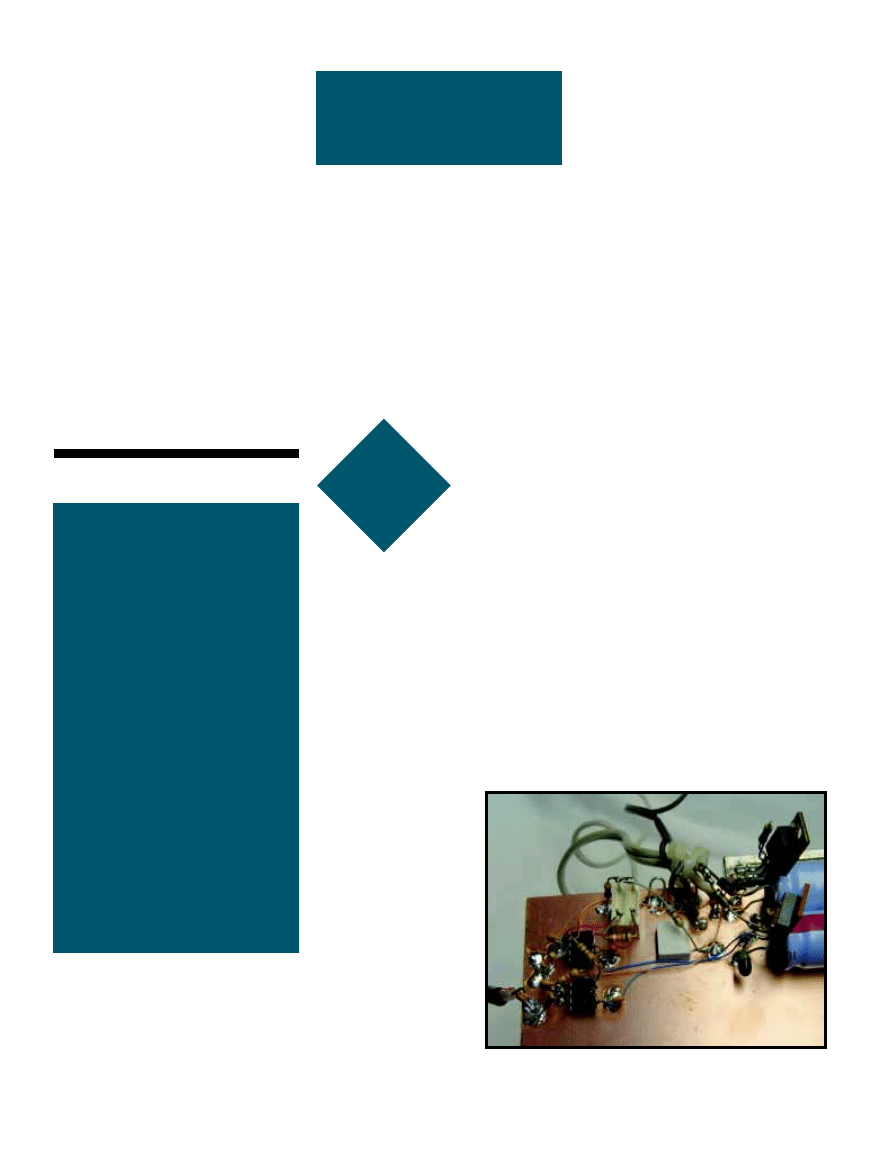

Photo 1—

When looking at the display mounting,

the EEPROM is visible at the bottom. Also notice

that two white connectors are used for the RS-232

and charger.

ciency. Previous versions of the altim-

eter used a converter with an internal

switch and about 60% efficiency.

Of course, the altimeter’s power

consumption is important. I measured

these values without using power man-

agement. The A/D converter consumes

0.5 mA, the LCD consumes 1 mA, the

op-amp and sensor consume 8 mA, and

the microcontroller consumes 10 mA.

Notice that the sensor and op-amp

use a large portion of the energy, but

are not powered all the time. That’s

why I implemented PMOS switch T1

and simple power management. The

op-amp, pressure sensor, and reference

are powered only during measurement,

every 2 s. Delay loops are imple-

mented in the program to avoid bad

readings from the sensor. Also, the

microcontroller idles when possible.

T1 is a TMOS P channel transistor

from ON Semiconductor with low

resistance and can be controlled di-

rectly by the microcontroller. The

transistor is turned on with 5 V on its

gate and turned off with 0 V.

Figure 6 shows the current con-

sumption of the altimeter at 5 V. It

shows three phases of the work of the

altimeter. During phase 1, the altim-

eter also powers the pressure sensor

and collects data from the A/D con-

verter. The current consumption is

about 26 mA.

The sensor is not biased during

phase 2. At this point, the processor is

active and calculates all of the data. It

takes about 130 ms and 15 mA from

the 5-V power supply. During the final

stage of Idle mode (phase 3), the inter-

nal timer wakes it every 50 ms. During

this short time period, the processor

checks for pressed buttons.

26

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

commence, thus protecting against bad

batteries. I selected R1 = 10 k

Ω

and R2

= 15 k

Ω

. These figures decrease the

battery’s 2.4 V to about 1.4 V, which

falls in the specified range.

Current drawn during the Maintain

mode should be about 0.03 to 0.05 of

battery capacity. I used cells with

500 mAh with 20-mA current. This

current is given by:

[6]

where V

in

is the input voltage and V

bat

is the voltage of the battery (2.4 V).

Then, with V

in

= 12 V and R5 = 455

Ω

,

you can use a 470-

Ω

resistor.

For the PCB, I decided to use a com-

mon DC connector with one switching

contact for the charger connection to

the altimeter. This contact unplugs the

altimeter’s electronics from the bat-

tery during charging.

ASSEMBLY AND DEBUGGING

The PCB is double-sided with a few

big holes for mounting it in a BOPLA

BOS-400 box. First, adjust the board’s

mechanical dimension with a file. The

box will need a few mechanical adjust-

ments, so use a knife to cut short pro-

trusions around the screws’ holes.

Then your PCB should match the box

exactly. The next step is to cut or mill

a window for the display, buttons, and

connectors. Dimensions for the win-

dow will depend on your materials.

After making the window, solder

the parts (except the microcontroller)

to the PCB. Connect the LCD via

Channel 1 500 mV

M 100 ms Channel 1

2.08 V

1–26 mA

2–15 mA

3–9 mA

Figure 6—

Simple power management was imple-

mented in the software. Period 1 represents pres-

sure measurement, period 2 shows calculations of

all variables, and period 3 marks the Idle mode.

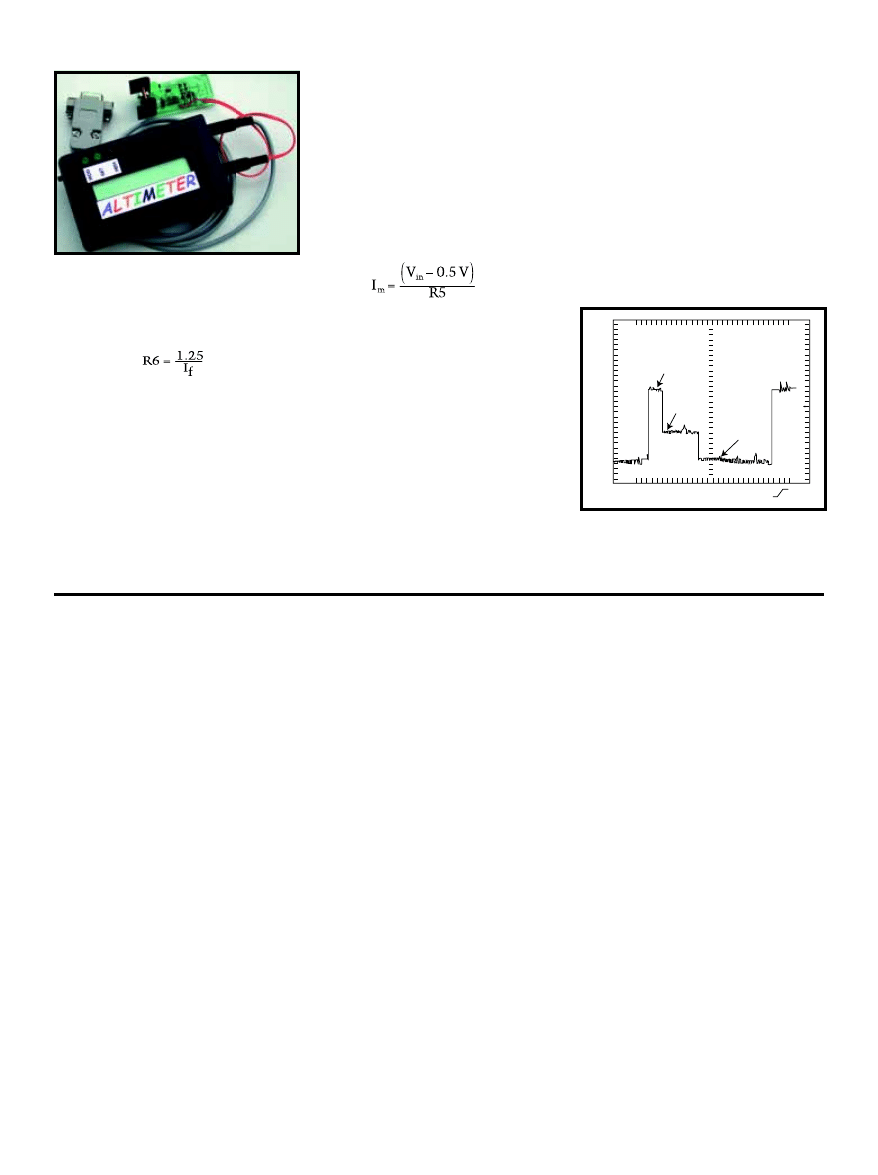

Photo 2—

Here’s the complete altimeter with

charger and cables.

Resistor R6 determines the fast

charging current and its value:

[5]

where I

f

is the charging current and 1.25

is the reference voltage of the LM317. It

should be chosen for a power dissipa-

tion of P = 1.25 × If. I selected 2 h of

charging with a current of If = 300 mA.

This gives R6 = 4

Ω

at 0.4 W.

R1 and R2 have to decrease the

battery’s voltage to 1 to 2 V. A voltage

outside of this range at pin 1 of

MC33340 won’t allow fast charging to

CIRCUIT CELLAR

®

Issue 127 February 2001

27

www.circuitcellar.com

SOURCES

AD7888

Analog Devices, Inc.

(800) 262-5643

(781) 329-4700

www.analog.com

Excel

Microsoft Corp.

(425) 882-8080

www.microsoft.com

Transistor, MC33340

ON Semiconductor

(602) 244-6600

www.onsemi.com

REFERENCES

[1] Motorola, Inc., MPX4115,

search.motorola.com/semiconduc-

tors/index.html.

[2] Motorola, Inc., “AN1646 Noise

Considerations for Integrated

Pressure Sensors.”

[3] Royal Philips Electronics,

KTY81-1,

www.semiconductors.com/pip/

KTY81.

[4] ON Semiconductor, MC33463,

SOFTWARE

The code and a parts list are avail-

golden pins and a precision socket (see

Photo 1) or with short cable. If you use

a socket for the microcontroller, you

may need to bend the display’s metal

holders.

There isn’t much space in the box,

so I use small audio jack 2.5-mm mono

connectors for charging and serial

output. This connector has contacts

that disconnect the altimeter from the

battery while it’s charging.

CHECKOUT

Connect the altimeter to a power

supply via an ammeter and check the

current consumption (see Photo 2). The

current shouldn’t exceed 50 mA at 2.4

V. Also, check the voltage at the out-

put of the DC/DC converter, which

should be 5 V. It’s important to take a

look at the 4.6-V reference at pin 1 of

IC6. Before taking measurements, tem-

porarily ground the T1 gate.

If everything is OK, solder the mi-

crocontroller or place it to the preci-

sion socket. After switching on the

power supply, the temperature will be

displayed and all functions of the al-

timeter should work. Next, perform

the necessary calibrations.

EVERYDAY USE

I developed this altimeter for a

hobby, not to compete with profes-

sionally made products. Professional

Figure 8—

The

MC33340 from

ON Semiconduc-

tor enables you to

charge the altim-

eter easily without

a stabilized power

supply.

Radek Vaclavik holds a college degree

in engineering. He is project leader at

ON Semiconductor Czech Design

Center. Radek is an active radio ama-

teur (call sign OK2XDX) and is inter-

ested in all aspects of electronics, from

DC to microwaves. You can find all of

Radek’s projects at his web site. He

may be reached at radek.vaclavik

@onsemi.com.

products are smaller but more expen-

sive. Moreover, I enjoyed constructing

the altimeter and seeing it work prop-

erly. The altimeter is easy to build and

debug and can be constructed by elec-

tronics beginners.

The parameters of the altimeter are

accurate, output values are stable, and

I achieved 1-meter resolution on all

units. Data storage is an interesting

option that enables you to see a profile

of the last trip. (There are visible

breaks where I stopped in some pubs.)

A GPS system will give you more accu-

rate values, but will cost more.

Other functions could be imple-

mented in the program. I’m working on

implementing an infrared port that

enables wireless transfer of data to a

PC. My next addition will process data

from a magnetic sensor on a bicycle

and enable gathering of profiles based

on traveled distance.

My latest altimeter version can

show altitude in feet, temperature in

Fahrenheit, and pressure in millimeters

of mercury. You can activate it by

grounding pin P3.6 of the microcon-

troller. Calibration must be done in

standard units, otherwise the software

will be difficult. An extended setup

menu lets you set your home altitude

and then the altimeter calculates the

absolute altitude.

You also can input an estimated

duration of the trip and the altimeter

will recalculate the internal constants

for better use of EEPROM memory. As

a result, you’ll get better resolution

because the altimeter will store the

altitude more often.

All new versions of SW require 8 KB

of program memory and use the 89C52

microcontroller instead of the 89C51.

The altimeter is a popular item at

my local cycle club because users can

compare achieved performance. After

0

1000

2000

3000

430

410

400

420

390

380

370

360

Time

Altitude

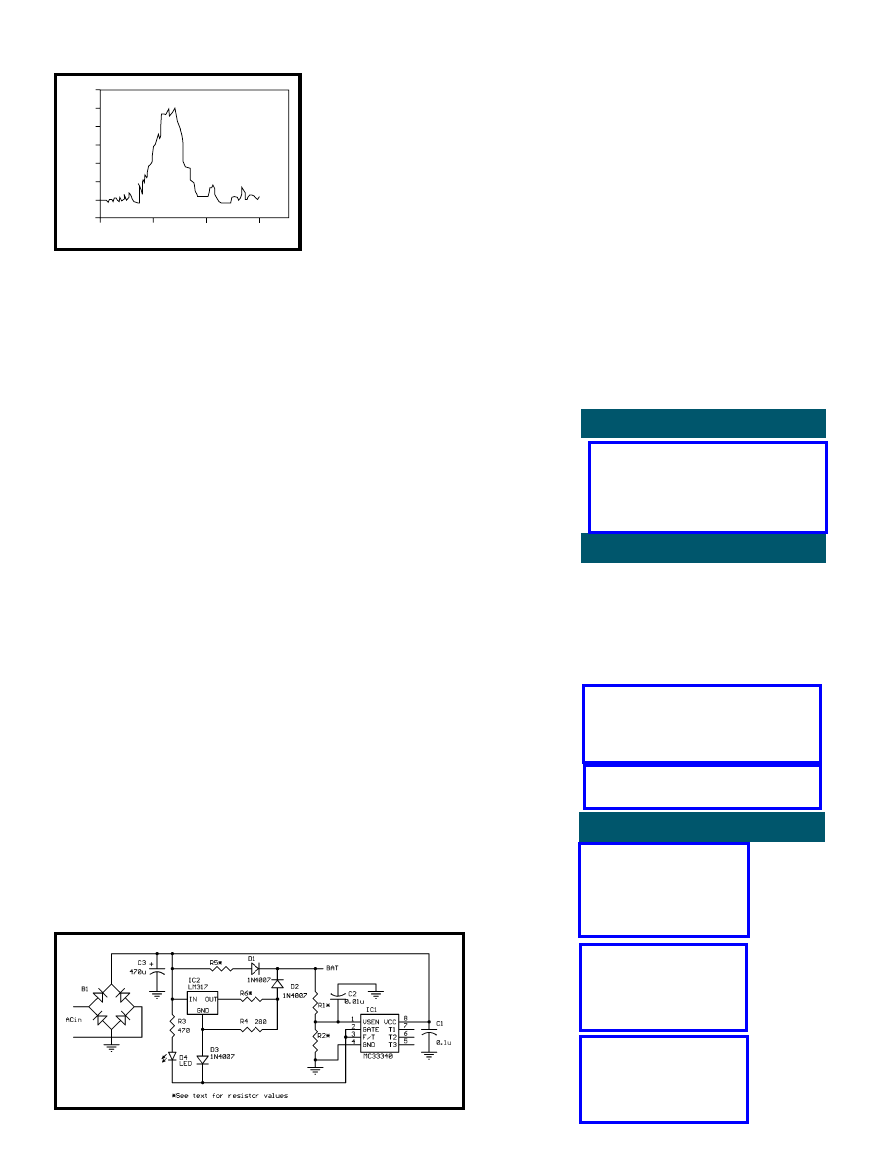

Figure 7—

When the prototype is ready, it’s time

to take a bicycle to the nearest hill and test it.

building this altimeter, I started an-

other project that I may write about in

the future. My newest creation is a

flying altimeter for use in model air-

planes. It transmits data down to the

modular. Keep an eye out for a story

about that project.

I

28

Issue 127 February 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

a

fter the new

DVD player was

plugged into the big

screen TV and I saw the

image, there was no going back to

composite video. A few weeks later, I

purchased a programmable remote to

control my home theater system and

became a highly optimized couch po-

tato. But my happiness did not last.

A few months ago, I added a new

digital cable service. After installation,

I realized that the decoder box had an

S-video output. The problem was that

my TV had only one S-video input and

the DVD player was connected to it. I

found a manual S-video switch box at

Radio Shack. It saved having to switch

the cable behind the TV, but I was now

a sub-optimal couch potato.

Happiness (and optimization) could

only be found with a remote control-

led S-video switch. It was time to heat

up the soldering iron and write some

PIC code.

This project requires using a com-

mon IR format and detector so that an

off-the-shelf remote can act as the

controller. It needs to support four

input channels of S-video, composite

video, and stereo audio. There has to

be a learning mode so that codes other

than the programmed default can be

used to switch channels.

Also note that the mechanical form

factor should be no larger than the

Radio Shack mechanical switch. The

channels can be selected with front

panel switches and with a remote.

I researched the format of IR remote

controls and found that there are a few

major standards for IR protocols, in-

cluding the ubiquitous RC5 codes.

This format consists of 14 bits that are

transmitted using Manchester codes. I

settled on Sony’s remote control, also

known as the RECS 80 standard.

Sony’s protocol is simple and easy

to decode. And, Sony has a number of

excellent, after-market, universal re-

mote controls. Not to mention, I al-

ready owned one. In addition, it’s

logical to map the codes for the differ-

ent channels to the audio amplifier,

which I already owned as well.

Sony uses a 12-bit protocol that

consists of a 5-bit ID code followed by

a 7-bit command code. The data is

transmitted least significant bit first

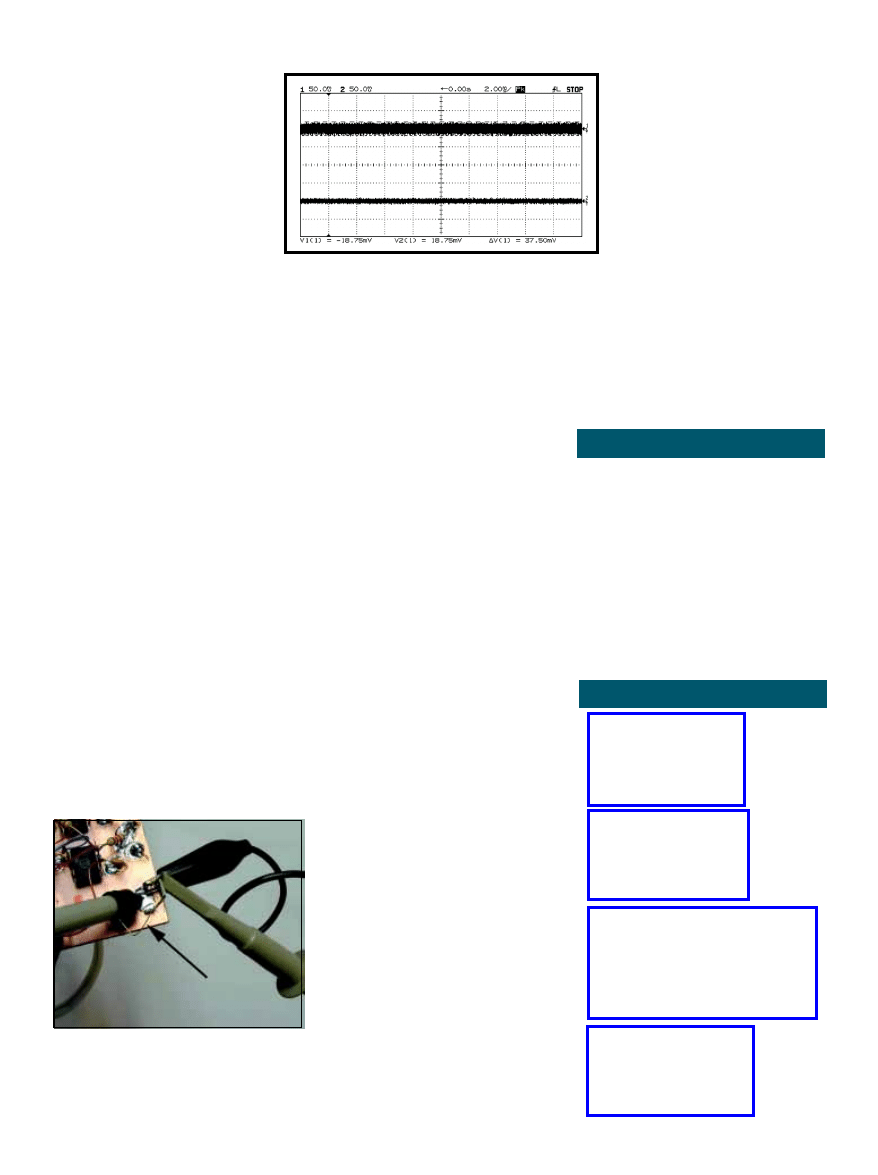

after a start or AGC bit. On my oscillo-

scope, I observed that the start bit has

2.6-ms duration. A one was low for

1.44 ms, followed by a 440-µs termina-

tor. A zero was low for 760 µs, fol-

lowed by a 440-µs terminator.

The code to set a Sony amplifier to

the Video1 input is 822 hex (see Fig-

ure 1). Other observed codes for input

selection for a Sony amplifier are

stated in Table 1. For default codes, I

chose Video1, Video2, CD, and TV.

Note that you can teach the switch to

remember any combination of codes as

long as it adheres to the Sony format.

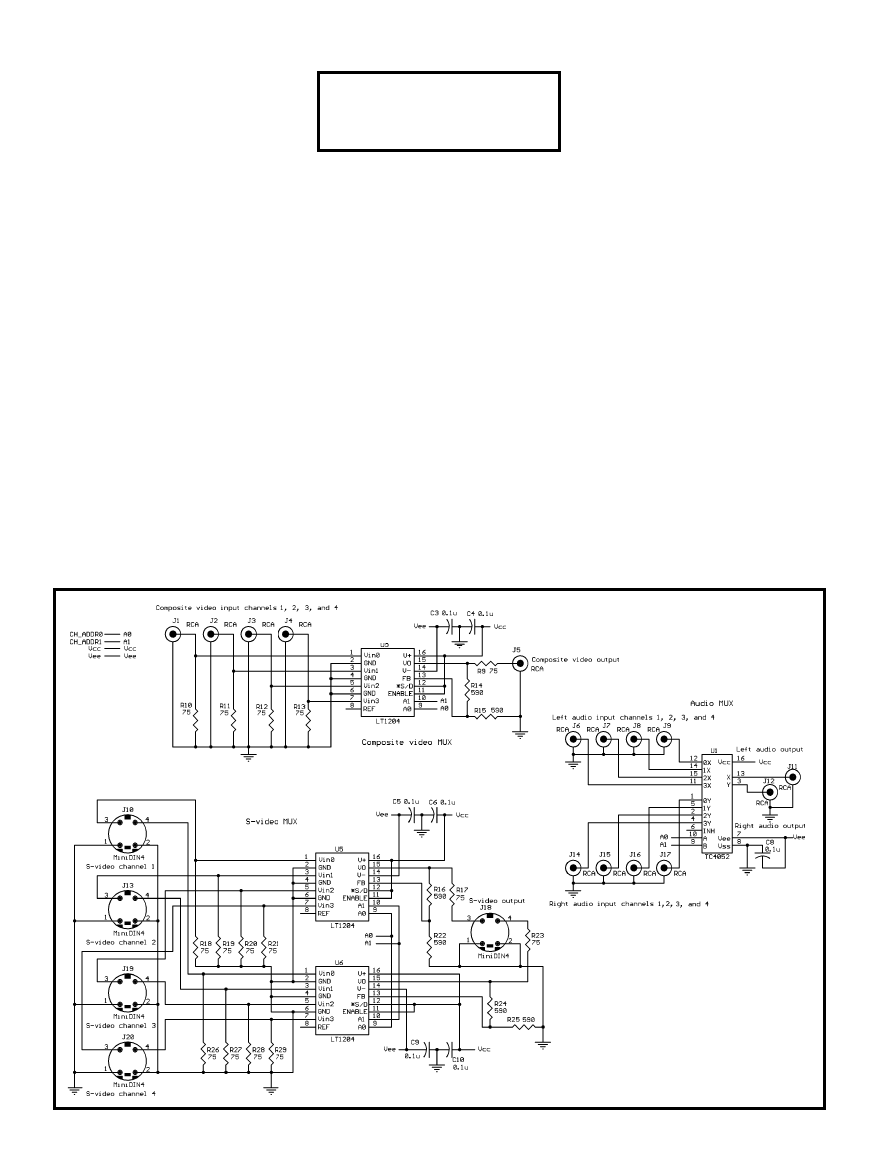

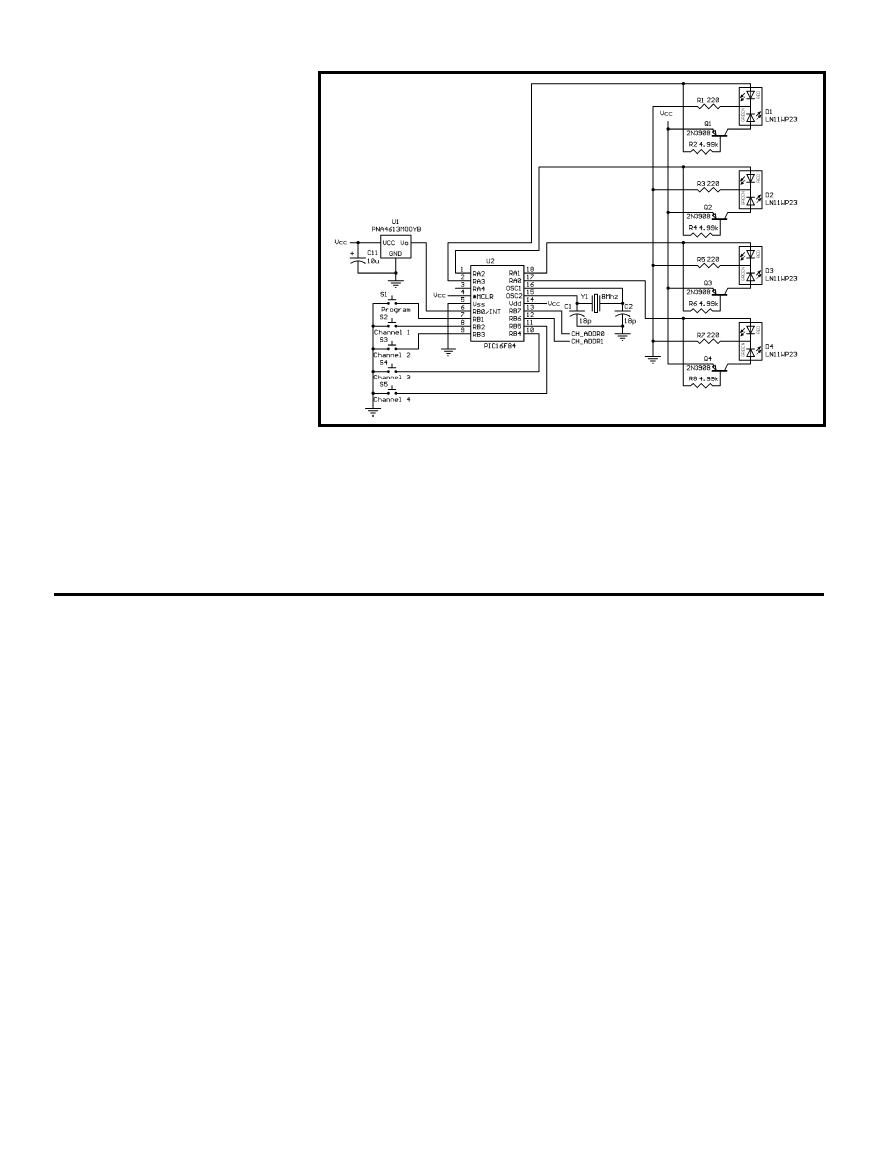

ENJOY THE CIRCUITS

The Panasonic PNA4613MOOYB

IR sensor, PIC16F84, and the Linear

Technology LT1204 4-input video

After upgrading his

home theater system,

only one thing hin-

dered Jerry from be-

coming the supreme

couch potato—the

manual S-video

switch for the TV. Not

to be deterred, he

built a remote switch

and continued his

quest for optimization.

Enabling the Couch Potato

Building a Remote-Controlled

AV Switch with S-Video

FEATURE

ARTICLE

Jerry Wasinger

Wasingerose

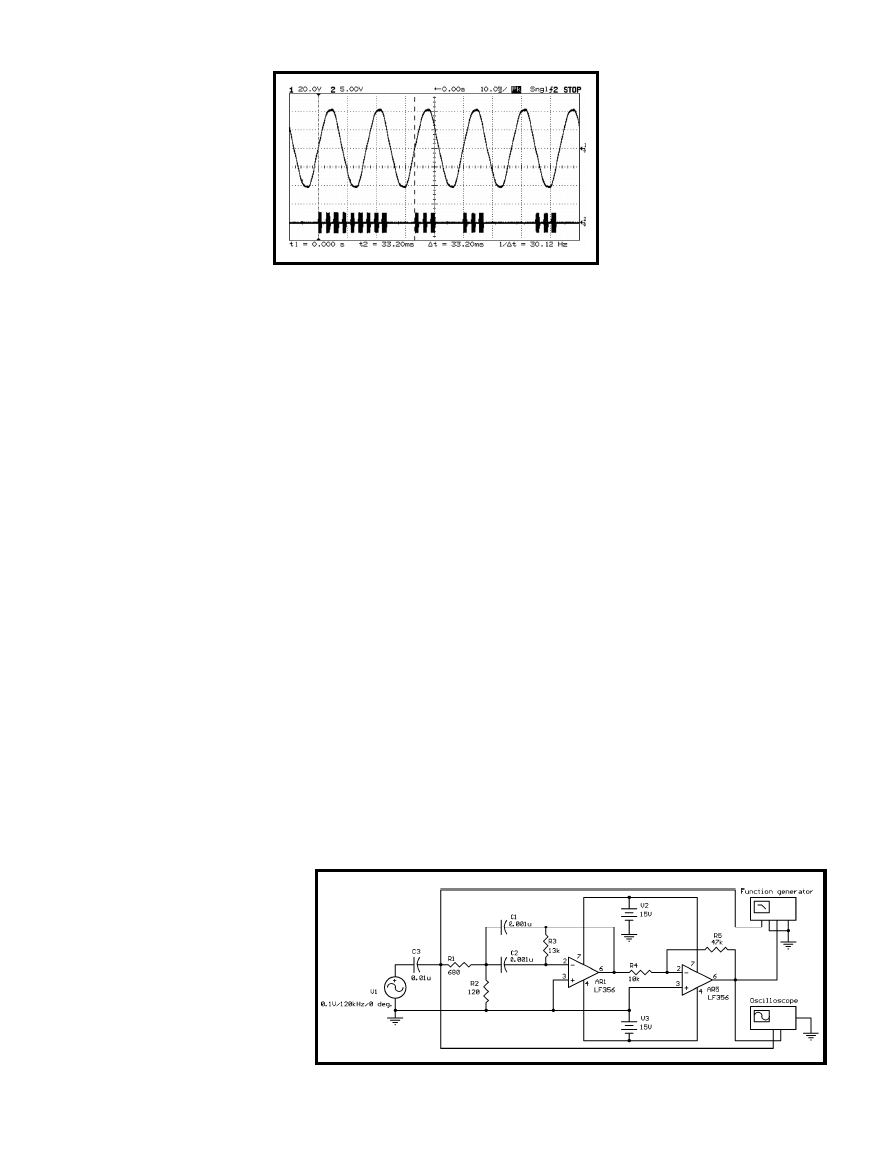

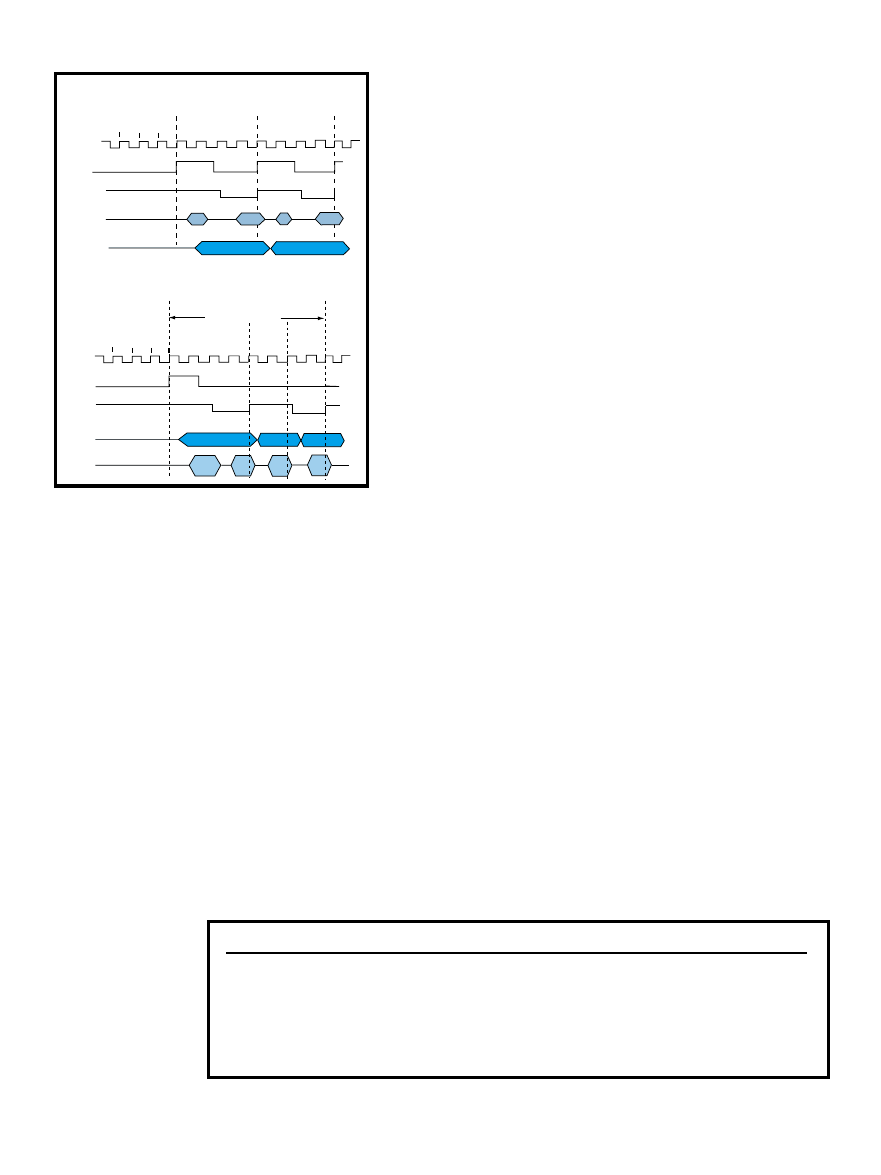

Figure 1—

Take a look at the Sony remote datastream observed at the output of the IR detector. This is the

code for 822 hex.

Start

0

0

0

0

0

0

0

0

0

1

1

1

CIRCUIT CELLAR

®

Issue 127 February 2001

29

www.circuitcellar.com

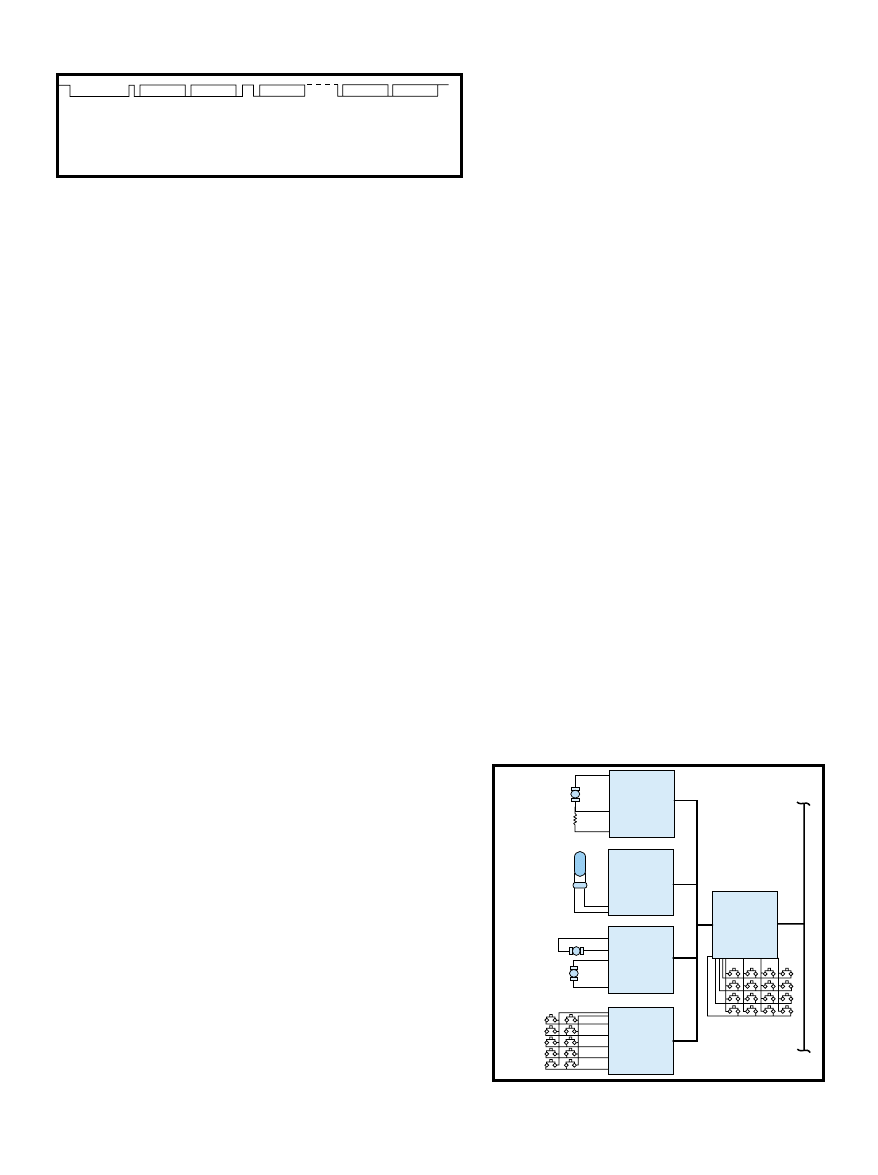

mux comprise this design. I used bicolor

LEDs to indicate the selected channel.

To modify this circuit to perform

tasks other than switching a video

mux, just tap off ADDR0 and ADDR1

with your own circuit. Or, use the LED

drivers as a set of one of four outputs.

The Panasonic IR sensor provides

the optical sensing, detection circuits,

40-kHz filtering, and amplification to

extract the signals from the remote.

The PIC has five pushbutton inputs,

one IR sensor input, four LED indicator

outputs, and two coded address selec-

tion outputs. Using an 8-MHz crystal

results in an instruction cycle of 500 ns,

or roughly two million instructions

per second, which is more than ad-

equate bandwidth for this application.

The LEDs have a circuit that allows

them to be controlled by one line. The

green LED is on and the transistor is off

when the input is high. The green LED

is off and the transistor turns on to

provide current for the red LED when

the input is low. The PIC outputs can

source up to 25 mA, which is more

than enough for an LED.

The LT1204 4-input video mux has a

30-MHz bandwidth that is adequate for

these signals. Here, you terminate the

inputs with 75

Ω

. So, you have to boost

the gain by two on the output. Other

devices, including Analog Devices’

AD8184 or the MAX454, can be substi-

tuted for this multiplexer. If the Analog

Devices part is used, a video amplifier

with a gain of two will have to follow

the outputs. For the audio switching, a

CD4052 dual 4:1 mux is used.

Power for the circuit is provided

with a 5-V linear regulator driven by a

common 9-VAC wall transformer. I use

a Linear Technology LTC660 inverter

to get the –5 VDC required by the

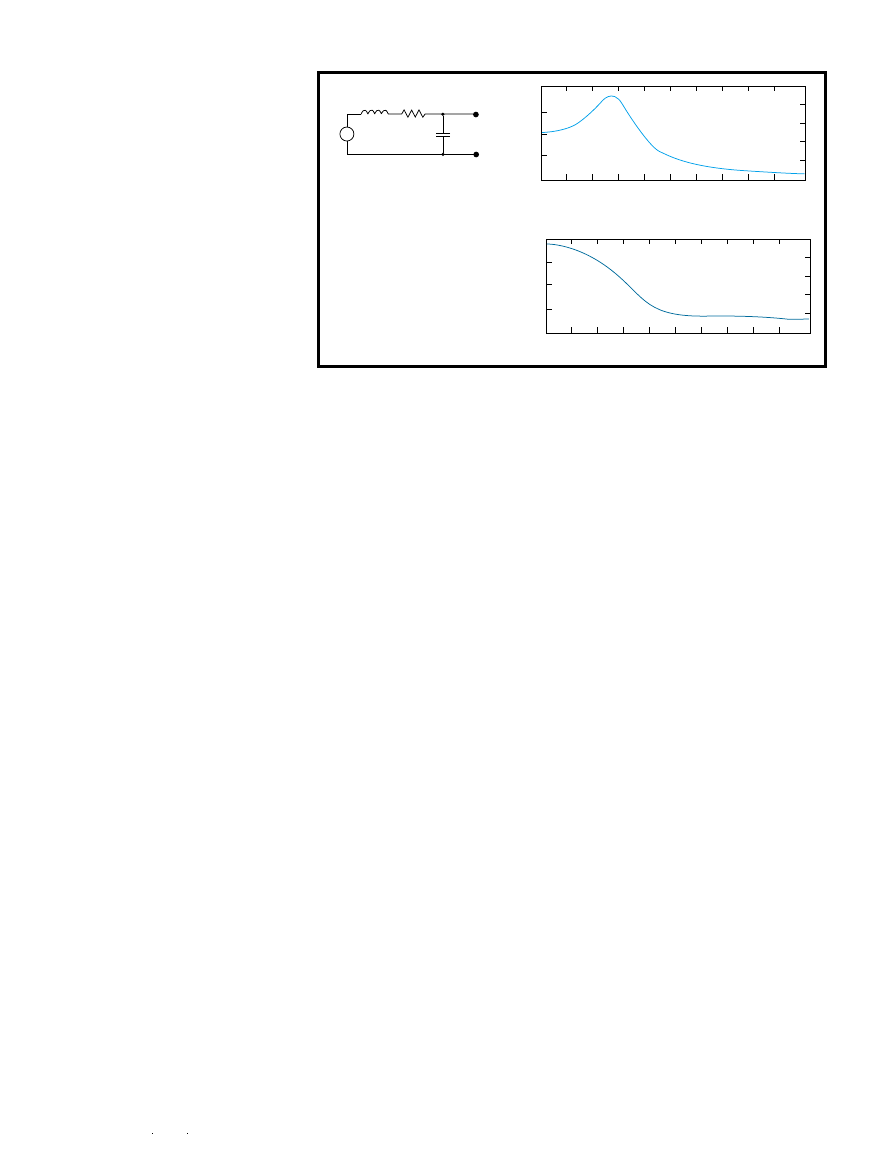

muxes. An LC circuit squelches re-

sidual switching noise from the in-

verter before going to the muxes.

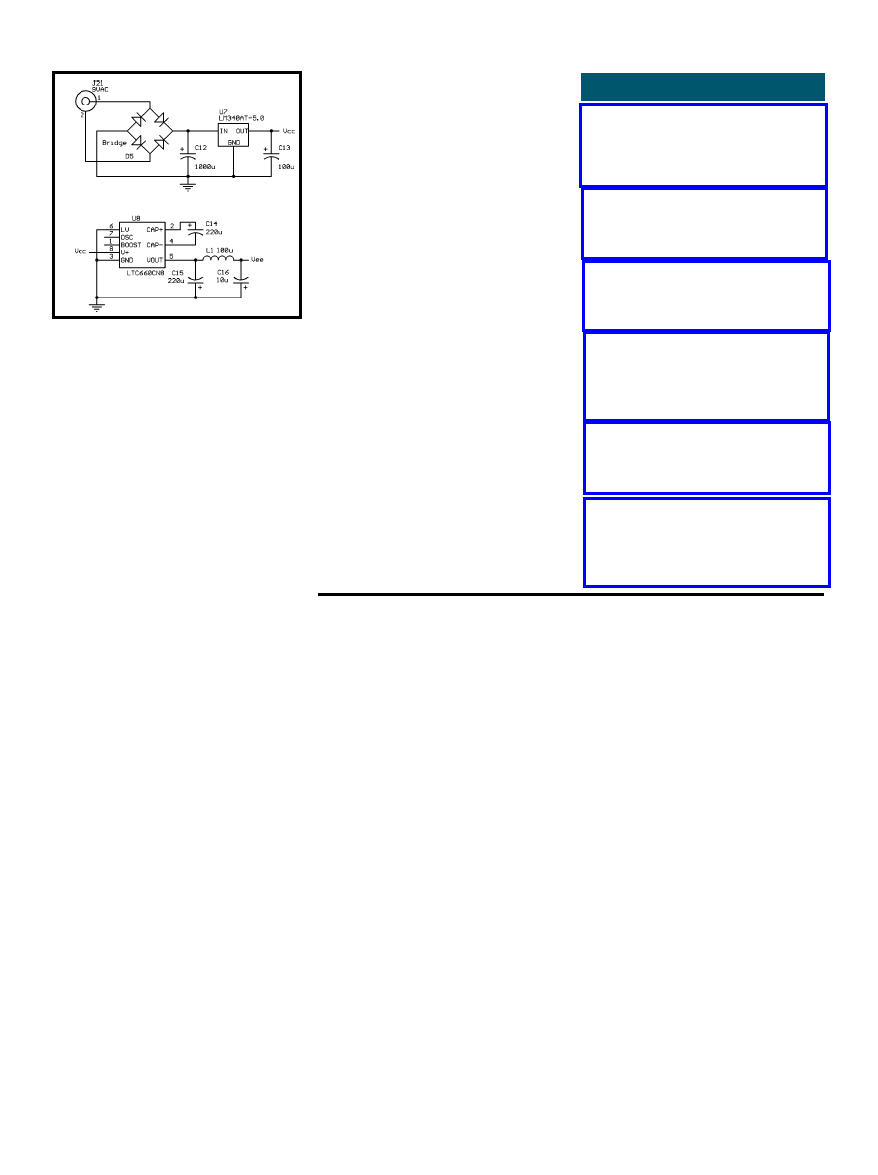

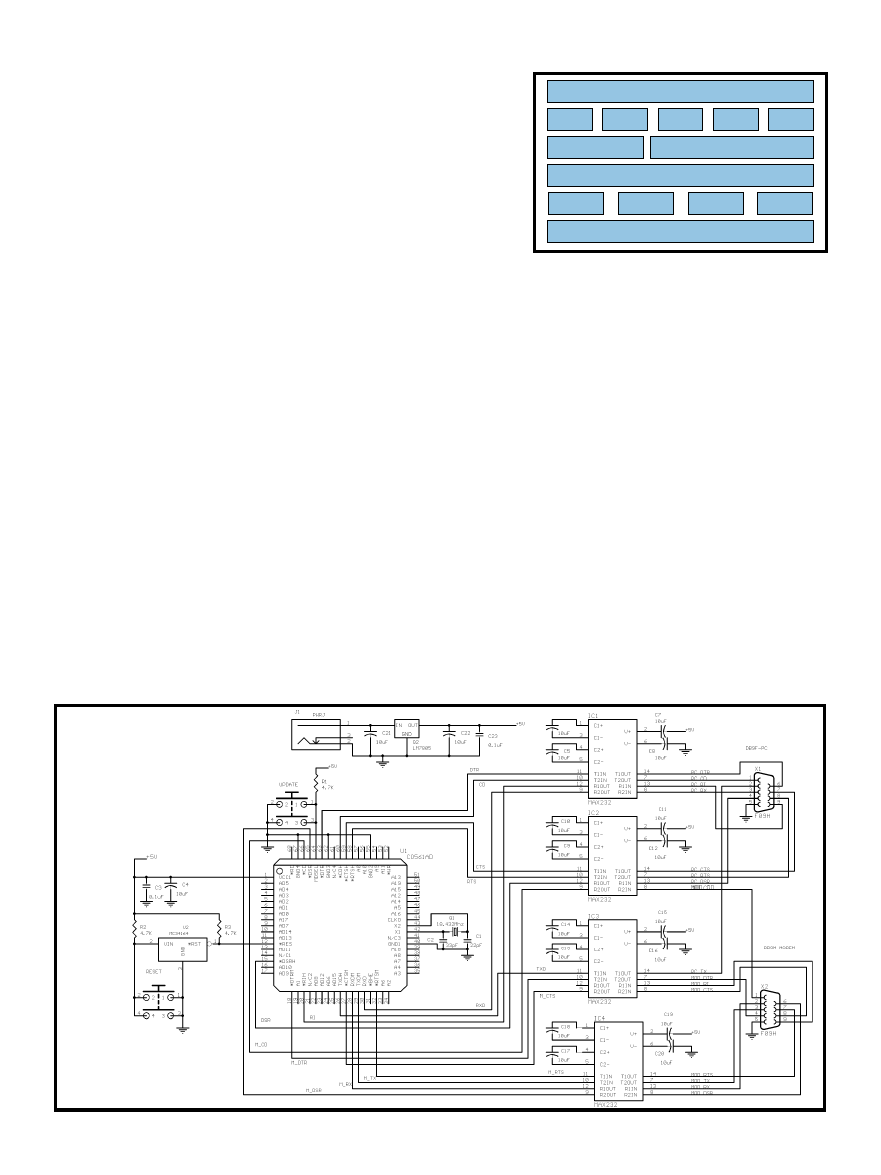

The three schematic diagrams illus-

trate the different sections of the cir-

cuit. Figure 2 shows the back end. The

front end consists of the muxes and

connectors (see Figure 3). And finally,

Figure 4 outlines the power supply.

SOFTWARE ANYONE?

The PIC program is straightforward.

After powerup, channel 1 is selected

by default. The code then goes into a

loop where it scans the buttons, main-

tains a timer, and waits for an inter-

rupt from the IR sensor. If a button is