1

Podstawy techniki

mikroprocesorowej

ETEW006

Układy czasowo – licznikowe

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

Standard Serial Interface

RS-232

(Recommended Standard 232; 1969), TIA-232-F Interface Between Data

Terminal Equipment and Data Circuit-Terminating Equipment Employing Serial Binary

Data Interchange, issued in 1997: TxD, RxD and

I

2

C–Bus

(Inter Integrated Circuit Bus; Philips, early 1980's):

SCL (clock)

SDA (data)

CAN

(Controller Area Network; Robert Bosch GmbH, 1983):

CAN_H

CAN_L

SMBus

(System Management Bus, Intel, 1995):

SMBCLK (clock)

SMBDAT (data)

USB

(Universal Serial Bus; Compaq, DEC, IBM, Intel, Microsoft, NEC and Nortel,

1994):

D+ (Data +)

D– (Data –)

SPI

(Serial Peripheral Interface Bus; Motorola),

Microwire

(National Semiconductor):

MOSI (Master Output Slave Input)

SO (Serial Output)

MISO (Master Input Slave Output)

SI (Serial Input)

SCK (Serial ClocK)

SK (Serial Shift Clock)

SS

(Slave Select)

CS (Chip Select)

single-ended simple two-wire bus

differential pair defined in the USB 2.0 specification

single-ended simple two-wire bus

differential pair defined in the USB 2.0 specification

N-bit

Timer/Counter

16-bit Timer

High Register

Timer

15..8

Clock

16-bit Timer

Low Register

Timer

7..0

Clock

8-bit

Timer Register

Timer

7..0

32-bit Timer

Lower Register

Timer

15..8

Clock

32-bit Timer

Lowest Register

Timer

7..0

32-bit Timer

Highest Register

Timer

31..24

32-bit Timer

Higher Register

Timer

23..16

0

0

0

7

7

7

8

8

15

15

16

23 24

31

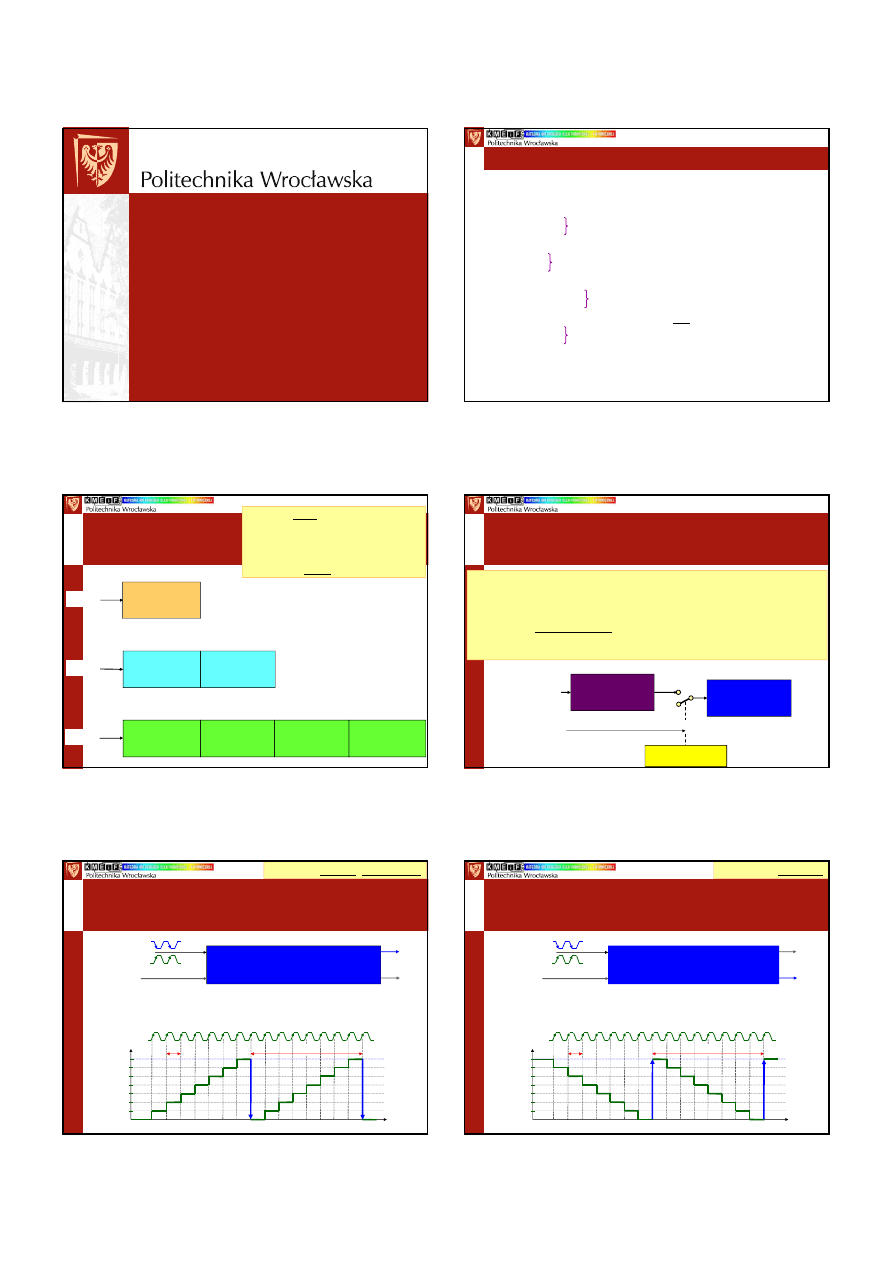

Timer

– zegar, stoper, czasomierz,

minutnik, mechanizm zegarowy (do

wł

ą

czania/wył

ą

czania), programator

zegarowy

Counter

– licznik

K-bit Prescaler

N-bit Timer/Counter

Taktowanie

(Clock)

K-bitowy

dzielnik wst

ę

pny

(Prescaler)

N-bitowy

dzielnik

(Timer / Counter)

1

0

Układ kontrolny

(Control Logic)

po sprz

ę

towym zerowaniu (after Reset)

Scaling

– skalowanie, zmiana skali: mno

ż

enie (np. powielanie

cz

ę

stotliwo

ś

ci sygnału w p

ę

tli PLL) lub dzielenie (np. podział cz

ę

stotliwo

ś

ci

sygnału w dzielniku, zmiana współczynnika wypełnienia sygnału itp.)

Prescaler

– wst

ę

pny dzielnik (łac. pre – przed, post – po) w celu

rozszerzenia zakresu cz

ę

stotliwo

ś

ci sygnałów wej

ś

ciowych lub zmiany

cz

ę

stotliwo

ś

ci sygnałów wyj

ś

ciowych

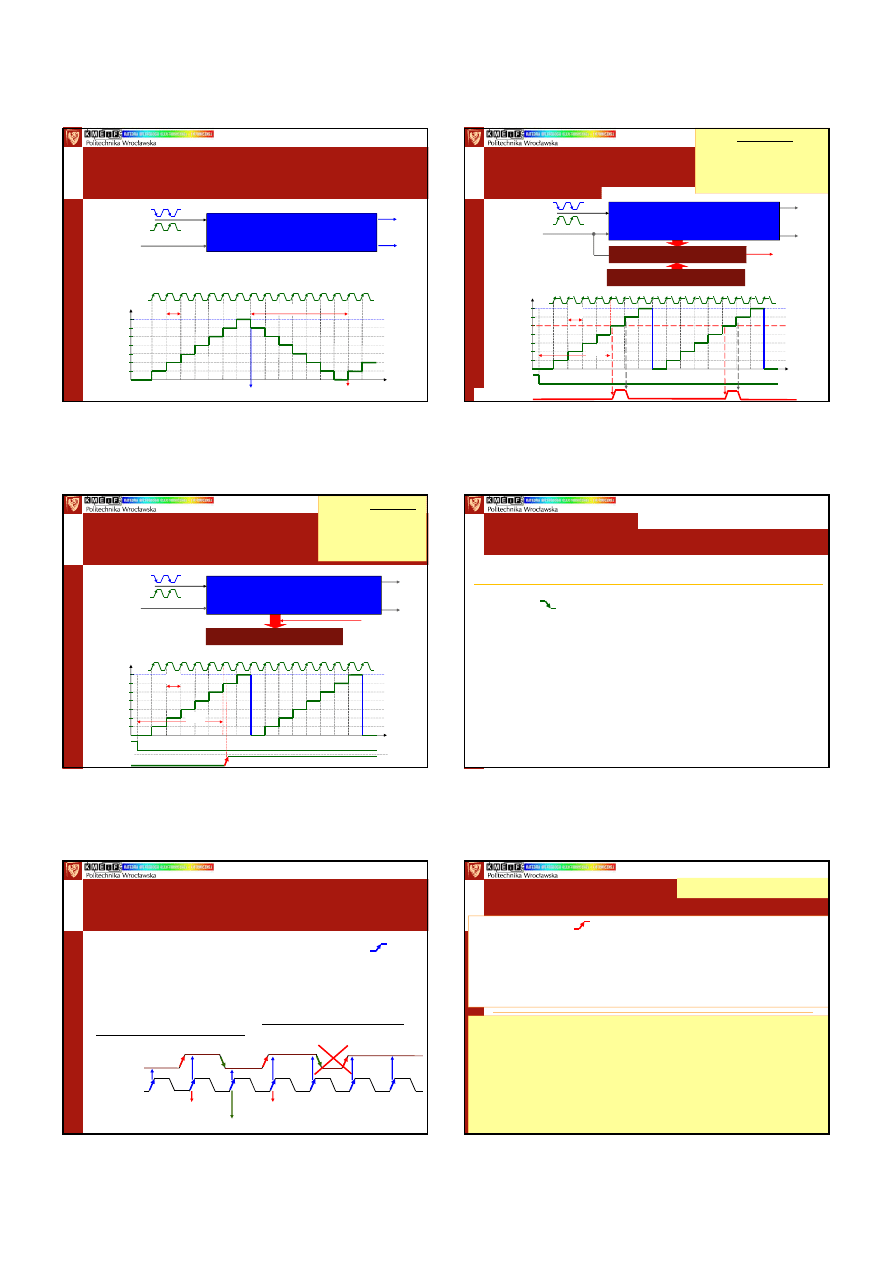

3

–

bitowy Timer/Counter

Tryb zliczania w górę

(Up

–

Counting Mode)

N=2

0

CLR

N-bitowy Timer/Counter

Timer

CLK

0

1

2

3

4

5

6

7

1

2

3

4

5

6

7

8

przepełnienie (overflow)

1

2

3

4

5

6

7

8

1

µµµµ

s

8

µµµµ

s

Timer

CLK

or

Underflow

Przepełnienie (Overflow)

Overflow

– nadmiar, przepełnienie

t

Clear

3

–

bitowy Timer/Counter

Tryb zliczania w dół

(Down

–

Counting Mode)

N=2

0

CLR

N-bitowy Timer/Counter

Timer

CLK

0

1

2

3

4

5

6

7

1

2

3

4

5

6

7

8

Niedomiar (Underflow)

1

2

3

4

5

6

7

8

1

µµµµ

s

8

µµµµ

s

Timer

CLK

or

Niedomiar (Underflow)

Overflow

Underflow

– niedomiar

t

Clear

2

3

–

bitowy Timer/Counter

Tryb odliczania w górę i w dół

(Up/Down

–

Counting Mode)

N=2

0

CLR

N-bitowy Timer/Counter

Timer

CLK

0

1

2

3

4

5

6

7

1

2

3

4

5

6

7

1

Przepełnienie (Overflow)

2

3

4

5

6

7

1

Niedomiar (Underflow)

7

µµµµ

s

Timer

CLK

or

2

t

1

µµµµ

s

Clear

Niedomiar (Underflow)

Przepełnienie (Overflow)

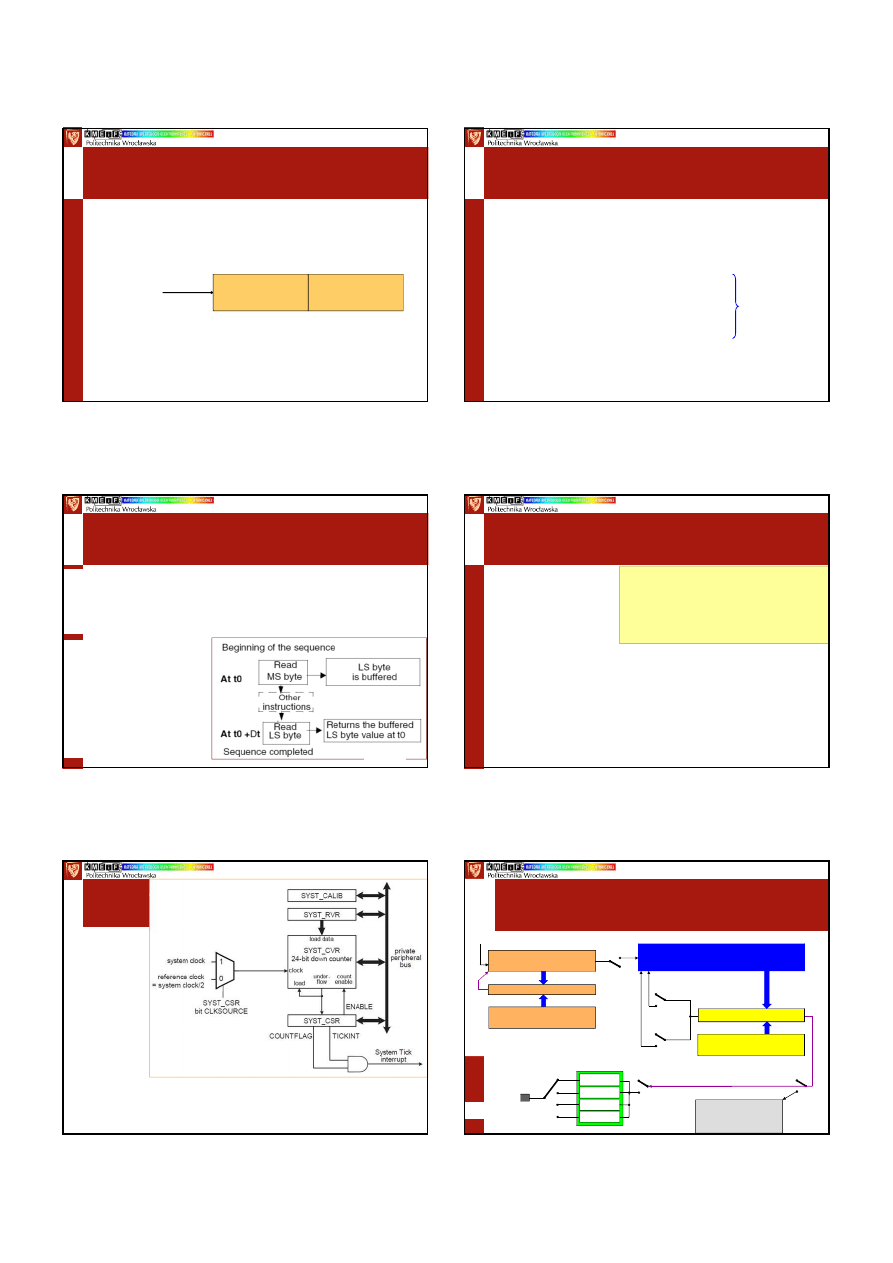

3

–

bitowy Timer/Counter

Tryb porównania

(Match Mode)

N=2

Clear

Timer

CLK

0

1

2

3

4

Match = 5

6

7

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

Clear

1

µµµµ

s

Timer

CLK

or

Znacznik

porównania

(Match Flag)

Match

– porównywa

ć

, paso-

wa

ć

, dopasowywa

ć

, dobie-

ra

ć

, zestawia

ć

, dorówny-

wa

ć

, dostosowywa

ć

, odpo-

wiada

ć

sobie

t

CLR

N-bitpwy Timer/Counter

Niedomiar (Underflow)

Przepełnienie (Overflow)

Match flag

5

µµµµ

s

N-bitowy komparator

=

N-bitowy Match Register

Reset flag ??

=

Reset flag ??

0

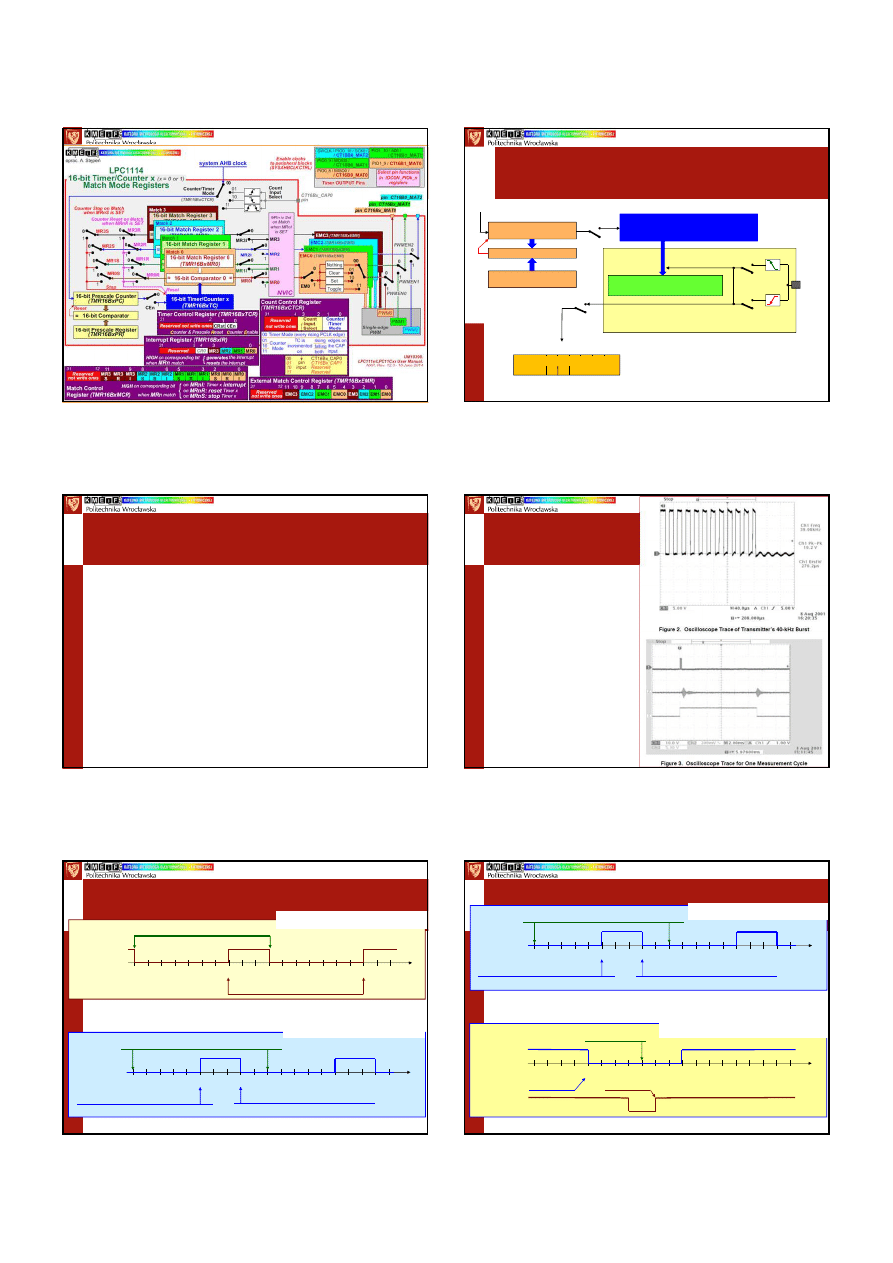

3

–

bitowy Timer/Counter

Tryb zapamiętania wartości

(Capture Mode)

N=2

0

Timer

CLK

0

1

2

3

4

5

6

7

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

Clear

1

µµµµ

s

Timer

CLK

or

Capture

write to

Capture

– chwycenie,

zdobycie, pojmanie,

uj

ę

cie, opanowanie,

zawładni

ę

cie, przej

ę

-

cie (read on the fly)

N-bitowy Capture Register

t

CLR

N-bitowy Timer/Counter

Niedomiar (Underflow)

Przepełnienie (Overflow)

Capture

6

µµµµ

s

Clear

stan licznika w funkcji ’Timer’ jest zwi

ę

kszany przy ka

ż

dym sygnale

taktuj

ą

cym PCLK

stan licznika w funkcji ’Counter’ jest zwi

ę

kszany po wykryciu zbocza

opadaj

ą

cego ( ) sygnału zewn

ę

trznego na wej

ś

ciu (pinie) mikrokontrolera

sygnał zewn

ę

trzny jest próbkowany jeden raz w ka

ż

dym cyklu maszynowym

mikrokontrolera:

•

stan licznika jest zwi

ę

kszany (inkrementowany) je

ś

li stan impulsu

zewn

ę

trznego jest wysoki w czasie jednego cyklu maszynowego i niski w

nast

ę

pnym cyklu

•

nowa warto

ść

licznika pojawia si

ę

w nast

ę

pnym cyklu, po którym wykryto

zmian

ę

sygnału zewn

ę

trznego

•

do wykrycia ka

ż

dego zbocza sygnału zewn

ę

trznego wymagane dwa

cykle maszynowe

•

minimalny czas trwania stanu niskiego / wysokiego sygnału

zewn

ę

trznego wynosi jeden cykl maszynowy mikrokontrolera

MCS51

Impulsy zewnętrzne

UM10147. P89LPC952/954 User manual.

NXP, Rev. 01 — 17 September 2007, p.47

MicroConverter

®

, Multichannel 12-Bit ADC with

Embedded Flash MCU. Analog Devices, Rev.F, 2013, p.29

ARM7

Zliczanie impulsów zewnętrznych

UM10120. LPC2131/2/4/6/8 User manual.

NXP, Rev. 4 — 23. April 2012, p.195

dwa kolejne narastaj

ą

ce zbocza sygnału taktuj

ą

cego PCLK ( )

wykorzystane do identyfikacji tylko jednego zbocza zewn

ę

trznego

sygnału na wej

ś

ciu CAP

• minimalny czas trwania stanu niskiego / wysokiego sygnału

zewn

ę

trznego wynosi jeden cykl maszynowy mikrokontrolera

(Since two successive rising edges of the PCLK clock are used to identify only

one edge on the CAP selected input, the frequency of the CAP input can not

exceed one fourth of the PCLK clock.)

PCLK

Timer + 1

sygnał

zewn

ę

trzny

Timer + 1

Timer + 1

Cortex-M0/M0+

Taktowanie zewnętrzne

(External input)

narastaj

ą

ce zbocze ( ) zewn

ę

trznego sygnału zwi

ę

ksza (inkrementuje)

stan licznika TPM (16-bit Timer/PWM Module)

cz

ę

stotliwo

ść

zewn

ę

trznego sygnału wej

ś

ciowego musi by

ć

o połow

ę

mniejsza ni

ż

cz

ę

stotliwo

ś

ci taktuj

ą

ca zegara/licznika TPM

programowalny stopie

ń

podziału w dzielniku wst

ę

pnym (prescaler counter,

divide-by 1, 2, 4, 8, 16, 32, 64, or 128)

KL14 Sub-Family Reference Manual.

Freescale, KL14P80M48SF0RM, Rev. 3, September 2012, p.520

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, p.342

dost

ę

pne dwa 16/32-bitowe liczniki / timery z 16/32-bitowym preskalerami

dwa kolejne zbocza narastaj

ą

ce sygnału taktuj

ą

cego PCLK wykorzystywane

do wykrycia zbocza sygnału zewn

ę

trznego na wej

ś

ciu CAP

cz

ę

stotliwo

ść

zewn

ę

trznego sygnału wej

ś

ciowego nie mo

ż

e

przekracza

ć

połowy cz

ę

stotliwo

ś

ci sygnału taktuj

ą

cego PCLK

(Since two successive rising edges of the PCLK clock are used to identify only one

edge on the CAP selected input, the frequency of the CAP input can not exceed one

half of the PCLK clock. Consequently, duration of the HIGH/LOW levels on the same

CAP input in this case can not be shorter than 1/(2

∗

PCLK).)

3

16-bitowy Timer/Counter w 8-bitowym MCU

Odczyt/wpis wartości

(Read/Write Timer/Counter Value)

Free running Timer

High Register

T

HIGH

Sekwencje odczytu

(Read sequence):

Sekwencje wpisu

(Write sequence):

1. Odczyt T

HIGH

2. Odczyt T

LOW

lub

1. Odczyt T

LOW

2. Odczyt T

HIGH

1. Wpis T

HIGH

2. Wpis T

LOW

lub

1. Wpis T

LOW

2. Wpis T

HIGH

Clock

Free running Timer

Low Register

T

LOW

Wpis/odczyt synchroniczny

• programowy wpis synchroniczny

:

– zatrzymanie licznika na czas wpisu

– korekta wpisywanej warto

ś

ci o czas wpisu,

zatrzymania, uruchomienia licznika

– wpis cz

ęś

ci mniej znacz

ą

cej

– wpis cz

ęś

ci bardziej znacz

ą

cej

– ponowne uruchomienie licznika

licznik

zatrzymany

Wpis / odczyt do / z 16-bitego rejestru

licznika Timer 1

(TIM1_CNTR)

8-bitowy bufor

przy

odczycie

:

Oprogramowanie

odczytuje bajt bardziej

znacz

ą

cy

(automatyczne

buforowanie bajtu mniej

znacz

ą

cego)

, a w drugiej

kolejno

ś

ci bajt mniej

znacz

ą

cy z bufora.

Brak buforowania przy wpisie warto

ś

ci do rejestru Timer 1

(TIM1_CNTR)

Wpis warto

ś

ci do rejestru licznika Timer 1 (TIM1_CNTRH & TIM1_CNTRL) w

dowolnym momencie; nie zaleca si

ę

wpisu nowej warto

ś

ci w trakcie pracy

licznika (nieprawidłowa warto

ść

).

Figure 30

RM0016. STM8S microcontroller family.

Reference manual. STMicroelectronics, Doc ID 14587, Rev 6. 2009, p.136

ATmega8 — Timer/Counter

Accessing 16-bit Registers

Write

:

; Set TCNT1 to 0x01FF

LDI

R17, 0x01

LDI

R16, 0xFF

OUT TCNT1H, R17

; TempReg

←

R17,

high byte first

OUT TCNT1L, R16

; TCNT1L

←

R16,

low byte second

; TCNT1H

←

TempReg

Read

:

; Read TCNT1 into R17:R16

IN

R16, TCNT1L

; TempReg

←

TCNT1H,

low byte first

IN

R17, TCNT1H

; R17

←

TempReg,

high byte second

ATmega8(L). 8-bit AVR with 8K Bytes In-System

Programmable Flash. Atmel Co. 2486T–AVR–05/08, p.79

unsigned int i;

.................

TCNT1 = 0x1FF; /* Set TCNT1 to 0x01FF */

.................

i = TCNT1;

/* Read TCNT1 into i */

.................

Cortex─M0

System Tick Timer

intended to

generate a fixed

10 millisecond

interrupt for use

by an operating

system or other

system

management

software

simple 24-bit

timer

no external pins

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, p.404

Fig 90. System Tick Timer block diagram

clocked internally by the system clock or the system clock/2

enabled through the SysTick control register

uses dedicated exception vector

Cortex

M0

System

Tick Timer

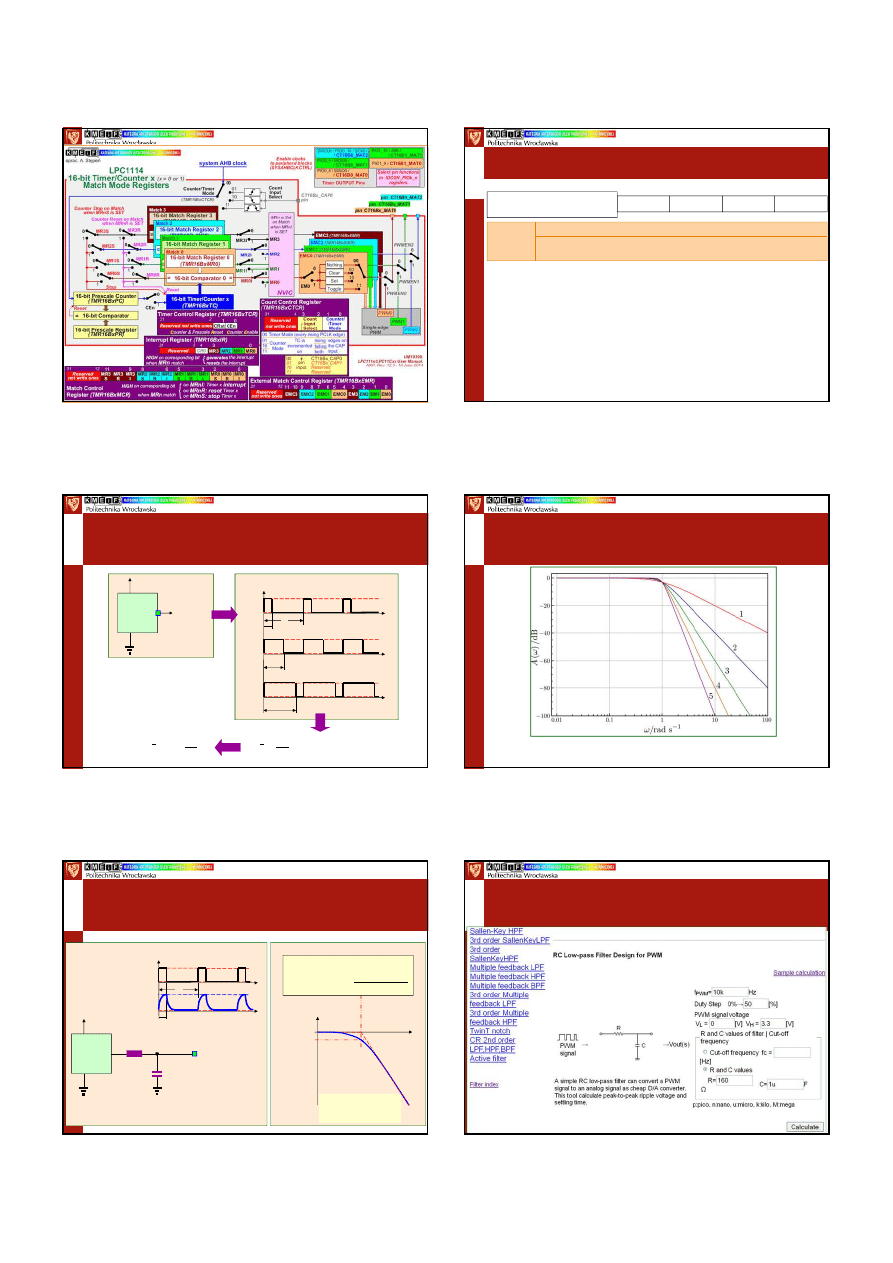

LPC1114

16-bit Timer/Counter 0/1

Match Mode

(TMR16BxTCR)

CEn

1

0

16-bit Comparator

16-bit Prescale Register

(TMR16BxPR)

=

16-bit Prescale Counter

(TMR16BxPC)

pin

CT16Bx_MATy

F

CORE

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, Chapter 20

16-bit Timer/Counter CT16Bx

(TMR16BxTC)

Reset

16-bit Comparator

16-bit Match Register y

(TMR16BxMRy)

=

=

MRyR

(TMR16BxMCR)

1

0

Reset

MRyS

(TMR16BxMCR)

1

0

Stop

1

0

MRyI

(TMR16BxMCR)

NVIC

Interrupt Register

(TMR16BxIR)

1

0

Nothing

Clear

Toggle

Set

00

01

10

11

EMCy

(TMR16BxEMR)

EMy

(TMR16BxEMR)

4

Cortex-M0 — CT16B0/1

Tryb porównania

(Match Mode)

LPC1114

32-bit Timer/Counter 1

Capture Mode

16-bit Capture 0 Register

(TMR16B1CR0)

(TMR32B1TCR)

CEn

1

0

32-bit Comparator

32-bit Prescale Register

(TMR32B1PR)

=

32-bit Prescale Counter

(TMR32B1PC)

1

0

pin

CAP0RE

(TMR16B1CCR)

1

0

CAP0FE

(TMR16B1CCR)

R

/

P

IO

1

_

0

/

A

D

1

/

C

T

3

2

B

1

_

C

A

P

0

32-bit Interrupt Register

(TMR32B1IR)

4

0

C

R

0

1

0

CAP0I

(TMR16B0CCR)

F

CORE

Capture 0

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, Chapter 20

32-bit Timer/Counter CT32B1

(TMR32B1TC)

Reset

MSP430xxx

Capture - Example

pr

ę

dko

ść

d

ź

wi

ę

ku w powietrzu w temperaturze pokojowej

wynosi

1100 ft/s (

~335 m/s

)

ultrad

ź

wi

ę

kowy nadajnik MSP430 generuje 12 prostok

ą

tnych

impulsów o cz

ę

stotliwo

ś

ci 40 kHz

;

ultrad

ź

wi

ę

kowy odbiornik

nasłuchuje

echa

Timer_A

w MSP430 zlicza impulsy o cz

ę

stotliwo

ś

ci

40-kHz

(rozdzielczo

ść

25

µ

s)

wszystkie sygnały s

ą

wyznaczane w generatorze sterowanym

rezonatorem kwarcowym (wysoka stabilno

ść

generowanych sygnałów)

M. Raju: Ultrasonic Distance Measurement

with the MSP430. Application Report. TI, SLAA136A, October 2001

MSP430xxx

Capture - Example

echo

jest wzmacniane w

wewn

ę

trznym wzmacniaczu

operacyjnym i doprowadzone

do wej

ś

cia

Komparatora_A

Komparator_A

wyzwala

przechwytywanie warto

ś

ci

chwilowej licznika

Timer_A;

warto

ść

odczytywana z

rejestru CCR1

(triggers a

capture of Timer_A count

value to capture compare

register CCR1)

12-cycle

echo

Single / Double Edge PWM

PWM1

t

0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7

8 9

PWMMR0 = 10, rate peroid for PWM1

PWM3

0 1 2 3 4 5

6 7 8 9 0 1

2 3 4 5 6 7 8 9

t

PWMMR0 = 10, rate peroid for PWM3

PWMMR3 = 8, PWM3 falling edge

PWMMR2 = 5, PWM3 rising edge

Single Edge Controlled Outputs

Double Edge Controlled Outputs

UM10120. LPC2131/2/4/6/8 User manual.

NXP, Rev. 3 – 4 October 2010

PWMMR1 = 7

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014

Cortex-M0

ARM7

Double Edge / Center—aligned PWM

PWM3

0 1 2 3 4 5

6 7 8 9 0 1

2 3 4 5 6 7

8 9

t

PWMMR0 = 10, rate peroid for PWM3

PWMMR3 = 8, PWM3 falling edge

PWMMR2 = 5, PWM3 rising edge

Double Edge Controlled Outputs

ARM7

0 1 2 3 4 5 6 7 8 7 6 5 4 3 2 1 0 1 2 3

t

TIMx_ARR = 8

CCRx = 4

Center—aligned Controlled Outputs

RM0367 Reference manual. Ultra-low-power

STM32L0x3 advanced ARM

®

-based 32-bit MCUs.

STMicroelectronics , April 2014

STM32L053

UM10120. LPC2131/2/4/6/8 User manual.

NXP, Rev. 3 – 4 October 2010

PWM1

CCRx = 7

5

Cortex-M0 — CT16B0/1

Tryb porównania

(Match Mode)

LPC1114 - PWM Control Register

(TMR16BxPWMC)

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, p.343

ka

ż

de

wyj

ś

cie CT16Bn_MATx mo

ż

na

niezale

ż

nie

ustawi

ć

jako wyj

ś

cie

modulatora PWM lub wyj

ś

cie sterowane komparatorem Emx

16-bitowy timer

CT16B0

ma

trzy

wyj

ś

cia PWM

CT16B0_MAT [2: 0]

16-bitowy timer

CT16B1

ma

dwa

wyj

ś

cia PWM

CT16B1_Mat [1: 0]

je

ś

li wyst

ą

pi

równo

ść

stanu licznika

CT16B0/1

z którymkolwiek z innych

rejestrów porównania

, to modulator PWM ustawia wyj

ś

cie w stan

HIGH

jeden dodatkowy rejestr okre

ś

la długo

ść

cyklu PWM , słu

ż

y do

zerowania

licznika

, a tym samym ustawia stan

LOW

na

wszystkich wyj

ś

ciach

PWM

PWMENx kanał x modulatora PWM (x = 0, 1, 2 lub 3)

0

wyj

ś

cie CT16Bn_MATx sterowane przez komparator (n = 0 lub 1)

1

wyj

ś

cie CT16Bn_MATx sterowane przez modulator PWM

PWMEN3

PWMEN2

PWMEN1

PWMEN0

Reserved

not write ones to bits 31:4

0

1

2

3

4

31

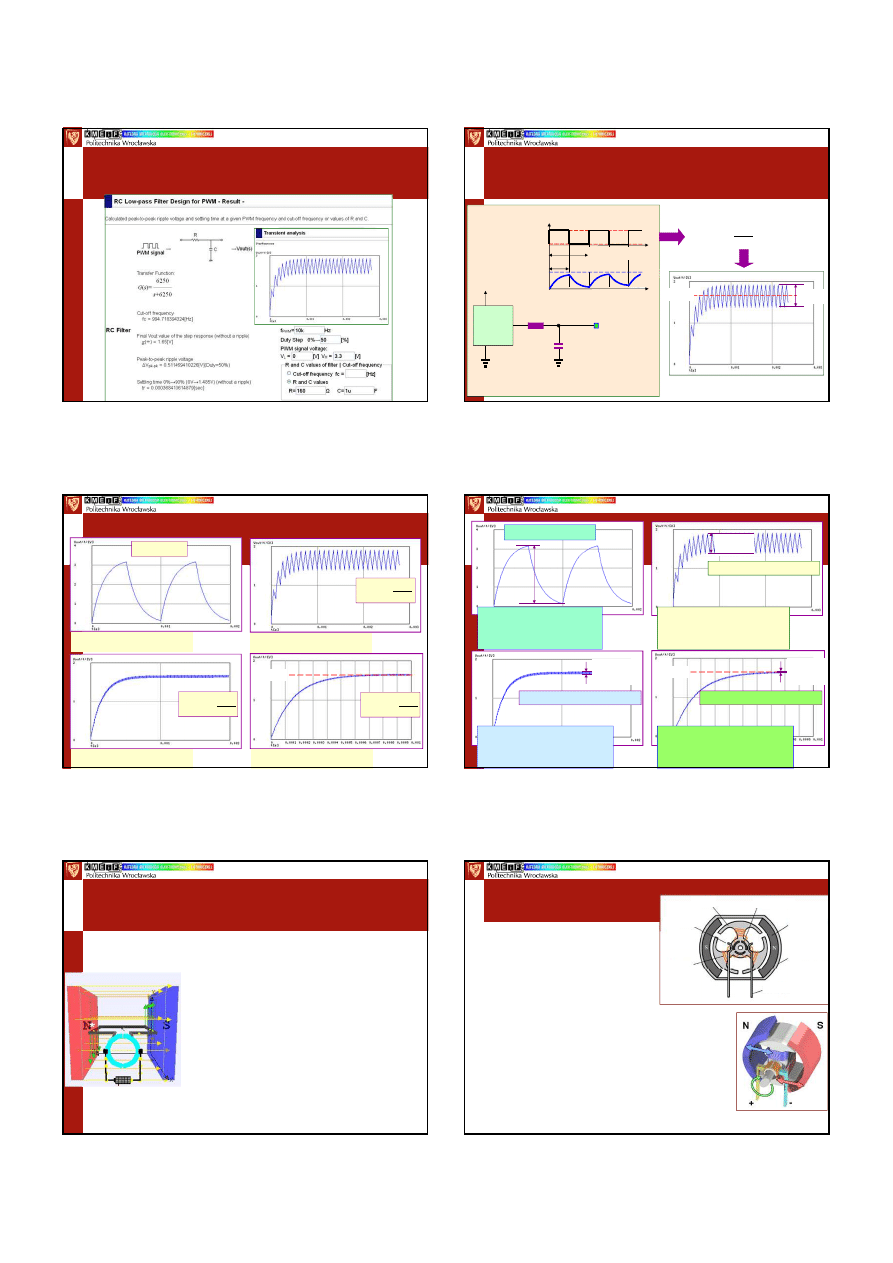

PWM

PDM

low

high

t

low

high

t

low

high

t

τ

= 20% T

Output

Output

∫

0

T

f (GPIO output) dt

1

T

y =

ττττ

T

ττττ

ττττ

GPIO

V

CC

V

GND

τ

T

y = V

CC

τ

= 50% T

τ

= 80% T

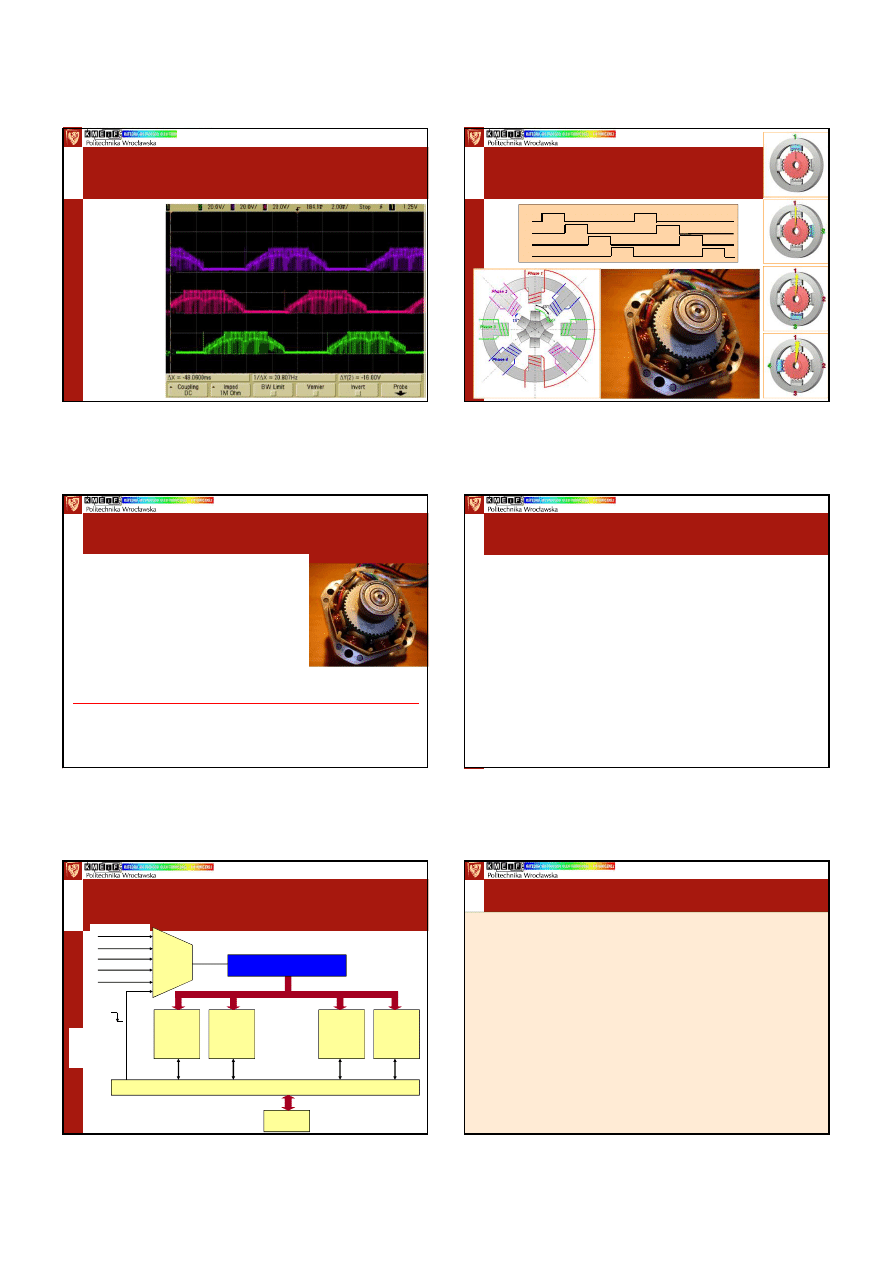

Butterworth Low Pass Filter Orders

(maximally flat magnitude filter)

Charakterystyka

dolno-przepustowego filtru Butterworth’a rz

ę

du 1 .. 5

,

cz

ę

stotliwo

ść

odci

ę

cia

ω

0

= 1.

nachylenie charakterystyki 20n dB/dekad

ę

, gdzie n jest rz

ę

dem filtru

http://en.wikipedia.org/wiki/Butterworth_filter

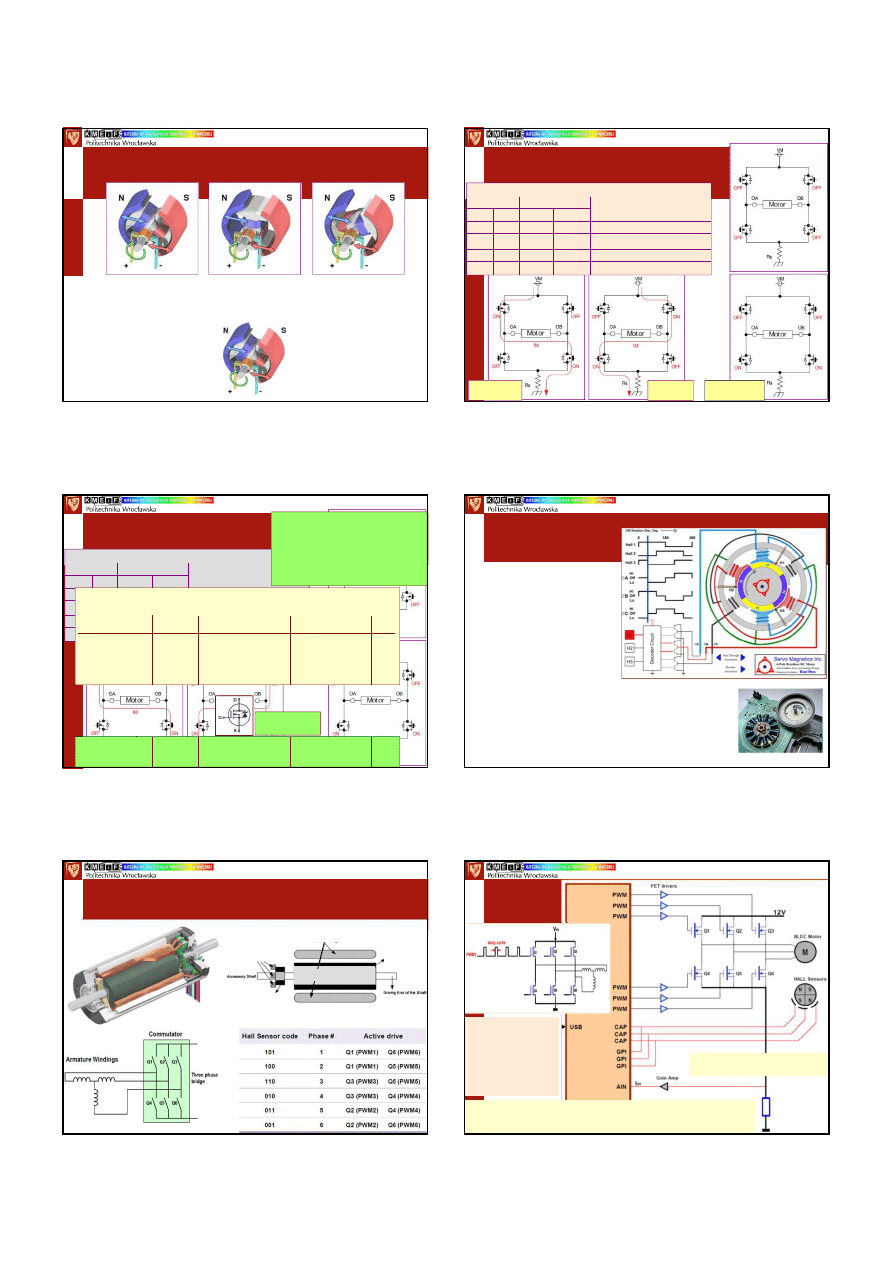

Simple RC Low Pass Filter

[1#2]

C = 1

µ

F

GPIO

0 dB

–3.01 dB

Gain

Slope:

– 6 dB/octave

–20 dB/decade

f

–3dB

= f

Cut-off

=

1

2

∗ π ∗

R

∗

C

Cut-off frequency:

f

low

high

t

Output

V

CC

t

V

GND

V

CC

V

GND

ττττ

T

R = 160

Ω

f

–3dB

= f

Cut-off

= 0.995 kHz

Simple RC Low Pass Filter

Design for PWM

[1#2]

OKAWA Electric Design

http://sim.okawa-denshi.jp/en/CRlowkeisan.htm

6

Simple RC Low Pass Filter

Design for PWM

[2#2]

OKAWA Electric Design

http://sim.okawa-denshi.jp/en/CRlowkeisan.htm

Simple RC Low Pass Filter

[2#2]

GPIO

V

CC

V

GND

OKAWA Electric Design

http://sim.okawa-denshi.jp/en/CRlowkeisan.htm

f

Cut-off

=

f

PWM

10

R = 160

Ω

C = 1

µ

F

f

–3dB

= f

Cut-off

= 0.995 kHz

1.65 V

low

high

t

Output

V

CC

t

V

GND

τ

= 50

µ

s

T = 100

µ

s

Peak-to-peak ripple voltage

Peak-to-peak ripple voltage:

∆

V

pk-pk

= 0.51 V

∆

V

pk-pk

PWM and Simple RC Low Pass Filter

OKAWA Electric Design

http://sim.okawa-denshi.jp/en/CRlowkeisan.htm

Peak-to-peak ripple voltage:

∆

V

pk-pk

= 3.03 V

f

Cut-off

= f

PWM

Peak-to-peak ripple voltage:

∆

V

pk-pk

= 0.51 V

Peak-to-peak ripple voltage:

∆

V

pk-pk

= 0.052 V

f

Cut-off

=

f

PWM

100

Peak-to-peak ripple voltage:

∆

V

pk-pk

= 0.026 V

f

Cut-off

=

f

PWM

200

1.65 V

f

Cut-off

=

f

PWM

10

PWM Resolution

f

Cut-off

=

f

PWM

= 1 kHz

1.65 V

10

f

Cut-off

=

f

PWM

= 10 kHz

100

f

Cut-off

=

f

PWM

= 100 kHz

200 f

Cut-off

= f

PWM

= 200 kHz

f

Timer CLK

8 bit

→

→

→

→

256 kHz

16 bit

→

→

→

→

65 536 kHz

32 bit

→

→

→

→

4 294 967 296 kHz

∆

V

pk-pk

= 3.03 V

∆

V

pk-pk

= 0.51 V

f

Timer CLK

8 bit

→

→

→

→

2 560 kHz

16 bit

→

→

→

→

655 360 kHz

32 bit

→

→

→

→

42 949 672 960 kHz

∆

V

pk-pk

= 0.052 V

f

Timer CLK

8 bit

→

→

→

→

25 600 kHz

16 bit

→

→

→

→

6 553 600 kHz

32 bit

→

→

→

→

429 496 729 600 kHz

∆

V

pk-pk

= 0.026 V

f

Timer CLK

8 bit

→

→

→

→

51 200 kHz

16 bit

→

→

→

→

13 107 200 kHz

32 bit

→

→

→

→

858 993 459 200 kHz

Timer PWM Resolution

Silnik prądu stałego

(DC Electric Motor)

http://en.wikipedia.org/wiki/DC_motor

na

przewodnik

z

pr

ą

dem

umieszczony w

polu

magnetycznym

działała

siła elektrodynamiczna

(siła Lorentza)

kierunek siły

(F) jest

prostopadły

do

kierunku linii

pola magnetycznego

(B) i

kierunku płyn

ą

cego

pr

ą

du

(I)

szczotkowy silnik pr

ą

du stałego

wykonuje obroty

przez oddziaływanie pola magnetycznego

ruchomego wirnika

zasilanego przez mechaniczny

komutator

i

nieruchomych magnesów stałych

(stojan)

komutator

(dwa półpier

ś

cienie)

zmienia kierunek

płyn

ą

cego

pr

ą

du

co pół obrotu wirnika

Silnik szczotkowy

prądu stałego

•

przeł

ą

czanie mi

ę

dzy poszczególnymi fazami

uzwojenia wirnika poprzez osadzone na wale

wirnika pr

ę

ty komutatora i nieruchome szczotki

w obudowie stojana

•

wł

ą

czanie przez szczotki kolejnych faz uzwojenia w

czasie obrotu wirnika, stały moment obrotowy i

ci

ą

gła praca silnika

•

zalety

: niskie koszty produkcji, łatwe sterowanie

•

wady

: wysoka emisja zakłóce

ń

elektromagnetycznych, problem szczotek

Silnik szczotkowy

(komutatorowy)

pr

ą

du stałego

(

D

direct

C

urrent Motor):

•

komutator mechaniczny,

wirnik z uzwojeniem

•

stojan z magnesami stałymi

AN10513 Brushed DC motor control using the LPC2101.

NXP, Application note, Rev. 01 – 12 January 2007

komutator

wirnik

szczotki

uzwojenia

obudowa

magnesy

stałe

wyprowadzenia

7

Silnik szczotkowy prądu stałego

(Brushed DC Electric Motor)

http://pl.wikipedia.org/wiki/Silnik_pr

ą

du_stałego

silnik pr

ą

du stałego z

magnesami stałymi

w uzwojeniu wirnika płynie

pr

ą

d, a wokół niego

powstaje pole magnetyczne

lewa strona wirnika jest

odpychana w prawo przez

lewy biegun magnesu

stałego i przyci

ą

gana przez

prawy biegun magnesu,

powoduj

ą

c obrót wirnika

gdy wirnik osi

ą

gnie

poło

ż

enie poziome,

komutator zmienia

kierunek pr

ą

du

płyn

ą

cego przez

uzwojenie wirnika,

zmieniaj

ą

c tym samym

kierunek wytworzonego

pola magnetycznego

proces powtarza si

ę

wirnik kontynuuje

obrót (bezwładno

ść

)

Sterowanie

silnikiem szczotkowym

[1#2]

STA6940M. Brushed DC Motor Driver IC With PWM Control.

Allegro MicroSystems, 2009

Forward

(do przodu)

Table 1. Input Truth Table, PWM Control

Input

Output

IN1

IN2

OA

OB

Motor Function

Low

Low High Z High Z

Free

(toczenie si

ę

, luz)

PWM Low

High

Low

Forward

(obroty do przodu)

Low PWM

Low

High

Reverse

(obroty do tyłu)

High High

Low

Low

Brake

(hamowanie)

Brake

(hamowanie)

Free

Reverse

(do tyłu)

Sterowanie

silnikiem szczotkowym

[2#2]

STA6940M. Brushed DC Motor Driver IC With PWM Control.

Allegro MicroSystems, 2009

Forward

Table 1. Input Truth Table, PWM Control

Input

Output

IN1

IN2

OA

OB

Motor Function

Low

Low High Z High Z Free (toczenie si

ę

, luz)

PWM Low

High

Low

Forward (obroty do przodu)

Low PWM

Low

High

Reverse (obroty do tyłu)

High High

Low

Low

Brake (hamowanie)

Brake

Free

Reverse

Czas martwy

(Dead Time):

czas wył

ą

czenia wszystkich

tranzystorów steruj

ą

cych

przy przeł

ą

czaniu w celu

unikni

ę

cia zwarcia zasilania

silnika

Switching Time

t

ON

Turn-On Time

–

–

130

ns

Switching Time

t

OFF

Turn-Off Time

–

–

77

ns

STA6940M. Brushed DC Motor Driver IC With PWM Control. Allegro MicroSystems, 2009

ELECTRICAL CHARACTERISTICS (T

A

= 25°C, V

BB

= 24 V, V

DD

= 5 V)

Characteristics

Symbol Test Conditions

Min. Typ. Max. Unit

Switching Time

t

CON

Measured from input

–

3.0

–

µ

s

to output on

Switching Time

t

COFF

Measured from input

–

2.7

–

µ

s

to output off

FDD13AN06A0

Fairchild Semi.

Silnik

bezszczotkowy

Silnik bezszczotkowy

(

B

rush

L

ess

D

direct

C

urrent

Motor):

•

uzwojenie stojana

•

pole magnetyczne

wytwarzane przez wiruj

ą

ce

magnesy stałe

•

komutator zast

ą

piony

elektronicznym falownikiem

•

zalety

: wysoka trwało

ść

ograniczona trwało

ś

ci

ą

ło

ż

ysk

(20 krotnie), precyzyjna regulacja obrotów (zamiast

silników krokowych)

•

wady

: wysoka cena (2-3 krotnie), skomplikowane

sterowanie

http://users.tinyworld.co.uk/flecc/4-pole-bldc-motor031102.swf

Brushless DC Motor

[1#2]

Brushless DC motor control using the LPC2141.

NXP, Application note AN10661, Rev. 01 – 17 October 2007

Hall Sensors

Hall Sensors

Magnets

Rotor

Magnet S

Rotor Magnet N

Stator Windings

Brushless

DC Motor

[2#2]

Brushless DC motor control using the LPC2141.

NXP, Application note AN10661, Rev. 01 – 17 October 2007

Motor: 120 W

Maxon EC-40

‘no-load’ speed is

5900 RPM at 24 V

maximum current

is 6 A

Motor commutation

set the PWM Timer duty cycle for speed

and drive Q1-Q6 MOSFET outputs for control of the three-phase

bridge

Timer1

generates a system-

interrupt every 10 ms

T

im

e

r0

10-bit

ADC

8

Sensorless Brushless

DC Motor Control

Figure 5.

Phase Voltages

AP08019. Sensorless Brushless DC Motor Control. Using Infineon

8-bit XC866 Microcontroller. Application Note, V1.0, Oct 2006, Infineon

Silnik krokowy

reluktancyjny

[1#2]

http://pl.wikipedia.org/wiki/Silnik_krokowy

http://en.wikipedia.org/wiki/Stepper_motor

1

2

3

4

Silnik krokowy

reluktancyjny

[2#2]

http://pl.wikipedia.org/wiki/Silnik_krokowy

http://en.wikipedia.org/wiki/Stepper_motor

k

ą

t obrotu silnika jest proporcjonalny do liczby

impulsów wej

ś

ciowych

precyzyjne pozycjonowanie i powtarzalno

ść

ruchu -

dokładno

ść

ok. 3 - 5% kroku i bł

ą

d nie kumuluje si

ę

z

kroku na krok

szybki rozbieg, hamowanie i zmiany kierunku

niezawodno

ść

- brak szczotek,

ż

ywotno

ść

ło

ż

ysk

bardzo niskie pr

ę

dko

ś

ci synchronicznych obrotów z

obci

ąż

eniem na wale silnika

szeroki zakres pr

ę

dko

ś

ci obrotowych; pr

ę

dko

ść

proporcjonalna do cz

ę

stotliwo

ś

ci

impulsów wej

ś

ciowych

rezonanse mechaniczne (niewła

ś

ciwe sterowanie)

trudno

ś

ci pracy z bardzo du

ż

ymi pr

ę

dko

ś

ciami

zjawisko gubienia kroków

du

ż

y pobór pr

ą

du i emisja ciepła

MCS51

PCA Features

[1#2]

The

PCA

consists of a :

• dedicated 16-bit counter/timer

• six 16-bit capture/compare modules

• each capture/compare module has its own associated I/O line (CEXn)

• I/O lines are routed through the Crossbar to Port I/O when enabled.

Each capture/compare module

may be configured to operate independently

in one of six modes:

• Edge-Triggered Capture

• Software Timer, High-Speed Output,

• Frequency Output,

• 8-Bit PWM

• 16-Bit PWM

The

PCA is configured and controlled

through the system controller's

Special Function Registers (SFR).

C8051F50x-F51x. Mixed Signal ISP Flash MCU Family.

Silicon Laboratories, Rev. 1.0 2/09

MCS51

PCA Features

[2#2]

SYSCLK/12

SYSCLK/4

T0 Overflow

SYSCLK

Ext Clock/8

Capture

Compare

Module 0

Capture

Compare

Module 1

Capture

Compare

Module 4

Capture

Compare

Module 5

WDT

ECI

CEX0

CEX1

CEX3

CEX4

Crossbar

Port I/O

PCA

CLOCK

MUX

max rate

=

SYSCLK/4

16-Bit Counter/Timer

C8051F50x-F51x. Mixed Signal ISP Flash MCU Family.

Silicon Laboratories, Rev. 1.0 2/09

...............

Problemy i pytania

1. Jakie jest cel stosowania liczników w mikrokontrolerach ?

2. W jakim celu do liczników jest doł

ą

czany preskaler i jaka jest jego rola ?

3. Na czym w licznikach polega tryb ’Up-Counting mode’ ?

4. Na czym w licznikach polega tryb ’Down-Counting mode’ ?

5. Na czym w licznikach polega tryb ’Up/Down-Counting mode’ ?

6. Na czym w licznikach polega tryb ’Compare mode’ ?

7. Na czym w licznikach polega tryb ’Capture mode’ ?

8. W jaki sposób w mikrokontrolerach jest wykrywane zbocze sygnału taktuj

ą

cego ?

9. Jakie s

ą

ograniczenia sygnałów taktuj

ą

cych liczniki mikrokontrolerów ?

10. Na czym polega wpis/odczyt synchroniczny liczników mikrokontrolerów ?

11. Co to jest Tick Timer i jaka jest jego rola ?

12. Jak interpretowa

ć

skrót PWM i jakie jest zastosowanie tej metody ?

13. Jakie jest przeznaczenie trybów PWM liczników mikrokontrolerów ?

14. Co oznacza poj

ę

cie BLDC ?

15. Co to jest PCA ?

Wyszukiwarka

Podobne podstrony:

10 Serial Interface 2015 www

13 Power 2015 www

4 Typy instrukcji Tryby adresowania 2015 www (1)

3 Przetw danych Typy proces 2015 www (1)

7 Stos 2015 www

12 DMA 2015 www

Lokalny program rewitalizacji osiedla „Stara Kolonia” w Brzeszczach 2005 2015 www old brzeszcze pl

6 Pamieci ROM RAM 2015 www

11 Przetworniki 2015 www

2 Architektura 2015 www

8 Przerwania 2015 www

5 Architektura MCU 2015 www (1)

10 Serial Interface 2015 www

11 Przetworniki 2015 www

Sprawozdanie 2015 www

więcej podobnych podstron