1

Podstawy techniki

mikroprocesorowej

ETEW006

Struktura mikroprocesora i

mikrokontrolera. Architektury

von Neumanna i harwardzka

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

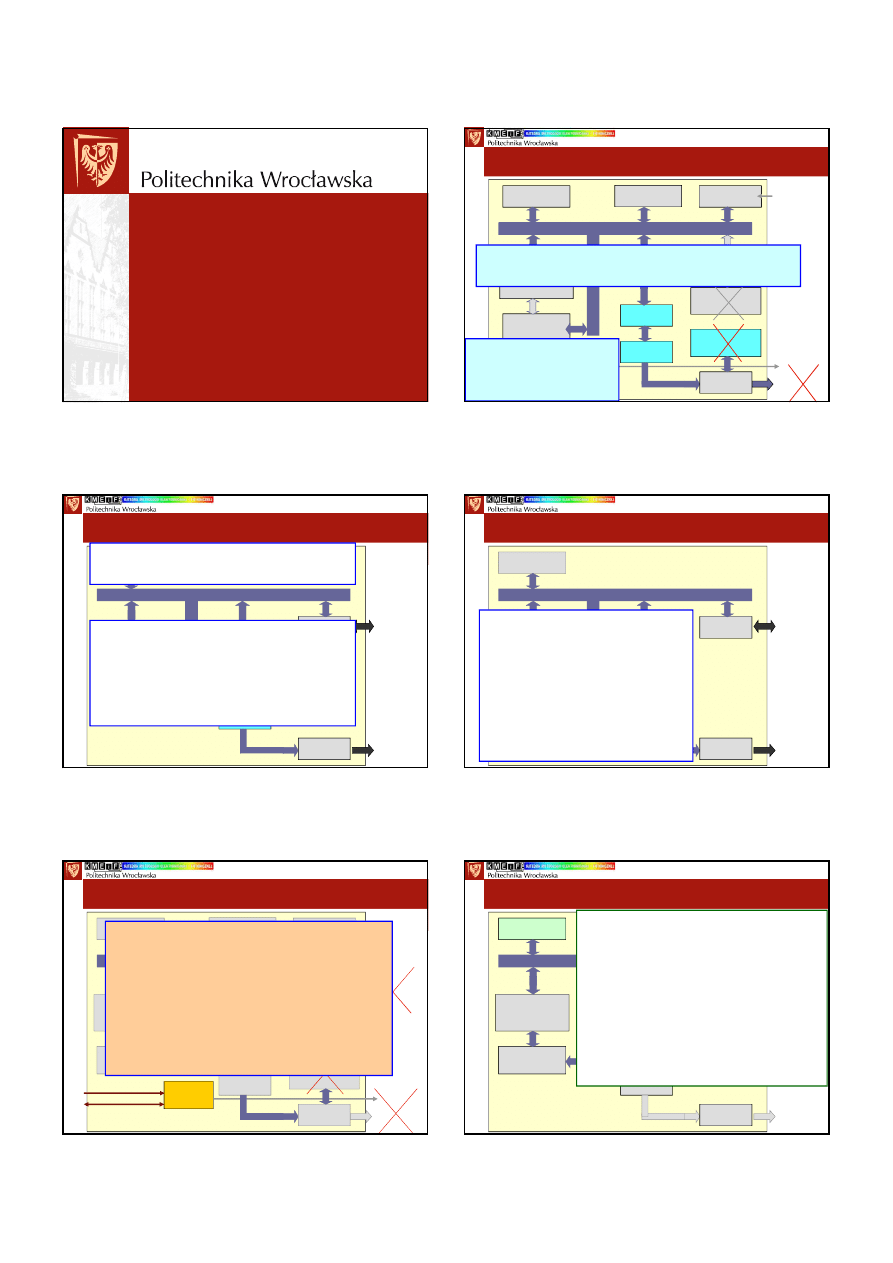

Dekoder Instrukcji i Licznik Rozkazów

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala adresowa i danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Dekoder

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Wewn

ę

trzna

Danych

Wewn

ę

trzna

Pami

ęć

Danych

Wewn

ę

trzna

Programu

Wewn

ę

trzna

Pami

ęć

Programu

Bufor

Bufor

Adresowy

Zasilanie

Układy

Taktuj

ą

ce

CLK

???

Wska

ź

nik

Stosu

Kontroler

Przerwa

ń

Zewn

ę

trzne

Przerwania

Licznik rozkazów

(Program

Counter / Instruction Pointer,

Register) – licznik adresuj

ą

cy

pami

ęć

kodu programu

(wykonywanego programu),

dane

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

Rejestr dekoduj

ą

cy instrukcje

(Instruction Decoder) – blok

funkcjonalny odpowiadaj

ą

cy za dekodowanie i synchronizacj

ę

wykonywanych instrukcji (programu)

Magistrale

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Bufor

Adresowy

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

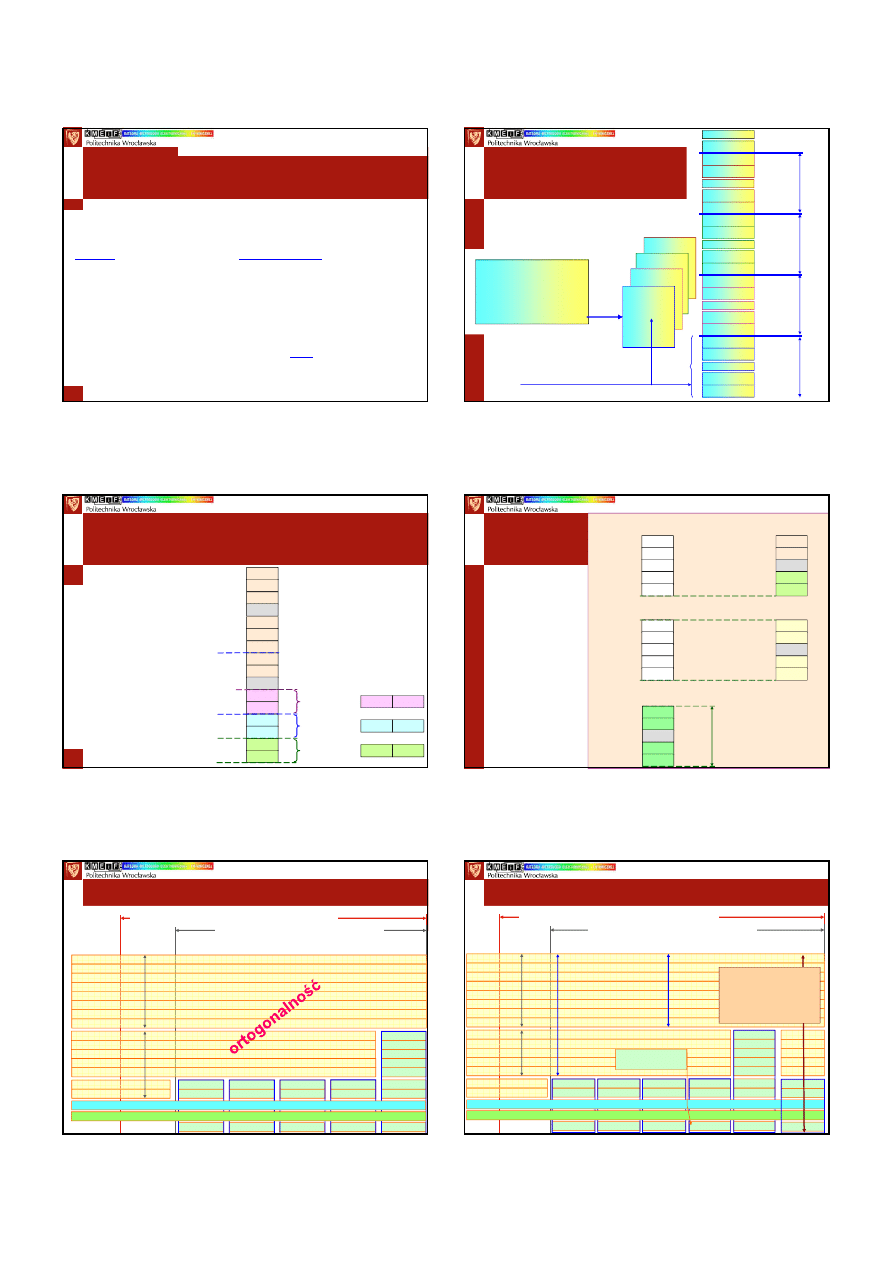

• wewn

ę

trzna

(Internal Bus) - do wymiany informacji w

wewn

ę

trznej strukturze mikroprocesora,

mikrokontrolera

• zewn

ę

trzna

(External Bus) - do komunikacji

mikroprocesora, mikrokontrolera z układami

zewn

ę

trznymi, np. pami

ę

ciami, układami wej

ś

ciowo-

wyj

ś

ciowymi; magistrala zewn

ę

trzna jest oddzielona

od magistrali wewn

ę

trznej za po

ś

rednictwem buforów;

Magistrala

(Bus) - to zespół linii, przewodów słu

żą

cych

do przesyłania informacji o tym samym charakterze oraz

układy steruj

ą

ce przepływem informacji:

Zasilanie

Magistrala adresowa i danych

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Bufor

Adresowy

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

Magistrala adresowa

(Address Bus) -

przesyłanie adresów pami

ę

ci lub układów

wej

ś

ciowo-wyj

ś

ciowych:

– jednokierunkowa, 2-stanowa

– jednokierunkowa, 3-stanowa ze stanem

wysokiej impedancji (3-state impedance)

w trybie HOLD lub DMA

Magistrala danych

(Data Bus) - przesyłanie

danych do/z pami

ę

ci lub układów wej

ś

ciowo-

wyj

ś

ciowych (dwukierunkowa, 3-stanowa ze

stanem wysokiej impedancji)

Zasilanie, Taktowanie, Sterowanie ..

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala adresowa i danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Dekoder

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

Wewn

ę

trzna

Danych

Wewn

ę

trzna

Pami

ęć

Danych

Wewn

ę

trzna

Wewn

ę

trzna

Pami

ęć

Programu

Bufor

Bufor

Adresowy

Zasilanie

Układy

Taktuj

ą

ce

CLK

RD, WR

???

Wska

ź

nik

Stosu

Kontroler

Przerwa

ń

Zewn

ę

trzne

Przerwania

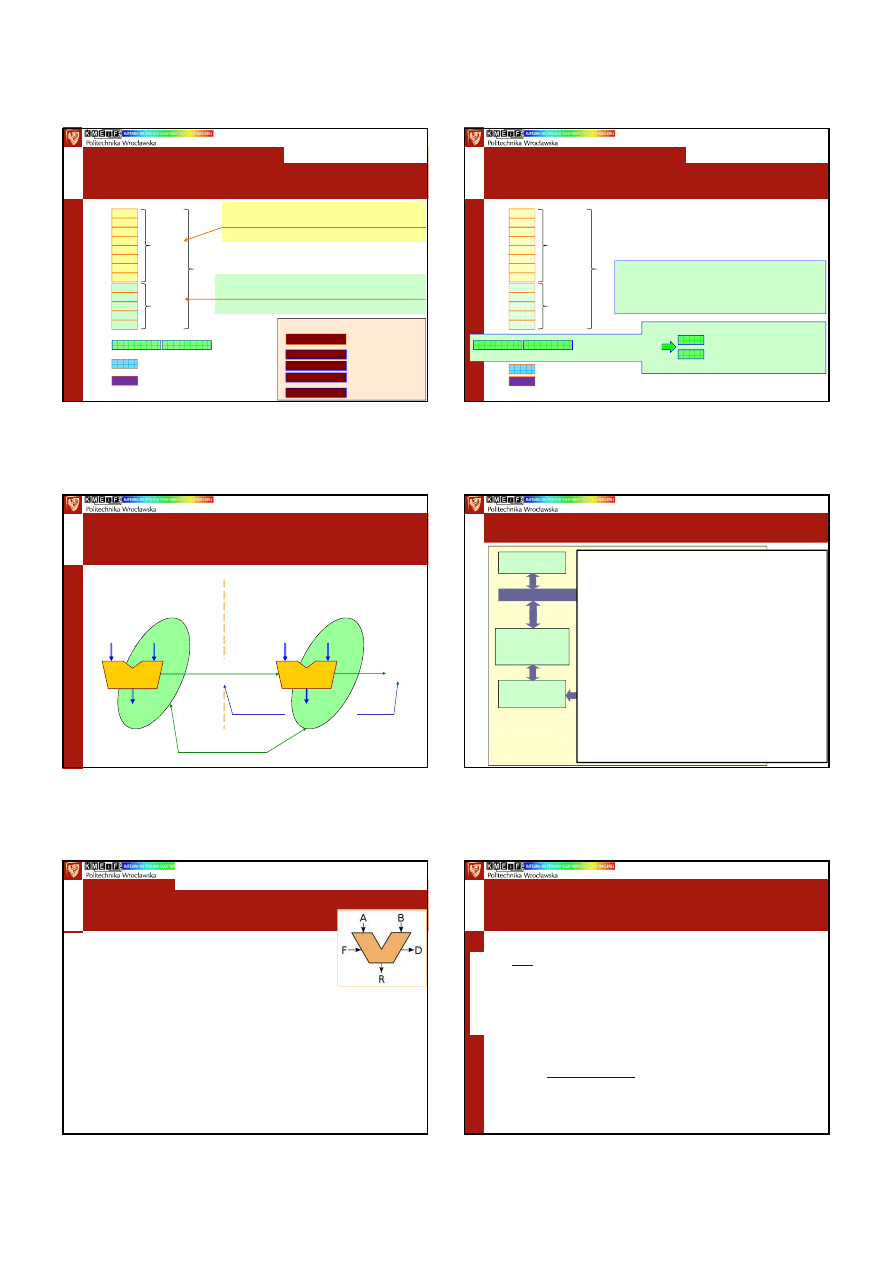

Magistrala steruj

ą

ca

(

Control Bus

) - sterowanie pami

ę

ci i

układów wej

ś

ciowo-wyj

ś

ciowych, np. zapis/odczyt do/z

pami

ę

ci/układów wej

ś

ciowo-wyj

ś

ciowych, chwilowe

wstrzymanie pracy mikroprocesora lub mikrokontrolera,

zgłoszenie przerwania itp.:

– jednokierunkowa, 2-stanowa

– jednokierunkowa, 3-stanowa w trybie HOLD / DMA

Magistrala zasilaj

ą

ca

(

Power Bus

) - rozdzielenie zasilania

ze wzgl

ę

du na redukcj

ę

zakłóce

ń

i zmniejszenie obci

ąż

enia

pr

ą

dowego

ś

cie

ż

ek zasilaj

ą

cych na płytce drukowanej; ró

ż

ne

napi

ę

cia rdzenia procesora i układów we/wy

Rejestry Robocze

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Dekoder

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Bufor

Bufor

Adresowy

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

Rejestr Roboczy

(Working Register) – wewn

ę

trzny

układ pami

ę

ciowy mikroprocesora, blok

funkcjonalny zbudowany z przerzutników

(najcz

ęś

ciej typu D) słu

żą

cy do chwilowego

zapami

ę

tywania danych i wyników

przetwarzania lub wykonywania operacji na

swojej zawarto

ś

ci; liczba przerzutników

wyznacza liczb

ę

bitów rejestru

Register File

– zestaw rejestrów

(an array of processor registers)

Register Bank

– rejestry grupowane w zestawy

(banki), np. w C51 4 banki rejestrów,

w ARM7 banki rejestrów zale

ż

ne od trybu pracy

2

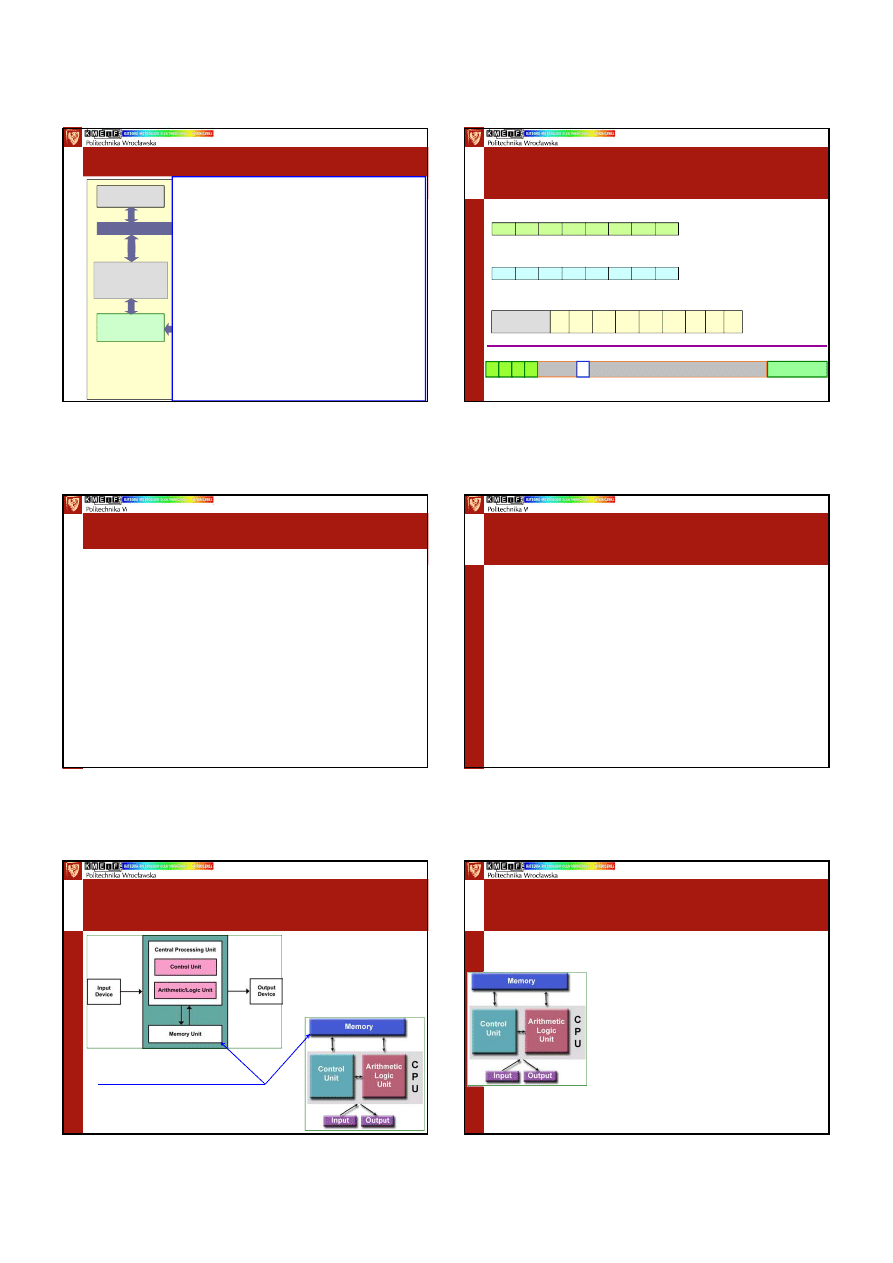

Bank rejestrów

(Register Bank)

zawiera okre

ś

lon

ą

liczb

ę

(bank, stron

ę

, grup

ę

, tablic

ę

)

rejestrów

(np. 8 rejestrów w MCS51, 5 rejestrów w ARM7/9 lub Cortex-Ax)

aktywny

(w danej chwili)

mo

ż

e by

ć

tylko jeden bank

(strona, grupa, tablica)

brak dodatkowych instrukcji

(w zestawie instrukcji procesora – ISA:

Instruction Set Architecture)

przy dost

ę

pie do wybranego banku rejestrów

w zestawie

instrukcji procesora

(

ISA

: Instruction Set Architecture) mog

ą

wyst

ą

pi

ć

dodatkowe instrukcje

do

zmiany

aktywnego

banku rejestrów

dane

mog

ą

by

ć

zapisywane

lub

odczytywane tylko

z

aktywnego banku

rejestrów

; mog

ą

istnie

ć

instrukcje lub sposoby (wynikaj

ą

ce z architektury

procesora) do przenoszenia danych z jednego banku do drugiego

http://en.wikipedia.org/wiki/Register_file

C500 Architecture and Instruction Set. User’s Manual. Infineon, July 2000

UM10120. LPC2131/2/4/6/8 User manual. NXP, Rev. 4 — 23 April 2012

MCS51

Banki rejestrów

128 BYTES

ON-CHIP

DATA MEMORY,

STACK,

4 REG. BANKS R[7:0]

DATA

IDATA

00h

7Fh

R0

R1

R6

R7

00h

01h

06h

07h

02h .. 05h

R0

R1

R6

R7

08h

09h

0Eh

0Fh

0Ah .. 0Dh

R0

R1

R6

R7

10h

11h

16h

17h

12h .. 15h

R0

R1

R6

R7

18h

19h

1Eh

1Fh

1Ah .. 1Dh

BIT0..7

20h

RB0

RB1

RB2

RB3

RB3

RB2

RB1

RB0

21h .. 7Fh

bank RB0 wybrany po

zerowaniu procesora

(RESET)

C500 Architecture and Instruction Set.

User’s Manual. Infineon, July 2000

numer

banku

ATmega

Rejestry ogólnego przeznaczenia

ATmega8/8L. 8-bit with 8KBytes

In-System Programmable Flash. Atmel, Rev.2486AA–AVR–02/2013

R0

R1

R2

.....

R13

R14

R15

R16

R17

.....

R26

R27

R28

R29

R30

R31

Rejestr–X

Rejestr–Y

Rejestr–Z

ka

ż

dy rejestr ma przypisany

adres pami

ę

ci danych

;

rejestry s

ą

mapowanie

bezpo

ś

rednio do pierwszych

32 bajtów w przestrzeni

danych u

ż

ytkownika (Data

Space)

nie jest to fizyczna pami

ęć

SRAM procesora

; taka

organizacja zapewnia du

żą

elastyczno

ść

w dost

ę

pie do

rejestrów

Adr = 0x00

0x01

0x02

0x0D

0x0E

0x0F

0x10

0x11

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

R26

R27

R28

R29

R30

R31

rejestry R26 .. R31

pełni

ą

dodatkowe

funkcje

s

ą

stosowane jako

16-bitowe rejestry

wska

ź

nikowe

w trybie

po

ś

redniego

adresowania przestrzeni

danych

ATmega8

Pamięć

danych

ATmega8/8L. 8-bit with 8KBytes

In-System Programmable Flash. Atmel, Rev.2486AA–AVR–02/2013, fig 8

$0000

$0001

.....

$001E

$001F

Bank rejestrów

(Register file)

R0

R1

.....

R30

R31

Rejestry we/wy

(I/O Registers)

$0020

$0021

.....

$005E

$005F

$00

$01

.....

$3E

$3F

Przestrze

ń

pami

ę

ci danych

(Data Address Space)

Wewn

ę

trzna pami

ęć

SRAM

(Internal SRAM)

$0060

$0061

.....

$045E

$045F

Figure 8. Mapa

pami

ę

ci

danych

(Data

Memory

Map)

1Kbyte Internal

SRAM

ARM7 Rejestry i wyjątki

(Exceptions)

User

System

Supervisor

Abort

Undefined Interrupt

Fast

Interrupt

tryb uprzywilejowany (Privileged Modes)

tryby wyj

ą

tków (Exception Modes)

R14_fiq

R13_fiq

R12_fiq

R11_fiq

R10_fiq

R9_fiq

R8_fiq

R14_irq

R13_irq

R14_und

R13_und

R14_abt

R13_abt

R14_svc

R13_svc

SPSR_svc

SPSR_abt

SPSR_und

SPSR_irq

SPSR _fiq

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

(SP)

R14

(LR)

re

je

s

tr

y

n

ie

b

a

n

k

o

w

a

n

e

re

je

s

tr

y

b

a

n

k

o

w

a

n

e

PC

CPSR

S. Furber: ARM System-on-chip architecture.

Addison-Wesley Professional, 2nd Edition, 2000

Rejestry Cortex-A8

User

System

Super-

visor

Abort

Unde-

fined

Interrupt

Fast

Interrupt

tryb uprzywilejowany (Privileged Modes)

tryby wyj

ą

tków (Exception Modes)

R14_fiq

R13_fiq

R12_fiq

R11_fiq

R10_fiq

R9_fiq

R8_fiq

R14_irq

R13_irq

R14_und

R13_und

R14_abt

R13_abt

R14_svc

R13_svc

SPSR_svc SPSR_abt SPSR_und SPSR_irq SPSR _fiq

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

(Stack Pointer)

R14

(Link Register)

u

n

b

a

n

k

e

d

re

g

is

te

rs

b

a

n

k

e

d

re

g

is

te

rs

PC

(Program Counter)

CPSR

(Current Program Status Register)

Saved Program

Status Register

tryb

ARM

tryb

Thumb

Cortex™-A8. Technical Reference Manual.

Revision: r3p2. ARM, DDI 0344K, fig. 2-10

Secure

monitor

R14_mon

R13_mon

SPSR_mon

efekt dwóch stanów pracy:

– bezpiecze

ń

stwa

(Secure state)

– braku bezpiecze

ń

stwa

(Nonsecure state)

3

Cortex

–

M

Rejestry ogólnego przeznaczenia

rejestry ogólnego przeznaczenia rdzenia

(General Purpose ARM Core Register)

Link Register (LR)

Program Counter (PC)

Stack

Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

rejestry

(Low

Register)

rejestry

(High

Register)

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13 (PSP)

R14

PC

R13 (MSP)

rejestry dost

ę

pne przez

wszystkie 16-bitowe

instrukcje

Thumb

i

wszystkie 32-bitowe

instrukcje

Thumb-2

p

rzy

p

a

d

k

o

w

e

w

a

rt

o

ś

c

i

re

je

s

tr

ó

w

p

o

s

ta

n

ie

R

E

S

E

T

rejestry dost

ę

pne przez

wszystkie 32-bitowe

instrukcje

Thumb-2

i

nie wszystkie 16-bitowe

instrukcje

Thumb

xPSR

PRIMASK

FAULTMASK

BASEPRI

CONTROL

Program status

register

Interrupt

mask

registers

Control register

Special registers

Cortex

–

M

Rejestry wskaźnika stosu

(Stack Pointer)

MSP

PSP

Main Stack Register

(SP_main po Reset)

Process Stack Register

(SP_process)

Link Register (LR)

Program Counter (PC)

Stack Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R14

PC

2 najmniej znacz

ą

ce bity wska

ź

nika stosu

(MSP lub PSP) s

ą

zawsze równe 0, co

oznacza,

ż

e s

ą

zawsze wyrównane do słowa

(

word aligned

)

R13 (PSP)

R13 (MSP)

rejestry ogólnego przeznaczenia rdzenia

(General Purpose ARM Core Register)

rejestry

(Low

Register)

rejestry

(High

Register)

Rejestry — ALU — Status

Dodawanie dziesiętne:

3

8

+

6

4

=

10

2

Krok 1

dodawanie jedno

ś

ci

ALU

4-bit

BCD

reg_1=

8

reg_2=

4

wynik=

2

przeniesienie

=

1

Krok 2

dodawanie dziesi

ą

tek

ALU

4-bit

BCD

reg_1=

3

reg_2=

6

wynik=

0

przeniesienie

=

1

najcz

ęś

ciej

Akumulator

status

(setki)

status

(dziesi

ą

tki)

Rejestry Robocze, Statusowy i ALU

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala danych

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Bufor

Adresowy

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

Rejestry Robocze (Working Registers)

– zespół

przerzutników przechowuj

ą

cych argumenty

operacji wykonywanych przez jednostk

ę

arytmetyczno-logiczn

ą

, argumenty instrukcji itp.

ALU (Arithmetic Logic Unit)

– jednostka

wykonuj

ą

ca podstawowe operacje arytmetyczno-

logiczne, np. dodawanie (+) i odejmowanie

arytmetyczne (–), negacj

ę

arytmetyczn

ą

, iloczyn i

sum

ę

logiczn

ą

(AND, OR), sum

ę

logiczn

ą

z

wył

ą

czno

ś

ci

ą

(XOR), negacj

ę

logiczn

ą

(NOT),

przesuni

ę

cia (SHIFT

),

obroty

(

ROTATE) itp.

Rejestr Statusowy (Status Register)

– rejestr z

1-bitowymi wynikami operacji wykonywanych

przez jednostk

ę

arytmetyczno-logiczn

ą

,

np. C, Z, N, V itp.

Układ arytmrtyczno-logiczny

(Arithmetic

&

Logic Unit)

model ALU

(Arithmetic & Logic Unit) zaproponowany

w 1945 roku przez Johna von Neumanna przy spisie

zało

ż

e

ń

dla nowego komputera EDVAC

układ cyfrowy do wykonywania

:

–

operacji arytmetycznych (dodawanie, odejmowanie, mno

ż

enie, dzielenie ..)

–

operacji logicznych (and, or, xor) pomi

ę

dzy dwiema liczbami

–

operacji jednoargumentowych takie jak przesuni

ę

cie bitów (shift, rotate)

negacja logiczna (not) lub arytmetyczna

wykonywanie działa

ń

na liczbach całkowitych bez znaku (kod binarny) lub

liczbach całkowitych ze znakiem (kod uzupełnienia do dwóch, U2)

jednostka zmiennoprzecinkowa (Floating Point Unit) równie

ż

wykonuje

operacje arytmetyczne na dwóch warto

ś

ciach, jednak s

ą

to liczby w

reprezentacji zmiennoprzecinkowej, pojedynczej precyzji (zwykle standard

IEEE 754)

http://en.wikipedia.org/wiki/Arithmetic_logic_unit

http://pl.wikipedia.org/wiki/Jednostka_arytmetyczno-logiczna

UM10398. LPC111x/LPC11Cxx User manual. NXP, Rev. 12.3 — 10 June 2014

Akumulator

MCS51

:

ACC

– adres akumulatora (0xE0)

A – skrót akumulatora w mnemonikach (np. MOV A, #12h)

w akumulatorze jeden z argumentów i wynik operacji:

– arytmetycznych: dodawania, odejmowania, mno

ż

enia, dzielenia,

– operacji logicznych: and, or, xor, not, przesuni

ę

cia, obrotu, wymiany

Brak akumulatora

:

AVR, ATmega

(8-bitowy),

MSP430

(16-bitowy),

ARM7/9

,

Cortex-A/R/M

(32- i 64-bitowy)

C500 Architecture and Instruction Set. User’s Manual. Infineon, July 2000

4

Rejestr Statusowy

[1#2]

Jednostka

Arytmetyczno–

–Logiczna

Wewn

ę

trzna magistrala danych

Rejestry

Rejestry

Robocze

Licznik

Rozkazów

Licznik

Rozkazów

Dekoder

Instrukcji

Dekoder

Instrukcji

Rejestr

Statusowy

Bufor

Danych

Bufor

Bufor

Adresowy

Zewn

ę

trzna

Magistrala

Danych

Zewn

ę

trzna

Magistrala

Adresowa

PSW (Program Status Word Register)

– rejestr

stanu (statusu) procesora po wykonanej operacji

zawieraj

ą

cy

znaczniki

(

Flags

), 1-bitowe

informacje o przebiegu lub wyniku

wykonywanych operacji, np. dla 8-bitowych liczb:

C (Carry)

– przeniesienie, przekroczenie zakresu liczb

całkowitych bez znaku (np.: 0 .. 255)

AC (Auxiliary Carry)

– przeniesienie połówkowe,

stosowane przy korekcji dziesi

ę

tnej (BCD)

OV (Overflow)

– nadmiar, przekroczenie zakresu liczb

całkowitych ze znakiem (np.:

−

128 .. +127)

Z (Zero)

– warto

ść

zerowa

P (Parity)

– parzysto

ść

S (Sign)

– znak liczby, rozró

ż

nienie liczb dodatnich i

ujemnych zapisanych w kodzie U2

Rejestr Statusowy

[2#2]

RS1 RS0

OV

F1

P

CY AC

F0

MCS51

S

V

N

Z

C

I

T

H

ATmega

ATmega8/8L. 8-bit with 8KBytes

In-System Programmable Flash.

Atmel, Rev.2486Z–AVR–02/11, p.11

C500 Architecture and Instruction Set.

User’s Manual. Infineon, July 2000, p.2-3

CPU

OFF GIE

N

Z

C

SCG

1

SCG

0

OSC

OFF

MSP430

V

Reserved

MSP430x4xx Family.

User’s Guide

TI, SLAU056K,

December 2012, p.3-6

N Z C V

27

6

23

5

0

Exception

number

24

31 30 29 28

Res

Reserved

T

Cortex™-

M0

(-M0+)

Devices. Generic User Guide. ARM DUI 0497A, 8 October 2009, p.2-4

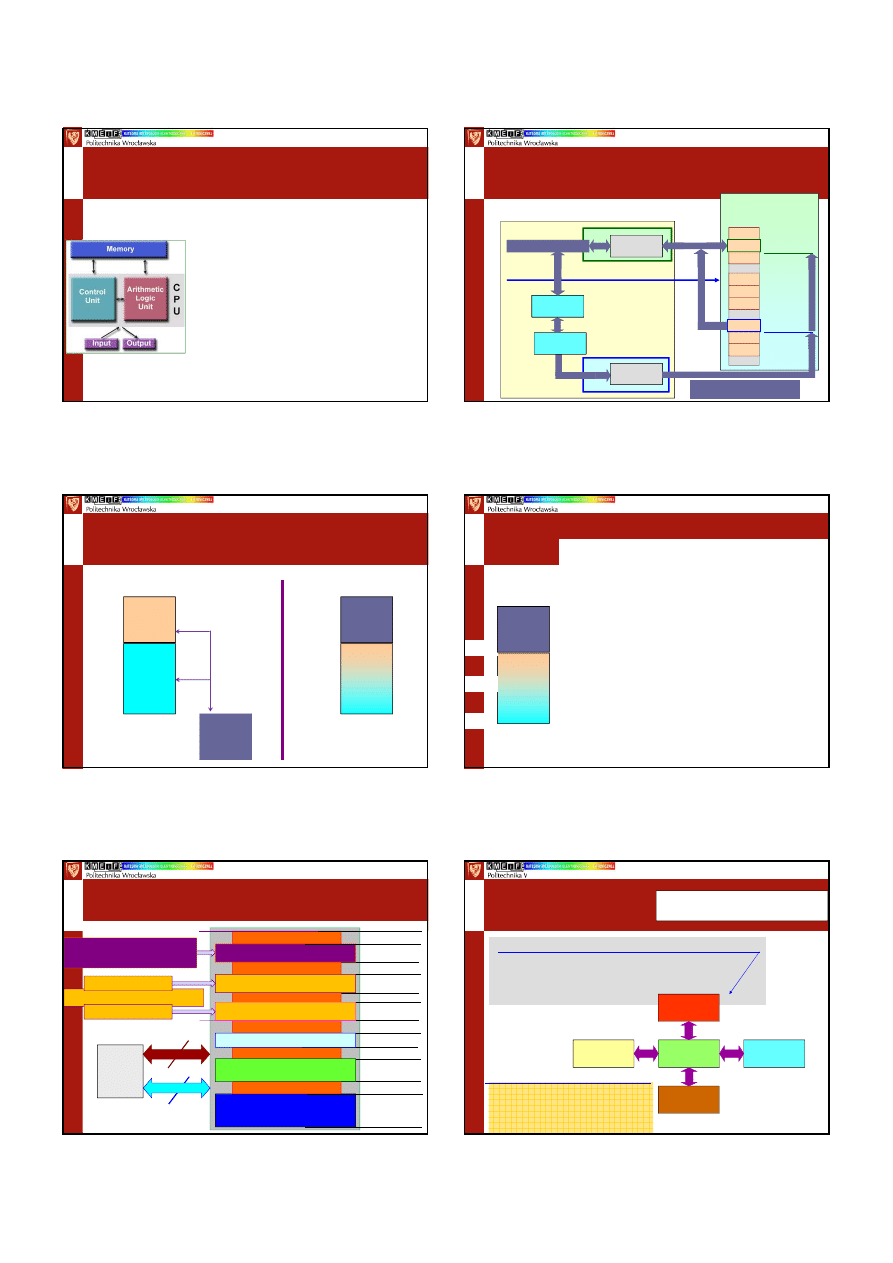

Architektura komputera

Architektura von Neumana

[1#5]

http://en.wikipedia.org/wiki/Von_Neumann_architecture

J. Biernat: Architektura komputerów. Oficyna Wydawnicza Politechniki Wrocławskiej, 2001

Najstarsze maszyny obliczeniowe

(komputery) miały

stały kod

(zasad

ę

)

działania, np. kalkulator:

–

wykonywanie podstawowych operacji matematycznych

–

wykluczone inne zastosowania, np. jako edytor tekstu, konsola do gier

Zmiana zasady działania to

komputery przechowuj

ą

ce program

:

–

b

ę

d

ą

cy uporz

ą

dkowanym, szczegółowym opisem wykonywanych oblicze

ń

–

zło

ż

ony z zestawu instrukcji przechowywanych w pami

ę

ci (zestaw instrukcji

tworzy program działania)

Matematyk

Alan Turing

(University of Cambridge) przedstawił w London

Mathematical Society (1936) koncepcj

ę

uniwersalnej maszyny

obliczeniowej

(znana jako Uniwersalna maszyna Turinga) z

nieograniczonymi mo

ż

liwo

ś

ciami,

zasobami

(pami

ę

ci

ą

),

zawieraj

ą

cymi

zarówno instrukcje oraz dane

John von Neumann poznał Alana Turinga w 1935 w University of Cambridge

Architektura komputera

Architektura von Neumana

[2#5]

Projekt ENIAC

, nad którym pracowali

J. Presper Eckert

oraz

John

Mauchly

w Moore School of Electrical Engineering (University of

Pennsylvania) zakładał

jednolity sposób pami

ę

tania kodu programu i

danych

, niezale

ż

nie od koncepcji Alana Turinga.

John von Neumann

, który był zaanga

ż

owany w Projekcie Manhattan w

Los Alamos National Laboratory (projekt bomby atomowej wymagał

ogromnych ilo

ś

ci oblicze

ń

)

doł

ą

czył do J. P. Eckert’a oraz J.

Mauchly’ego

.

w lecie 1944 roku

Herman Heine Goldstine

(matematyk i współtwórca

komputera ENIAC)

w nazwał niedoko

ń

czony projekt koncepcj

ą

von

Neumanna

, ku konsternacji Eckert’a i Mauchly'ego; dokument ten został

przeczytany przez dziesi

ą

tki kolegów von Neumann’a w Ameryce i

Europie, a

nazwa zasady działania pozostała do dzisiaj

.

http://en.wikipedia.org/wiki/Von_Neumann_architecture

J. Biernat: Architektura komputerów. Oficyna Wydawnicza Politechniki Wrocławskiej, 2001

Architektura komputera

Architektura von Neumana

[3#5]

http://en.wikipedia.org/wiki/Von_Neumann_architecture

Pami

ęć

(Memory) zawiera

kod programu i dane (oblicze

ń

)

Architektura komputera

Architektura von Neumana

[4#5]

http://en.wikipedia.org/wiki/Von_Neumann_architecture

http://pl.wikipedia.org/wiki/Architektura_von_Neumanna

Komputer o architekturze von Neumann’a

tworz

ą

:

–

pami

ęć

komputerowa

(Memory) przechowuj

ą

ca

instrukcje programu oraz dane programu; ka

ż

da

komórka pami

ę

ci ma unikatowy identyfikator

nazywany jej adresem

–

jednostka steruj

ą

ca

(Control Unit)

odpowiedzialna za pobieranie danych i instrukcji

z pami

ę

ci oraz ich sekwencyjne przetwarzanie

–

jednostka arytmetyczno-logiczna

(Arithmetic

Logic Unit) odpowiedzialna za wykonywanie

podstawowych operacji arytmetycznych

–

urz

ą

dzenia wej

ś

cia/wyj

ś

cia

(Input / Output)

słu

żą

ce do interakcji z operatorem

5

Architektura komputera

Architektura von Neumana

[5#5]

http://en.wikipedia.org/wiki/Von_Neumann_architecture

http://pl.wikipedia.org/wiki/Architektura_von_Neumanna

System komputerowy

zbudowany w oparciu o

architektur

ę

von Neumanna

powinien:

– mie

ć

sko

ń

czon

ą

i funkcjonalnie pełn

ą

list

ę

rozkazów

(Instruction Set Architecture)

– mie

ć

mo

ż

liwo

ść

wprowadzenia programu do

systemu komputerowego poprzez urz

ą

dzenia

zewn

ę

trzne

i jego

przechowywanie w pami

ę

ci

w sposób identyczny jak danych

– dane i instrukcje

w takim systemie powinny by

ć

jednakowo dost

ę

pne dla procesora

– informacja jest tam przetwarzana dzi

ę

ki

sekwencyjnemu odczytywaniu instrukcji z

pami

ę

ci komputera i wykonywaniu

tych

instrukcji

w procesorze.

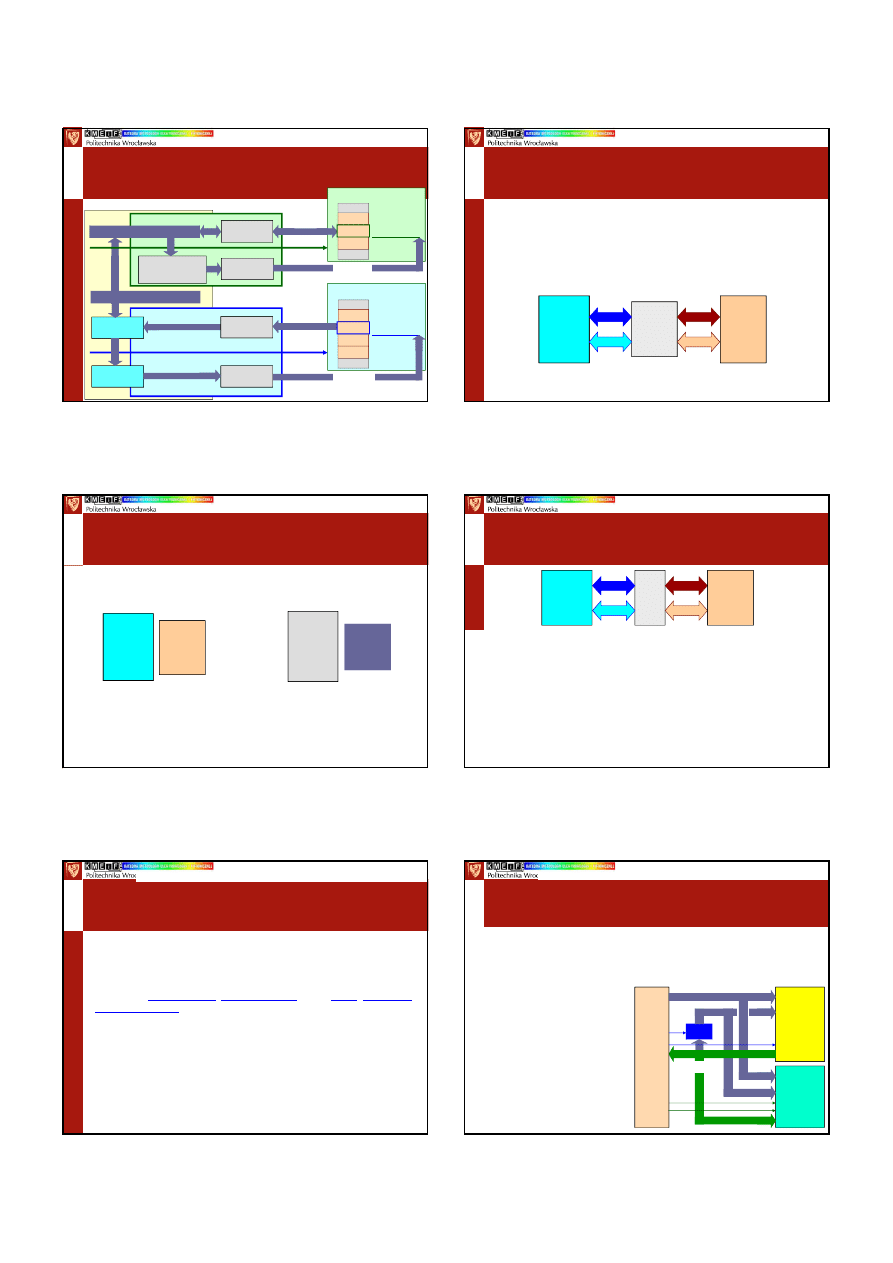

Architektura von NEUMANNa

albo Kod albo Dane

Data & Addr Bus

Bufor

Danych

Bufor

Adresowy

Licznik

Licznik

Rozkazów

addr_1

addr_1+1

addr_1+2

addr_2

addr_2+1

addr_2+2

addr_3

addr_3+1

addr_3+2

CPU

Pami

ęć

Danych i Programu

instr

Dane

Adres

Danych lub Instrukcji

MEM

RD

MEM

WR

data

In

s

tr

u

k

c

je

NAPRZEMIENNY DOST

Ę

P

DO DANYCH LUB INSTRUKCJI

Dekoder

Instrukcji

Architektura von NEUMANN’a

Pamięć i układy we/wy

addr1

addr2

Pami

ęć

programu

(Program

Memory)

Mapowanie

układów we/wy

w przestrzeni pami

ę

ci

(Memory Mapped I/O)

addr1

addr2

addr3

Data

&

Program

Memory

Układy

we / wy

(I/O)

Pami

ęć

Danych

(Data

Memory)

addr??????

Układy

we / wy

(I/O)

ró

ż

ne

instrukcje

??????

ró

ż

ne

zasady

dost

ę

pu

??????

Architektura von NEUMANNa

Wady

Zalety

addr1

addr2

addr3

Pami

ęć

Danych

i

Programu

Urz

ą

dzenia

we/wy

te same magistrale dla kodu i danych

(prostota układów

adresuj

ą

cych i dekoduj

ą

cych):

–

adresowa (Address Bus)

–

danych (Data Bus)

–

steruj

ą

ca (WR#/MemWr#, RD#/MemRd#, OE#/CS# itp.)

zwykle,

liniowe adresowanie

przestrzeni pami

ę

ci

warto

ść

adresu decyduje o dost

ę

pie do pami

ę

ci

programu, danych lub układów we/wy

brak ró

ż

nych instrukcji

przy dost

ę

pie do kodu programu

(ROM/Flash)

i danych (RAM)

uproszczona struktura kompilatora

mo

ż

liwo

ść

uruchomienia

programu

dynamicznie

zapisanego w pami

ę

ci RAM (danych, szybko

ść

RAM – Flash)

mo

ż

liwo

ść

wykonania samomodyfikuj

ą

cego

si

ę

kodu

programu, np. szyfrowanie kodu

Architektura von-NEUMANN’a

Cortex-M0

[NXP LPC1114]

CPU

Data

Addr

Pami

ęć

programu

(Program Memory

32KB

MAX

on-chip Flash)

0x1000 0000

0x0000 0000

Zarezerwowane (Reserved)

32-bity

32-bity

Zarezerwowane (Reserved)

0x4000 0000

0x5000 0000

0xE000 0000

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, fig. 7

0x0001 0000

0x1000 2000

Zarezerwowane (Reserved)

1 GB

0x4008 0000

Zarezerwowane (Reserved)

0x5020 0000

Zarezerwowane (Reserved)

Własna magistrala peryferii

(PPB Private Peripheral Bus)

0xE010 0000

Zarezerwowane (Reserved)

0xFFFF FFFF

Pami

ęć

danych

(Data Memory – 8KB

MAX

SRAM)

Peryferia typu APB

(APB Peripherals)

Peryferia typu AHB

(AHB Peripherals)

4 GB

Rdze

ń

(core): NVIC, SysTick,

System Control Block;

(only word)

AHB – Advanced High-performance Bus

APB – Advanced Peripheral Bus

pozostałe peryferia

GPIO PIO3..PIO0

0x1FFF 0000

0x1FFF 4000

16KB BootLoader

Przetwarzanie

sygnałów

http://en.wikipedia.org/wiki/Harvard_architecture

Pobranie dwóch argumentów

(współczynniki i warto

ś

ci

wej

ś

ciowe/wyj

ś

ciowe)

w jednym cyklu instrukcji

instrukcje dodawania i mno

ż

enia

obsługa buforów (buforów pier

ś

cieniowych)

sprz

ę

towe opó

ź

nienia

Architektura Harvard

– fizyczne

rozdzielenie pami

ę

ci i dost

ę

pu

do instrukcji oraz danych

(efektywny dost

ę

p do pami

ę

ci)

Pami

ęć

instrukcji

Pami

ęć

danych

Układy

we/wy

ALU

Jednosta

steruj

ą

ca

współczynniki w

kodzie programu

(ROM)

dane

wej

ś

ciowe/wyj

ś

ciowe w

pami

ę

ci danych (RAM)

y[n]

=

a[k]

∗

x[n–k]

+

b[j]

∗

y[n–j]

Σ

Σ

k

j

http://en.wikipedia.org/wiki/Harvard_architecture

J. Biernat: Architektura komputerów. Oficyna Wydawnicza Politechniki Wrocławskiej, 2001

6

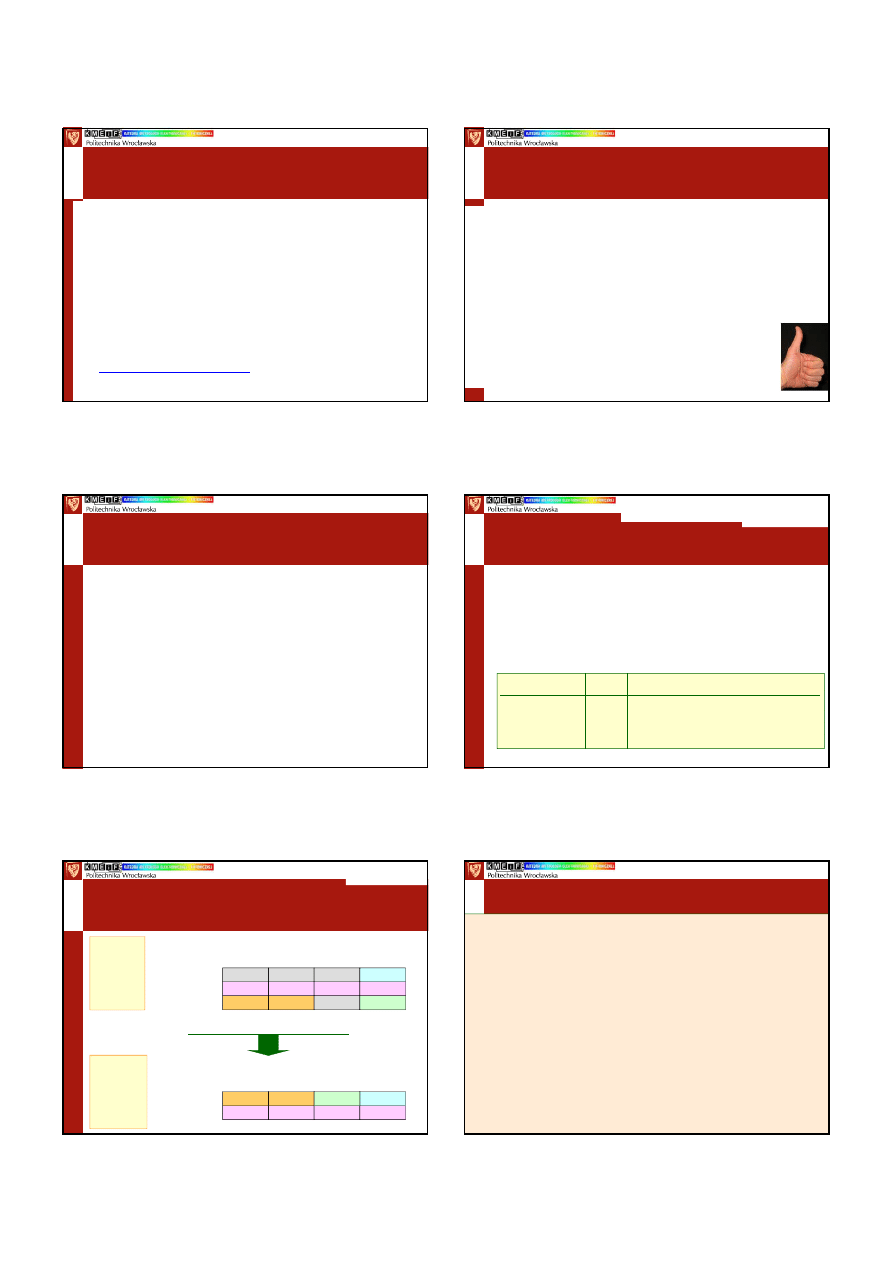

Architektura HARVARD

i Kod i Dane

Internal Data Bus

Dekoder

Dekoder

Instrukcji

Bufor

Adresowy

Licznik

Licznik

Rozkazów

CPU

obliczanie

adresu

pami

ę

ci danych

Internal Address Bus

Bufor

Adresowy

Bufor

Danych

RAM

RD

RAM

WR

addr_2

addr_2+1

addr_2+2

Pami

ęć

Danych

Dane

Adres

Danych

Bufor

Instrukcji

ROM

RD

ROM

WR

addr_1

addr_1+1

addr_1+2

Pami

ęć

Programu

Instrukcje

Adres

Instrukcji

data

instr

RÓWNOCZENY DOST

Ę

P

DO DANYCH I INSTRUKCJI

Architektura Harvard

ró

ż

ne magistrale pami

ę

ci programu i danych

Pami

ęć

programu

(Program

Memory)

Pami

ęć

Danych

(Data

Memory)

wykorzystuje

fizycznie rozdzielne pami

ę

ci

instrukcji (kodu) i danych

ka

ż

dy

rodzaj pami

ę

ci

jest

dost

ę

pny

za po

ś

rednictwem

innej magistrali

instrukcje

i

dane

(argumenty) mog

ą

by

ć

pobrane

jednocze

ś

nie,

równolegle

CPU

Instr

Addr

Data

Addr

Architektura Harvard

Pamięć i układy we/wy

addr1

addr2

addr3

addr4

rozdzielone układy we/wy

Pami

ęć

Programu

lub

pami

ęć

danych

addr5

addr6

Układy

we/wy

addr7

addr8

rozdzielone pami

ę

ci

Pami

ęć

programu

(Program

Memory)

Pami

ęć

Danych

(Data

Memory)

Architektura HARVARD

Wady i Zalety

CPU

Instr

Addr

Data

Addr

rozdzielone magistrale dla kodu i danych

(zło

ż

ona struktura układów

adresuj

ą

cych i dekoduj

ą

cych),

du

ż

a szybko

ść

wykonywanego

programu

ze

wzgl

ę

du

na równoczesny dost

ę

p do kodu i danych

łatwo

ść

implementacji przetwarzania potokowego

ró

ż

ne instrukcje

przy dost

ę

pie do kodu programu (ROM/Flash) i danych (RAM)

nie

ma mo

ż

liwo

ś

ci

uruchomienia

programu

dynamicznie

zapisanego w pami

ę

ci

RAM (danych)

zerowa warto

ść

adresu kodu (np. 24-bitowe adresowanie) nie jest tym samym co

zerowa warto

ść

adresu danych (np. 8-bitowe adresowanie)

trudno

ś

ci z implementacj

ą

,

du

ż

a liczba wyprowadze

ń

Pami

ęć

programu

(Program

Memory)

Pami

ęć

Danych

(Data

Memory)

Zmodyfikowana Architektura

HARVARD

[1#4]

Pami

ęć

kodu

(instrukcje)

i pami

ęć

danych zajmuj

ą

ró

ż

n

ą

przestrze

ń

adresow

ą

ale wykorzystuj

ą

wspólne magistrale adresow

ą

i danych

Zawarto

ść

pami

ę

ci kodu i pami

ę

ci danych jest w ró

ż

ny, sprz

ę

towy

sposób dost

ę

pna do jednostki centralnej CPU

(cecha konstrukcyjna

CPU);

instrukcje i dane s

ą

dost

ę

pne w ró

ż

ny sposób

Zmodyfikowana architektura Harvard

, odmiana ‚czystej’ architektury

Harvard,

umo

ż

liwia dost

ę

p do zawarto

ś

ci pami

ę

ci kodu

(instrukcji)

tak, jak gdyby były to

dane

(wi

ę

kszo

ść

współczesnych komputerów,

które wykorzystuj

ą

architektur

ę

Harvard w rzeczywisto

ś

ci korzysta ze

zmodyfikowanej architektury Harvard), np.

Cortex-M3

(architektura

ARMv7-M)

http://en.wikipedia.org/wiki/Modified_Harvard_architecture

ARM

®

Developer Suite. Developer Guide. ARM DUI 0056D, November 2001, Version 1.2

Zmodyfikowana Architektura

HARVARD

[2#4]

Pami

ęć

Kodu

Programu

(Flash)

Pami

ęć

Danych

(RAM)

P0

P2

adres

bufor

ALE

CPU

MCS51

PSEN#

RD#

WR#

A

15..8

A

7..0

D

7..0

adres/dane

Pami

ęć

kodu

(instrukcje)

i pami

ęć

danych zajmuj

ą

ró

ż

n

ą

przestrze

ń

adresow

ą

ale wykorzystuj

ą

wspólne magistrale adresow

ą

i danych:

oznacza ró

ż

ne typy pami

ę

ci,

ró

ż

ne warto

ś

ci (struktury

binarne)

–

w strukturze von NEUMANNa i

zmodyfikowanej strukturze

HARVARD interpretacja

zawarto

ś

ci (struktury binarnej)

zerowego adresu w pami

ę

ci

kodu i w pami

ę

ci danych zale

ż

y

wył

ą

cznie od realizowanego

programu (zwykle wymaga

u

ż

ycia innych instrukcji, np.

MOVC i MOVX w MCS51)

–

w strukturze HARVARD zerowy adres w pami

ę

ci kodu i w pami

ę

ci danych

http://en.wikipedia.org/wiki/Modified_Harvard_architecture

ARM

®

Developer Suite. Developer Guide. ARM DUI 0056D, November 2001, Version 1.2

7

Zmodyfikowana Architektura

HARVARD

[3#4]

Zawarto

ść

pami

ę

ci kodu i pami

ę

ci danych jest w ró

ż

ny, sprz

ę

towy

sposób dost

ę

pna przez jednostk

ę

centraln

ą

CPU:

–

w strukturze HARVARD rozdzielony sposób dost

ę

pu do obu typów

pami

ę

ci

–

w zmodyfikowanej strukturze HARVARD

rozdzielony dost

ę

p jedynie

do pami

ę

ci podr

ę

cznej

(I-Cache, D-Cache)

oraz TCM

ARM

(Tightly

Coupled Memory

1

) – pami

ę

ci konfigurowalnej, poł

ą

czonej,

ś

ci

ś

le

powi

ą

zanej ale jednolity dla pozostałych pami

ę

ci

–

równoczesny dost

ę

p do pami

ę

ci kodu

(instrukcje) i

danych

(dane),

wi

ę

ksza szybko

ść

realizacji programu

–

z punktu widzenia programisty zmodyfikowana architektura

HARVARD zachowuje si

ę

jako struktura von NEUMANNa

(mo

ż

liwo

ść

samomodyfikacji programu), z wyj

ą

tkiem dost

ę

pu do Cache i TCM

1

) ARM

®

Developer Suite. Developer Guide.

ARM DUI 0056D, November 2001, Version 1.2, p.7-2

Zmodyfikowana Architektura

HARVARD

[4#4]

Instrukcje i dane s

ą

dost

ę

pne w ró

ż

ny sposób:

–

w komputerze MARK I kod programu wprowadzany za pomoc

ą

ta

ś

my

papierowej, a dane pami

ę

tane w układach elektro-mechanicznych

–

w strukturze HARVARD, np. w mikrokontrolerach serii PIC (Microchip)

stosowane 12-bitowe adresowanie pami

ę

ci kodu (Flash) i 8-bitowe

adresowanie pami

ę

ci danych (RAM)

–

w strukturze von NEUMANN’a (ARM7TDMI) i zmodyfikowanej

HARVARD (ARM9, Cortex-M3) jednolity sposób dost

ę

pu do:

•

pami

ę

ci kodu (Flash) dost

ę

p 16-bitowy (rozkazy Thumb) i

32-bitowy (rozkazy ARM w ARM7 lub Thumb-2 w Cortex-M3)

•

danych (RAM) – mo

ż

liwy 8-, 16- i 32-bitowy dost

ę

p do danych

Alokacja programu

Alokacja programu

(program allocation) - sposób rozmieszczenia

programu w pami

ę

ci komputera, mikrokomputera, mikrokontrolera:

– program

nieprzesuwalny

, absolutny (absolute file or segment) -

bezwzgl

ę

dne adresy rozkazów ustalane na etapie pisania programu,

np.

start procesora

,

wektory przerwa

ń

, fizyczne obszary pami

ę

ci,

bankowanie pami

ę

ci

– program

przesuwalny

,

relokowalny (relocatable file or segment) -

kod programu nie zale

ż

y od miejsca zajmowanego w pami

ę

ci i mo

ż

e

by

ć

przemieszczany bez dodatkowych przeadresowa

ń

, np.

kompilatory j

ę

zyków wysokiego poziomu, programy biblioteczne

ARM Compiler v5.04 for µVision armasm User Guide. Keil Software - ARM, 2014

sposób składowania danych w pami

ę

ci tak, by mogły by

ć

efektywnie

wykorzystane

procesory ARM maj

ą

bajtowy (8-bitowy), pół-słowowy (16-bitowy) i

słowowy (32-bitowy) dost

ę

p do danych w pami

ę

ci

1)

kompilator procesorów ARM rozmieszcza dane w pami

ę

ci wg. zasady:

2)

Uporządkowanie danych

(Data alignment)

typ

liczba

rozmieszczenie w pami

ę

ci

bajtów

char

1

od dowolnego adresu

short

2

od adresu podzielnego przez 2 bez reszty

float, int, long

4

od adresu podzielnego przez 4 bez reszty

long long, double

8

od adresu podzielnego przez 8 bez reszty

1)

Big and Little Endian Byte Addressing. App Note 61

.

ARM,

DAI 0061A, p.4

2)

ARM

®

Compiler toolchain. Using the Compiler. Version 4.1.

ARM DUI 0472C, p.6-43

ARM - efektywne programowanie w C

Struktury danych w pamięci

(Little-Endian Memory System)

struct {

char

a;

int

b

;

char

c

;

short d

;

}

b

23 .. 16

wolne

d

7 .. 0

b

31 .. 24

wolne

d

15 .. 8

b

15 .. 8

wolne

wolne

b

7 .. 0

a

c

+0

+1

+2

+3

+0

+4

+8

Adres

uporz

ą

dkowanie zmiennych w pami

ę

ci

struct {

char

a;

char

c

;

short d

;

int

b

;

}

b

23 .. 16

d

7 .. 0

b

31 .. 24

d

15 .. 8

b

15 .. 8

b

7 .. 0

a

c

+0

+1

+2

+3

+0

+4

Adres

uporz

ą

dkowanie zmiennych w pami

ę

ci

efektywne wykorzystanie pami

ę

ci

A. Sloss, D. Symes, C. Wright: ARM System Developer’s

Guide. Desining and Optimizing System Software.

Morgan Kaufmann, 2004

Problemy i pytania

1.

Co to jest ALU ?

2.

Do czego słu

żą

rejestry robocze procesora ?

3.

Wyja

ś

ni

ć

ró

ż

nice mi

ę

dzy poj

ę

ciami: ‘register bank’ i ‘register file’.

4.

Jak

ą

rol

ę

w procesorze pełni akumulator ?

5.

Po co w mikroprocesorze rejestr statusowy ?

6.

Jakie informacje zawieraj

ą

rejestry statusowe mikroprocesorów ?

7.

Czym si

ę

ró

ż

ni

ą

tryby: ‘microprocessor mode’ i ‘microcontroller mode’ ?

8.

Co mo

ż

e by

ć

ź

ródłem zerowania (Reset) mikroprocesora/mikrokontrolera ?

9.

Co to jest alokacja programu ?

10. Jakie s

ą

typy alokacji programów ? Poda

ć

przykłady.

11. Na czym polega architektura von-Neumanna ?

12. Na czym polega architektura Harvard ?

13. Poda

ć

wady i zalety architrktury von-Neumanna i Harvard.

14. Na czym polega zmodyfikowana architektura Harvard ?

15. Wyja

ś

ni

ć

poj

ę

cia ‘Memory Mapped I/O’ i ‘Isolated I/O’.

Wyszukiwarka

Podobne podstrony:

5 Architektura MCU 2015 www (1)

opis ZAGOSPODAROWANIE, PRAKTYKI - dokumentacja, Wiewióra&Golczyk Architekci 2015, amfiteatr, AMFITEA

9 Liczniki 2015 www

10 Serial Interface 2015 www

13 Power 2015 www

opis TECHNICZNY, PRAKTYKI - dokumentacja, Wiewióra&Golczyk Architekci 2015, amfiteatr, AMFITEATR OPI

4 Typy instrukcji Tryby adresowania 2015 www (1)

3 Przetw danych Typy proces 2015 www (1)

7 Stos 2015 www

12 DMA 2015 www

Lokalny program rewitalizacji osiedla „Stara Kolonia” w Brzeszczach 2005 2015 www old brzeszcze pl

6 Pamieci ROM RAM 2015 www

11 Przetworniki 2015 www

8 Przerwania 2015 www

opis ZAGOSPODAROWANIE, PRAKTYKI - dokumentacja, Wiewióra&Golczyk Architekci 2015, amfiteatr, AMFITEA

9 Liczniki 2015 www

10 Serial Interface 2015 www

więcej podobnych podstron