1

Podstawy techniki

mikroprocesorowej

ETEW006

Stos

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

Odwrotna Notacja Polska

Reverse Polish Notation

[1#2]

wprowadzona

w latach 1950 przez Burksa, Warrena i Wright / Hamblina na

cze

ść

polskiego matematyka Jana Łukasiewicza

, jako zapis wyra

ż

e

ń

arytmetycznych, w którym

znak

wykonywanej

operacji

umieszczony

po

operandach

(zapis postfiksowy), a nie pomi

ę

dzy nimi (konwencjonalny zapis

algebraiczny – zapis infiksowy) lub przed operandami (zwykła notacja polska

– zapis prefiksowy)

jednoznacznie okre

ś

la

kolejno

ść

wykonywanych działa

ń

: ”

3 + 4

”

→

”

3 4 +

”

zapis całkowicie

rezygnuje

z u

ż

ycia

nawiasów w wyra

ż

eniach

automatyczny stos

pozwala na proste przechowywania po

ś

rednich wyników

do wykorzystania w pó

ź

niejszych obliczeniach

stos zawiera list

ę

oczekuj

ą

cych warto

ś

ci/argumentów

http://pl.wikipedia.org/wiki/Odwrotna_notacja_polska

http://en.wikipedia.org/wiki/Reverse_Polish_notation

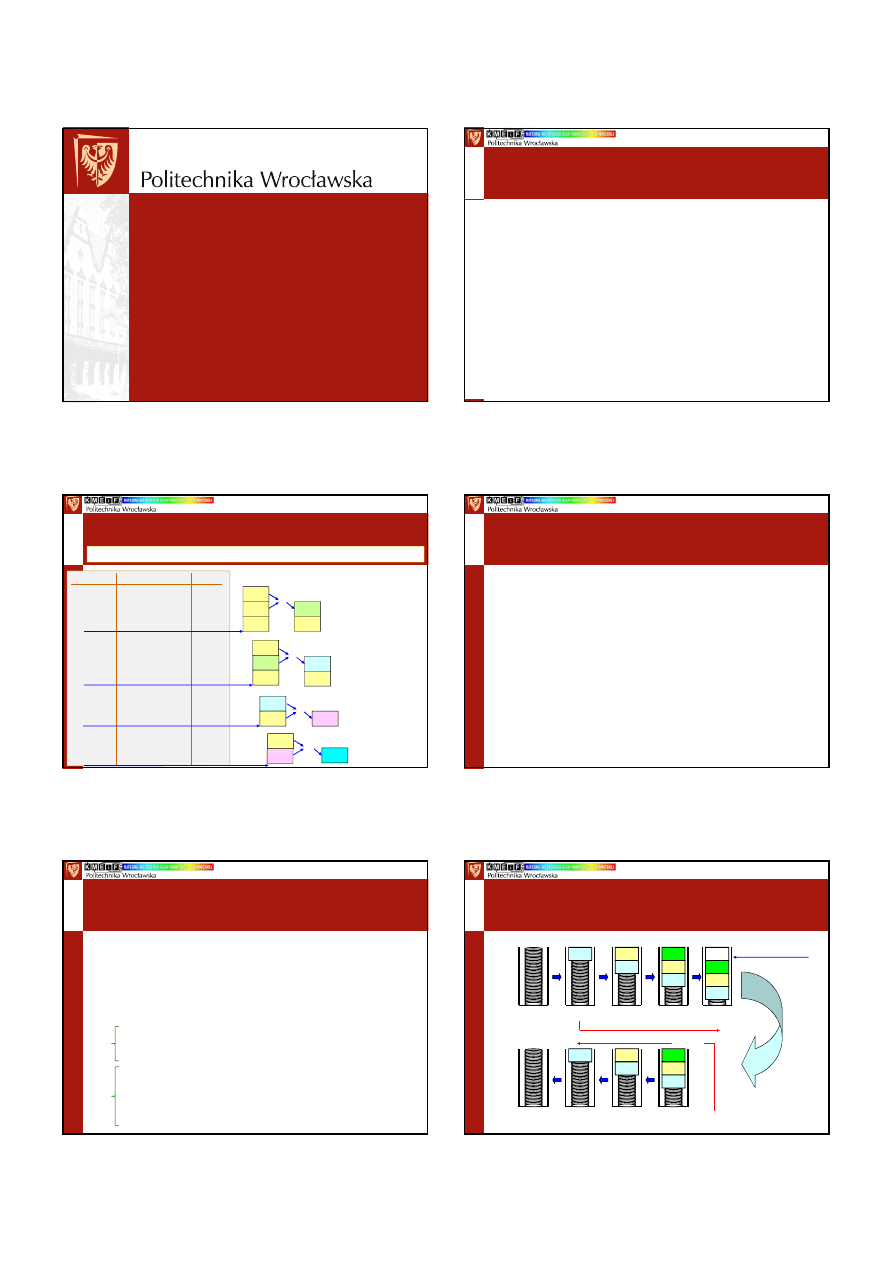

parametr

operacja

stos

5

na stos

5

1

na stos

5, 1

2

na stos

5, 1, 2

+

dodawanie

5,

3

4

na stos

5, 3, 4

∗

mno

ż

enie

5,

12

+

dodawanie

17

3

na stos

17, 3

̶

odejmowanie

14

Odwrotna Notacja Polska

[2#2]

wyra

ż

enie "

5 + ((1 + 2)

∗∗∗∗

4) − 3

" zapisane w

RPN

jako:

5 1 2 + 4

∗∗∗∗

+ 3 −

http://pl.wikipedia.org/wiki/Odwrotna_notacja_polska

http://en.wikipedia.org/wiki/Reverse_Polish_notation

3

5

+

stos

12

5

∗

17

+

14

̶

1

2

5

3

5

4

12

5

17

3

Jak rozwiązać problem ?

Je

ś

li w j

ę

zyku wysokiego poziomu (ALGOL/FORTRAN,

rok 1950) zwi

ę

kszy

ć

efektywno

ść

i wydajno

ść

przez

wprowadzenie podprogramów, to jak:

• przenie

ść

zmienne z programu głównego do tego

podprogramu ?

• zapami

ę

ta

ć

adres powrotu z podprogramu ?

• zapami

ę

tywa

ć

warto

ś

ci chwilowe oblicze

ń

?

• upro

ś

ci

ć

obliczenia, np. typu X = (A + B)

∗

(C + D) ?

Po co komu stos ?

Rozwi

ą

zanie

wprowadzi

ć

stos

(Stack), liniow

ą

struktur

ę

danych traktowan

ą

jako

rejestr

typu

LIFO

(Last In First Out) lub

wydzielony obszar

pami

ę

ci RAM

wprowadzi

ć

instrukcje procesora typu:

– PUSH arg

, odesłanie argumentu na stos

– POP arg

, pobranie argumentu ze stosu

– CALL addr

,

wywołanie podprogramu – odesłanie na stos

adresu powrotu z podprogramu

– RET

,

powrót z podprogramu – pobranie ze stosu adresu

powrotu, adresu dalszej cz

ęś

ci programu głównego

Stos (Stack)

12

34

12

PUSH 12 PUSH 34

56

34

PUSH 56

12

78

56

PUSH 78

34

12

12

34

12

POP 12

POP 34

56

34

POP 56

12

POP 78

TOS

(Top Of Stack -

szczyt stosu )

PUSH

POP

Fig. 1.1 – An

example of

stack operation

z

g

ra

w

it

a

c

j

ą

,

b

e

z

p

ra

w

m

e

c

h

a

n

ik

i

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

LIFO

2

Komputery stosowe

(Stack Computers)

Stos

jest prost

ą

, intuicyjn

ą

struktur

ą

(

Stacks are simple, a child intuitively

understands a stack of things and how it works

)

Stos

jest struktur

ą

, tablic

ą

, obszarem danych o dost

ę

pie typu

LIFO

(

L

ast

I

n

F

irst

O

ut buffer).

Komputer stosowy

to maszyna posiadaj

ą

ca cz

ęść

:

–

sprz

ę

tow

ą

:

→

wska

ź

nik stosu

(

SP – stack pointer

) adresuj

ą

cy wydzielony obszar

pami

ę

ci RAM (stos)

→

zestaw wewn

ę

trznych rejestrów

(

on-chip registers

) pełni

ą

cych rol

ę

całego lub cz

ęś

ci stosu (pozostała cz

ęść

stosu w pami

ę

ci RAM)

–

programow

ą

– instrukcje

w celu łatwej komunikacji ze stosem

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

Operacje na stosie

MCU wykorzystuje wieloelementowe instrukcje

zapisu/odczytu (

load-store multiple instructions

)

do wykonywania operacji na stosie:

operacja

PUSH

(

placing data onoto the stack

) do zapisu danych na stosie

operacja

POP

(lub

PULL

) (

removing data from a stack

) do odczytu

danych ze stosu

przepełnienie stosu

(

stack overflow

) wyst

ę

puje, je

ś

li w trakcie operacji

PUSH

wska

ź

nik stosu (

stack pointer

) zwi

ę

kszany (

increment

) lub

zmniejszany (

decrement

) przekracza zadeklarowany rozmiar stosu

niedomiar stosu

(

underflow occurs

) – je

ś

li w trakcie operacji

POP

wska

ź

nik stosu (

stack pointer

) zmniejszany (

decrement

) lub zwi

ę

kszany

(

increment

) doprowadza do odczytu danych z poza zadeklarowanego

obszaru stosu

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

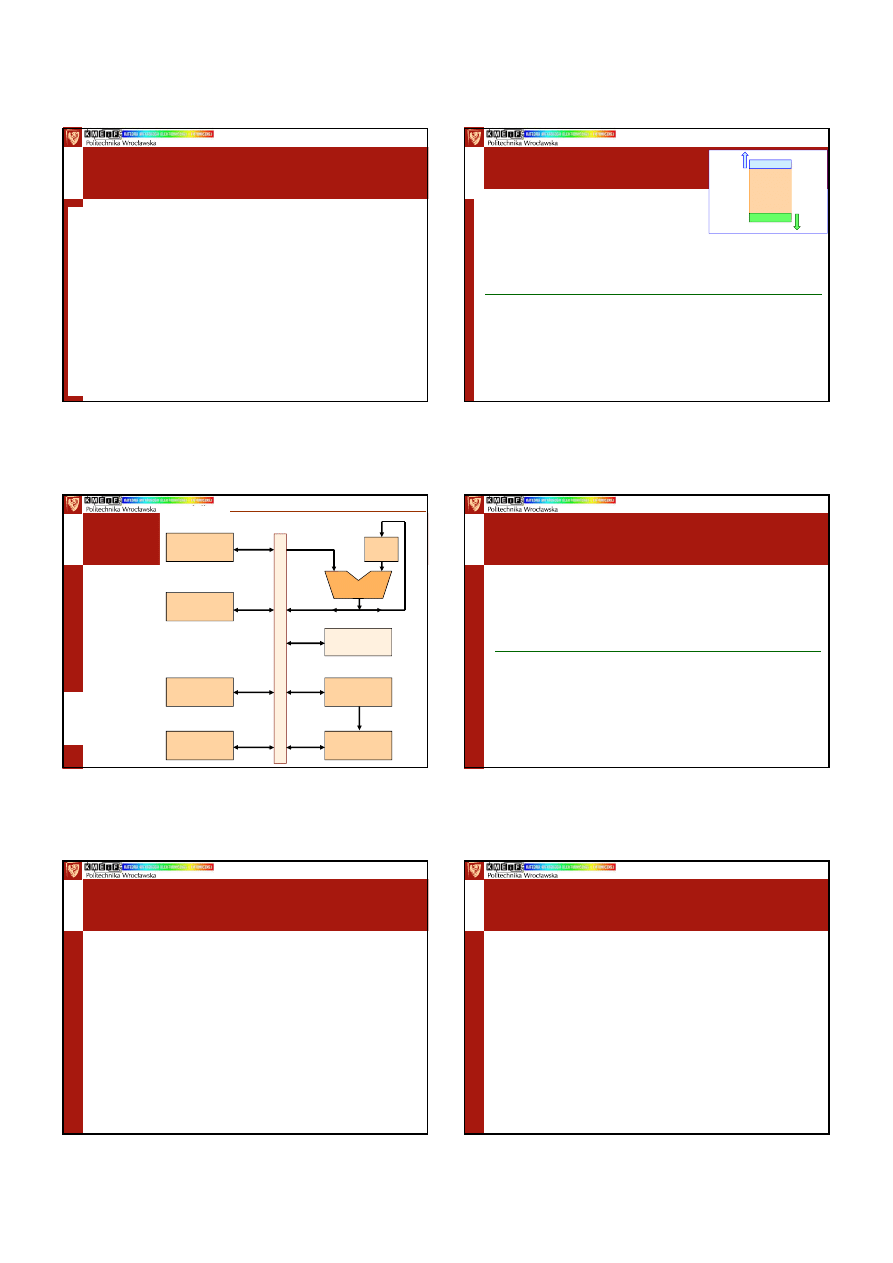

Stos

(stack)

pocz

ą

tek

koniec

PUSH

POP

Stack

Machine

DS

Data Stack

Program

Counter

Data

Address

ALU

RS

Return Stack

TOS

Program

Memory

Control

Logic & IR

I/O

Memory

Address

Register

Data

D

A

T

A

B

u

s

push & pop

operations

(LIFO)

store subroutine

return address

Fig. 3.1 – The

Canonical

Stack

Machine

ALU: addition, subtraction,

logical (AND, OR, XOR) and

test for zero

T

o

p

-O

f-

S

ta

c

k

re

g

is

te

r

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

Typy stosu

sprz

ę

towy

:

- stos zło

ż

ony z

N

dodatkowych, równoległych

rejestrów

lub rejestrów

przesuwnych typu LIFO

- szybkie

(w stosunku do realizacji programowej) odwołania do stosu

mały rozmiar stosu

(w stosunku do realizacji programowej)

programowy

:

- adresowanie

dodatkowym rejestrem,

wska

ź

nikiem stosu SP

(Stack Pointer)

- automatyczna inkrementacja

/

dekrementacja

wska

ź

nika stosu SP

przy ka

ż

dorazowym odwołaniu do stosu

- alokacja stosu w pami

ę

ci RAM

, specjalnej lub ogólnej

- rozmiar stosu ograniczony rozmiarem dost

ę

pnej pami

ę

ci RAM

Pojedynczy stos

pojedynczy stos

standardowo obsługiwany przez procesor –

dedykowany zestaw instrukcji (PUSH, POP, CALL, RET itp.)

przeznaczenie pojedynczego stosu

– przechowywanie stanu

procesora przy wywoływaniu funkcji i obsłudze przerwa

ń

oraz

przechowywanie wyników cz

ą

stkowych oblicze

ń

; zwykle

wykorzystywane przez kompilator

zaleta pojedynczego stosu

– łatwiejsze zarz

ą

dzanie pami

ę

ci

ą

, jeden

obszar pami

ę

ci przeznaczony na stos

wada pojedynczego stosu

– wzajemne zagnie

ż

d

ż

enie parametrów

wej

ś

ciowych i wyj

ś

ciowych podprogramów oraz adresów powrotów z

podprogramów i obsługi przerwa

ń

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

Wielokrotny stos

wielokrotny stos

kontrola przepływu danych i sterowania:

−

jeden stos (jeden obszar pami

ę

ci RAM) do pami

ę

tania adresów

powrotów z podprogramów i obsługi przerwa

ń

(sterowanie)

−

inne stosy (inne obszary pami

ę

ci RAM) do przenoszenia parametrów

do/z funkcji (dane)

w

komputerach stosowych

mo

ż

liwo

ść

automatycznego dost

ę

pu do

parametrów wej

ś

ciowych i wyj

ś

ciowych funkcji – przetwarzanie

równoległe

dwa stosy w j

ę

zyku Forth:

jeden do przenoszenia parametrów, drugi do

przechowywania adresów powrotów z podprogramów

P. J. Koopman, Jr.: Stack Computers the new wave.

Originally published by Ellis Horwood in 1989

3

Cortex-A Registers

User

System

Super-

visor

Abort

Unde-

fined

Interrupt

Fast

Interrupt

Privileged Modes

Exception Modes

R14_fiq

R13_fiq

R12_fiq

R11_fiq

R10_fiq

R9_fiq

R8_fiq

R14_irq

R13_irq

R14_und

R13_und

R14_abt

R13_abt

R14_svc

R13_svc

SPSR_svc SPSR_abt SPSR_und SPSR_irq SPSR _fiq

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

(Stack Pointer)

R14

(Link Register)

u

n

b

a

n

k

e

d

re

g

is

te

rs

b

a

n

k

e

d

re

g

is

te

rs

PC

(Program Counter)

CPSR

(Current Program Status Register)

Saved Program

Status Register

ARM

state

Thumb

state

Cortex™-A8. Technical Reference Manual.

Revision: r3p2. ARM, DDI 0344K, fig. 2-10

Secure

monitor

R14_mon

R13_mon

SPSR_mon

The basis of the

Security

Extensions model

is that the

computing environment

splits

into

two

isolated

states, the

Secure state

and

the

Nonsecure state

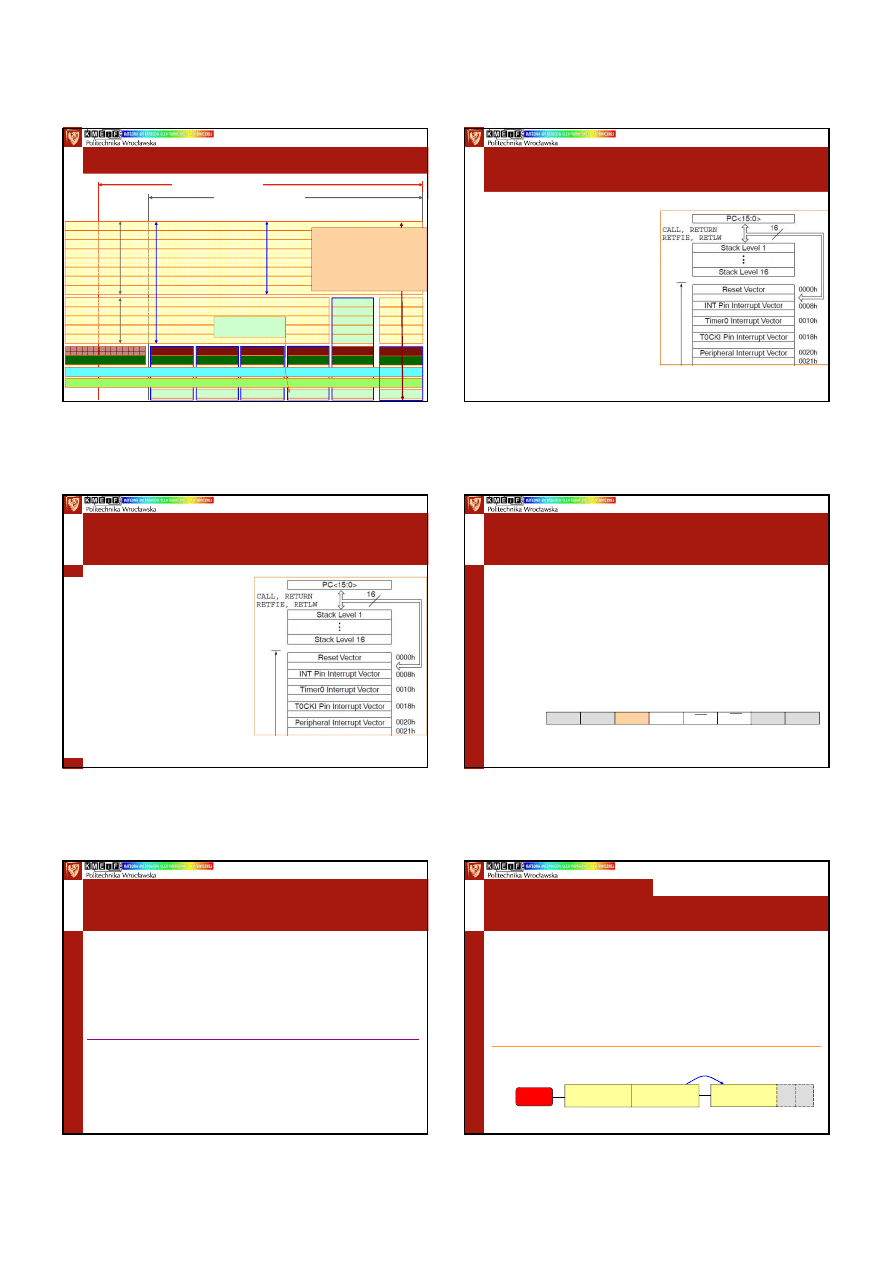

Hardware Stack

PIC17C4x

(Microchip Technology) [1#2]

PIC17C4X. High-Performance 8-Bit CMOS EPROM/ROM

Microcontroller. Microchip Technology, 1996, DS30412C

FIGURE 6-1:PROGRAM MEMORY

MAP AND STACK

stos

nie jest cz

ęś

ci

ą

programu i nie jest

cz

ęś

ci

ą

pami

ę

ci danych (zestaw

wewn

ę

trznych rejestrów)

brak

mo

ż

liwo

ś

ci wpisu i odczytu

zawarto

ś

ci warto

ś

ci do/ze wska

ź

nika stosu

stan licznika programu (PC) zapisywany

na stosie, gdy jest wykonywana instrukcja

CALL

lub jest przyjmowane przerwanie

instrukcje

RETURN

(Return from subroutine)

,

RETLW

(Return literal to WREG [Working

Register])

lub

RETFIE

(Return from interrupt

and enable interrupts)

pobieraj

ą

zawarto

ść

ze

stosu

U

s

e

r

M

e

m

o

ry

S

p

a

c

e

szesna

ś

cie, 16-bitowych rejestrów tworzy

stos sprz

ę

towy

Hardware Stack

PIC17C4x

(Microchip Technology) [2#2]

stos

jest buforem

kołowym/pier

ś

cieniowym (

circular

buffer

)

warto

ść

pocz

ą

tkowa wska

ź

nika

stosu po dowolnym zerowaniu

wynosi

'0‚

po

16-krotnym

wykonaniu

operacji

PUSH

(bez operacji POP), 17-ta

operacja PUSH

nadpisuje

warto

ść

pierwszej

operacji

PUSH

18-ta operacja PUSH

nadpisuje

warto

ść

drugiej

operacji

PUSH

itd.

U

s

e

r

M

e

m

o

ry

S

p

a

c

e

PIC17C4X. High-Performance 8-Bit CMOS EPROM/ROM

Microcontroller. Microchip Technology, 1996, DS30412C

FIGURE 6-1:PROGRAM MEMORY

MAP AND STACK

Hardware Stack

STKAV bit

bit STKAV

(

stack available

) do kontroli przepełnienia stosu

bit STKAV = 1

ustawiany po zerowaniu procesora

bit STKAV = 0

po osi

ą

gni

ę

ciu przez wska

ź

nik stosu warto

ś

ci

0Fh

(16-ty

wpis do stosu)

bit STKAV = 0

je

ś

li wyst

ą

pi przepełnienie stosu – wska

ź

nik stosu

zmienia stan z 0Fh na 00h (stack pointer rolls over) i pozostaje w tym

stanie do zerowania procesora

STKAV = 1,

stos dost

ę

pny

STKAV = 0,

stos zapełniony

STKAV

GLINTD

TO

PD

unimpl

unimpl

unimpl

unimpl

– 0

– 0

R – 1 R/W – 1 R – 1

R – 1

– 0

– 0

CPUSTA

REGISTER

PIC17C4X. High-Performance 8-Bit CMOS EPROM/ROM

Microcontroller. Microchip Technology, 1996, DS30412C

Rozpoczęcie programu

Cortex

–

M0 / Cortex-M0+

[1#3]

Plik: startup_LPC11xx.s

www.Keil.com

27

; <h> Stack Configuration

28

; <o> Stack Size (in Bytes) <0x0-0xFFFFFFFF:8>

29

; </h>

30

31

Stack_Size

EQU

0x00000200

32

33

AREA

STACK

,

NOINIT

,

READWRITE

,

ALIGN

=

3

34

Stack_Mem

SPACE

Stack_Size

35

__initial_sp

54

; Vector Table Mapped to Address 0 at Reset

55

56

AREA

RESET, DATA,

READONLY

57

EXPORT

__Vectors

58

59

__Vectors

DCD

__initial_sp

; Top of Stack

60

DCD

Reset_Handler

; Reset Handler

61

.................................................................................

Rozpoczęcie programu

Cortex

–

M0 / Cortex-M0+

[2#3]

J. Yiu: The Definitive Guide to the ARM Cortex-M0.

Elsevier Inc. 2011, p.39

J. Yiu: The Definitive Guide to the ARM Cortex-M3.

Second Edition. Elsevier Inc. 2010, p.40

po

zako

ń

czeniu stanu reset

procesor odczytuje dwa słowa:

─

pierwsze o adresie

0x0000 0000

: warto

ść

pocz

ą

tkowa wska

ź

nika stosu

R13 = MSP

─

drugie o adresie

0x0000 0004

: rozpocz

ę

cie wykonywania kodu programu

u

ż

ytkownika (Reset vector); LSB = 1 oznacza tryb Thumb

to

zasadnicza ró

ż

nica

, poniewa

ż

standardowo, inne procesory od adresu

0x0000 0000 rozpoczynaj

ą

wykonywanie kodu programu

Address=

0x0000 0004

Address=

0x0000 0000

Reset

inicjalizacja

wska

ź

nika stosu

MSP

adres pocz

ą

tku

kodu programu

Address=

Reset vector

pocz

ą

tek kodu

programu

4

Rozpoczęcie programu

Cortex

–

M0 / Cortex-M0+

[3#3]

Plik: *.map

www.Keil.com

Plik 3_Klawisz_LED_SysTick.map

:

Image Symbol Table

Local Symbols

Symbol Name Value

Ov Type Size

Object(Section)

RESET

0x00000000

Section

192

startup_lpc11xx.o(RESET)

...........................................................................................................................

HEAP

0x10000088

Section

0

startup_lpc11xx.o(HEAP)

STACK

0x10000088 Section

512

startup_lpc11xx.o(STACK)

Heap_Mem

0x10000088

Data

0

startup_lpc11xx.o(HEAP)

Stack_Mem

0x10000088 Data

512

startup_lpc11xx.o(STACK)

__initial_sp

0x10000288 Data

0

startup_lpc11xx.o(STACK)

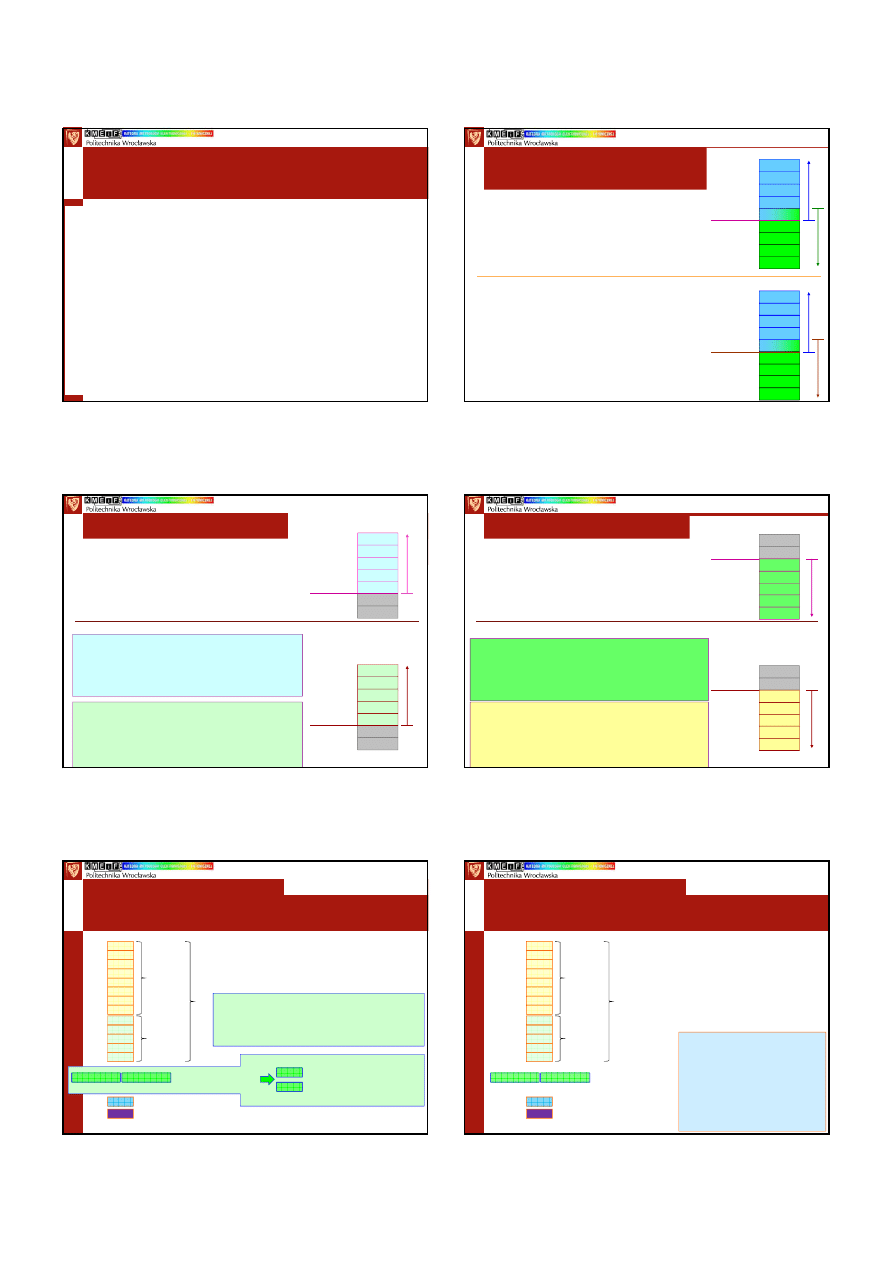

Organizacja

stosu programowego

Stos

narasta w

gór

ę

lub w

dół

;

stos

:

−

narastaj

ą

cy

(

A

– ascending) – narastaj

ą

ce

adresy pami

ę

ci RAM traktowanej jako stos

−

malej

ą

cy

(

D

– descending) – malej

ą

ce adresy

pami

ę

ci RAM traktowanej jako stos

Wska

ź

nik stosu

(Stack pointer – SP) wskazuje:

−

pełny stos

(

F

– full stack), wska

ź

nik stosu SP

wskazuje adres ostatniej zaj

ę

tej lub pełnej

komórki pami

ę

ci RAM

−

pusty stos

(

E

– empty stack), wska

ź

nik stosu

SP wskazuje adres pierwszej wolnej lub

pustej komórki pami

ę

ci RAM

SP = addr

addr+1

addr+2

addr+3

addr+4

addr–1

addr–2

addr–3

addr–4

last

next

next + 1

next + 2

next + 3

next

next + 1

next + 2

next + 3

SP = addr

addr+1

addr+2

addr+3

addr+4

addr–1

addr–2

addr–3

addr–4

last

next

next + 1

next + 2

last

next

next + 1

RAM

RAM

ARM Architecture. Reference Manual.

ARM DDI 0100I, July 2005, p.A5-47

nex + 2

Organizacja typu: FA /

EA

SP = addr

addr+1

addr+2

addr+3

addr+4

addr–1

addr–2

last

next

next + 1

next + 2

next + 3

SP = addr

addr+1

addr+2

addr+3

addr+4

addr–1

addr–2

last

next

next + 1

nex + 2

RAM

RAM

Stos o narastaj

ą

cych adresach

lub malej

ą

cych

adresach

:

−

narastaj

ą

ce

(

A

scending)

adresy wska

ź

nika

stosu

(SP)

przy zapisie do stosu

−

malej

ą

ce (Descending) adresy wska

ź

nika stosu

(SP) przy zapisie do stosu

Wska

ź

nik stosu

(SP)

wskazuje na

:

−

pełny stos

(

F

ull stack), wska

ź

nik stosu (SP)

wskazuje na ostatni

ą

zaj

ę

t

ą

komórk

ę

pami

ę

ci

stosu; kolejno

ść

operacji PUSH:

1.

wpis zmiennej na stos

2.

inkrementacja wska

ź

nika stosu

(SP)

−

pusty stos

(

E

mpty stack), wska

ź

nik stosu

(SP) wskazuje na pierwsz

ą

woln

ą

komórk

ę

pami

ę

ci stosu; kolejno

ść

operacji PUSH:

1. inkrementacja wska

ź

nika stosu

(SP)

2. wpis zmiennej na stos

FA

EA

Organizacja typu: FD /

ED

SP = addr

addr+1

addr–1

addr–2

addr–3

addr–4

next

next + 1

next + 2

next + 3

SP = addr

addr+1

addr+2

addr–1

addr–2

addr–3

addr–4

last

next

next + 1

next + 2

addr+2

last

RAM

RAM

Stos o

narastaj

ą

cych adresach

lub malej

ą

cych

adresach

:

−

narastaj

ą

ce (Ascending) adresy wska

ź

nika stosu (SP)

przy zapisie do stosu

−

malej

ą

ce

(

D

escending)

adresy wska

ź

nika

stosu

(SP)

przy zapisie do stosu

Wska

ź

nik stosu

(SP)

wskazuje na

:

−

pełny stos

(

F

ull stack), wska

ź

nik stosu (SP)

wskazuje na ostatni

ą

zaj

ę

t

ą

komórk

ę

pami

ę

ci

stosu; kolejno

ść

operacji PUSH:

1.

wpis zmiennej na stos

2.

dekrementacja wska

ź

nika stosu

(SP)

−

pusty stos

(

E

mpty stack), wska

ź

nik stosu (SP)

wskazuje na pierwsz

ą

woln

ą

komórk

ę

pami

ę

ci

stosu; kolejno

ść

operacji PUSH:

1.

dekrementacja wska

ź

nika stosu

(SP)

2.

wpis zmiennej na stos

FD

ED

Cortex

–

M

Rejestry wskaźnika stosu

(Stack Pointer)

MSP

PSP

Main Stack Register

(SP_main po Reset)

Process Stack Register

(SP_process)

Link Register (LR)

Program Counter (PC)

Stack Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R14

PC

2 najmniej znacz

ą

ce bity wska

ź

nika stosu

(MSP lub PSP) s

ą

zawsze równe 0, co

oznacza,

ż

e s

ą

zawsze wyrównane do

słowa (

word aligned

)

R13 (PSP)

R13 (MSP)

rejestry ogólnego przeznaczenia rdzenia

(General Purpose ARM Core Register)

rejestry

(Low

Register)

rejestry

(High

Register)

Cortex

–

M

Rejestr powiązań

(Link Register)

Link Register (LR)

Program Counter (PC)

Stack

Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R14

PC

R13 (PSP)

R13 (MSP)

rejestry ogólnego przeznaczenia rdzenia

(General Purpose ARM Core Register)

rejestry

(Low

Register)

rejestry

(High

Register)

Link Register

(R14 = LR)

przechowuje adres powrotu z

podprogramu, obsługi

wyj

ą

tku/przerwania

(exception/interrupt)

nieokre

ś

lona warto

ść

po

zerowaniu procesora (reset)

5

Cortex

–

M0

(ARMv6M)

Operation Modes

J. Yiu: The Definitive Guide to the ARM Cortex-M0.

Elsevier Inc. 2011, Fig. 3.1

Thread Mode

Executing normal

code

Thumb State

Exception

request

Exception

return

Handler Mode

Executing exception

handler

Debug State

(The processor stop

executing instruction)

Debug

activities

The

Cortex-M0

processor

has two operation modes

and two states

Start

(

Reset

)

An

ARMv6-M implementation only supports

privileged operation

[DDI0419C, A2.1.1]

In

Handler mode

, the processor uses the

Main Stack Pointer

(MSP).

In

Thread mode

it can use

Main Stack Pointer

or

Process Stack Pointer

(PSP).

Cortex

–

M3

(ARMv7M)

Operation Modes

J. Yiu: The Definitive Guide to the ARM Cortex-M3.

Second Edition. Elsevier Inc. 2010, Fig. 2.4, 2.5

Privileged

Thread

Thumb/Thumb-2 State

Exception

request

Exception

exit

Start

(

Reset

)

Privileged

Handler

User

Thread

Exception

request

When

running an exception

handler

When

not running an exception

handler (e.g., main program)

Privileged

User

Handler

mode

Thread

mode

Thread mode

Program of CONTROL

register

Cortex

–

M0+

(ARMv6M)

Operation Modes

[1#2]

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010, p.A1-27

An

ARMv6-M implementation only supports

privileged operation

[DDI0419C, A2.1.1]

In

Handler mode

, the processor uses the

Main Stack Pointer

(MSP).

In

Thread mode

it can use

Main Stack Pointer

or

Process Stack Pointer

(PSP).

In ARMv7-M, software can run either at privileged or unprivileged level

.

In systems implemented with the ARMv6-M base architecture, all

software runs at privileged level.

By

adding

the

Unprivileged/Privileged Extension

,

ARMv6-M

systems can

use the same privilege levels as ARMv7-M

while still having the benefit of

very low gate count.

In addition, with the same privilege levels as ARMv7-M,

ARMv6-M systems

can use the optional MPU

(Memory Protection Unit) that the PMSA

(Protected Memory System Architecture) Extension provides.

Cortex

–

M0+

(ARMv6M)

Operation Modes

[2#2]

PM0223. STM32L0 Series Cortex

®

-M0+ programming manual.

STMicroelectronics , DocID025763 Rev 1 , April 2014, p.13

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010, p.A1-27

Table 2. Summary of processor mode, execution privilege level, and stack

use options

Processor Used to execute

Privilege level for

Stack used

mode

software execution

Thread

Applications

Privileged

Main stack

or

unprivileged

or

process stack

Handler

Exception handlers

Always

privileged

Main stack

Table 9. Control register bit assignments

Bits

Name

Function

[31:2]

Reserved.

[1]

SPSEL

Defines the current stack:

0 = MSP is the current stack pointer

.

1 = PSP is the current stack pointer

.

In Handler mode this bit reads as zero and ignores writes.

[0]

nPRIV

Defines the Thread mode privilege level:

0 = Privileged

.

1 = Unprivileged

AAPCS

ARM7/9

1)

www.keil.com

2)

Procedure Call Standard for the ARM

®

Architecture.

ARM, IHI 0042E, 30th November 2012

__irq void IRQ_Timer0 (void)

1)

{

// STMDB

R13!, {R0-R1}

………………………………………

}

// LDMIA

R13!, {R0-R1}

// SUBS

PC, R14, #4

AAPCS

(

Procedure Call Standard for the ARM Architecture

) – relacje mi

ę

dzy

procedur

ą

wywołuj

ą

ca i wywoływan

ą

2)

:

zasady wywoływania podprogramu, u

ż

ycia rejestrów

zasady wykorzystania rejestrów przez procedur

ę

wywoływan

ą

zasady ingerencji procedury wywoływanej w stan procedury wywołuj

ą

cej

Przeznaczenie rejstrow

:

R1 .. R0 – argumenty / wyniki / robocze

R3 .. R2 – argumenty / robocze

R8 .. R4 – argumenty

MSP430

PUSH — wpis na stos

PUSH[.W]

Wpisz słowo na stos

PUSH.B

Wpisz bajt na stos

Syntax

PUSH

dst

lub

PUSH.W dst

PUSH.B dst

Operation

SP – 2

→

SP

dst

→

@SP

Przykład

MOV.W #0x0280, SP

; np. SP = 0280h po Init

PUSH

R9

; SP = 0280h – 2 = 027Eh

; R9

→

@SP

PUSH

#1234h

; SP = 027Eh – 2 = 027Ch

; #1234h

→

@SP

MSP430FR57xx Family User's Guide.

TI SLAU272B, May 2011–Revised January 2013, p.169

po inicjalizacji:

SP

INIT

= End_of_RAM + 1

= 0280h

R9

?

1234h

SP = 027Eh

SP = 027Ch

Stos

6

MSP430

POP — odczyt ze stosu

POP[.W]*

Odczytaj słowo ze stosu

POP.B*

Odczytaj bajt ze stosu

Syntax

POP

dst

←

←

←

←

*

MOV

@SP+, dst

instrukcja emulowana

lub

POP.W dst

←

←

←

←

*

MOV.W @SP+, dst

instrukcja emulowana

POP.B dst

←

←

←

←

*

MOV.B @SP+, dst

instrukcja emulowana

Operation

@SP

→

temp

SP + 2

→

SP

temp

→

dst

MSP430FR57xx Family User's Guide.

TI SLAU272B, May 2011, Revised January 2013, p.168

PUSH

&

POP

Cortex

–

M0 / Cortex-M0+

(ARMv6M)

PM0223. STM32L0 Series Cortex

®

-M0+ programming manual.

STMicroelectronics, DocID025763 Rev 1, 2014, p.52

Cortex™-M0 Revision: r0p0. Technical Reference Manual.

ARM DDI 0432C, p.3-6

Full-Descending stack

:

Operation Description

Assembler

Cycles

PUSH

Push

PUSH {<loreglist>}

1+N

Push with link register PUSH {<loreglist>, LR}

1+N

POP

Pop

POP

{<loreglist>}

1+N

Pop and return

POP

{<loreglist>, PC}

3+N

<loreglist> must use only R0-R7

instructions do not change the flags

Examples:

PUSH {R0 – R2}

; (SP

─

4)

←

R2

; (SP

─

8)

←

R1

; (SP

─

12)

←

R0

Branch (CALL)

Cortex

–

M0 / Cortex-M0+

(ARMv6M)

PM0223. STM32L0 Series Cortex

®

-M0+ programming manual.

STMicroelectronics, DocID025763 Rev 1, 2014, p.66

Cortex™-M0 Revision: r0p0. Technical Reference Manual.`

ARM DDI 0432C, p.3-6

Operation

Description

Assembler

Cycles

Branch

Branch with Link

BL

label

4

Branch indirect with Link

BLX Rm

3

POP

Pop and return

POP {<loreglist>, PC}

3+N

Examples:

BL

funC

; Branch with link (Call) to function funC,

; return address stored in LR

BLX

R0

; Branch with link and exchange (Call)

; to a address stored in R0

Cortex-M

Składowanie

(Stacking)

Cortex™-M0 Devices. Generic User Guide.

ARM DUI 0497A, p.2-24

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14 (LR)

R15 (PC)

R0

R1

R2

R3

R12

R14 (LR)

R15 (PC)

xPSR

stacking

PRIMASK

FAULTMASK

BASEPRI

CONTROL

APSR

IPSR

EPSR

wpis do rejestru IPSR

(Interrupt Program Status

Register)

numeru

wyj

ą

tku/przerwania

(exception/interrupt

number)

wpis do licznika rozkazów

(PC)

adresu procedury

obsługi wyj

ą

tku/przerwania

(exception/interrupt vector

handler) i pobranie pierwszej

instrukcji tej procedury

aktualizacja warto

ś

ci rejestru

LR

do warto

ś

ci zwanej

EXC_RETURN

MSP

(Main Stack Pointer)

or

PSP

(Process Stack Pointer)

warto

ść

wska

ź

nika

stosu

(SP)

przed

przyj

ę

ciem

wyj

ą

tku/przerwania

<poprzedni>

Application

+ Execution

+ Interrupt

Program Status

Register

[8]

[1]

[2]

[7]

[6]

[5]

[4]

[3]

warto

ść

wska

ź

nika

stosu

(SP)

po

przyj

ę

ciu

wyj

ą

tku/przerwania

Problemy i pytania

1. Jakie jest przeznaczenie stosu ?

2. Gdzie s

ą

pami

ę

tane argumenty w komputerze stosowym ?

3. Jaka jest kolejno

ść

wykonywanych operacji w odwrotnej notacji polskiej ?

4. Jaka jest logiczna organizacja stosu ?

5. Co oznaczaj

ą

skróty FA i EA dotycz

ą

ce organizacji stosu ?

6. Co oznaczaj

ą

skróty FD i ED dotycz

ą

ce organizacji stosu ?

7. Jakie s

ą

zalety i wady pojedynczego stosu ?

8. Jakie s

ą

zalety i wady wielokrotnego stosu ?

9. Czym si

ę

ró

ż

ni stos sprz

ę

towy od programowego ?

10. Jakie jest przeznaczenie instrukcji PUSH i POP ?

11. Jakie jest przeznaczenie instrukcji CALL i RET ?

12. W jaki sposób jest adresowany i obsługiwany stos sprz

ę

towy ?

13. W jaki sposób jest adresowany i obsługiwany stos programowy ?

14. Jakie jest przeznaczenie rejestru SP ?

15. Jak rozszyfrowa

ć

poj

ę

cie TOS przy dost

ę

pie do stosu ?

16. Na czym polega inicjalizacja stosu ?

Wyszukiwarka

Podobne podstrony:

9 Liczniki 2015 www

10 Serial Interface 2015 www

13 Power 2015 www

4 Typy instrukcji Tryby adresowania 2015 www (1)

3 Przetw danych Typy proces 2015 www (1)

12 DMA 2015 www

Lokalny program rewitalizacji osiedla „Stara Kolonia” w Brzeszczach 2005 2015 www old brzeszcze pl

6 Pamieci ROM RAM 2015 www

11 Przetworniki 2015 www

2 Architektura 2015 www

8 Przerwania 2015 www

5 Architektura MCU 2015 www (1)

9 Liczniki 2015 www

10 Serial Interface 2015 www

11 Przetworniki 2015 www

Sprawozdanie 2015 www

więcej podobnych podstron