1. Układ przewidujący skoki określany jako (2,3) wykorzystuje:

a) 2 bity określające globalne zachowanie w celu wyboru dla wykonywanej instrukcji skoku jednego z 4-rech

układów przewidujących skoki;

b) 3 bity określające globalne zachowanie w celu wyboru dla wykonywanej instrukcji skoku jednego z 4-

rech układów przewidujących skoki;

c) 3 bity określające globalne zachowanie w celu wyboru dla wykonywanej instrukcji skoku jednego z 8-śmiu

układów przewidujących skoki;

d) Brak poprawnej odpowiedzi.

2. Czym różnią się sieci statyczne od dynamicznych?

a) Nie różnią się niczym;

b) W sieciach statycznych połączenia są stałe, a w dynamicznych mogą być zmieniane w zależności od

potrzeb;

c) W sieciach dynamicznych połączenia są stałe, a w statycznych mogą być zmieniane w zależności od

potrzeb;

d) Brak poprawnej odpowiedzi.

3. Dlaczego w przypadku skoków realizujących powrót z procedury nie stosuje się algorytmów przewidywania

skoków?

a) Pytanie błędne, wtedy też się stosuje;

b) Ponieważ praktycznie za każdym razem "przewidywanie" byłoby niepoprawne;

c) Ponieważ byłby problem z zagnieżdżonymi procedurami;

d) Brak poprawnej odpowiedzi.

4. Do czego służy bufor adresów docelowych skoków?

a) W buforze adresów docelowych skoków zapamiętywane są prognozy, tzn. informacje czy skok będzie

wykonany, czy nie;

b) W buforze adresów docelowych skoków zapamiętywane są przewidywane adresy instrukcji, które będą

wykonane po instrukcji skoku;

c) W buforze adresów docelowych skoków zapamiętana jest historia realizacji skoków;

d) Brak poprawnej odpowiedzi.

5. Co oznacza, że pamięć cache jest asocjacyjna? (ZAŁOŻENIA W NAWIASACH)

a) Każdy blok ma jedno, wyróżnione miejsce, które może zajmować w pamięci cache;

b) Każdy blok może zajmować miejsce spośród wyróżnionej puli miejsc w pamięci cache; (SET

ASSOCIATIVE)

c) Bloki pamięci mogą zajmować dowolne miejsce w pamięci cache; (FULLY ASSOCIATIVE)

d) Brak poprawnej odpowiedzi.

6. Jak wyliczamy średni czas dostępu do pamięci gdy wykorzystujemy pamięć cache?

a) hit time + miss rate * miss penalty;

b) hit time * miss rate * miss penalty;

c) Nie definiujemy takiego czasu;

d) Brak poprawnej odpowiedzi;

7. Prawo Amdahla mówi, że:

a) Przyspieszenie jest ograniczone przez równoległą część programu;

b) Nie ma ograniczenia na przyspieszenie;

c) Przyspieszenie rośnie liniowo wraz ze wzrostem liczby procesorów;

d) Brak poprawnej odpowiedzi.

8. Przyspieszenie definiuje się jako stosunek czasu potrzebnego na rozwiązanie problemu na jednym

procesorze (T sek), do czasu rozwiązania tego samego problemu na "p" procesorach (T row). Kiedy mówimy,

że przyspieszenie jest względne?

a) Kiedy T sek jest czasem wykonania algorytmu równoległego na jednym z procesorów komputera

równoległego;

b) Kiedy T sek jest czasem wykonania najlepszego algorytmu sekwencyjnego na jednym z procesorów

komputera równoległego;

c) Kiedy T sek jest czasem wykonania najlepszego algorytmu sekwencyjnego na najszybszym komputerze

sekwencyjnym;

d) Brak poprawnej.

9. Konflikt dostępu do danych w przetwarzaniu potokowym polega na:

a) Kolejna wykonywana instrukcja żąda dostępu do rejestru wykorzystywanego przez poprzednią

b)

Brak poprawnej odpowiedzi

c)

Kolejna wykonywana instrukcja żąda dostępu do zajętego procesora

d)

Kolejna wykonywana instrukcja żąda dostępu do nie wyliczonej jeszcze przez poprzednią instrukcję

wartości

10. Rozważ poniższy kod:

LD R1, Dana1

ADD R1 Dana 2

SUB R1 Dana 3

ST Wynik, R1

Między instrukcjami ADD i SUb występuje zależność:

a) właściwa;

b) wyjściowa;

c) antyzależność;

d) Brak poprawnej odpowiedzi.

11. Rozważ instrukcję pętli w któej realizuje się 10 iteracji i pętla się kończy ( nie ma kolejnego przebiegu). Jaka

jest skuteczność przewidywania skoku, jeśli używamy jednobitowego ukłądu przewidywania skoków przy

inicjalizacji układu na 1?

ZAŁOŻENIE: Jeśli w pętli jesteśmy z 11 przebiegiem (w tym przebiegu zostaje zakończona pętla) to

skuteczność wynosi 90%

a) 80%

b) 95%

c) 90%

d) Brak poprawnej

12. Jedną z cech rozproszonej pamięci współdzielonej (zwanej NUMA) jest:

a) Taki sam czas dostępu dla wszystkich komórek;

b) Czas dostępu zależy od fizycznej lokalizacji i od procesora żądającego;

c) Nie da się jednoznacznie określić zależności między czasem reakcji, a lokalizacją i procesorem;

d) Brak poprawnej odpowiedzi.

13. Przy skoku opóźnionym, instrukcja znajdująca się bezpośrednio po instrukcji skoku:

a) Jest wykonywana zawsze;

b) Jest wykonywana tylko gdy skok jest realizowany;

c) Jest wykonywana tylko gdy skok nie jest realizowany;

d) Brak poprawnej.

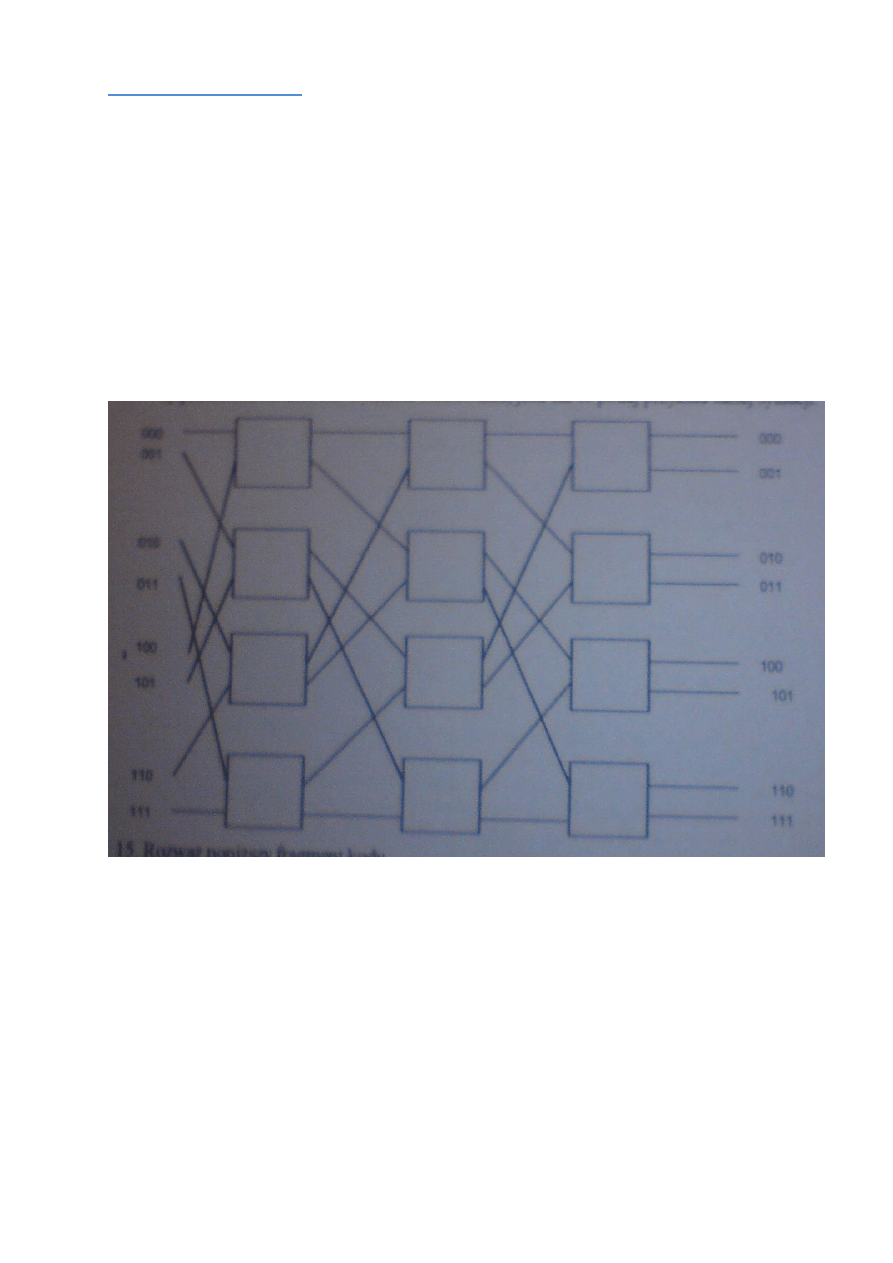

14. Na rysunku poniżej przedstawiono tzw. Omega Network dla ośmiu wejść i ośmiu wyjść. Odpowiedz na

poniższe pytania związane z tą siecią:

a) Jak wyznacza się drogę pomiędzy wejściem, a wyjściem? Algorytm zilustruj przykładem.

b) Czy ta sieć ma własność blokowania? Jeśli tak podaj przykład tej sytuacji.

15. Rozważ poniższy fragment kodu

If (d==0) d=1;

If (d==1) …….

Zbuduj tabele akcji (jak na wykładzie dla 1-bitowego układu przewidywania skoków z jednym bitem korelacji.

Zaloz ze układy przewidywania skokow dla obu skokow są zainicjalizowane na Not taken/taken oraz bit

korelacji na taken . Wartość zmiennej d zmienia się w następujący sposób 1,2,1,2. Zaznacz sytuacje gdy

przewidywanie skoku jest niepoprawne.

Wyszukiwarka

Podobne podstrony:

pierwszpomoc id 357780 Nieznany

pierwszakomunia2008 id 357704 Nieznany

01 KSIEGA PIERWSZA id 362763 Nieznany (2)

Badania pierwsze id 76624 Nieznany (2)

2377 Moje pierwsze SMD id 30349 Nieznany (2)

Pierwsza pomoc 3 id 357506 Nieznany

pierwsza pomoc 9 id 357525 Nieznany

Ethernet pierwszej mili id 1643 Nieznany

2377 Moje pierwsze SMD id 30349 Nieznany (2)

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

więcej podobnych podstron