1

Podstawy Technologii Komputerowych

Podstawy Technologii Komputerowych

dr inż. Krzysztof MURAWSKI

dr inż. Krzysztof MURAWSKI

mgr inż. Józef TURCZYN

mgr inż. Józef TURCZYN

Tel.: 6837752, E

Tel.: 6837752, E

-

-

: k.

: k.

murawski

murawski

@

@

ita

ita

.

.

wat

wat

.

.

edu

edu

.

.

pl

pl

2

Skale scalenia układów elektronicznych.

Skale scalenia układów elektronicznych.

> układy SSI, MSI, LSI, VLSI, GLSI <

> układy SSI, MSI, LSI, VLSI, GLSI <

© K. MURAWSKI, J. TURCZYN

3

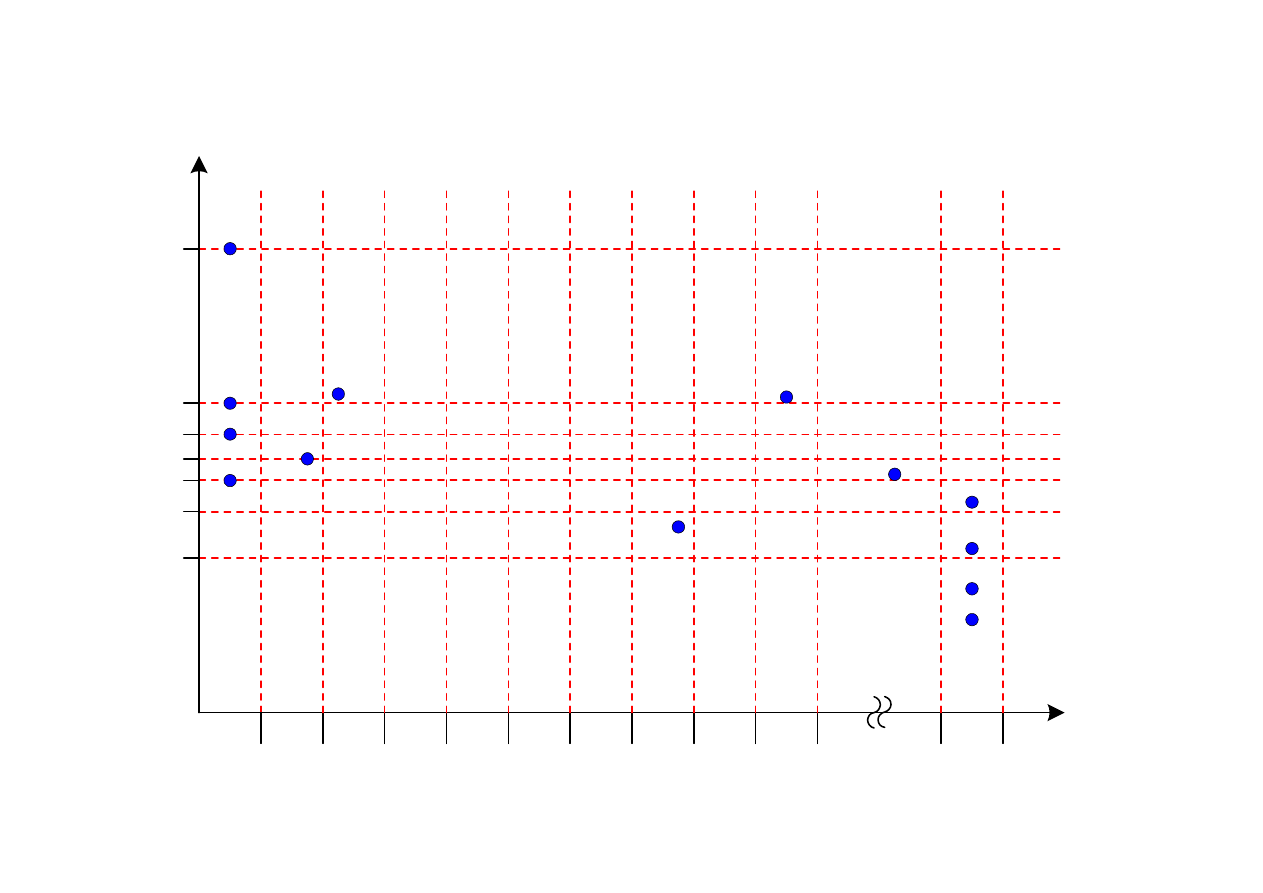

Liczba bramek w pojedynczym

Liczba bramek w pojedynczym

ukł

ukł

. scalonym

. scalonym

© K. MURAWSKI, J. TURCZYN

10

100

1000

10.000

100.000

1.000.000

SSI

MSI

LSI

VLSI

GLSI

10

100

1000

10.000

100.000

1.000.000

1960

1970

1980

1990

2000

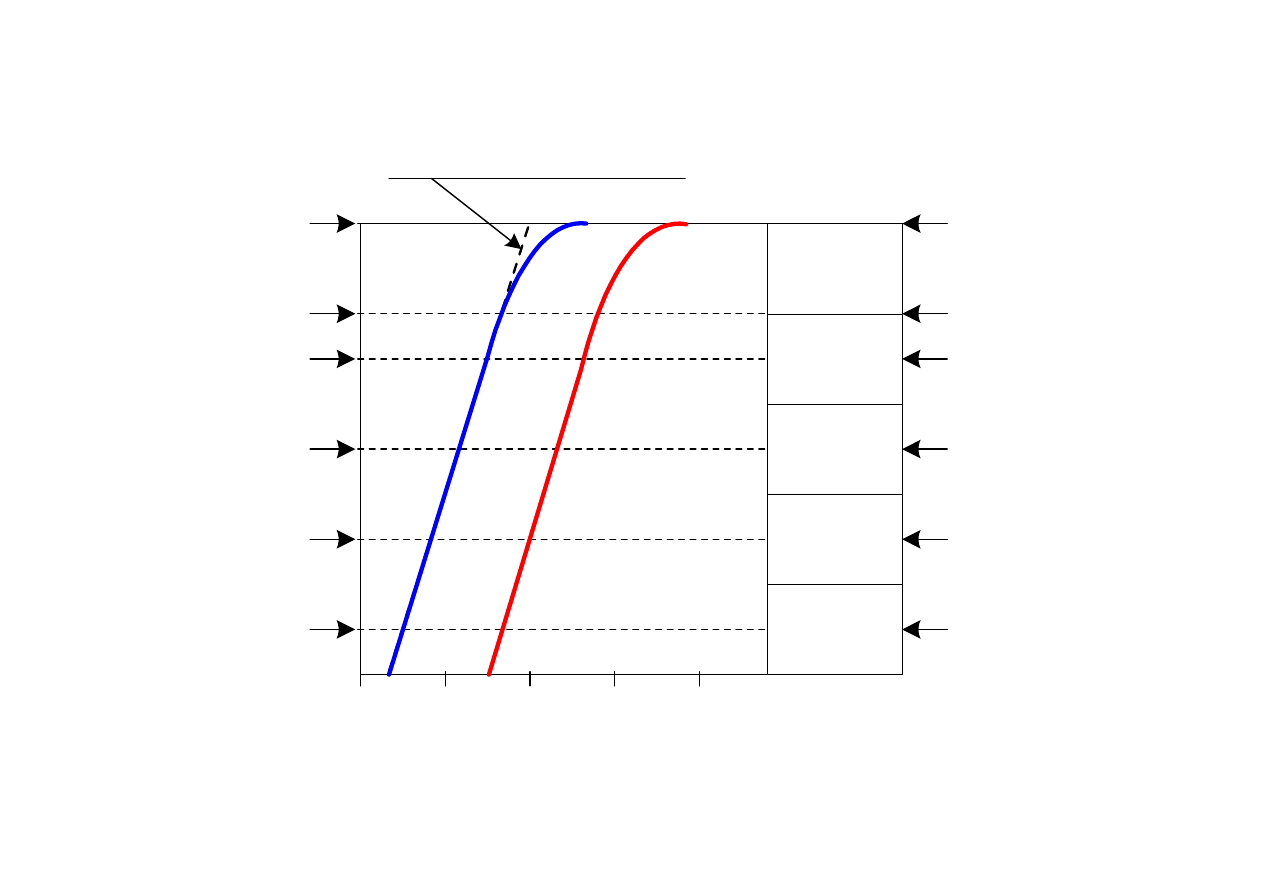

Prawo Moore'a dla krzemu

Si

GaAs

Liczba elementów w największych dla danego roku

Liczba elementów w największych dla danego roku

ukł

ukł

. scalonych podwaja się w ciągu

. scalonych podwaja się w ciągu

roku. (1975 rok).

roku. (1975 rok).

4

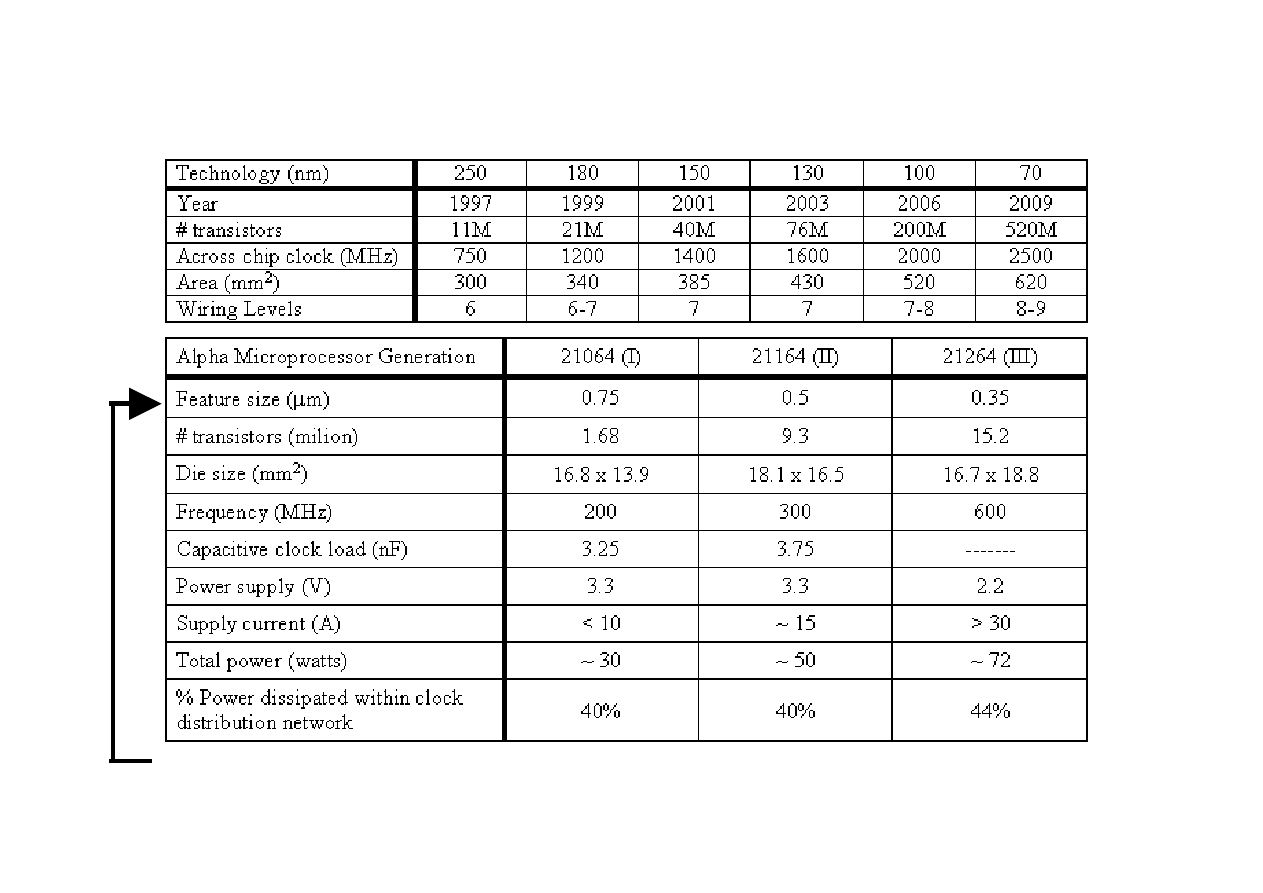

Prognozy

Prognozy

–

–

przyszłość czy przeszłość ?

przyszłość czy przeszłość ?

© K. MURAWSKI, J. TURCZYN

Transistor feature size: the minimum size of a transistor

5

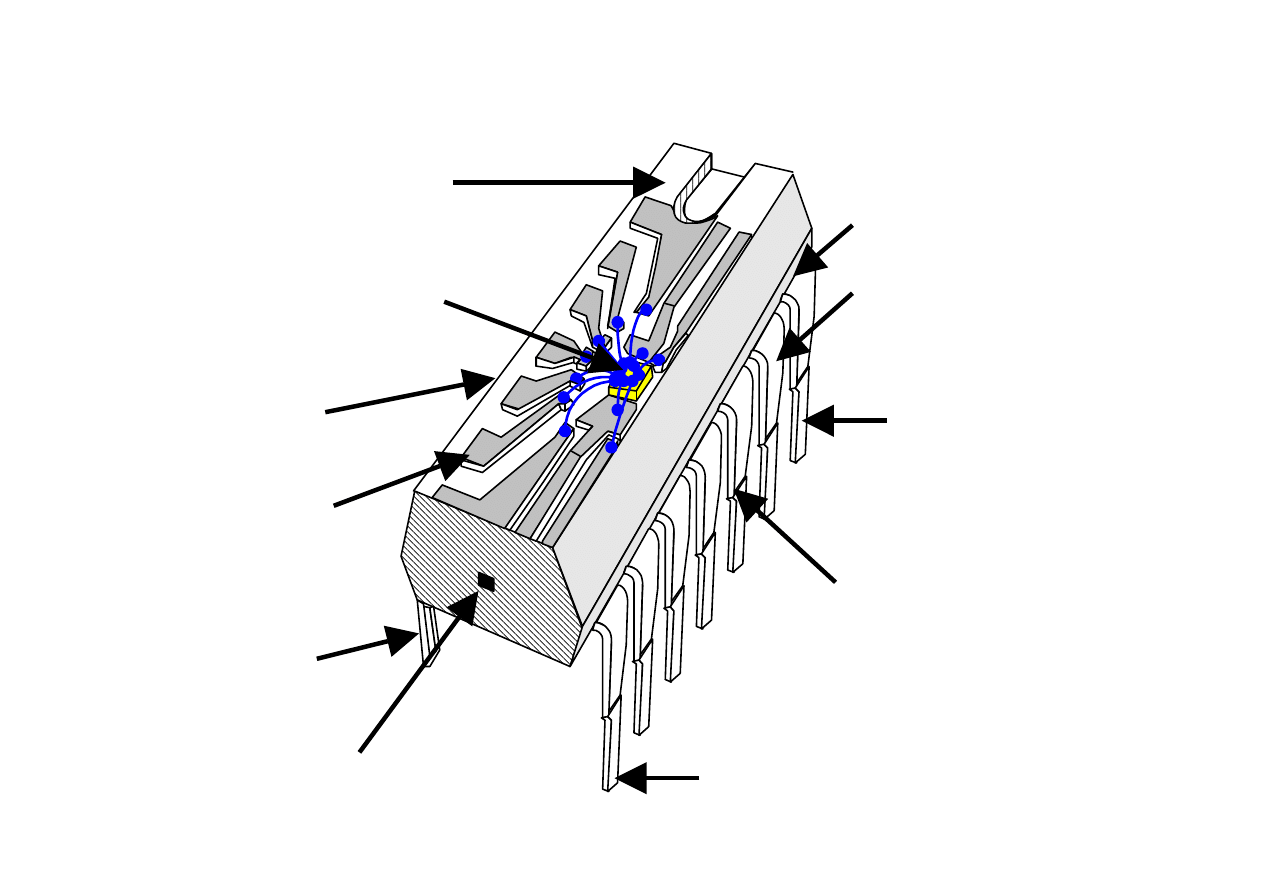

Układ scalony od środka

Układ scalony od środka

© K. MURAWSKI, J. TURCZYN

Końcówka 8

Końcówka 14

Końcówka 7

Szkielet metalowy ułatwiający

rozpraszanie ciepła.

Wyprowadzenia są silnie

związane z obudową.

Przewodność cieplna obudowy

ogranicza wzrost temperatury układu.

Położenie półprzewodnika uniemożliwia

powstawanie zwarć wewnętrznych.

Jednolita obudowa

podtrzymuje druty łączące.

Materiał obudowy ściśle

przylega do wyprowadzeń.

Wykonanie końcówek umożliwia

montaż automatyczny.

Zgrubienia końcówek utrzymują

obudowę ponad płytką montażową,

zapewniając wentylację i eliminując

wilgoć.

6

Układy scalone

Układy scalone

-

-

przykłady oznaczeń

przykłady oznaczeń

© K. MURAWSKI, J. TURCZYN

Oznaczenia układów TTL:

UCY7400

– Standard TTL – oznaczenie polskie;

SN7400

– Standard TTL – oznaczenie Texas Instr;

SN74L00

– Low Power TTL;

SN74S00

– Shotky TTL;

SN74LS00

– Low Power Shotky TTL;

SN74F00

– Fast TTL;

SN74ALS00 – Advanced LS TTL;

SN74AS00 – Advanced Shotky.

Oznaczenia układów CMOS:

B

– Buffered;

HCMOS – High CMOS;

FACT

– Fairchild Advanced CMOS Technology;

ACL

– Advanced CMOS Logic;

7

Moc rozpraszana i czasy propagacji

Moc rozpraszana i czasy propagacji

© K. MURAWSKI, J. TURCZYN

1

2

3

4

5

6

7

8

9

10

20

21

P

D

[mW]

t

P

[ns]

1

2

3

4

5

10

100

ACL

FACT

HCMOS

4000B

TTL-LS

TTL-ALS

TTL-AS

TTL

TTL-S

ECL(10k)

ECL(10kH)

ECL(100k)

ECL(ECLIPS)

8

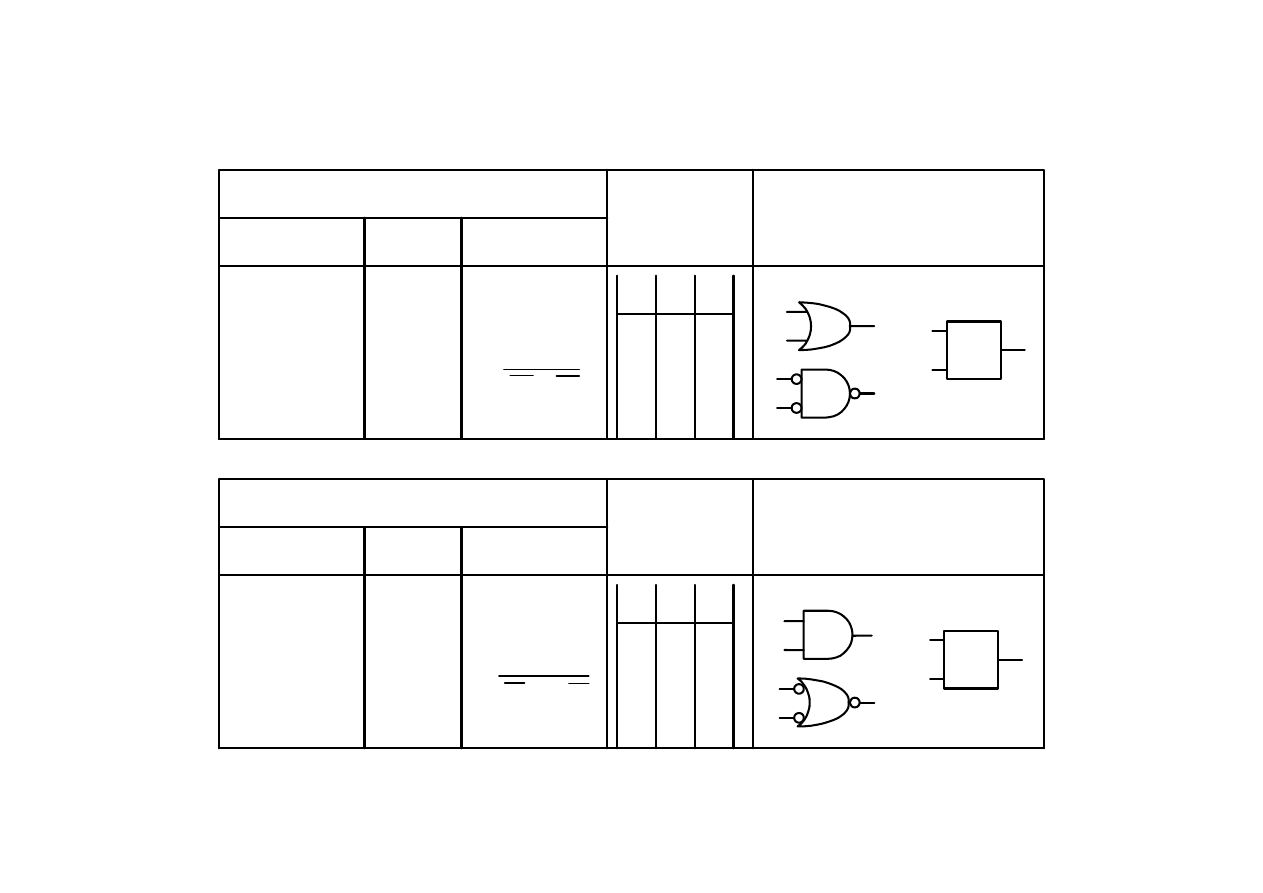

Podstawowe funktory logiczne

Podstawowe funktory logiczne

© K. MURAWSKI, J. TURCZYN

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Suma

LUB

(OR)

Y

A B

= +

A B

=

i

A

B

Y

0

0

0

1

1

0

1

1

0

1

1

1

A

B

Y

A

B

Y

A

B

Y

1

≥

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Iloczyn

I

(AND)

Y

A B

=

i

A

B

= +

A

B

Y

0

0

0

1

1

0

1

1

0

0

0

1

A

B

Y

A

B

Y

A

B

Y

&

9

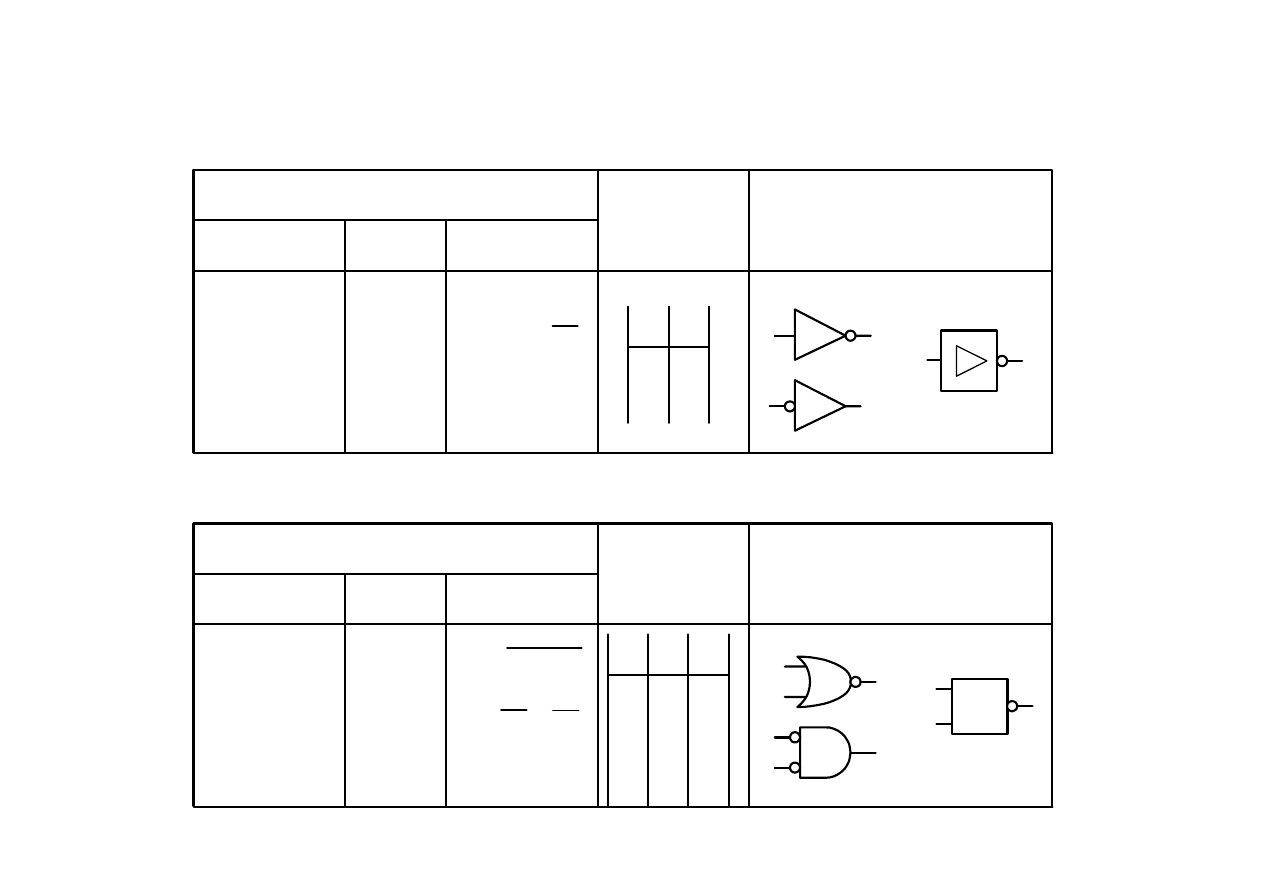

Podstawowe funktory logiczne

Podstawowe funktory logiczne

© K. MURAWSKI, J. TURCZYN

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Negacja

NIE

(NOT)

Y

A

=

A

Y

0

1

1

0

A

Y

A

Y

A

Y

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Negacja

sumy

lub-nie

(NOR)

Y

A B

= +

A B

=

i

A

B

Y

0

0

0

1

1

0

1

1

1

0

0

0

A

B

Y

A

B

Y

A

B

Y

1

≥

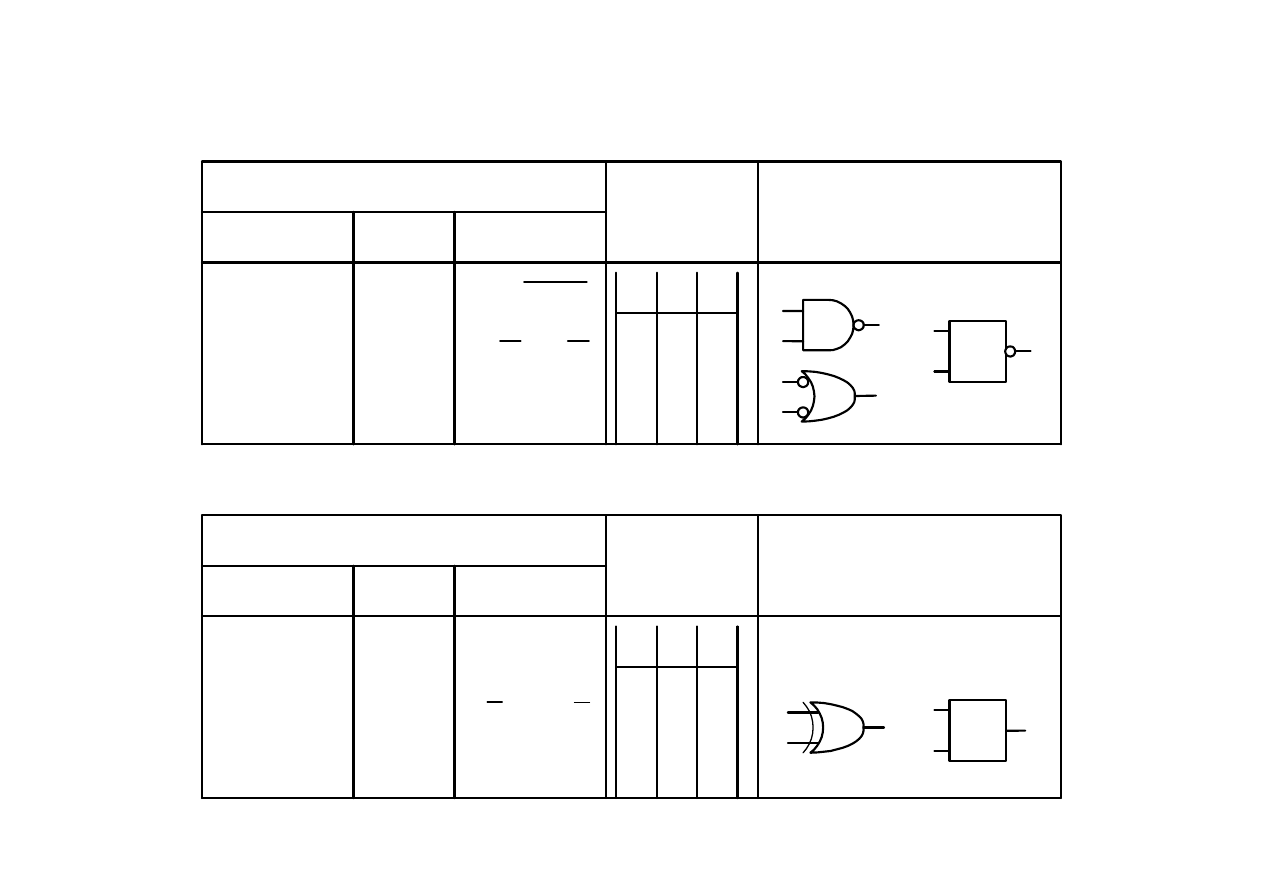

10

Podstawowe funktory logiczne

Podstawowe funktory logiczne

© K. MURAWSKI, J. TURCZYN

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Negacja

iloczynu

I-NIE

(NAND)

Y

A B

=

i

A B

= +

A

B

Y

0

0

0

1

1

0

1

1

1

1

1

0

A

B

Y

A

B

Y

A

B

Y

&

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

Suma

modulo 2

WYŁĄ

CZNIE

- LUB

(EXOR)

Y A B

= ⊕

AB AB

=

+

A

B

Y

0

0

0

1

1

0

1

1

0

1

1

0

A

B

Y

A

B

Y

1

=

11

Podstawowe funktory logiczne

Podstawowe funktory logiczne

© K. MURAWSKI, J. TURCZYN

Funkcja

Tabela

stanów

Symbole

Nazwa

Ozn.

Zapis

WYŁĄC

ZNIE -

LUB -

NIE

(EXNOR)

Y

A

B

= ⊕

AB AB

=

+

A

B

Y

0

0

0

1

1

0

1

1

1

0

0

1

Negacja

suma

modulo 2

A

B

Y

A

B

Y

1

=

12

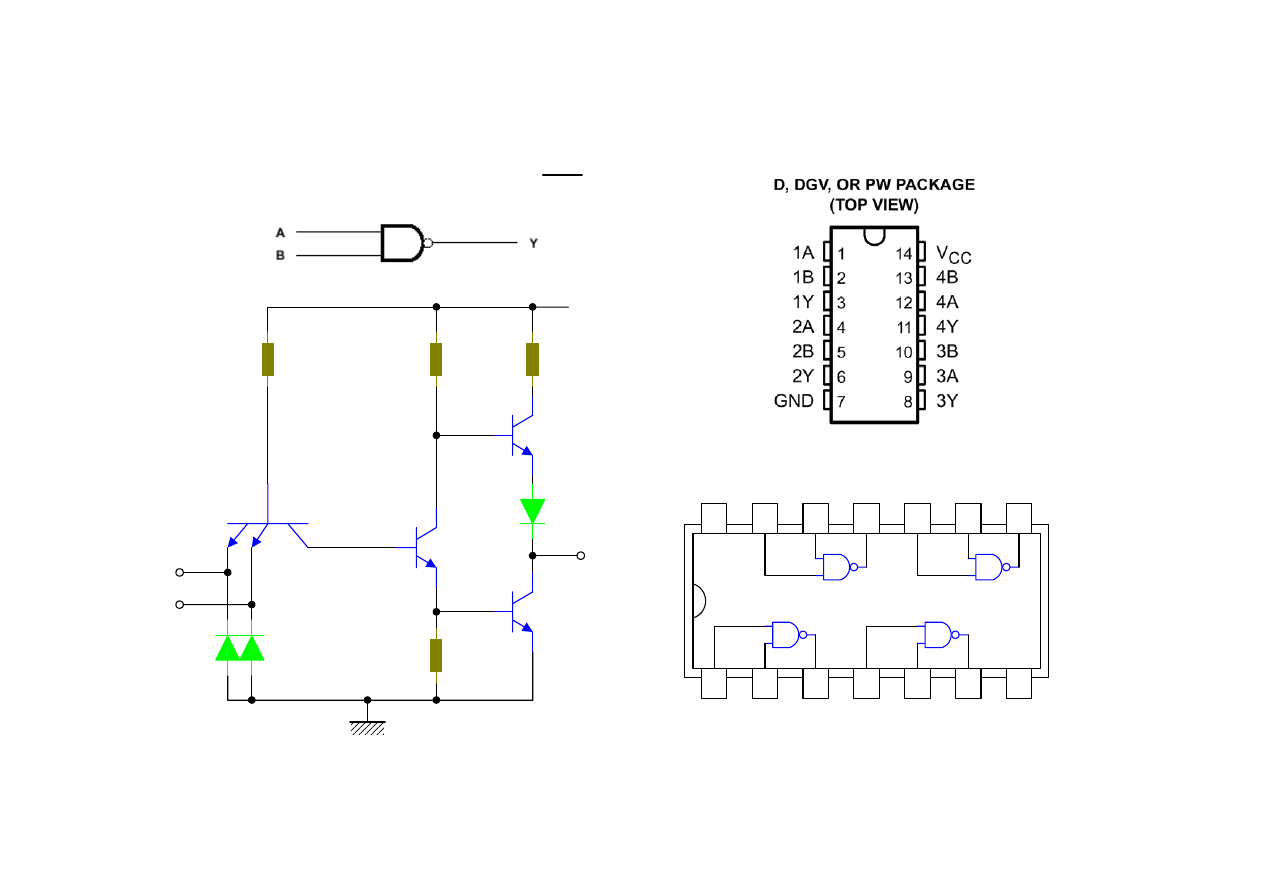

Przykłady układów scalonych

Przykłady układów scalonych

–

–

UCY7400

UCY7400

A

B

Y

T1

T2

T3

T4

D1

D3

D2

4k

Ω

1.6k

Ω

130

Ω

1k

Ω

CC

V

GND

© K. MURAWSKI, J. TURCZYN

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

3B

3A

3Y

4B

4A

4Y

V

cc

GND

Logika dodatnia:

Logika dodatnia:

Y

AB

=

13

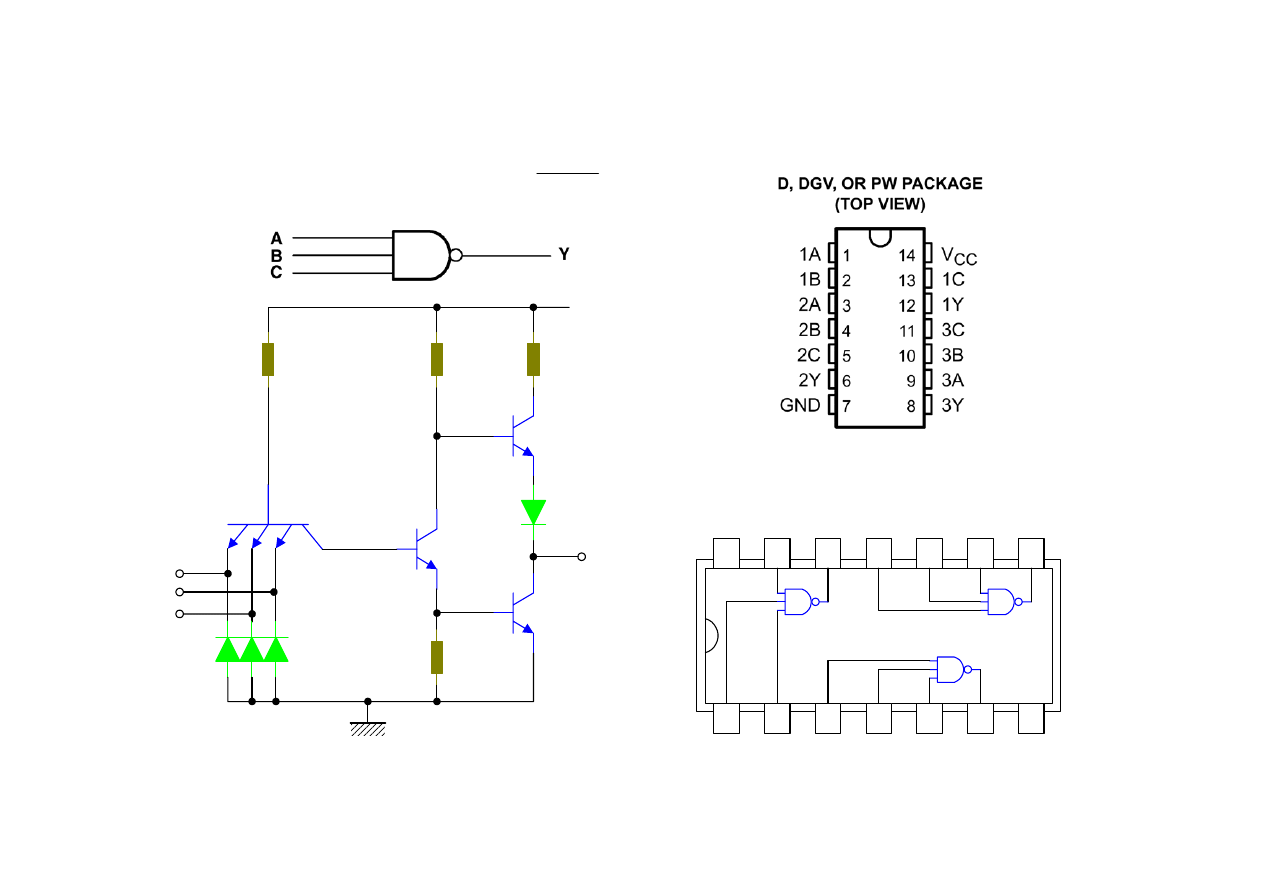

Przykłady układów scalonych

Przykłady układów scalonych

–

–

UCY7410

UCY7410

A

B

Y

T1

T2

T3

T4

D1

D3

D2

4k

Ω

1.6k

Ω

130

Ω

1k

Ω

CC

V

GND

D4

C

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

3B

3A

3Y

1C

3C

V

cc

GND

2C

© K. MURAWSKI, J. TURCZYN

Logika dodatnia:

Logika dodatnia:

Y

ABC

=

14

1

2

3

4

5

1

2

3

4

10

20

U

I

U

0

[V]

15

I

CC

[mA]

U

0

I

CC

~ 0.65V ~ 1.3V

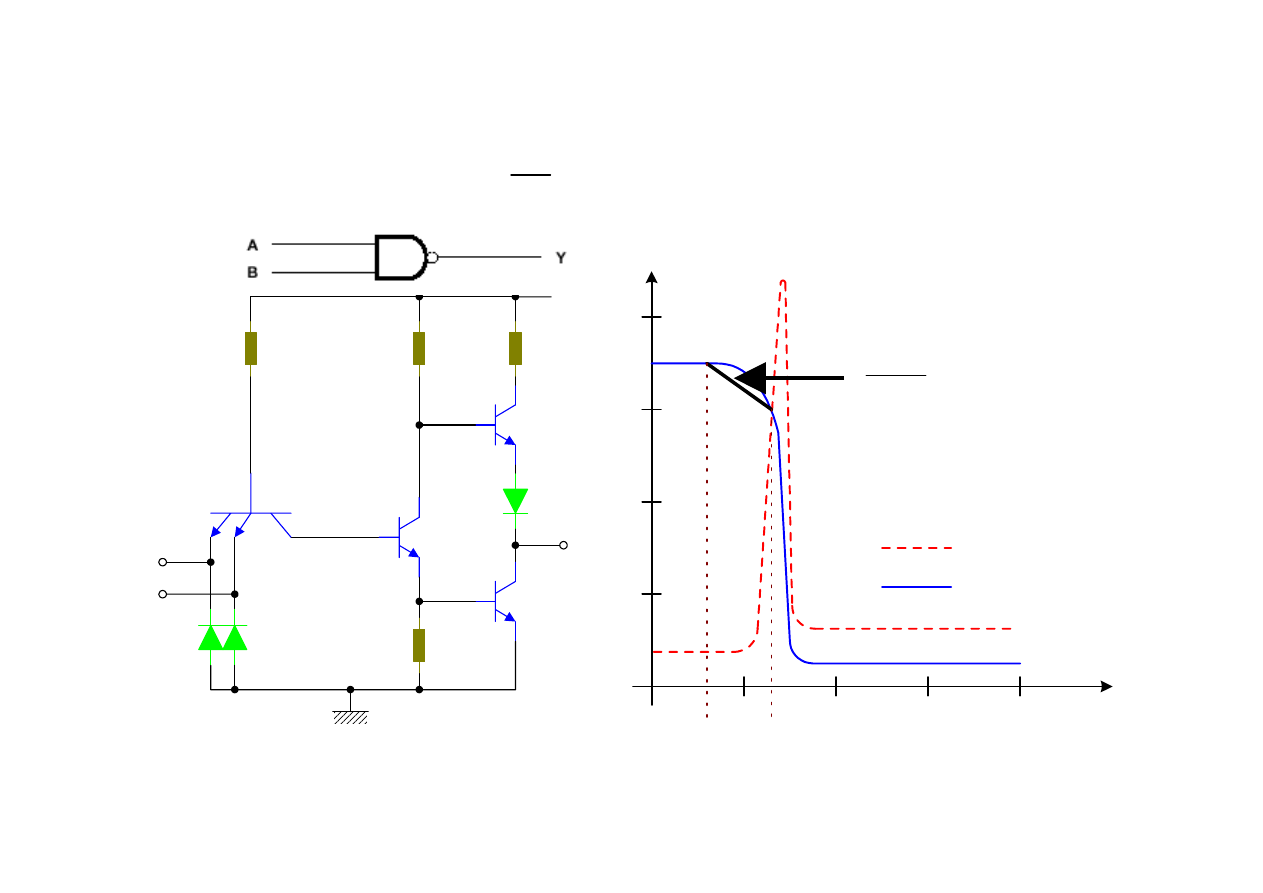

Przykłady układów scalonych

Przykłady układów scalonych

–

–

UCY7400

UCY7400

A

B

Y

T1

T2

T3

T4

D1

D3

D2

4k

Ω

1.6k

Ω

130

Ω

1k

Ω

CC

V

GND

© K. MURAWSKI, J. TURCZYN

Charakterystyka przejściowa i poboru prądu

Charakterystyka przejściowa i poboru prądu

1.6

O

I

U

U

∆

= −

∆

Logika dodatnia:

Logika dodatnia:

Y

AB

=

15

Przykłady układów scalonych

Przykłady układów scalonych

© K. MURAWSKI, J. TURCZYN

http://www.ita.wat.edu.pl/users/kmuraw/PTK/scyd013.pdf

16

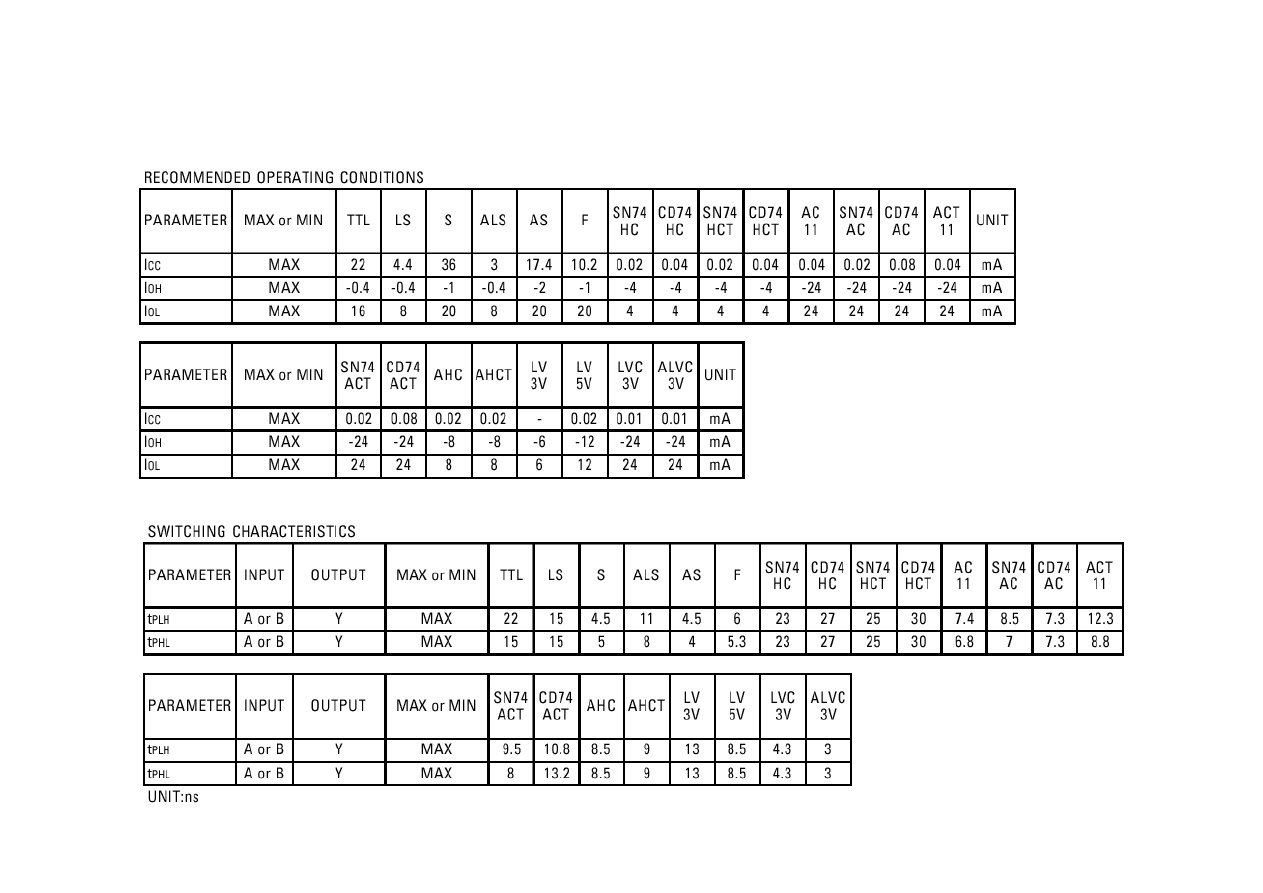

Podstawowe param. statyczne

Podstawowe param. statyczne

ukł

ukł

. cyfrowych

. cyfrowych

© K. MURAWSKI, J. TURCZYN

SN5400

SN7400

MIN NOM MAX

MIN NOM MAX

Miano

V

CC

Napięcie zasilania

4,5

5

5,5

4,75

5

5,25

[ V ]

U

IH

Napięcie wejściowe

w stanie wysokim

2

2

[ V ]

U

IL

Napięcie wejściowe

w stanie niskim

0,8

0,8

[ V ]

I

OH

Prąd wyjściowy

w stanie wysokim

-0,4

-0,4

[ mA ]

I

OL

Prąd wyjściowy

w stanie niskim

16

16

[ mA ]

T

A

Temperatura otoczenia

podczas pracy układu

-55

125

0

70

[

o

C ]

Parametry i ich rekomendowane (zalecane) wartości.

Parametry i ich rekomendowane (zalecane) wartości.

17

Podstawowe param. statyczne

Podstawowe param. statyczne

ukł

ukł

. cyfrowych

. cyfrowych

© K. MURAWSKI, J. TURCZYN

Parametry i ich rekomendowane (zalecane) wartości.

Parametry i ich rekomendowane (zalecane) wartości.

SN5400

SN7400

MIN NOM MAX MIN NOM MAX

Miano

V

IK

V

CC

= MIN, I

I

= -12mA

-1,5

-1,5

[ V ]

U

OH

V

CC

= MIN, U

IL

= 0.8V,

I

OH

= -0.4mA

2,4

3,4

2,4

3,4

[ V ]

U

OL

V

CC

= MIN, U

IH

= 2V,

I

OL

= 16mA

0,2

0,4

0,2

0,4

[ V ]

I

I

V

CC

= MAX, U

I

= 5.5V

1

1

[ mA ]

I

IH

V

CC

= MAX, U

I

= 2.4V

40

40

[

µ

A ]

I

IL

V

CC

= MAX, U

I

= 0.4V

-1,6

-1,6

[ mA ]

I

OS

V

CC

= MAX

-20

-55

-18

-55

[ mA ]

I

CCH

V

CC

= MAX, U

I

= 0.0V

4

8

4

8

[ mA ]

I

CCL

V

CC

= MAX, U

I

= 4.5V

12

22

12

22

[ mA ]

18

Podstawowe param. układów cyfrowych

Podstawowe param. układów cyfrowych

© K. MURAWSKI, J. TURCZYN

19

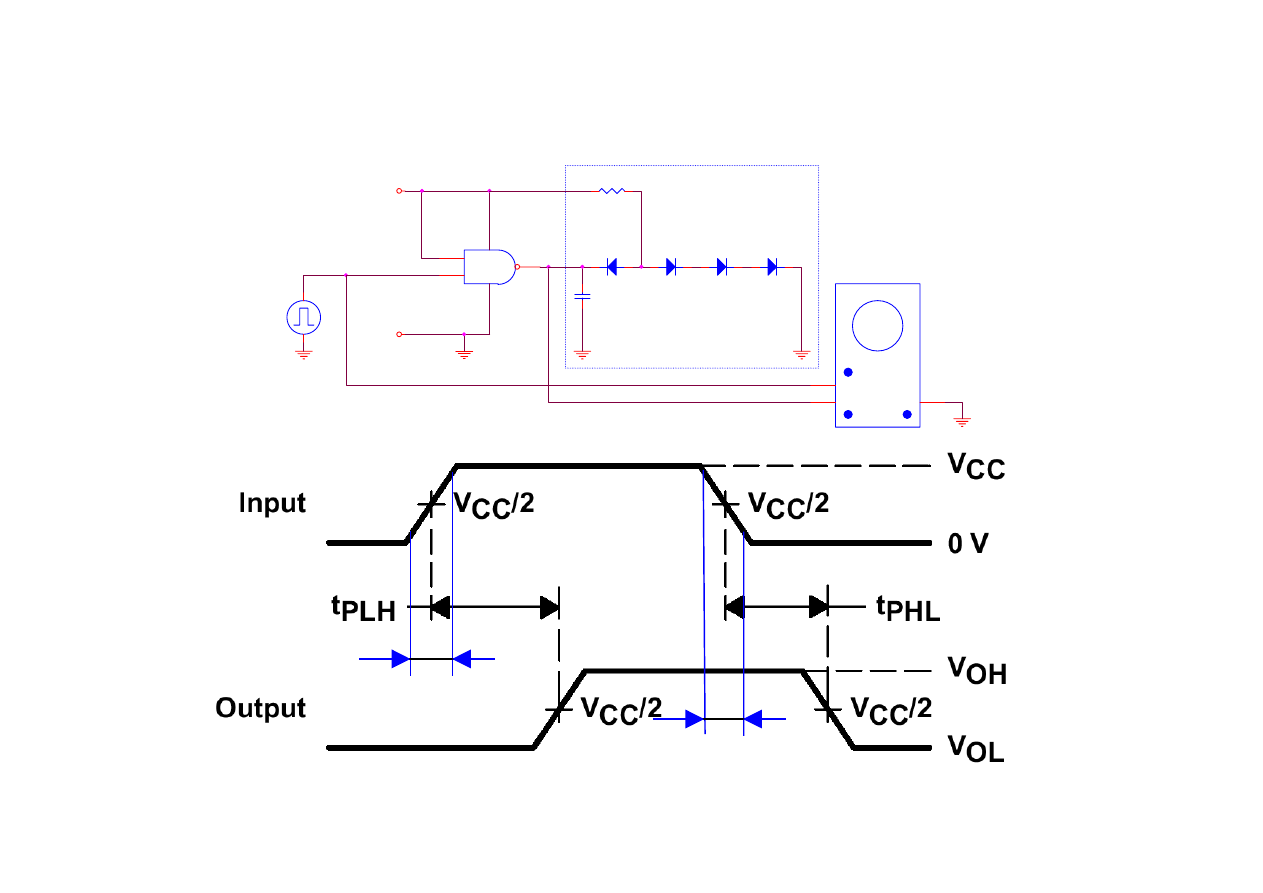

Podstawowe param. układów cyfrowych

Podstawowe param. układów cyfrowych

© K. MURAWSKI, J. TURCZYN

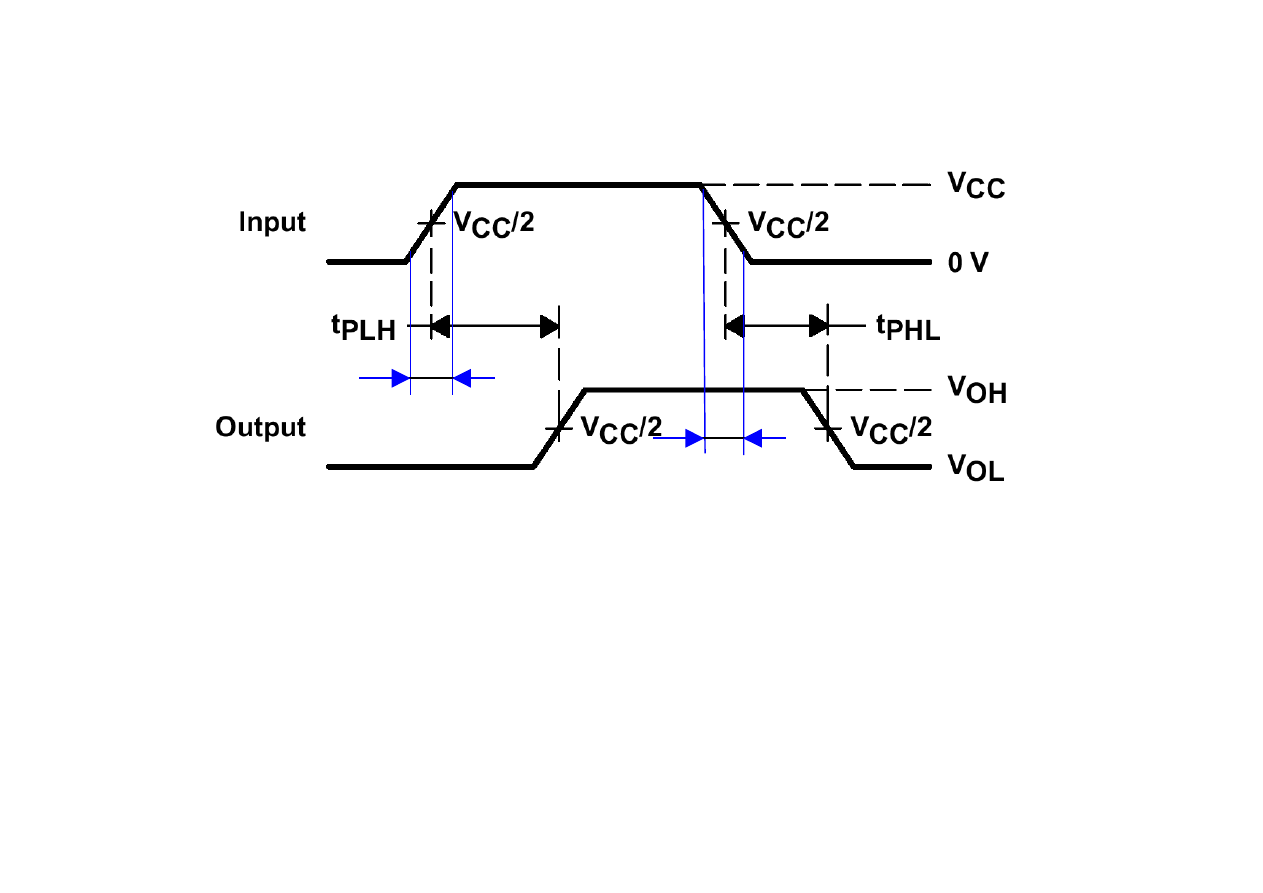

50%

10%

90%

t

TLH

50%

10%

90%

t

THL

t

t

PLH

PLH

–

–

Czas propagacji zmiany stanu z niskiego na wysoki;

Czas propagacji zmiany stanu z niskiego na wysoki;

t

t

PHL

PHL

–

–

Czas propagacji zmiany stanu z wysokiego na niski;

Czas propagacji zmiany stanu z wysokiego na niski;

t

t

TLH

TLH

,

,

t

t

r

r

–

–

Czas narastania zbocza sygnału;

Czas narastania zbocza sygnału;

t

t

THL

THL

,

,

t

t

f

f

–

–

Czas opadania zbocza sygnału.

Czas opadania zbocza sygnału.

20

Podstawowe param. układów cyfrowych

Podstawowe param. układów cyfrowych

© K. MURAWSKI, J. TURCZYN

Ucc=+5V

GND

A

B

Obci

enie

bramki TTL

1

2

3

Gen

390

15p

OSC

A

B

GND

50%

10%

90%

t

TLH

50%

10%

90%

t

THL

21

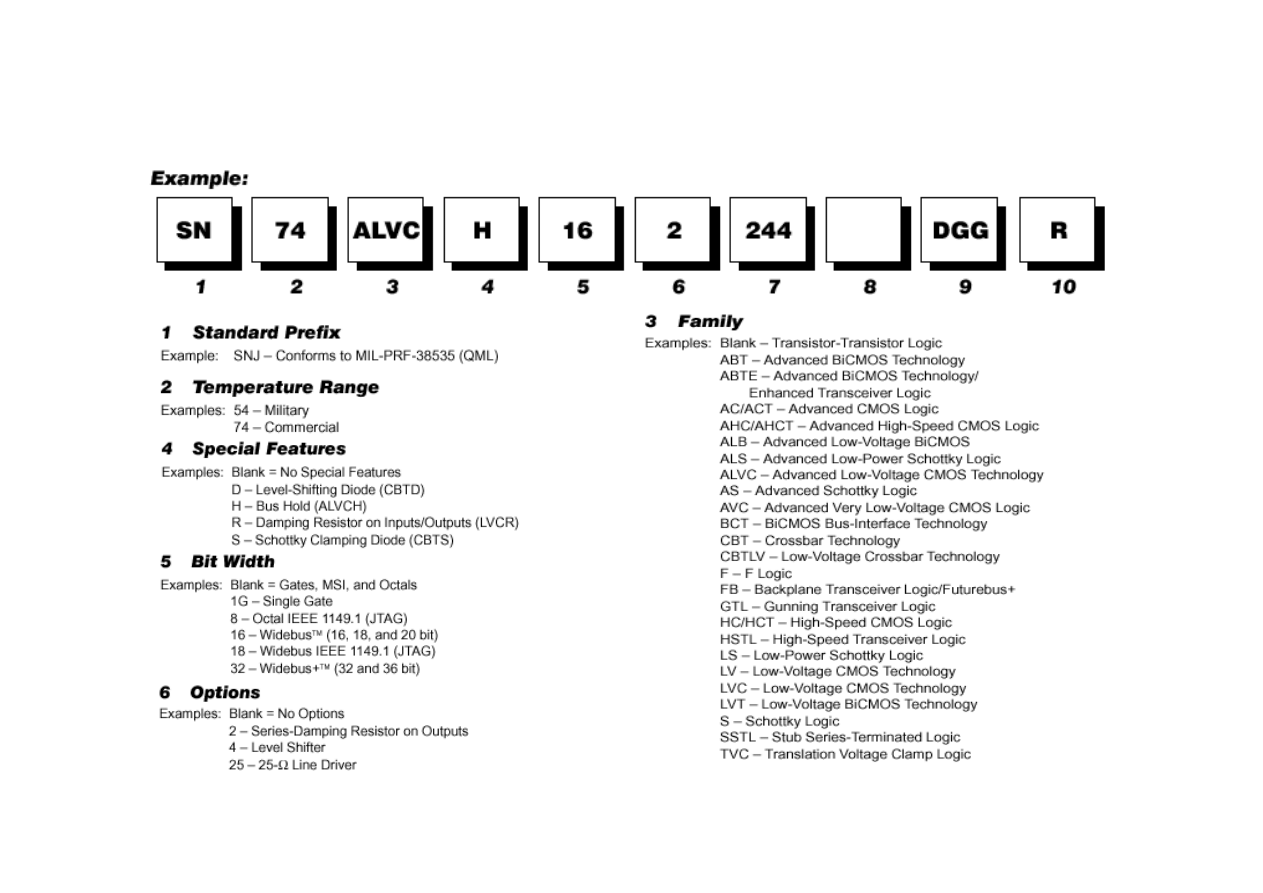

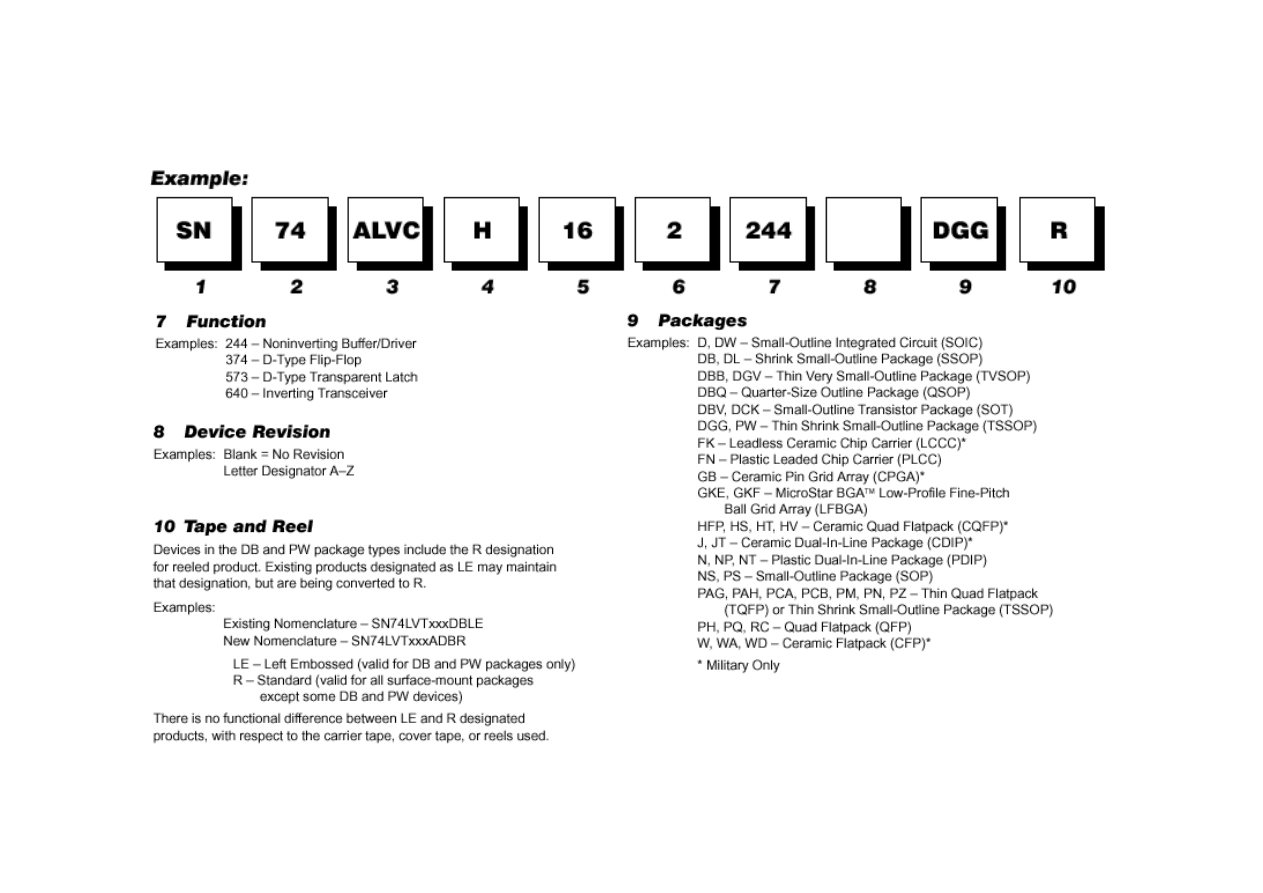

Ogólne zasady oznaczeń układów scalonych

Ogólne zasady oznaczeń układów scalonych

© K. MURAWSKI, J. TURCZYN

22

Ogólne zasady oznaczeń układów scalonych

Ogólne zasady oznaczeń układów scalonych

© K. MURAWSKI, J. TURCZYN

23

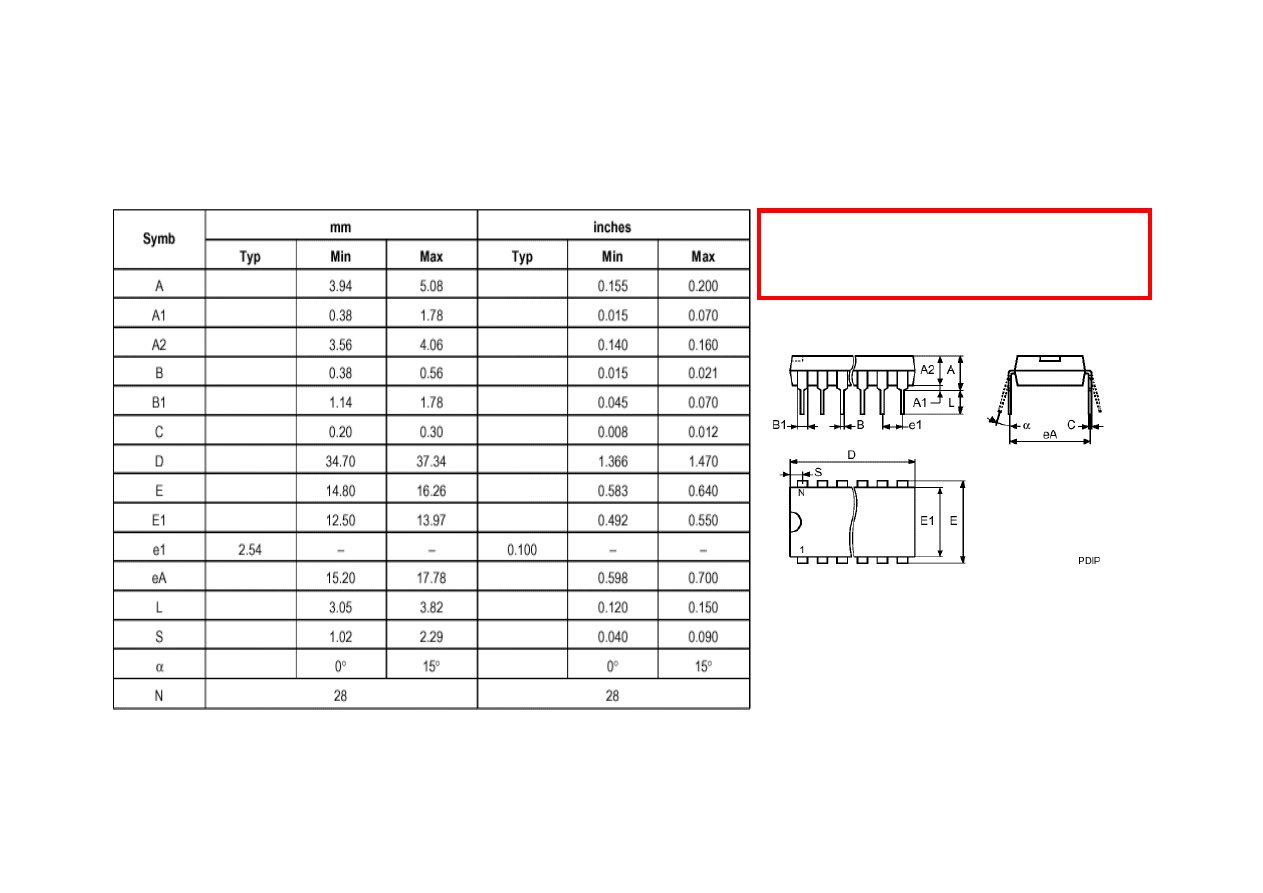

Układy scalone

Układy scalone

–

–

wymiary

wymiary

© K. MURAWSKI, J. TURCZYN

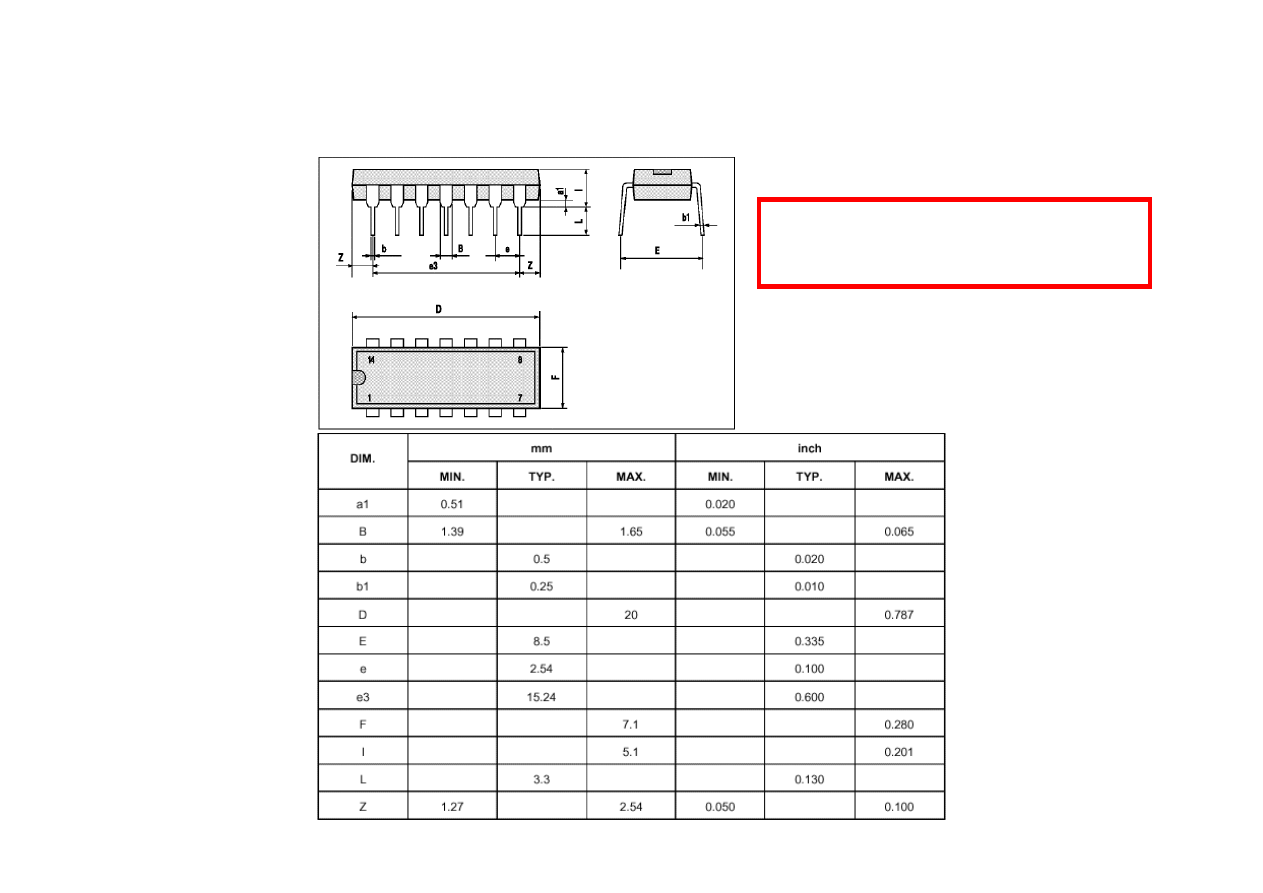

Obudowa typu:

DIP

(

P

lastic

D

ual

I

n line

P

ackage)

24

Układy scalone

Układy scalone

–

–

wymiary

wymiary

© K. MURAWSKI, J. TURCZYN

Obudowa typu:

DIP

(

P

lastic

D

ual

I

n line

P

ackage)

25

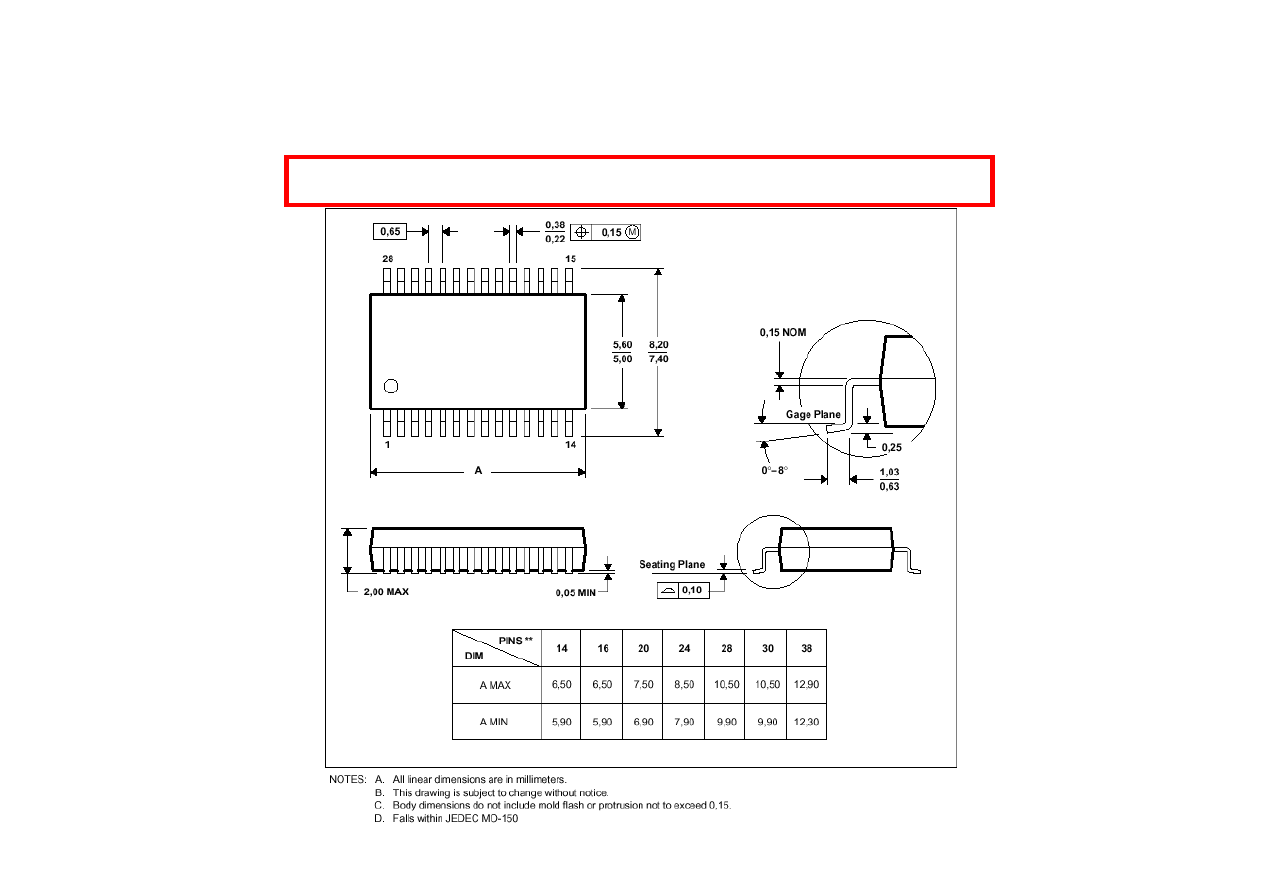

Układy scalone

Układy scalone

–

–

wymiary

wymiary

© K. MURAWSKI, J. TURCZYN

Obudowa typu:

SOP -

Plastic

S

mall

O

utline

P

ackage

26

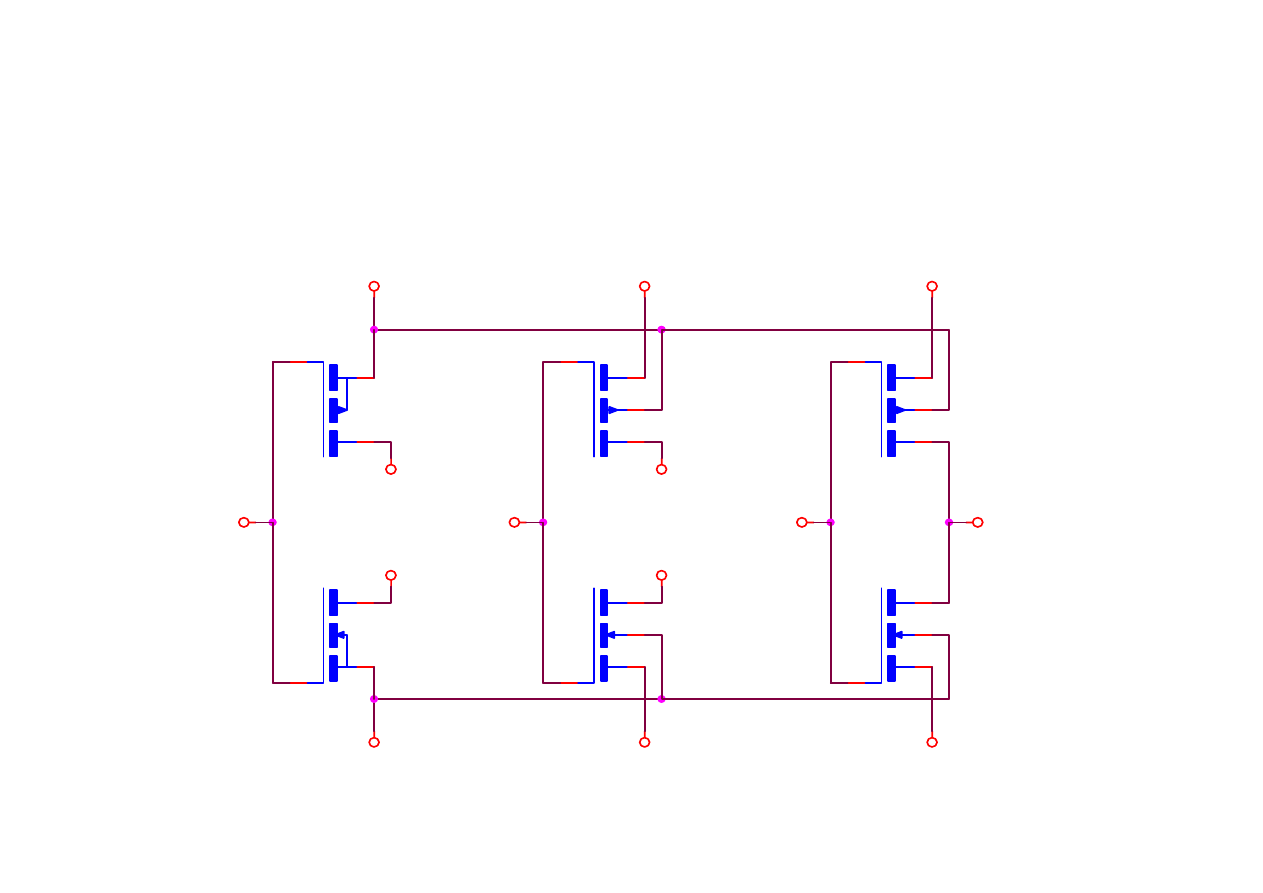

Układy scalone CMOS

Układy scalone CMOS

© K. MURAWSKI, J. TURCZYN

Układ scalony 4007

Układ scalony 4007

6

3

10

13

1

12

8

5

14

2

11

7

4

9

N

N

N

P

P

P

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

SS

U

DD

U

27

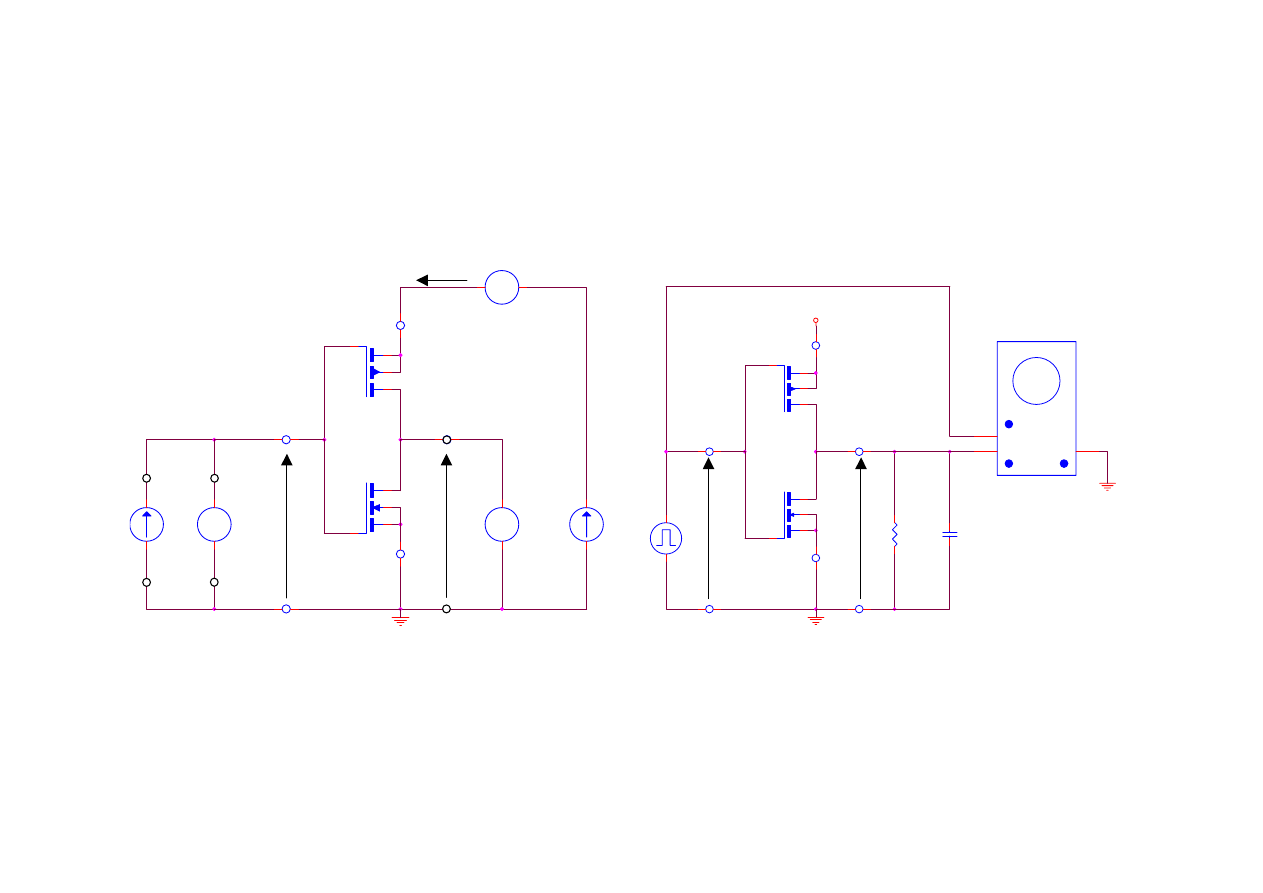

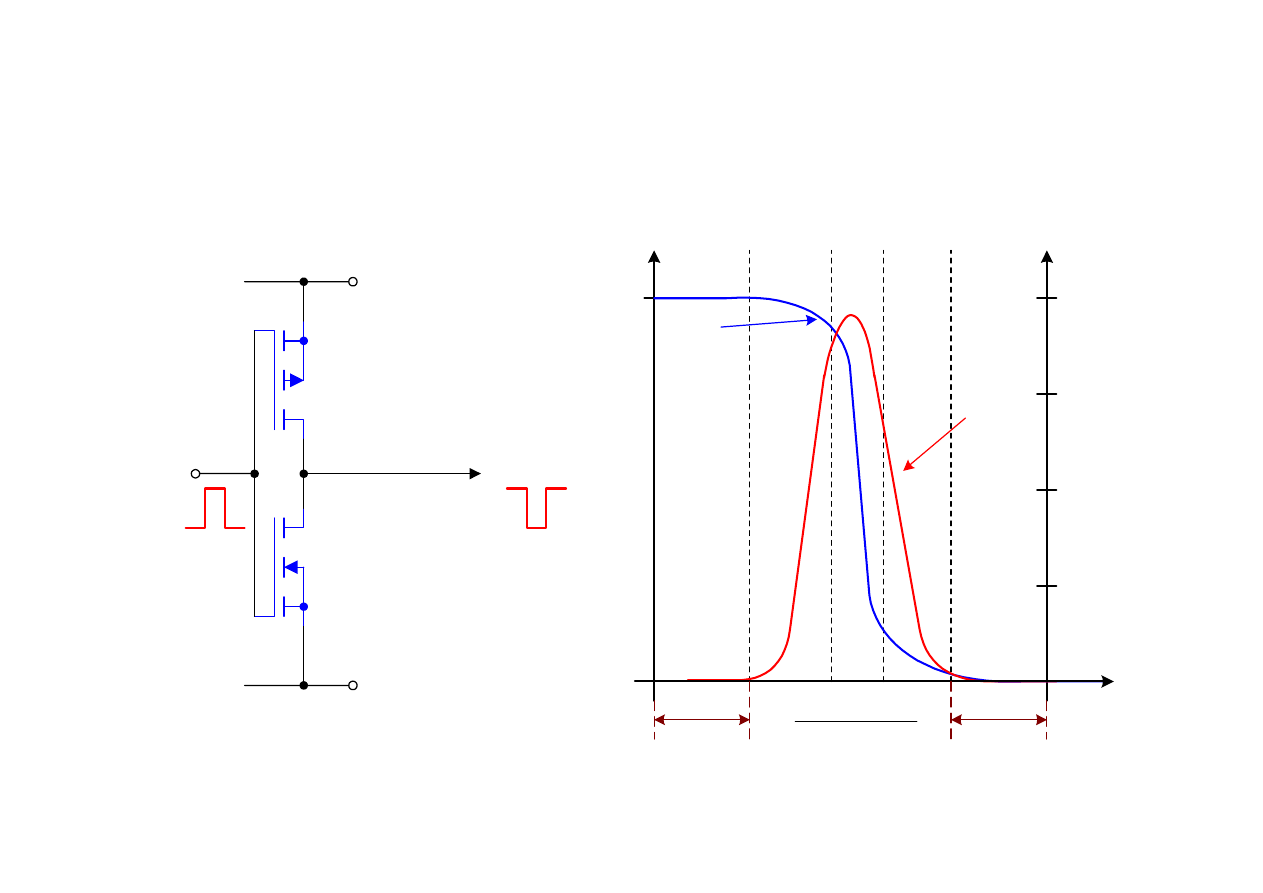

Inwerter

Inwerter

CMOS

CMOS

© K. MURAWSKI, J. TURCZYN

..

..

..

mA

V

V

..

..

T1

.

.

.

.

T2

.

.

.

.

O

U

5

DD

U

V

= +

DD

I

I

U

F

A

Udd=+5V

A

B

..

..

..

..

..

Gen

OSC

A

B

GND

..

T1

.

.

.

.

T2

.

.

.

.

10

L

R

K

=

200

L

C

pF

=

SS

U

O

U

F

A

I

U

28

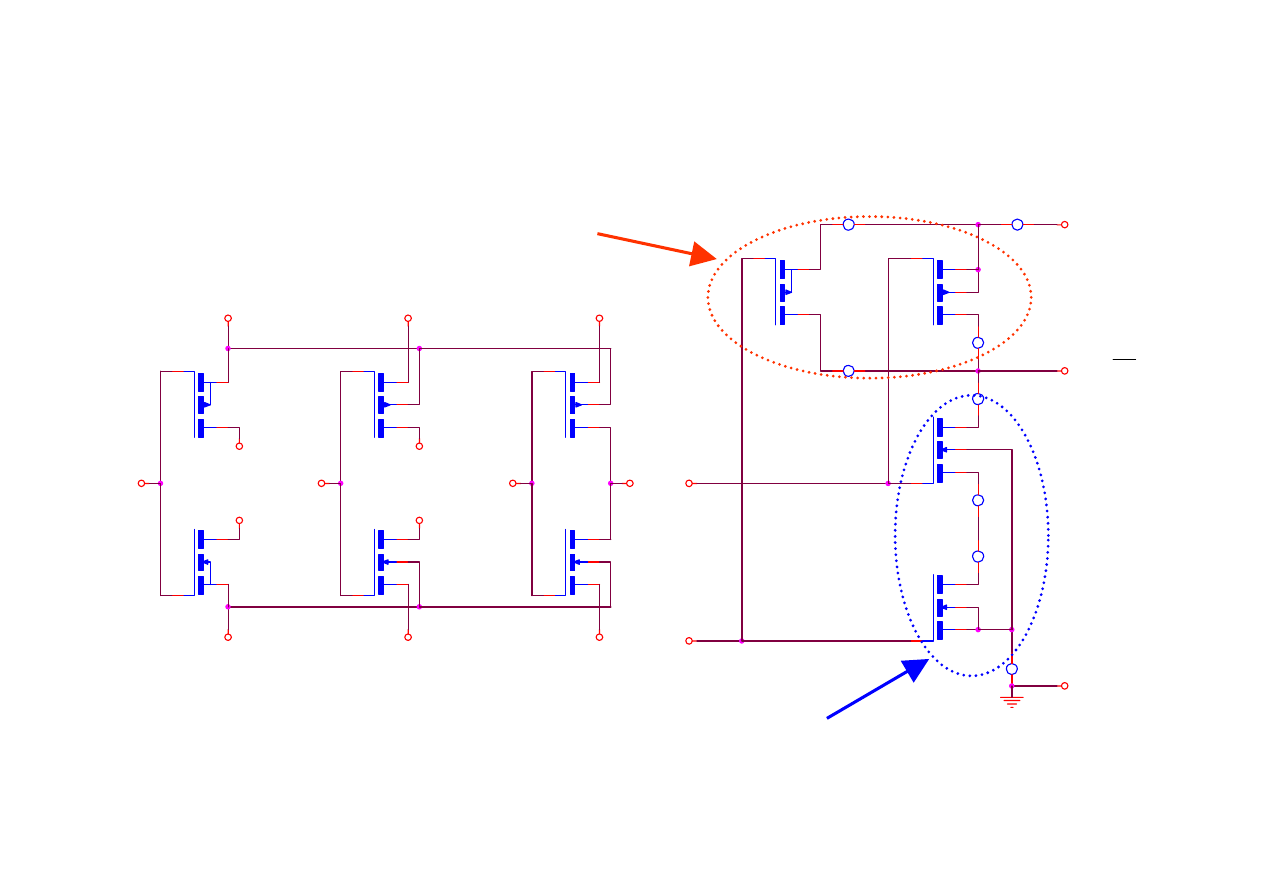

Bramka NAND

Bramka NAND

-

-

CMOS

CMOS

© K. MURAWSKI, J. TURCZYN

(na układzie 4007)

(na układzie 4007)

6

3

10

13

1

12

8

5

14

2

11

7

4

9

N

N

N

P

P

P

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

SS

U

DD

U

3

6

F = AB

Udd

Uss

N

N

P

P

A

B

.

.

.

.

.

.

.

.

.

.

.

14

..

2

..

13

..

1

..

5

..

4

..

8

..

7

..

.

.

.

.

Połączone równolegle

Połączone równolegle

Połączone szeregowo

Połączone szeregowo

29

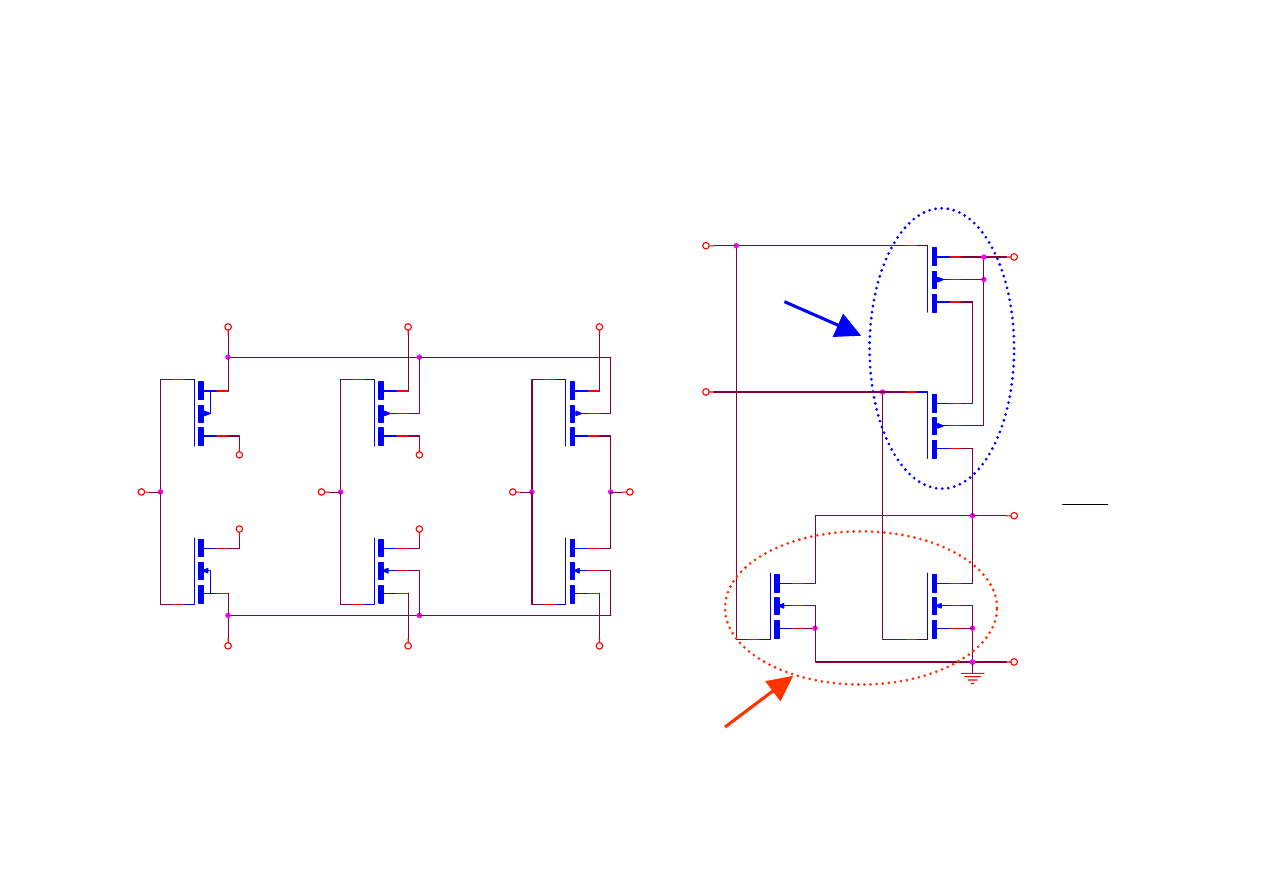

Bramka NOR

Bramka NOR

-

-

CMOS

CMOS

© K. MURAWSKI, J. TURCZYN

(na układzie 4007)

(na układzie 4007)

6

3

10

13

1

12

8

5

14

2

11

7

4

9

N

N

N

P

P

P

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

SS

U

DD

U

F = A + B

Udd

A

B

Uss

P

N

P

N

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Połączone równolegle

Połączone równolegle

Połączone szeregowo

Połączone szeregowo

30

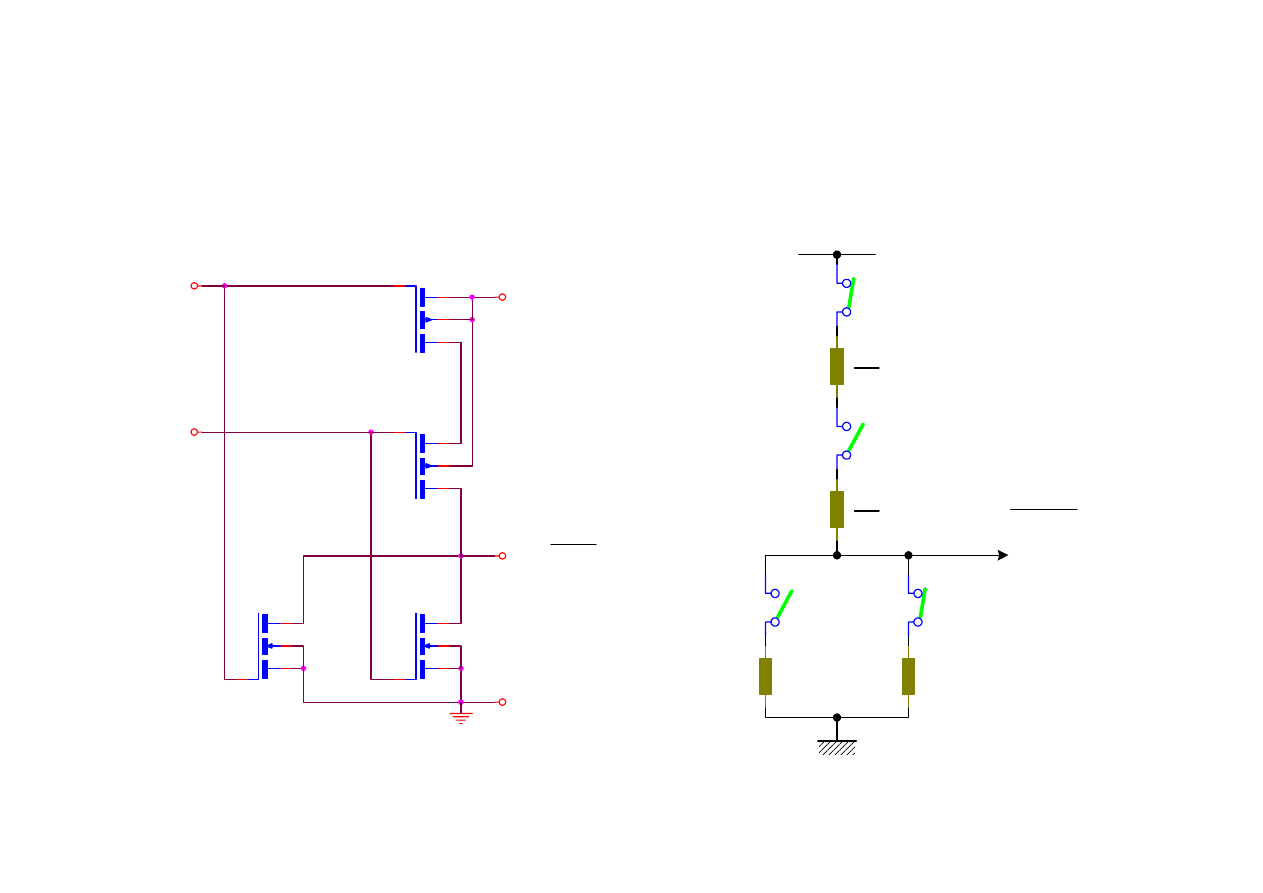

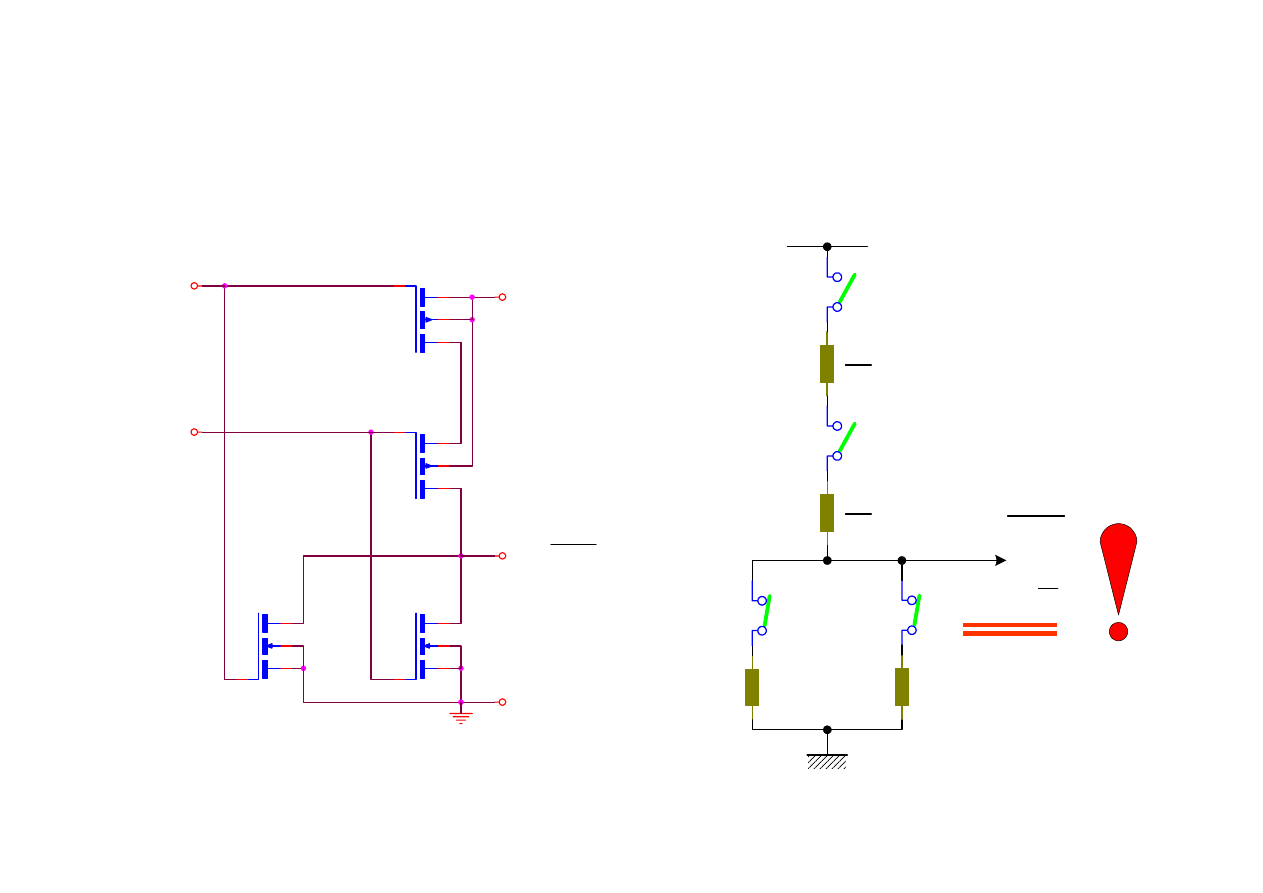

Rezystancja wyjściowa R

Rezystancja wyjściowa R

OUT

OUT

bramki CMOS

bramki CMOS

F = A + B

Udd

A

B

Uss

P

N

P

N

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

© K. MURAWSKI, J. TURCZYN

(BRAMKA NIE BUFOROWANA)

(BRAMKA NIE BUFOROWANA)

1P

2P

1N

2N

BRAMKA NIE BUFOROWANA

BRAMKA NIE BUFOROWANA

1P

CC

V

GND

2

R

2P

2

R

R

R

1N

2N

OUT

F

A B

R

R

= +

=

0

1

A

B

=

=

31

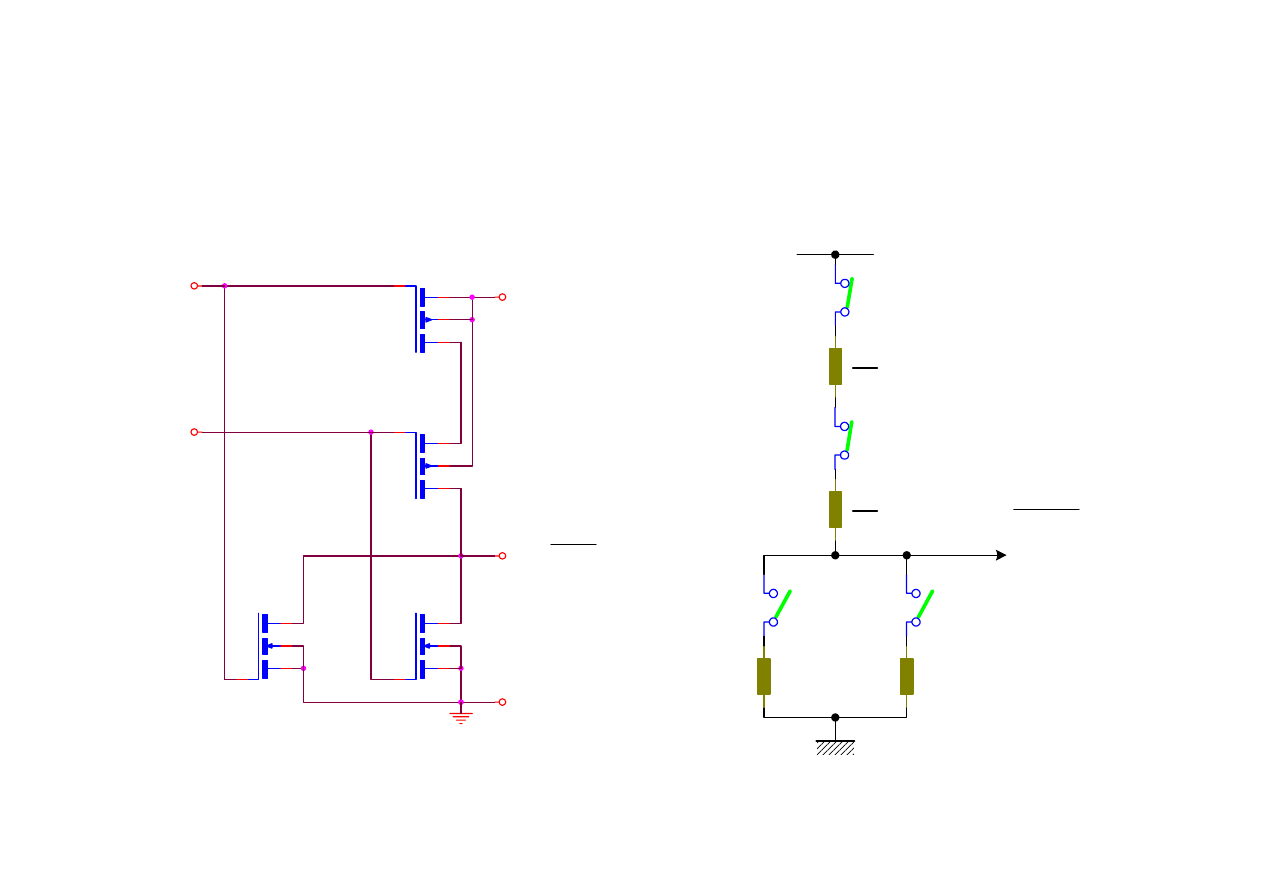

Rezystancja wyjściowa R

Rezystancja wyjściowa R

OUT

OUT

bramki CMOS

bramki CMOS

F = A + B

Udd

A

B

Uss

P

N

P

N

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

© K. MURAWSKI, J. TURCZYN

(BRAMKA NIE BUFOROWANA)

(BRAMKA NIE BUFOROWANA)

1P

2P

1N

2N

BRAMKA NIE BUFOROWANA

BRAMKA NIE BUFOROWANA

1P

CC

V

GND

2

R

2P

2

R

R

R

1N

2N

OUT

F

A B

R

R

= +

=

0

0

A

B

=

=

32

Rezystancja wyjściowa R

Rezystancja wyjściowa R

OUT

OUT

bramki CMOS

bramki CMOS

F = A + B

Udd

A

B

Uss

P

N

P

N

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

© K. MURAWSKI, J. TURCZYN

(BRAMKA NIE BUFOROWANA)

(BRAMKA NIE BUFOROWANA)

1P

2P

1N

2N

BRAMKA NIE BUFOROWANA

BRAMKA NIE BUFOROWANA

1P

CC

V

GND

2

R

2P

2

R

R

R

1N

2N

2

OUT

F

A B

R

R

= +

=

1

1

A

B

=

=

33

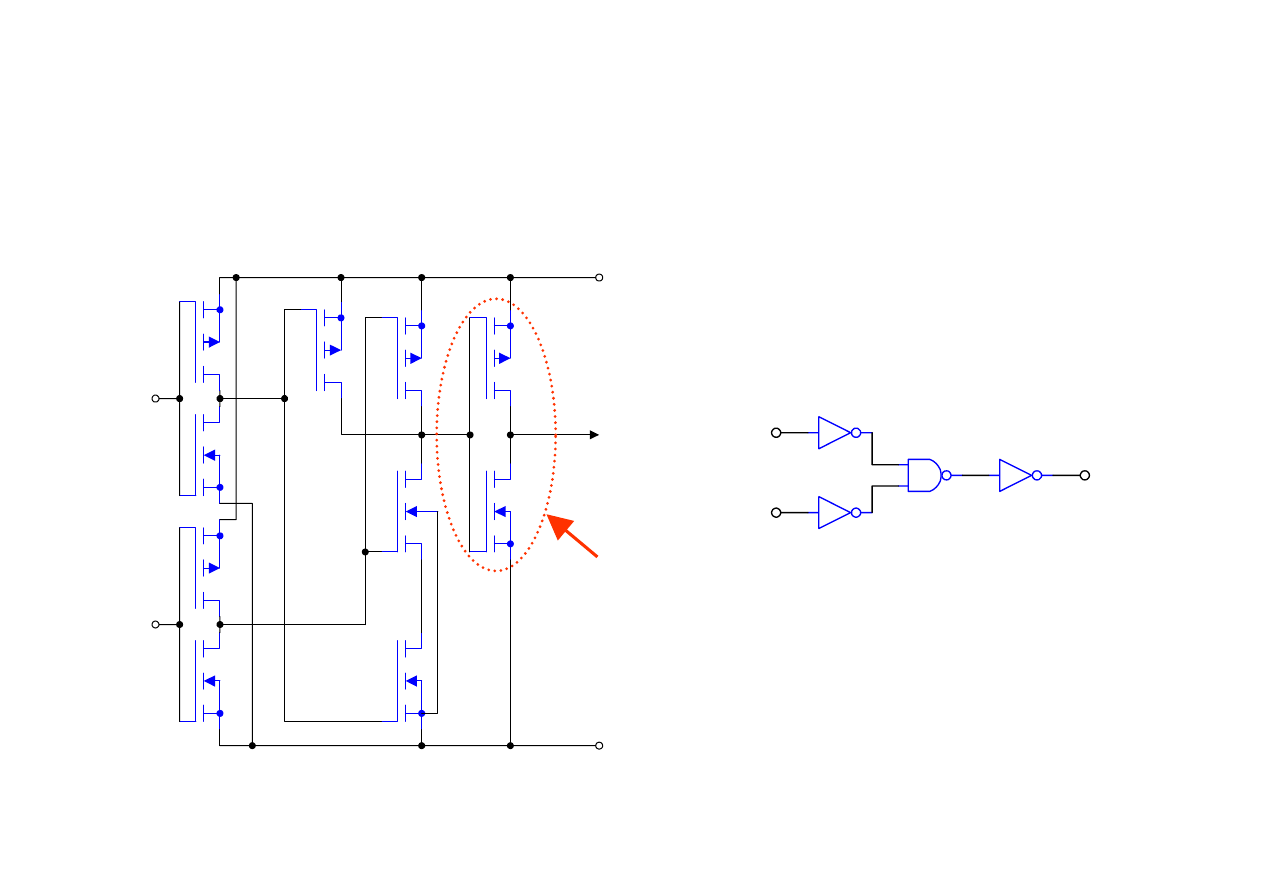

Buforowana bramka NOR CMOS

Buforowana bramka NOR CMOS

© K. MURAWSKI, J. TURCZYN

BRAMKA BUFOROWANA

BRAMKA BUFOROWANA

A

B

F

V

CC

V

SS

Inwerter buforujący

wyjście, R

OUT

= R.

A

B

F

Schemat ideowy

Schemat ideowy

34

U

I

U

O

[V]

I

DD

[mA]

[V]

SS

U

TN

U

TP

U

DD

U

O

U

DD

I

2

DD

SS

U

U

−

T1 - n.n.

T2 - zab.

T1 - n.n.

T2 - nas.

T1 - nas.

T2 - nas.

T1 - nas.

T2 - n.n.

T1 - zab.

T2 - n.n.

Charakterystyki

Charakterystyki

inwertera

inwertera

CMOS

CMOS

© K. MURAWSKI, J. TURCZYN

Charakterystyka przejściowa i poboru prądu

Charakterystyka przejściowa i poboru prądu

A

F

V

CC

V

SS

T2 (N)

T1 (P)

U

O

U

I

zab

zab

.

.

–

–

zablokowany; n.n.

zablokowany; n.n.

–

–

nienasycony; nas.

nienasycony; nas.

-

-

nasycony

nasycony

35

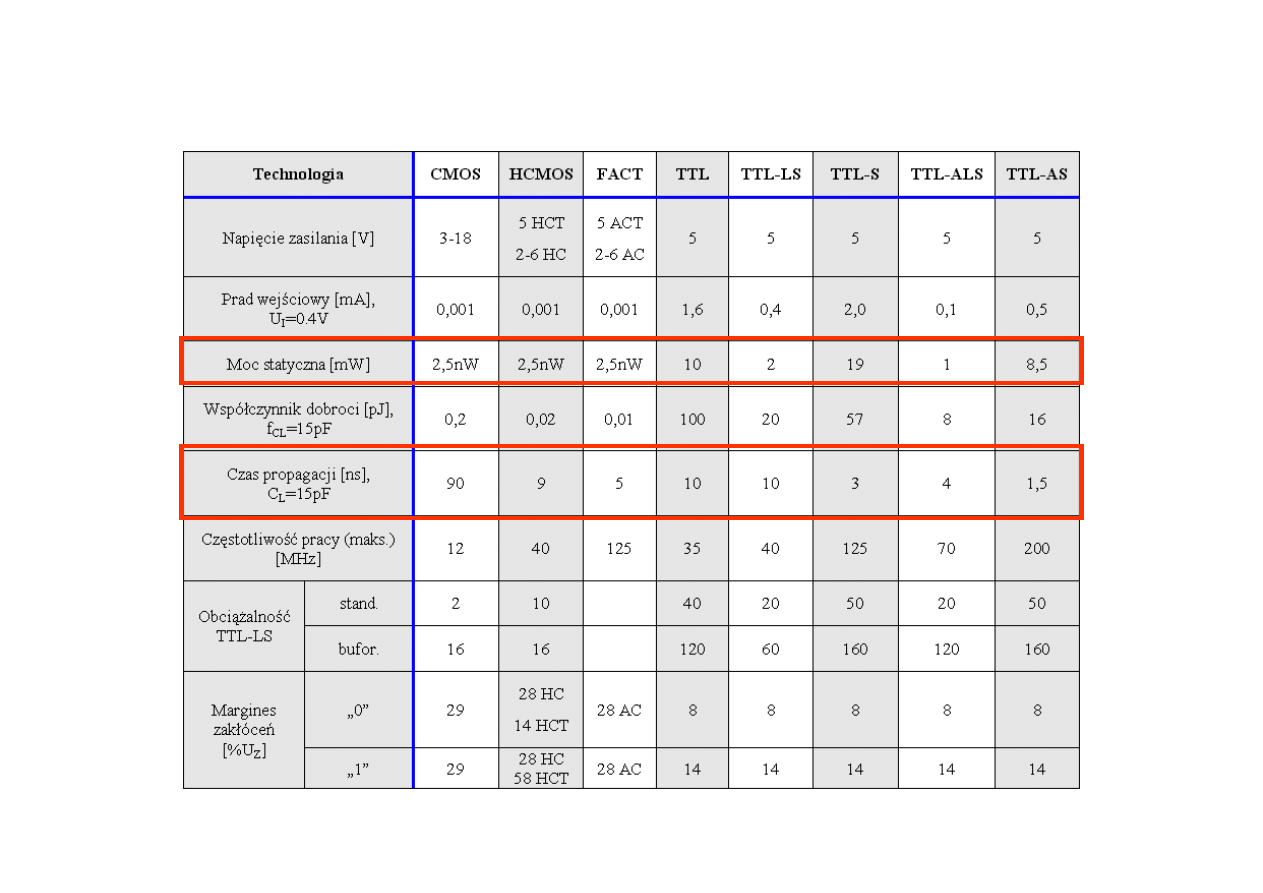

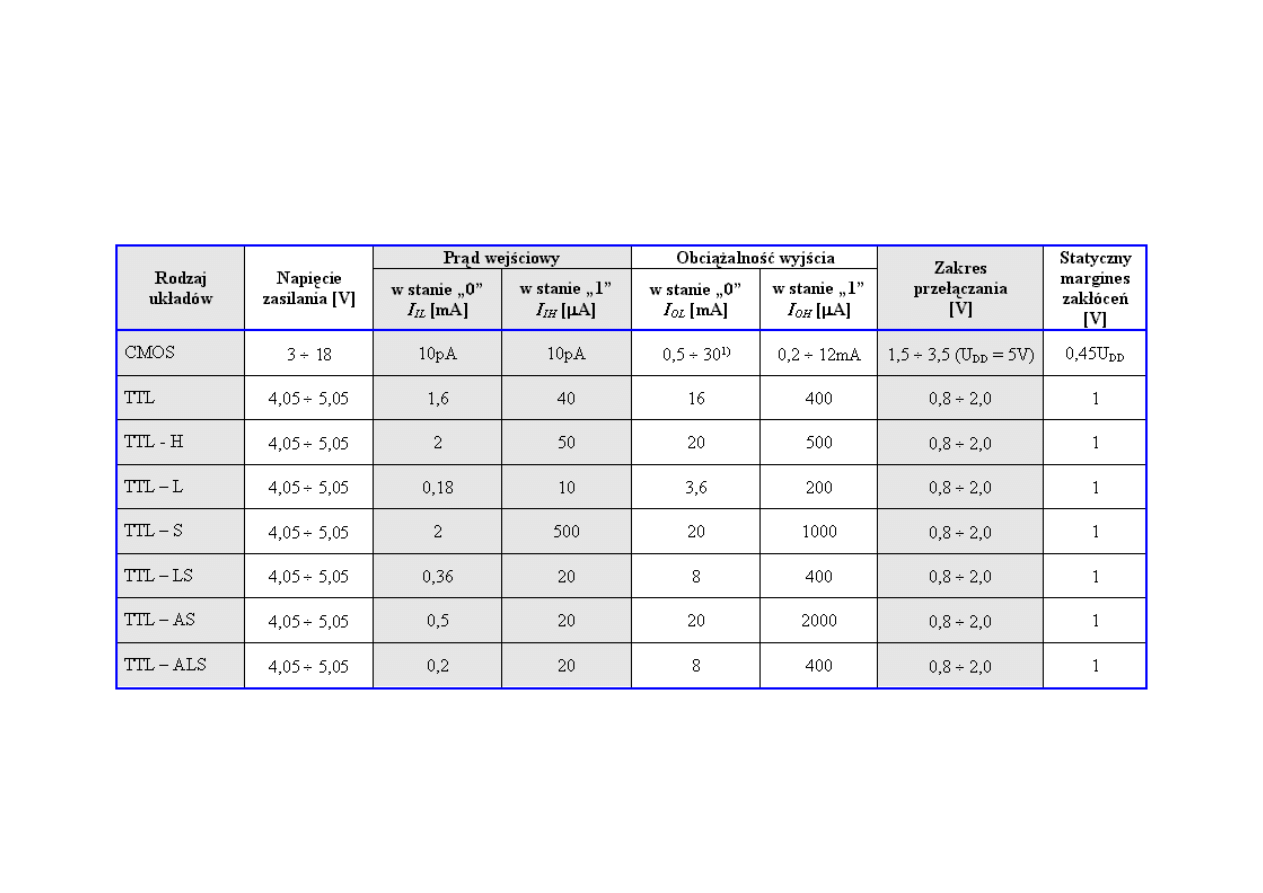

Podstaw. param. rodzin układów CMOS i TTL

Podstaw. param. rodzin układów CMOS i TTL

© K. MURAWSKI, J. TURCZYN

36

Parametry układów CMOS i TTL

Parametry układów CMOS i TTL

istotne przy łączeniu

istotne przy łączeniu

© K. MURAWSKI, J. TURCZYN

1)

1)

przy: U

przy: U

DD

DD

=5V, U

=5V, U

OL

OL

= 0,4V

= 0,4V

→

→

I

I

OLmin

OLmin

= 1mA;

= 1mA;

U

U

DD

DD

=5V, U

=5V, U

OH

OH

= 4,6V

= 4,6V

→

→

I

I

OHmin

OHmin

= 1mA.

= 1mA.

37

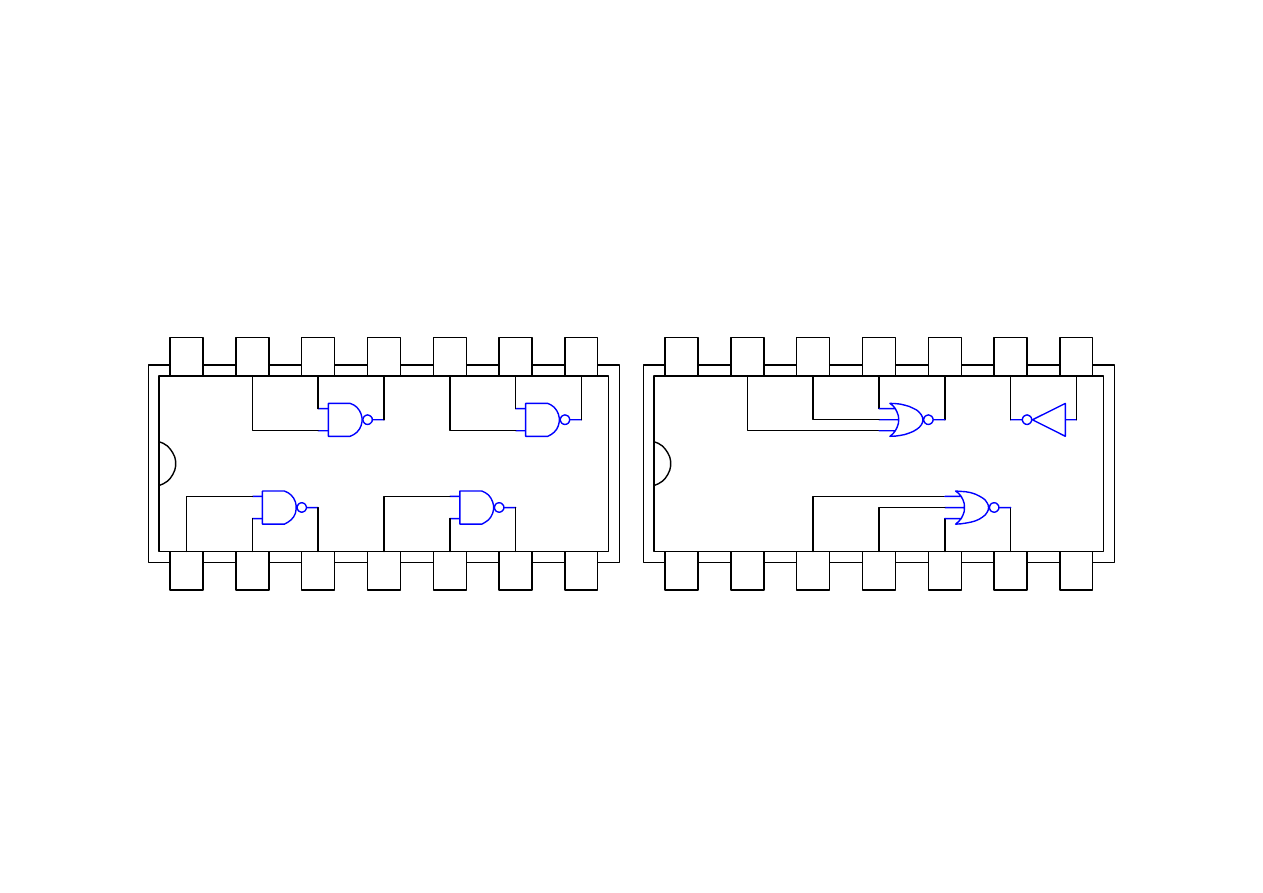

Uwaga: „

Uwaga: „

podobne

podobne

” nie znaczy „

” nie znaczy „

takie same

takie same

”

”

© K. MURAWSKI, J. TURCZYN

1

2

3

4

5

6

7

14

13

12

11

10

9

8

NC NC 1A

1B

1C

1Y

3Y

2Y

2A

3C

3B

3A

V

cc

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

3B

3A

3Y

4B

4A

4Y

V

cc

GND

SN7400

74000

TTL

CMOS

38

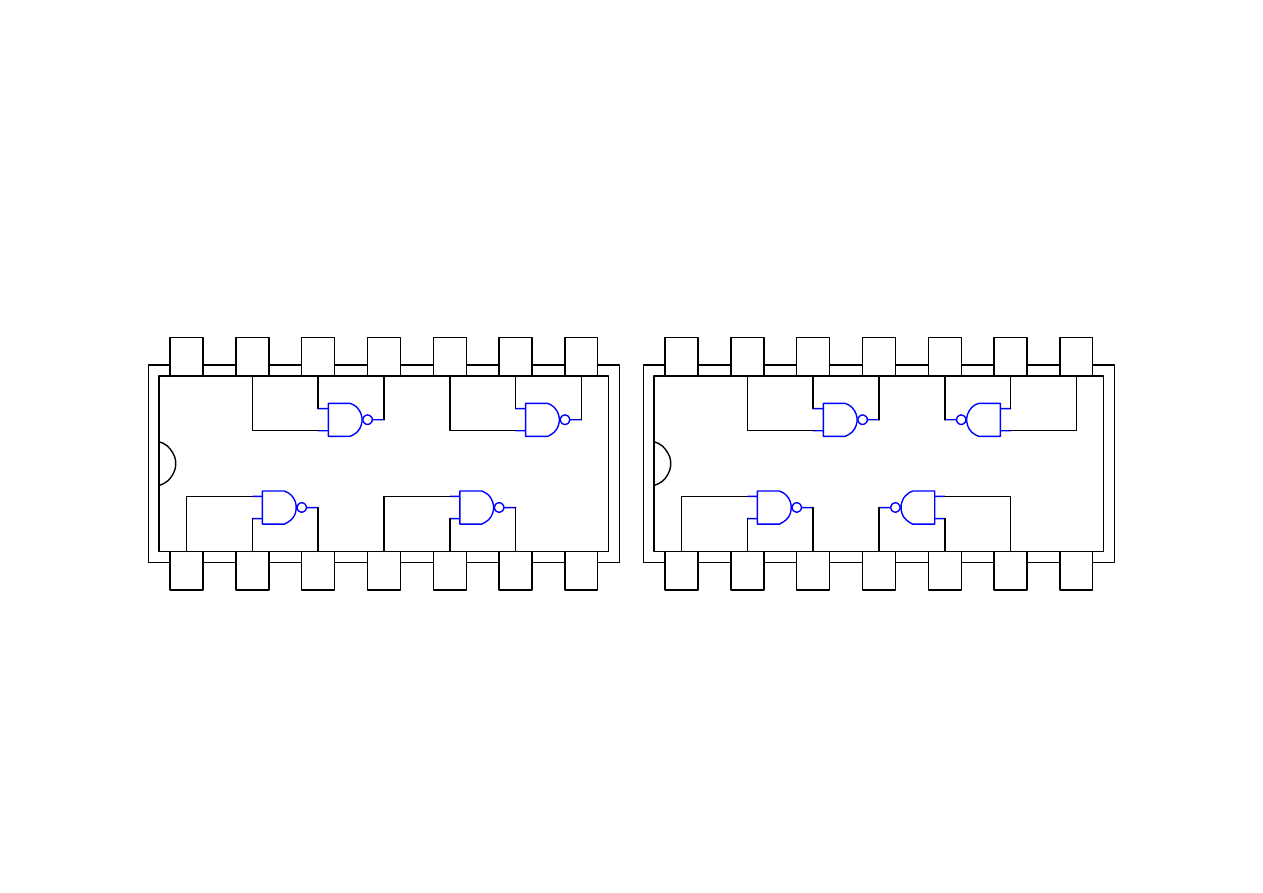

Uwaga: „

Uwaga: „

podobne

podobne

” nie znaczy „

” nie znaczy „

takie same

takie same

”

”

© K. MURAWSKI, J. TURCZYN

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2A

2B

2Y

3B

3A

3Y

4B

4A

4Y

V

cc

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1A

1B

1Y

2Y

2A

2B

3Y

3B

3A

4B

4A

4Y

V

cc

GND

SN7400

74011

TTL

CMOS

Wyszukiwarka

Podobne podstrony:

05 SkaleScalenia

podrecznik 2 18 03 05

regul praw stan wyjątk 05

05 Badanie diagnostyczneid 5649 ppt

Podstawy zarządzania wykład rozdział 05

05 Odwzorowanie podstawowych obiektów rysunkowych

05 Instrukcje warunkoweid 5533 ppt

05 K5Z7

05 GEOLOGIA jezior iatr morza

05 IG 4id 5703 ppt

05 xml domid 5979 ppt

Świecie 14 05 2005

Wykł 05 Ruch drgający

TD 05

6 Zagrozenia biosfery 07 05 05

więcej podobnych podstron