„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

MINISTERSTWO EDUKACJI

NARODOWEJ

Hanna Grządziel

Wykonywanie badań i pomiarów układów cyfrowych

stosowanych w telekomunikacji

725

[02].O1.04

Poradnik dla ucznia

Wydawca

Instytut Technologii Eksploatacji – Państwowy Instytut Badawczy

Radom 2006

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

1

Recenzenci:

mgr inż. Anna Górska

mgr inż. Beata Miętus

Opracowanie redakcyjne:

mgr inż. Hanna Grządziel

Konsultacja:

mgr inż. Andrzej Zych

Korekta:

Poradnik stanowi obudowę dydaktyczną programu jednostki modułowej 725[02].O1.04

„Wykonywanie badań i pomiarów układów cyfrowych stosowanych w telekomunikacji”

zawartego w modułowym programie nauczania dla zawodu Monter sieci i urządzeń

telekomunikacyjnych.

Wydawca

Instytut Technologii Eksploatacji – Państwowy Instytut Badawczy, Radom 2006

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

2

SPIS TREŚCI

1. Wprowadzenie

3

2. Wymagania wstępne

5

3. Cele kształcenia

6

4. Materiał nauczania

7

4.1. Sygnał cyfrowy i pozycyjne systemy liczbowe

7

4.1.1. Materiał nauczania

7

4.1.2. Pytania sprawdzające

14

4.1.3. Ćwiczenia

14

4.1.4. Sprawdzian postępów

16

4.2. Synteza układów kombinacyjnych

17

4.2.1. Materiał nauczania

17

4.2.2. Pytania sprawdzające

23

4.2.3. Ćwiczenia

23

4.2.4. Sprawdzian postępów

26

4.3. Komutacyjne i arytmetyczne układy cyfrowe

27

4.3.1. Materiał nauczania

27

4.3.2. Pytania sprawdzające

33

4.3.3. Ćwiczenia

33

4.3.4. Sprawdzian postępów

35

4.4. Układy sekwencyjne - liczniki, rejestry

36

4.4.1. Materiał nauczania

36

4.4.2. Pytania sprawdzające

41

4.4.3. Ćwiczenia

41

4.4.4. Sprawdzian postępów

43

4.5. Pamięci i układy mikroprocesorowe

44

4.5.1. Materiał nauczania

44

4.5.2. Pytania sprawdzające

47

4.5.3. Ćwiczenia

48

4.5.4. Sprawdzian postępów

49

5. Sprawdzian osiągnięć

50

6. Literatura

56

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

3

1. WPROWADZENIE

Poradnik stanowi pomoc w przyswajaniu wiedzy o układach cyfrowych technologii TTL

i CMOS, a także ułatwia wykonywanie badań, lokalizację usterek i uruchamianie prostych

układów cyfrowych.

Poradnik ten zawiera:

1. Wymagania wstępne, czyli wykaz niezbędnych umiejętności i wiedzy, które powinieneś

mieć opanowane, aby przystąpić do realizacji tej jednostki modułowej.

2. Cele kształcenia tej jednostki modułowej.

3. Materiał nauczania (rozdział 4) podzielony na 5 tematów. Umożliwia on samodzielne

przygotowanie się do odpowiedzi na pytania sprawdzające, wykonania ćwiczeń i

sprawdzianów postępów. Wykonując sprawdzian postępów powinieneś odpowiadać na

pytanie „tak”–, jeśli opanowałeś materiał lub „nie”, co oznacza, że powinieneś jeszcze

nad tym popracować. Do poszerzenia wiedzy wykorzystaj wskazaną literaturę oraz inne

źródła informacji.

Ćwiczenia znajdujące się w każdym temacie zawierają treść poleceń, wskazówki

dotyczące sposobu wykonania oraz opis wyposażenia stanowiska potrzebnego do

realizacji ćwiczenia. Jeżeli masz trudności ze zrozumieniem tematu lub ćwiczenia, to

poproś nauczyciela lub instruktora o wyjaśnienie i ewentualne sprawdzenie, czy dobrze

wykonujesz daną czynność.

4. W rozdziale 5 poradnika zamieszczony jest zestaw zadań sprawdzających Twoje

opanowanie wiedzy i umiejętności z zakresu całej jednostki modułowej. Prawidłowe

wykonanie tego sprawdzianu jest dowodem osiągnięcia umiejętności określonych

w tej jednostce modułowej. Przykładowe testy sprawdzające znajdziesz także

w literaturze [1].

Jednostka modułowa: Wykonywanie badań i pomiarów układów cyfrowych stosowanych

w telekomunikacji, której treści teraz poznasz jest konieczna do zapoznania się z procesem

analizy działania i lokalizacji usterek w układach cyfrowych i stanowi jedną z pięciu

jednostek

w

module

725[02].O1

–

Pomiary

parametrów

elementów

i układów elektronicznych – schemat 1. Ten ogólnozawodowy moduł przygotowuje Cię do

realizacji modułów zawodowych programu nauczania dla zawodu monter sieci

i urządzeń telekomunikacyjnych.

Bezpieczeństwo i higiena pracy

W czasie pobytu w pracowni musisz przestrzegać regulaminów, przepisów bhp oraz

instrukcji przeciwpożarowych, wynikających z rodzaju wykonywanych prac. Przepisy te

poznasz

podczas

przeszkolenia

wstępnego

rozpoczynającego

Twoja

pracę

w laboratorium.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

4

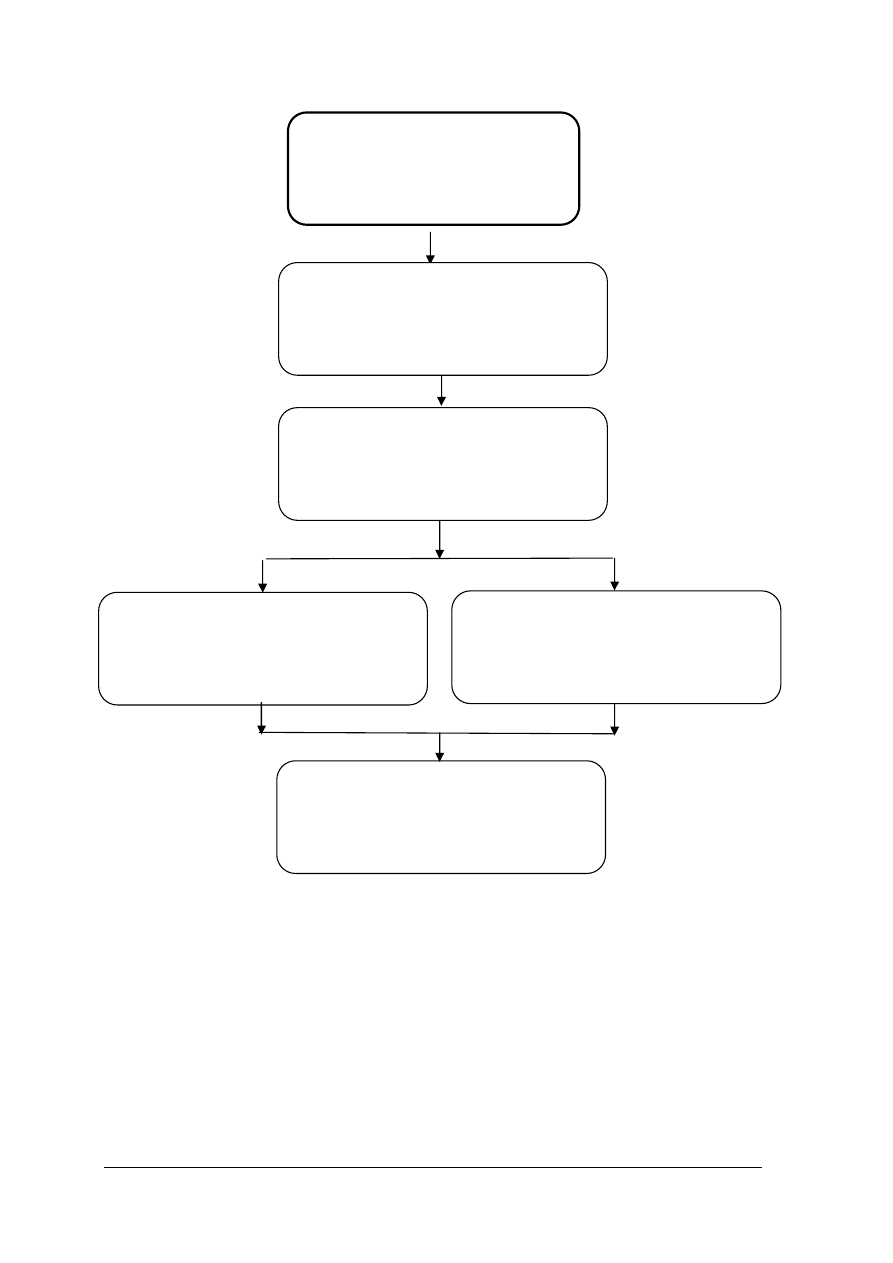

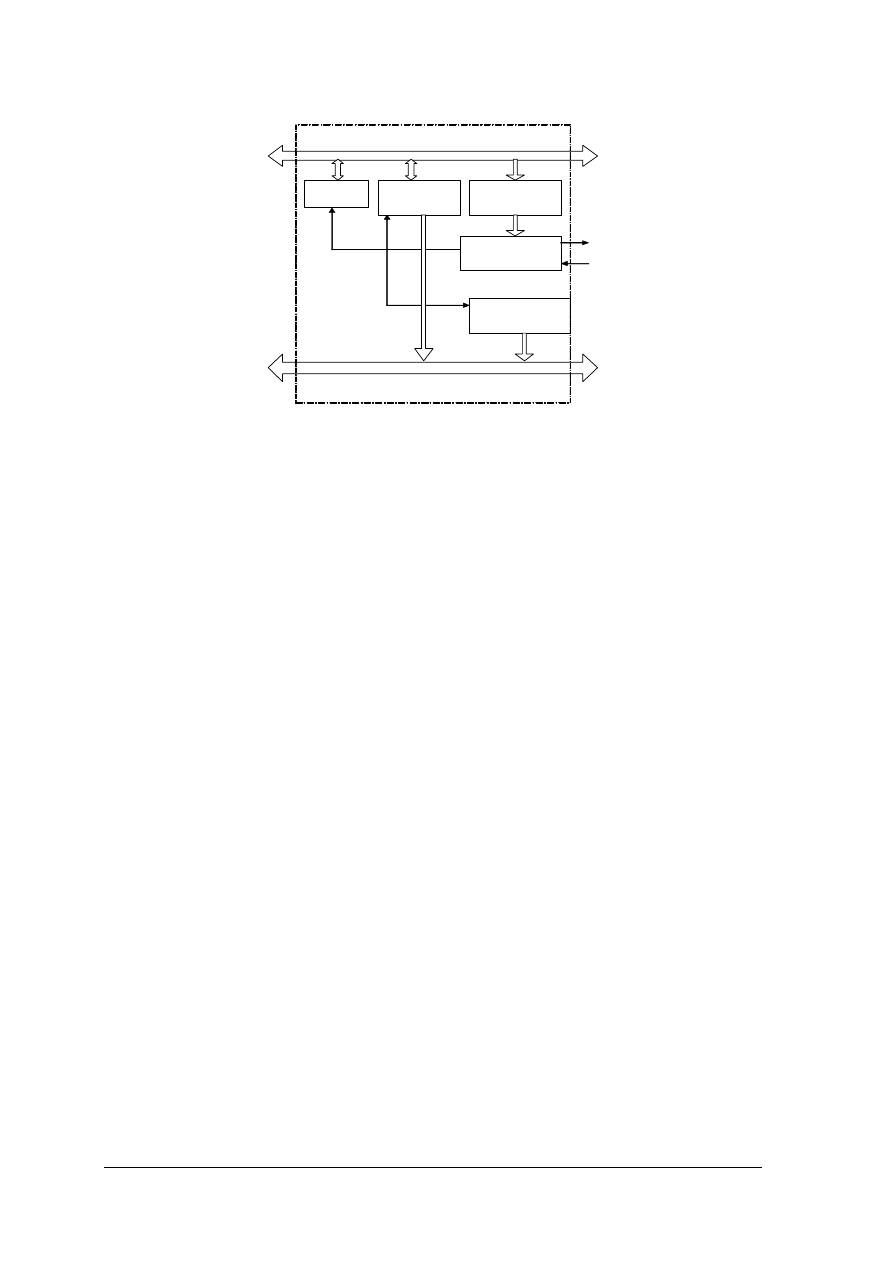

725(02).O1

Pomiary parametrów elementów

i układów elektronicznych

725(02).O1.05

Analiza działania oraz zastosowania

podstawowych maszyn i urządzeń

elektrycznych

725(02).O1.03

Wykonywanie badań i pomiarów układów

analogowych stosowanych

w telekomunikacji

725(02).O1.01

Wykonywanie badań i pomiarów obwodów

prądu stałego

725(02).O1.02

Wykonywanie badań i pomiarów obwodów

prądu przemiennego

725(02).O1.04

Wykonywanie badań i pomiarów

układów cyfrowych stosowanych

w telekomunikacji

Schemat układu jednostek modułowych w module 725[02].O1

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

5

2. WYMAGANIA WSTĘPNE

Przystępując do realizacji programu jednostki modułowej „Wykonywanie badań

i pomiarów układów cyfrowych stosowanych w telekomunikacji” powinieneś umieć:

–

stosować podstawowe prawa elektrotechniki,

–

interpretować

podstawowe

zjawiska

z

zakresu

elektrotechniki

występujące

w obwodach prądu stałego i zmiennego,

–

rozpoznawać na podstawie wyglądu oraz symbolu elementy elektroniczne,

–

analizować proste układy prądu stałego i zmiennego,

–

obliczać i oszacować podstawowe wielkości elektryczne w układach prądu stałego

i zmiennego,

–

dobierać przyrządy pomiarowe do pomiarów w układach prądu stałego i zmiennego,

–

rysować prosty układ pomiarowy,

–

planować pomiary w obwodach prądu stałego i zmiennego,

–

organizować stanowisko pomiarowe,

–

łączyć układy zgodnie ze schematem,

–

dokonywać pomiarów podstawowych wielkości elektrycznych w układach prądu stałego

i zmiennego,

–

analizować i interpretować wyniki pomiarów oraz wyciągać wnioski praktyczne,

–

przedstawiać wyniki w formie tabeli i wykresu,

–

czytać informację z tabeli lub wykresu,

–

demonstrować efekty wykonywanych pomiarów,

–

przewidywać zagrożenia dla życia i zdrowia w czasie realizacji ćwiczeń,

–

udzielać pierwszej pomocy w przypadkach porażenia prądem elektrycznym,

–

stosować procedurę postępowania w sytuacji zagrożenia,

–

korzystać z różnych źródeł informacji.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

6

3. CELE KSZTAŁCENIA

W wyniku realizacji programu jednostki modułowej powinieneś umieć:

–

zakodować liczby w kodzie binarnym, heksagonalnym i BCD,

–

zastosować podstawowe prawa algebry Boole’a,

–

rozpoznać na podstawie symbolu graficznego i katalogowego podstawowe elementy

cyfrowe i technologie ich wykonania,

–

rozróżnić funkcje podstawowych układów cyfrowych,

–

przeanalizować działanie prostych układów cyfrowych na podstawie schematów

logicznych,

–

przeanalizować działanie układów cyfrowych na podstawie schematów blokowych,

–

wskazać podstawowe zastosowania elementów i układów cyfrowych,

–

obsłużyć urządzenia do testowania elementów układów cyfrowych,

–

zinterpretować wyniki pomiarów w układach cyfrowych oraz wyciągnąć wnioski

praktyczne,

–

skorzystać z katalogów układów cyfrowych różnych technologii,

–

połączyć proste układy do badania elementów cyfrowych i bloków funkcjonalnych,

–

wykryć usterki w układach cyfrowych,

–

przewidzieć zagrożenia dla życia i zdrowia w czasie realizacji ćwiczeń.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

7

4. MATERIAŁ NAUCZANIA

4.1. Sygnał cyfrowy i pozycyjne systemy liczbowe

4.1.1. Materiał nauczania

4.1.1.1. Pozycyjne systemy liczbowe

Wszyscy posługujemy się na codzień systemem dziesiętnym, który jest systemem

pozycyjnym, tzn. na poszczególnych pozycjach zapisywana jest liczba jednostek, dziesiątek,

setek, tysięcy,....

2856 = 2 * 1000 + 0 * 100 + 0 * 10+6 * 1= 2 * 10

3

+ 8 * 10

2

+ 5 * 10

1

+ 6 * 10

0

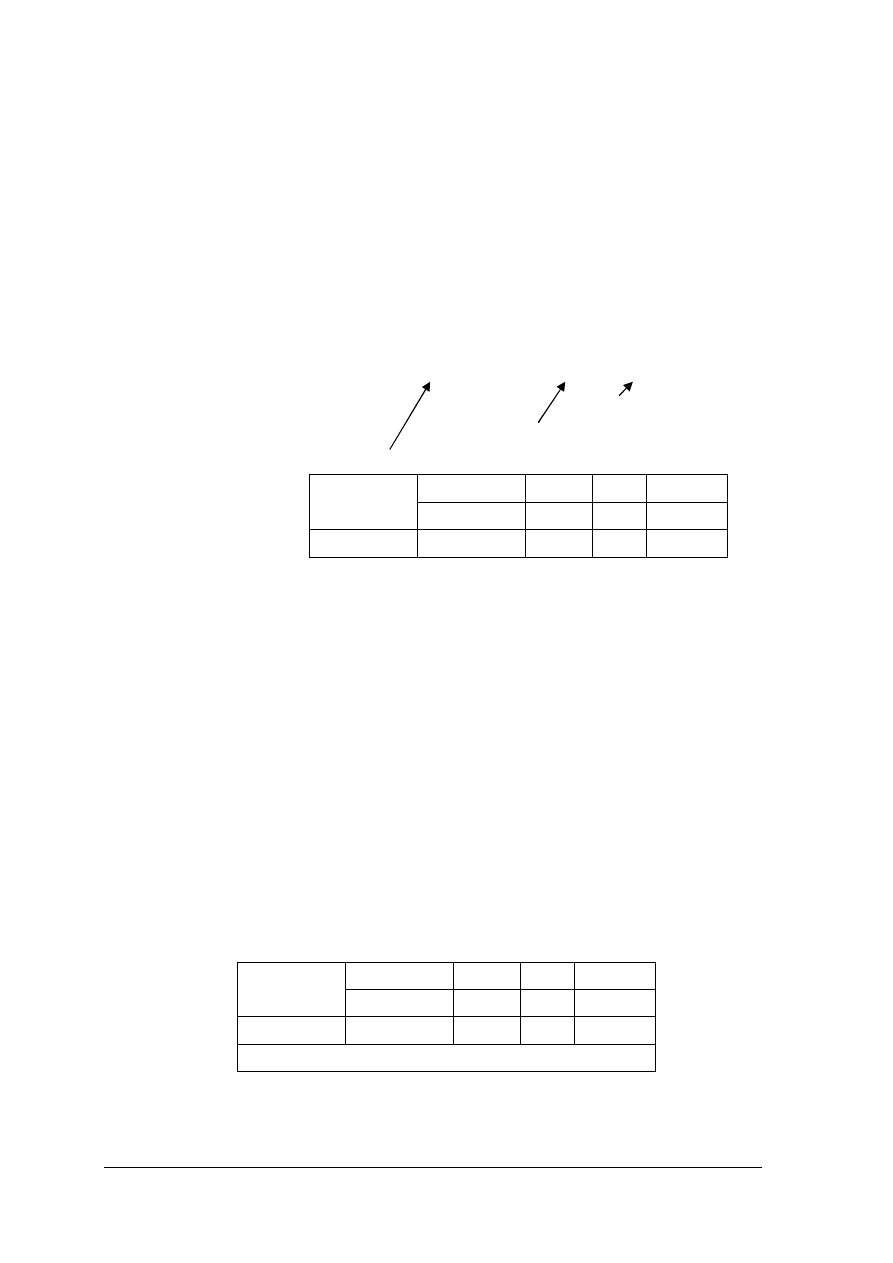

cyfra na 1 pozycji

cyfra na 2 pozycji

cyfra na 4 pozycji

1000

100

10

1

Waga cyfry

10

3

10

2

10

1

10

0

2

8

5

6

W każdym systemie pozycyjnym wyróżnić możemy: podstawę systemu P i zbiór cyfr C

i

.

Dla systemu dziesiętnego:

P = 10 C

i

= {0,1,2,3,4,5,6,7,8,9}

Ostatnia cyfra w systemie o podstawie P to P-1

Ponieważ liczby mogą być zapisywane w różnych systemach liczbowych –

w systemach o różnych podstawach - w nawiasie obok liczby zapiszemy podstawę systemu

liczbowego, w którym jest zapisana, przykładowo liczbę dziesiętną zapiszemy w postaci -

2856

(10)

a liczbę w systemie o podstawie 2 – 1101

(2)

(można inaczej powiedzieć, że jest to

liczba w systemie dwójkowym zwanym także binarnym) [3].

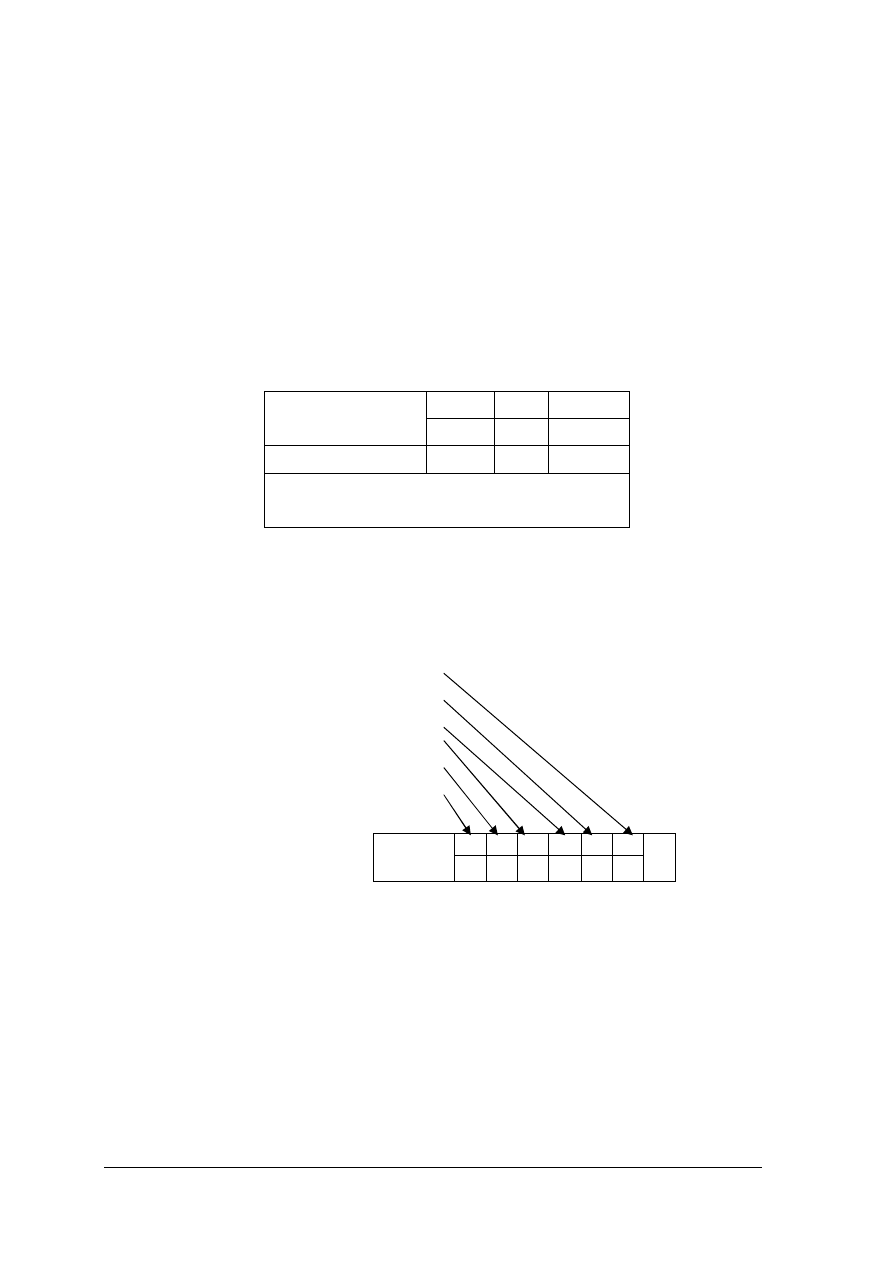

4.1.1.2. Konwersja z systemu dwójkowego na dziesiętny

Dla systemu binarnego ( dwójkowego):

P = 2 C

i

= {0,1} Pamiętaj, że ostatnia cyfra w systemie o podstawie P to P-1

Wartość liczby

1101

(2)

możemy obliczyć korzystając z tabeli wagowej dla systemu binarnego

8

4

2

1

Waga cyfry

2

3

2

2

2

1

2

0

1

1

0

1

1101

(2)

= 1*8 + 1*4 + 0*2 + 1*1 = 13

(10)

W zależności od systemu liczbowego określona liczba ma inny zapis. Proces zmiany

sposobu zapisu liczby nazywany konwersją.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

8

4.1.1.3. Konwersja z systemu szesnastkowego na dziesiętny

W praktyce do analizy działania układów cyfrowych i mikroprocesorowych stosuje się

także system o podstawie P=16 (system szesnastkowy zwany również systemem

heksadecymalnym). Korzystanie z tego systemu pozwala skrócić – zmniejszyć liczbę cyfr

w dużych liczbach. Zapis w systemie szesnastkowym stosuje się przykładowo do zapisu

adresów portów oraz adresowania komórek pamięci w systemach komputerowych.

Dla systemu szesnastkowego:

P = 16 C

i

= {0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F}

gdzie A =10, B=11, C=12, D=13, E=14, F=15

Przykład liczby w systemie szesnastkowym:

4.1.1.4. Konwersja z systemu dziesiętnego na dwójkowy

Teraz dowiesz się jak można zamienić liczbę z systemu dziesiętnego na dwójkowy.

Algorytm postępowania przedstawia poniższy przykład:

Jak zauważyłeś, liczbę dziesiętną dzielimy przez nową podstawę systemu, w tym

przypadku przez 2, z dokładnością do liczby całkowitej – bez ułamków. Powstałe reszty

zapisane w odpowiedniej kolejności tworzą zapis dwójkowy. Dzielenie kończymy, gdy

uzyskamy wynik równy 0. Korzystając z tego algorytmu możemy zamienić liczbę

z dziesiętnego systemu na inny – o dowolnej podstawie.

256

16

1

Waga cyfry

16

2

16

1

16

0

2

A

F

2AF

(16)

= 2*16

2 +

10*16

1

+ 15*16

0

2AF

(16)

= 2*256 + 10*16 + 15*1 = 687

(10)

37

(10)

: 2 = 18, reszta 1

18 : 2 = 9, reszta 0

9 : 2 = 4, reszta 1

4 : 2 = 2, reszta 0

2 : 2 = 1, reszta 0

1 : 2 = 0, reszta 1

1

0

0

1

0

1

37

(10)

=

2

5

2

4

2

3

2

2

2

1

2

0

(2)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

9

1 0111 1011

(2)

=

1

7

B

0001 0111 1011

(2)

=

↔ ↔ ↔

1 7 B

16

2

16

1

16

0

(16)

101111011

(2)

= 17B

(16)

4.1.1.5. Konwersja z systemu dziesiętnego na szesnastkowy

Sposób wykonania tej zamiany jest podobny jak poprzednio tylko tym razem dzielimy

liczbę dziesiętną przez 16.

4.1.1.6. Konwersja z systemu binarnego na szesnastkowy

Z systemu binarnego na system szesnastkowy można zamienić liczbę korzystając

z następującego algorytmu: zapis liczby w systemie dwójkowym zaczynając od przecinka

dzielimy na grupy składające się z 4 cyfr, w razie potrzeby przed pierwszą cyfrą można

dopisać zera. Każdą grupę 4 cyfr składających się z 0 i 1 zamieniamy na cyfrę szesnastkową.

4.1.1.7.

Działania na liczbach w różnych systemach

Dodawanie wykonujemy podobnie jak w systemie dziesiętnym: zaczynamy dodawać

cyfry od prawej strony i jeśli wynik jest większy od podstawy, to odejmujemy wielokrotność

podstawy, resztę zapisujemy pod kreską a wielokrotność podstawy dodajemy do sumy dwóch

kolejnych cyfr.

Odejmowanie wykonujemy podobnie: zaczynamy odejmować cyfry od prawej strony

i jeśli cyfra odjemnika jest większa niż cyfra odjemnej, to musimy wykonać pożyczkę

z pozycji wcześniejszej. Przypomnij sobie jak to się robi w systemie dziesiętnym

i przeanalizuj przykłady znajdujące się poniżej.

37

(10)

: 16 = 2 reszta 5

2 : 16 = 0 reszta 2

2

5

37

(10)

=

16

1

16

0

(16)

37

(10)

= 25

(16)

1

110001

(2)

+ 1011

111100

1

10A

(16)

+ 13F

249

1

108

(10)

+ 135

243

po pożyczce

0

1

1

2+

1 1 0 0 0 1

(2)

- 1 0 1 1

1 0 0 1 1 0

2

15+ 16+

3 0 A

(16)

- 1 3 F

1 C B

po pożyczce 2 9+ 10+

3 5 2

(10)

- 1 7 5

1 7 7

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

10

4.1.1.8. Sygnał cyfrowy

System dwójkowy nazywany jest systemem binarnym od słowa „bit”. Bitem nazywamy

elementarną jednostkę informacji, która może przyjmować wartość 0 lub 1. Ciąg 8 bitów

nazywamy bajtem.

Liczba zapisana w jednym bajcie może mieć następującą postać:

waga bitu

128=2

7

64=2

6

32=2

5

16=2

4

8=2

3

4=2

2

2=2

1

1=2

0

liczba binarna

0

0

0

1

0

1

1

1

oznaczenie bitu

b

7

b

6

b

5

b

4

b

3

b

2

b

1

b

0

MSB

LSB

Bit związany z największą wagą nazywamy najstarszym lub najbardziej znaczącym –

MSB, a bit związany z najmniejszą wagą (skrajny od prawej strony) najmłodszym lub

najmniej znaczącym – LSB.

Nasze rozważania dotyczące zapisu binarnego mają na celu wyjaśnienie jak powstaje

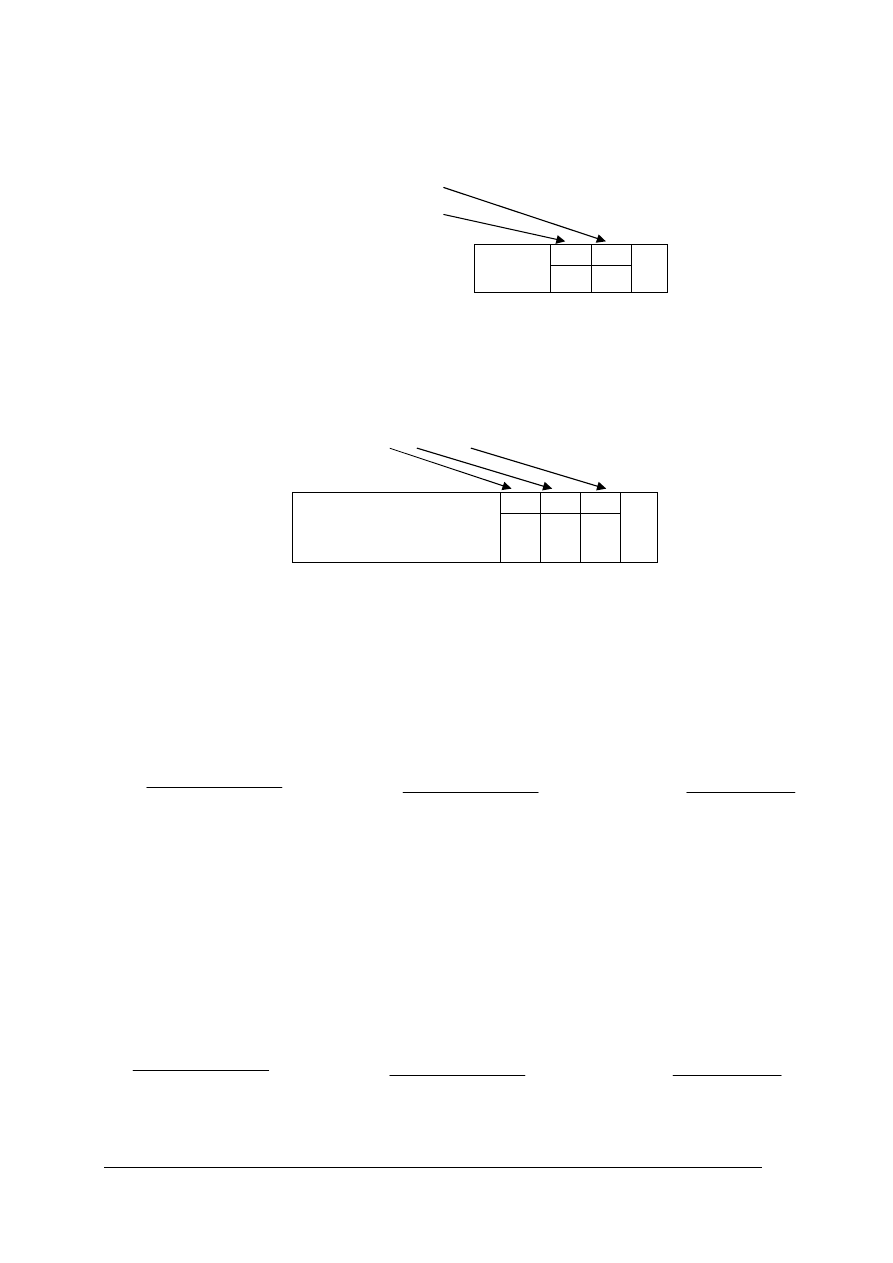

sygnał cyfrowy. Na rys.1 przedstawiony jest przebieg amplitudy dźwięku w czasie. Jest to

sygnał analogowy – ciągły w czasie.

Rys. 1. Zmiana zapisu sygnału z analogowego na cyfrowy.

Aby zapisać „cyfrowo” dźwięk wykonuje się następujące czynności:

−

mierzy się wartość amplitudy sygnału w pewnych odcinkach czasu, przykładowo 44

tysiące razy na sekundę, jest to „próbkowanie”,

−

ustala się próg próbkowania dla określenie wartości amplitudy tak, aby można ją było

przedstawić jako całkowitą wielokrotność jednostki zwanej progiem próbkowania –

proces ten nazywamy „kwantyzacją”,

A

9

8

7

6

5

4

3

2

1

0110

0101

0111

1001

0111

0100

t

6

5

9

7

4

Binarne kody próbek

P

róg

k

w

an

to

wa

n

ia

7

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

11

−

ustaloną w poprzednim kroku wartość amplitudy określoną przez liczbę wskazującą na

wielokrotność progu próbkowania zapisujemy w kodzie binarnym – proces ten

nazywamy „kodowaniem”.

Na rys. 1 pokazany jest zapis amplitudy w pewnym przedziale czasu. Załóżmy, że

dokonano w tym czasie 6 pomiarów amplitudy, a w wyniku kwantyzacji największa wartość

amplitudy wyniosła 9. Każdą, tak określoną wartość amplitudy zamieniono na postać binarną,

a do zakodowania zastosowano w tym przypadku kod binarny naturalny.

Jakość zapisu cyfrowego (jakość dźwięku) będzie zależna od tego, jaka jest częstotliwość

próbkowania – im więcej pomiarów w jednostce czasu, tym lepsza jakość oraz od progu

kwantyzacji – im mniejszy próg, tym lepiej (tym lepszy dźwięk).

Do zamiany sygnału z postaci analogowej na cyfrową wykorzystujemy układy

przetworników analogowo-cyfrowych (przetworników A/C). Sygnały cyfrowe są bardziej

odporne na zniekształcenia i można je regenerować. Dlatego też często w celu transmisji

sygnału przetwarzamy go w przetworniku A/C, aby w fazie końcowej odtworzyć sygnał

analogowy w przetworniku cyfrowo-analogowym (przetworniku C/A).

Cyfrowo zapisujemy nie tylko dźwięki, ale korzystając ze skanera można też zapisywać

cyfrowo obraz. Często korzystamy z cyfrowych aparatów fotograficznych. Wszystkie te

informacje mają postać sygnału cyfrowego, w którym rozróżniamy dwa stany stan „1” zwany

wysokim – H i stan „0” zwany niskim – L.

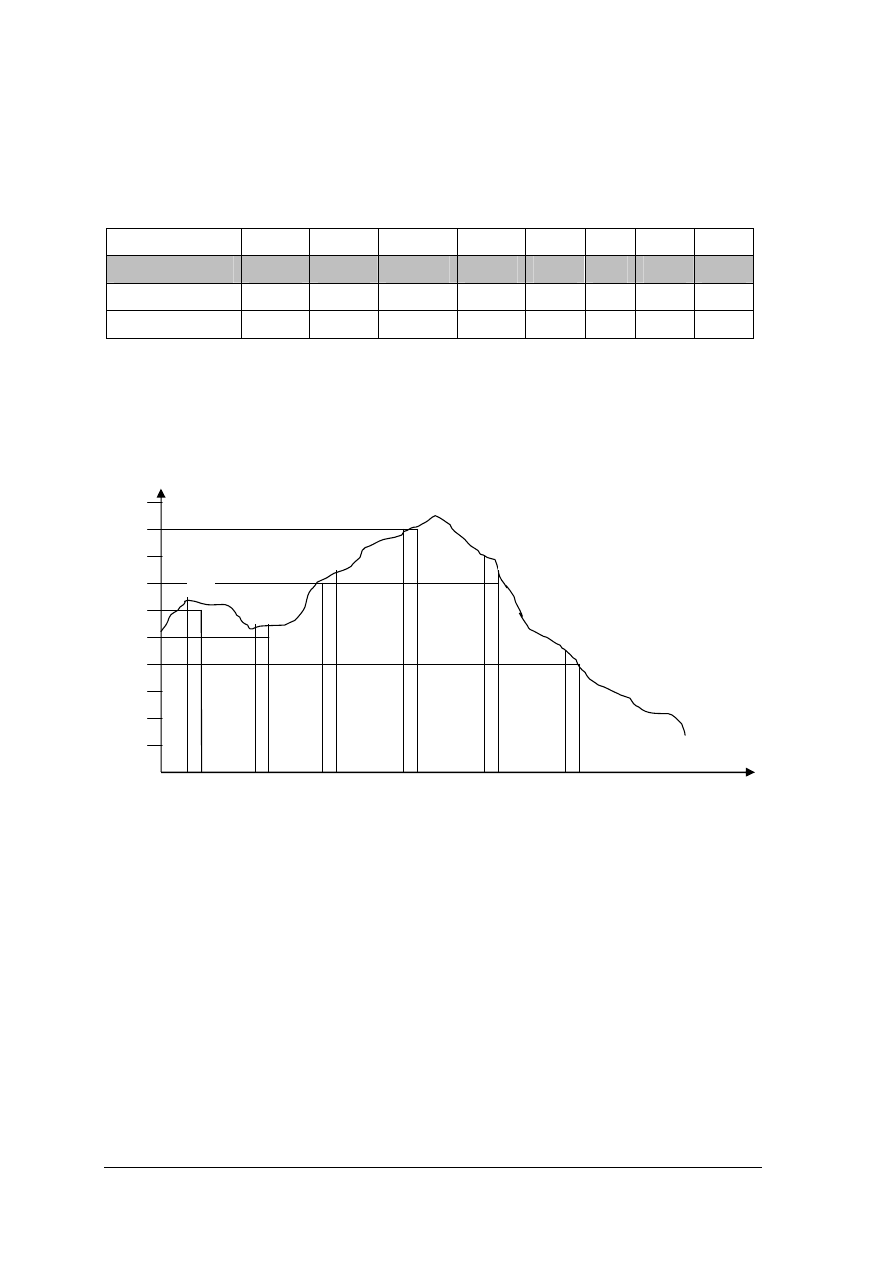

Przebieg sygnału cyfrowego może być następujący:

Rys. 2. Cyfrowa postać sygnału.

Sygnały mogą być przesyłane, wprowadzane lub wyprowadzane z układu cyfrowego

szeregowo – „bit po bicie” lub równolegle – wszystkie bity „jednocześnie”

Rys. 3. Transmisja sygnału cyfrowego: a) szeregowa, b) równoległa.

4.1.1.9. Kody binarne

Jak już wcześniej wyjaśnialiśmy, aby dokonać cyfrowego zapisu informacji analogowej

należy wykonać: próbkowanie, kwantyzację i kodowanie. Teraz zapoznasz się

z najpopularniejszymi kodami służącymi do kodowania informacji.

1

0

0

0

1

t[s]

A

[v]

0

1

0

Stan wysoki

Stan niski

01010010

01010010

0

1

0

1

0

0

1

0

1

0

1

0

0

1

a)

b)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

12

Kod binarny prosty - naturalny

Zapis w postaci naturalnego systemu dwójkowego został już wcześniej opisany. Można

za jego pomocą kodować informacje, które dadzą się zapisać w postaci liczb całkowitych bez

znaku. Kodu tego używa się na przykład do kodowania rzeczywistych adresów komórek

pamięci.

Kod BCD

Kodowanie dwójkowo-dziesiętne BCD (od angielskiego Binary Coded Decimal) polega

na zastąpieniu każdej cyfry dziesiętnej odpowiadającym jej 4-cyfrowym zapisem binarnym.

5 9 0 3

(10)

= 0101 1001 0000 0011

BCD 8421

Tabela 1. Przykład liczby dziesietnej zakodowanej kodem BCD .

5

9

0

3

(10)

0 1

0 1 1 0 0 1 0 0 0 0 0 0 1 1

BCD 8421

Kod szesnastkowy

Jeżeli podzielimy bajt na dwie czterobitowe grupy - dwa półbajty, to będziemy mogli

przedstawić je za pomocą jednej cyfry szesnastkowej. Stosowanie kodu szesnastkowego

pozwala znacznie skrócić zapis adresów binarnych lub kodów instrukcji w języku

wewnętrznym procesora.

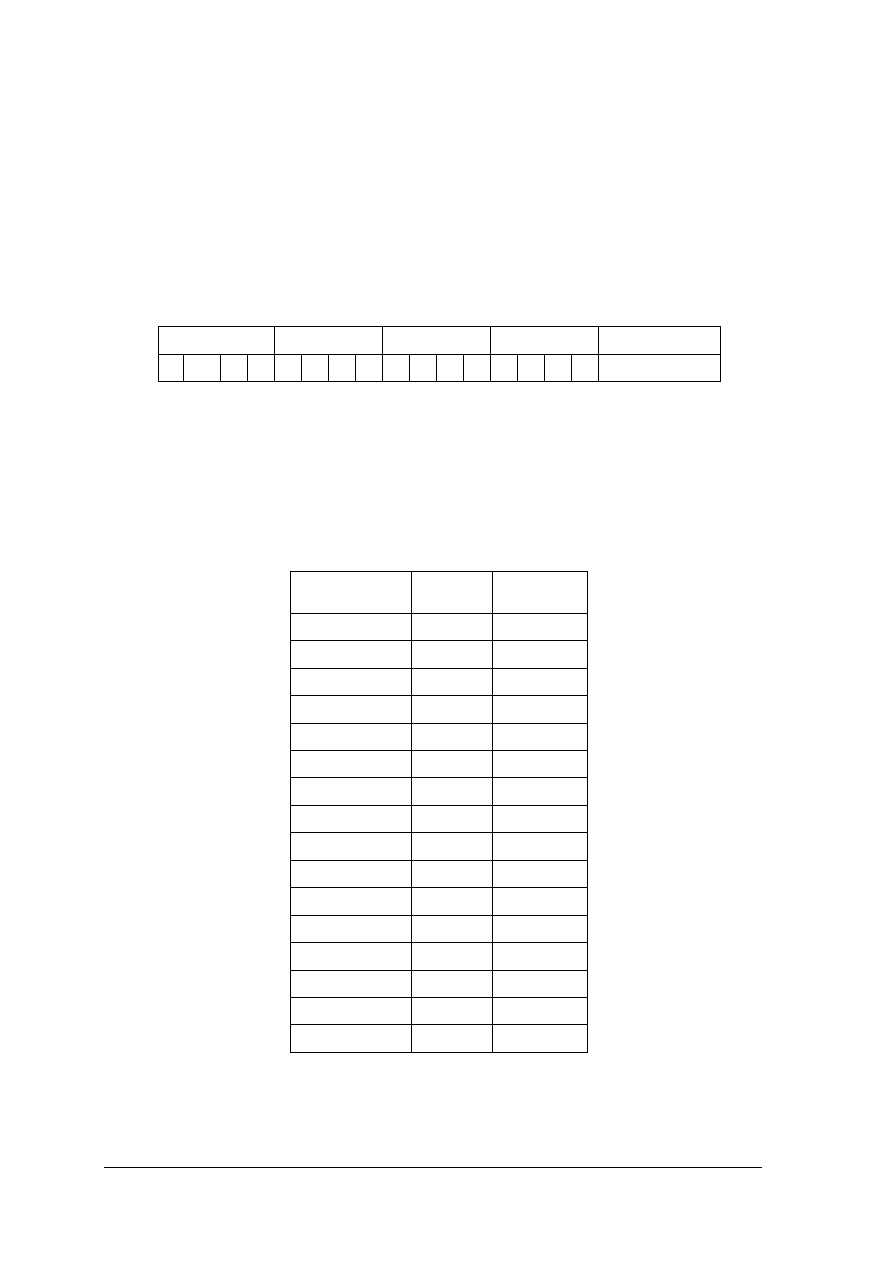

Kodowanie znacznie ułatwi Ci umieszczona poniżej tabela kodów.

Tabela 2. Tabela kodów

Cyfra

szesnastkowa

Zapis

binarny

Zapis

dziesiętny

0

0000

0

1

0001

1

2

0010

2

3

0011

3

4

0100

4

5

0101

5

6

0110

6

7

0111

7

8

1000

8

9

1001

9

A

1010

10

B

1011

11

C

1100

12

D

1101

13

E

1110

14

F

1111

15

System szesnastkowy jest bardzo zwięzły w zapisie. Bardzo proste jest przejście

z systemu binarnego na szesnastkowy i odwrotnie. W celu oznaczenia systemu można na

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

13

końcu liczby umieścić literę B – dla kodu binarnego lub H – dla kodu szesnastkowego oraz D

– dla dziesiętnego. Ta konwersja umożliwia też zamianę odwrotną.

1110

0010

B = E2 H

3

C

H =

00111100 B

E

2

0011

1100

Kody detekcyjne

W układach cyfrowych stosowane są najczęściej dwa kody detekcyjne, kody, które

umożliwiają wykrycie błędu:

1. Kod z kontrolą parzystości – do bitów stanowiących informację dodajemy jeden bit

kontrolny, którego wartość zależy od tego czy w informacji jest parzysta liczba jedynek.

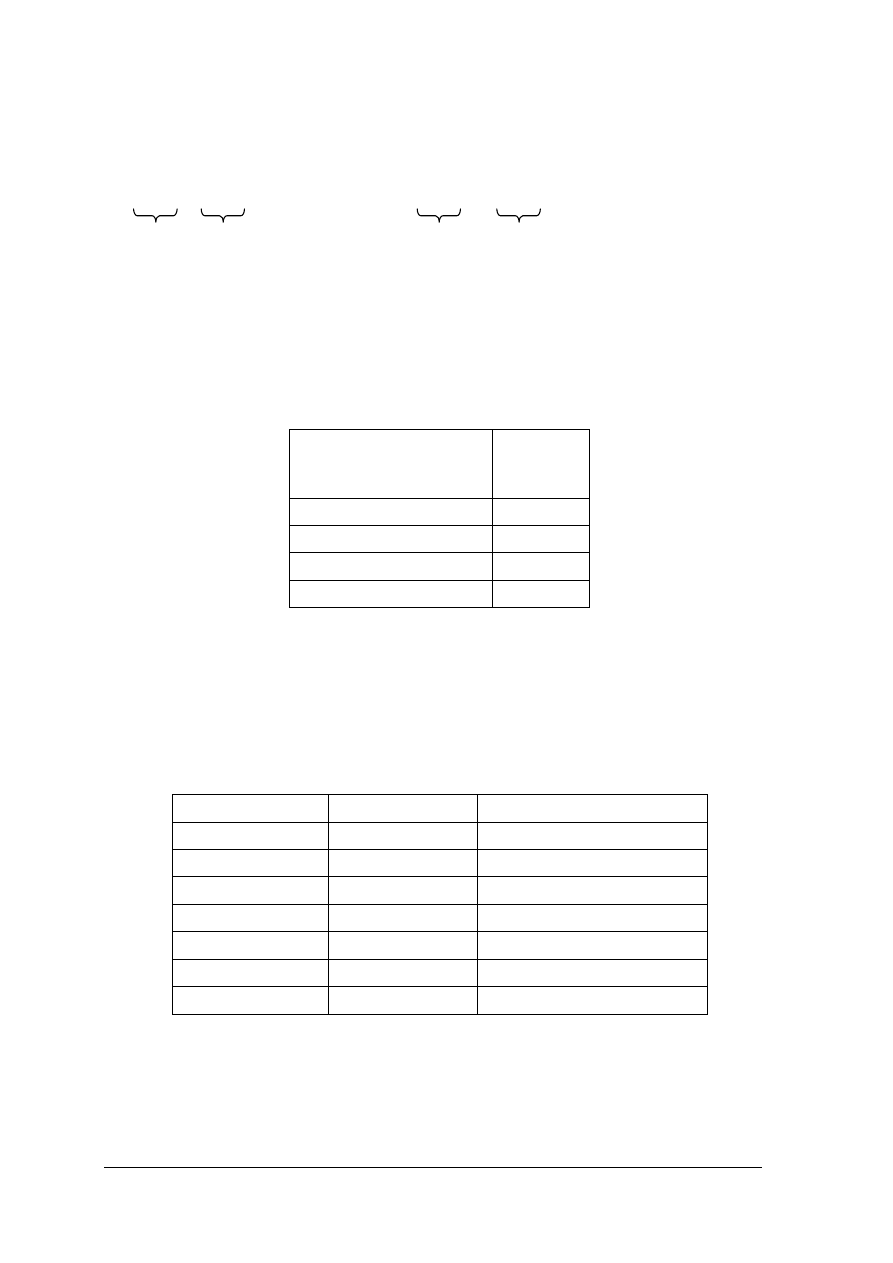

Tabela 3. Informacje uzupełnione bitem kontrolnym

Informacja

Bit

kontrolny

parzystości

1010010

1

0010001

0

1111111

1

0000000

0

W każdym słowie kodowym składającym się z informacji i bitu kontrolnego jest parzysta

liczba jedynek. Stwierdzenie nieparzystej ich liczby w informacji sygnalizuje fakt wystąpienia

błędu na drodze transmisji. Niestety przekłamanie na dwóch pozycjach pozostaje nie wykryte,

jednak zdarzenie to jest mało prawdopodobne.

2. Kod ze stałą liczbą jedynek - kod „1 z N”, gdzie N może być dowolna liczbą całkowitą.

Kod „1zN” jest najczęściej stosowanym kodem ze stałą liczbą jedynek. Znając liczbę

jedynek w słowie kodowym można łatwo wykryć błąd w transmisji.

Tabela 4. Tabela kodów „1 z 10”

Kod „1 z 10”

Zanegowany kod „1z 10”

Cyfra/ waga kodu

9 8 7 6 5 4 3 2 1 0

9 8 7 6 5 4 3 2 1 0

0

0 0 0 0 0 0 0 0 0 1

1 1 1 1 1 1 1 1 1 0

1

0 0 0 0 0 0 0 0 1 0

1 1 1 1 1 1 1 1 0 1

2

0 0 0 0 0 0 0 1 0 0

1 1 1 1 1 1 1 0 1 1

....

..........................

8

0 1 0 0 0 0 0 0 0 0

1 0 1 1 1 1 1 1 1 1

9

1 0 0 0 0 0 0 0 0 0

0 1 1 1 1 1 1 1 1 1

Kod ASCII

W postaci binarnej można zapisywać nie tylko liczby, ale i dowolne znaki. Wystarczy

ustawić je w kolejności i każdemu przypisać numer - kod znaku. Litery ustawiono

w porządku alfabetycznym, kolejność innych znaków ustalono tworząc w ten sposób

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

14

standard. Najbardziej znany jest standard w skrócie określany ASCII. Kod znaku jest

zapisywany w jednym bajcie. Tabelę tego kodu znajdziesz w literaturze [3, s. 325].

4.1.2. Pytania sprawdzające

Odpowiadając na pytania sprawdzisz, czy jesteś przygotowany do wykonania ćwiczeń.

1. Czym się charakteryzują pozycyjne systemy liczbowe?

2. Jaka jest podstawa systemu binarnego i jakie cyfry mogą występować w binarnym

zapisie liczby?

3. Jaka jest podstawa systemu szesnastkowego i jakie cyfry mogą występować

w zapisie liczby w tym systemie?

4. Jak dokonać konwersji liczby z sytemu binarnego na system dziesiętny i odwrotnie?

5. Jak wykonać dodawanie liczb zapisanych w systemie binarnym?

6. Jak dokonać konwersji liczby z sytemu dziesiętnego na system szesnastkowy

i odwrotnie?

7. Jak dokonać konwersji liczby z sytemu binarnego na system szesnastkowy

i odwrotnie?

8. Jakie procesy pozwalają przekształcić sygnał analogowy na postać cyfrową?

9. Jakie czynniki wpływają na jakość sygnału cyfrowego?

10. Gdzie znajduje zastosowanie kod binarny i heksadecymalny?

11. Do czego służą kody detekcyjne?

12. Do czego służy kod ASCII?

13. Jakie korzyści wynikają ze stosowania przetworników A/C i C/A?

14. W jakich urządzeniach stosuje się przetwarzanie informacji z postaci analogowej na

cyfrową i odwrotnie?

15. Od czego zależy jakość przetwarzanego sygnału, uzasadnij to na przykładach?

4.1.3. Ćwiczenia

Ćwiczenie 1

Wykonaj konwersję:

- z systemu dwójkowego na dziesiętny następujących liczb:

a) 1010

(2)

b) 10101

(2)

c) 1110101

(2)

- z systemu dziesiętnego na dwójkowy następujących liczb:

d) 33

(10)

e) 10

(10)

f) 121

(10)

- z systemu dziesiętnego na szesnastkowy następujących liczb:

g) 33

(10)

h) 13

(10)

i) 121

(10)

-

z systemu szesnastkowego na dziesiętny następujących liczb:

j) 21

(16)

k) E1

(16)

- z systemu szesnastkowego na binarny następujących liczb:

l) 91

(16)

m) E1

(16)

-

z systemu dwójkowego na dziesiętny następujących liczb:

n) 10101

(2)

o) 11101011

(2)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

15

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z algorytmem wykonania konwersji liczb zapisanych w różnych systemach

(Materiał nauczania pkt.4.1.1),

2) dokonać konwersji krok po kroku,

3) sprawdzić poprawność wykonanych działań poprzez wykonanie konwersji odwrotnej.

Jeśli masz trudności zwróć się o pomoc do nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

literatura[3].

Ćwiczenie 2

Wykonaj następujące działania arytmetyczne:

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z algorytmem wykonania działań na liczbach w różnych systemach

(Materiał nauczania pkt.4.1.1),

2) wykonać działanie krok po kroku zwracając szczególną uwagę na nową podstawę

systemu, w którym wykonywane jest działanie,

3) sprawdzić poprawność wykonanych działań poprzez wykonanie działania odwrotnego, –

jeśli masz trudności zwróć się o pomoc do nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania, kalkulator,

−

poradnik dla ucznia,

−

literatura [3].

Ćwiczenie 3

Zakoduj liczbę dziesiętną 53 w następujących kodach:

a) w kodzie binarnym,

b) w kodzie BCD

8421,

c) w kodzie heksadecymalnym.

Sposób wykonania ćwiczenia

Aby wykonać te ćwiczenie, powinieneś:

1) zapoznać się z tabelami odpowiednich kodów (Materiał nauczania pkt.4.1.1),

2) wykonać kodowanie,

3) sprawdzić poprawność kodowania, – jeśli masz trudności zwróć się o pomoc do

nauczyciela.

b) 1 1 1 1 0 1

(2)

- 1 0 1 1

a) 1 1 0 0 0 1

(2)

+ 1 0 1 1

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

16

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

literatura [3].

Ćwiczenie 4

Zakoduj swoje imię korzystając z tabeli kodów ASCII zapisując kod binarny każdej litery

i jej odpowiednik w kodzie heksadecymalnym.

Kod binarny każdej litery uzupełnij o bit parzystości.

Sposób wykonania ćwiczenia

Aby wykonać te ćwiczenie, powinieneś:

4) zapoznać się z tabelami odpowiednich kodów (Materiał nauczania pkt.4.1.1),

5) wykonać kodowanie,

6) sprawdzić poprawność kodowania, – jeśli masz trudności zwróć się o pomoc do

nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

literatura [3].

4.1.4. Sprawdzian postępów

Tak Nie

Czy potrafisz:

1) zapisać liczbę w systemie dwójkowym i szesnastkowym?

¨

¨

2) dokonać konwersji z systemu dwójkowego na dziesiętny?

¨

¨

3) dokonać konwersji z systemu szesnastkowego na dziesiętny?

¨

¨

4) dokonać konwersji z systemu dziesiętnego na dwójkowy?

¨

¨

5) dokonać konwersji z systemu dziesiętnego na szesnastkowy?

¨

¨

6) dokonać konwersji z systemu dwójkowego na szesnastkowy?

¨

¨

7) dokonać konwersji z systemu szesnastkowego na dwójkowy?

¨

¨

8) zapisać liczbę w kodzie binarnym, heksadecymalnym, BCD

8421

?

¨

¨

9) wykonać kodowanie informacji w kodzie ASCII?

¨

¨

10) wykonać dodawanie i odejmowanie liczb w systemie binarnym?

¨

¨

11) określić procesy umożliwiające zamianę sygnału analogowego

na postać cyfrową?

¨

¨

12) ocenić wpływ parametrów przetwarzania A/C na jakość

odtwarzanego sygnału analogowego?

¨

¨

13) wskazać przykłady praktycznego zastosowania przetworników

A/C i C/A

¨

¨

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

17

4.2. Synteza układów kombinacyjnych

4.2.1. Materiał nauczania

4.2.1.1. Algebra Boole’a

Układem kombinacyjnym nazywamy układ logiczny, w którym stan na wyjściach zależy

wyłącznie od stanu na wejściach – od kombinacji stanów na wejściach.

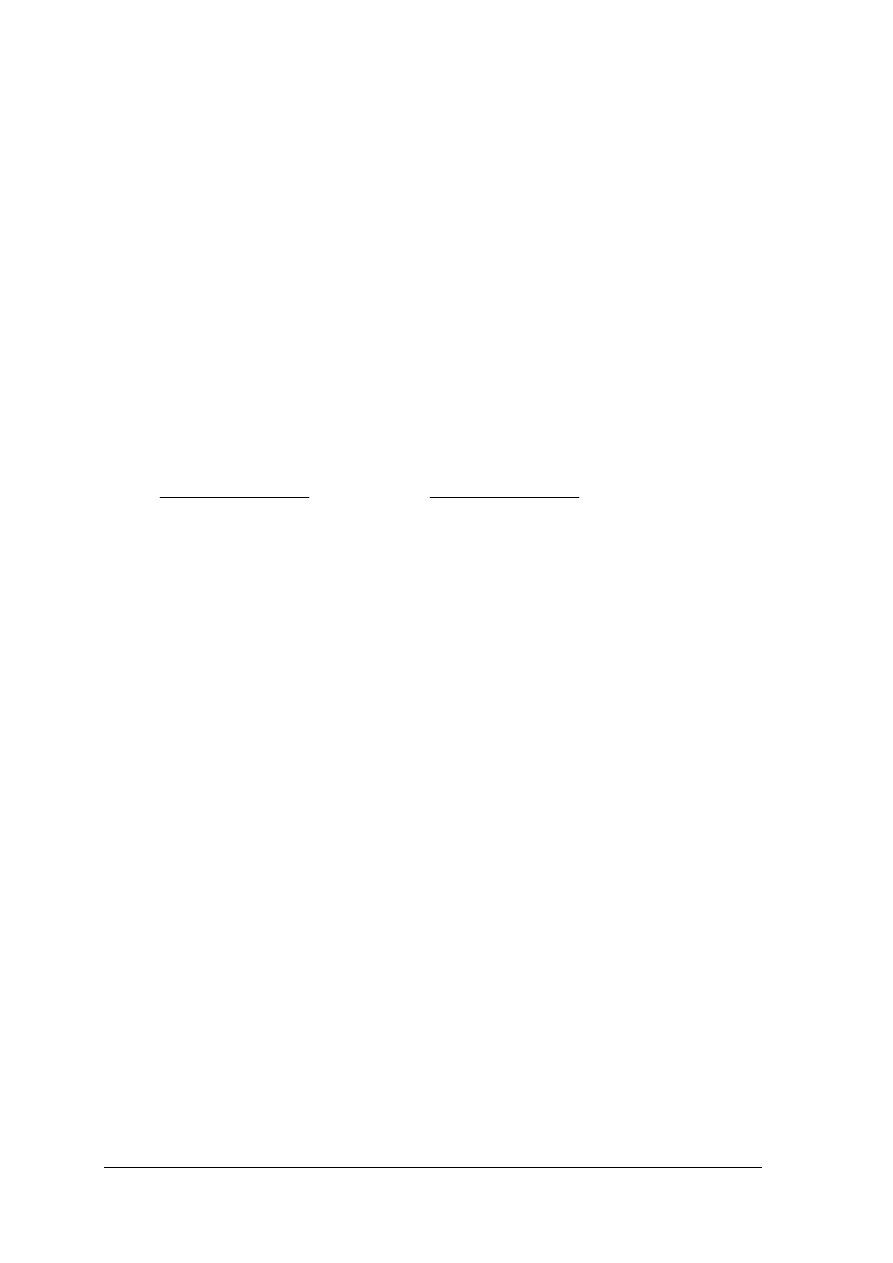

Rys. 4. Układ kombinacyjny.

Układy logiczne działają zgodnie z aksjomatami algebry Boole’a. Aksjomat to

twierdzenie, które przyjmujemy za prawdziwe bez udowadniania. Algebra ta posługuje się

tylko dwoma wielkościami: „1” logiczna - prawda i „0” logiczne – fałsz. Na dowolnych

zmiennych logicznych, które mogą mieć wartość 1 lub 0 można wykonać następujące

działania logiczne: dodawanie logiczne, mnożenie logiczne i negację. Dla ułatwienia

działania te będziemy oznaczać podobnie jak w algebrze, którą posługujesz się dotychczas:

dodawanie logiczne – znak „+”, mnożenie logiczne – znak „ ∙ ”. Negację zmiennej A

zaznaczamy A’ lub Ā. Pamiętaj, że dodawanie arytmetyczne to inne działanie niż dodawanie

logiczne i wyniki tych działań też mogą być różne. Zapoznaj się z podstawowymi

twierdzeniami algebry Boole’a:

A + A + A + ∙∙∙ + A = A

A ∙ A ∙ A ∙∙∙ A = A

A + 1 = 1

A ∙ 1 = A

A + 0 = A

A ∙ 0 = 0

A + A’= 1

A ∙ A’ = 0

Prawo podwójnej negacji A’’ = A

Prawa de Morgana:

(A + B )’ = A’∙ B’

(A ∙ B )’ = A’+ B’

Pozostałe prawa znajdziesz w literaturze [3, 6]. Korzystając z tych aksjomatów będziesz mógł

w sposób uproszczony opisywać działanie układów cyfrowych.

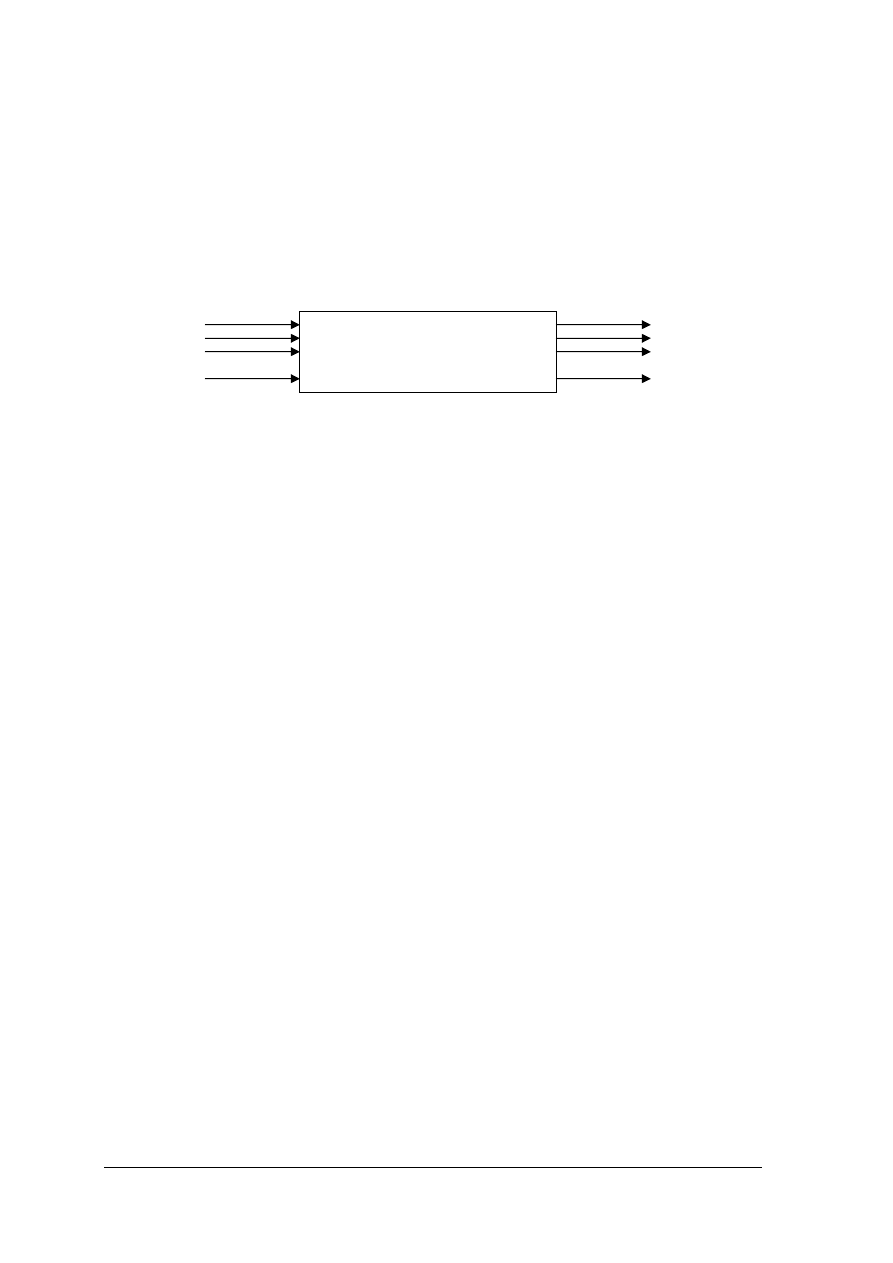

4.2.1.2. Bramki logiczne – funktory

Układy, które realizują funkcje logiczne nazywamy popularnie bramkami. Tabela 6

przedstawia informacje o trzech podstawowych bramkach logicznych: AND, OR, NOT. A i B

są wejściami, na które podawane są sygnały logiczne „0” lub „1”. Jaki sygnał będzie na

wyjściu bramki, przy każdej z czterech możliwych kombinacji sygnałów wejściowych,

przedstawia tabela działania.. Ostania kolumna tabeli 6 zawiera obwody zastępcze na

przełącznikach, które ułatwią Ci zrozumienie działania odpowiednich bramek. Przeanalizuj te

układy zakładając, że jeśli żarówka się świeci to odpowiada to F=1, dla zestyków zwiernych

przyjmujemy, że zestyk w stanie otwartym odpowiada stanowi logicznemu „0”, zestyk

Układ kombinacyjny

Wej

śc

ia

W

yj

śc

ia

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

18

w stanie zamkniętym odpowiada stanowi logicznemu „1”. Dla zestyków rozwiernych

przyjmujemy odwrotnie.

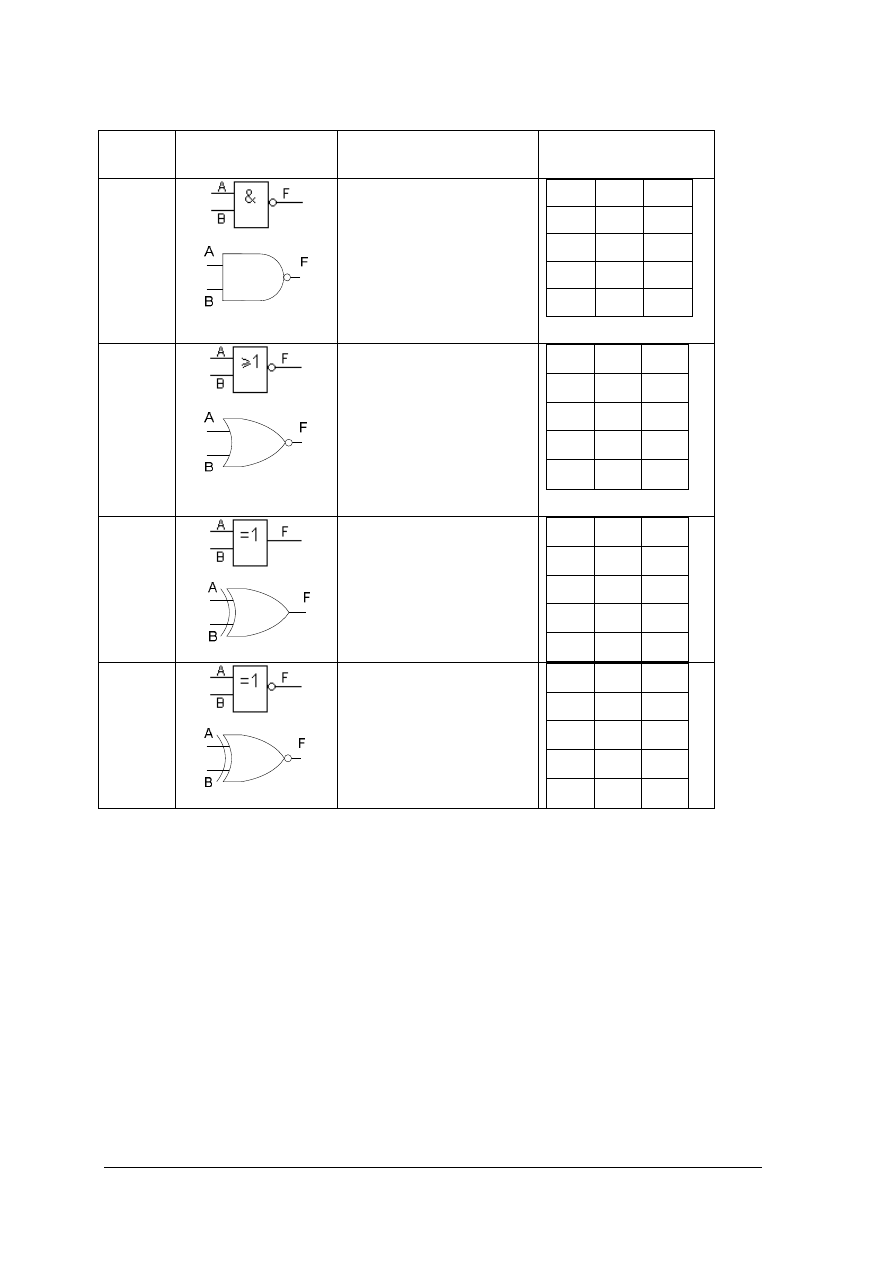

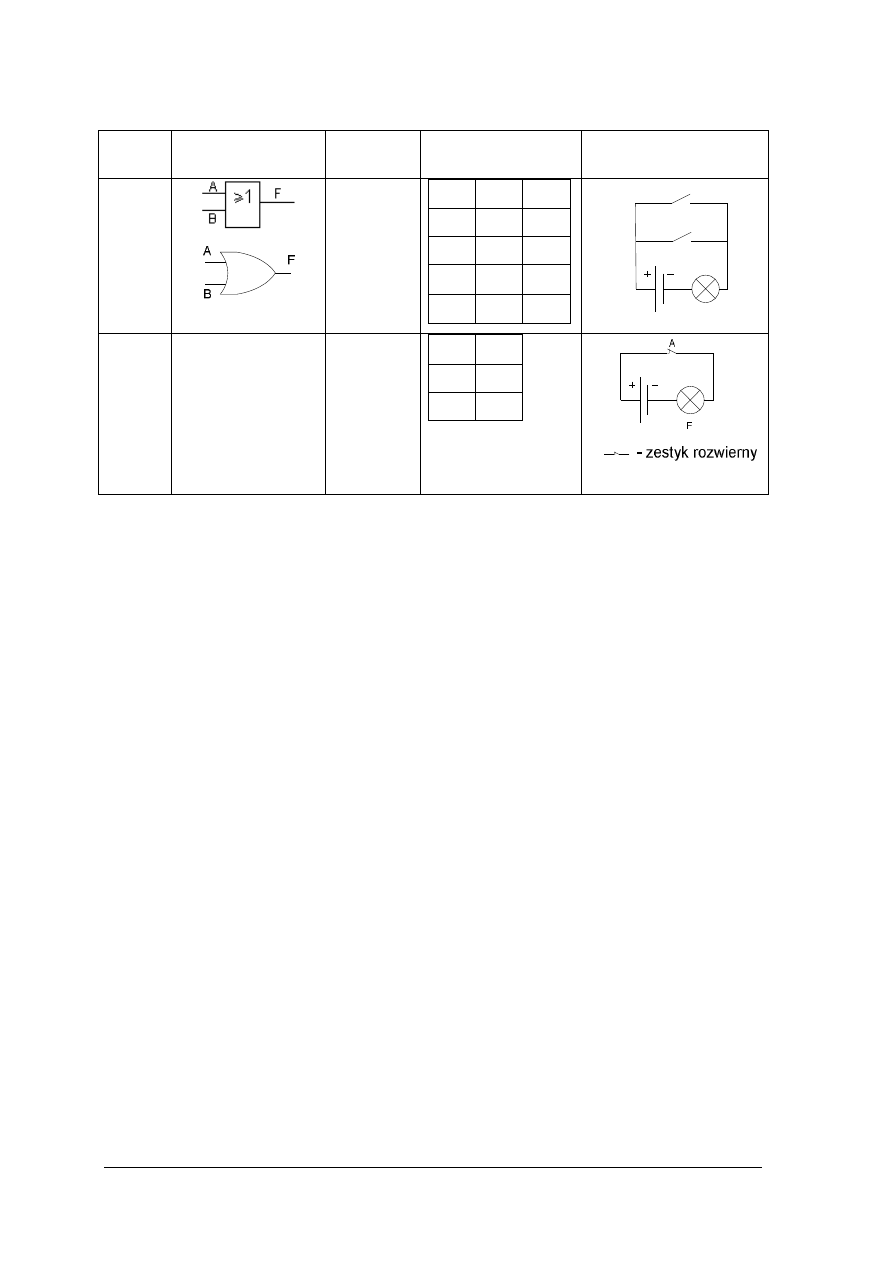

Tabela 6. Podstawowe bramki logiczne

Nazwa

bramki

Symbol graficzny

Funkcja

Tabela działania

Realizacja

na

przełącznikach

AND

F = A ∙ B

mnożenie

logiczne

(iloczyn

logiczny)

A

B

F

0

0

0

0

1

0

1

0

0

1

1

1

OR

F = A + B

dodawanie

logiczne

(suma

logiczna)

A

B

F

0

0

0

0

1

1

1

0

1

1

1

1

A

B

F

NOT

F = A’

negacja

A

F

0

1

1

0

Za pomocą bramek AND, OR, NOT można zrealizować dowolny układ logiczny. Tworzą

one układ funkcjonalnie pełny.

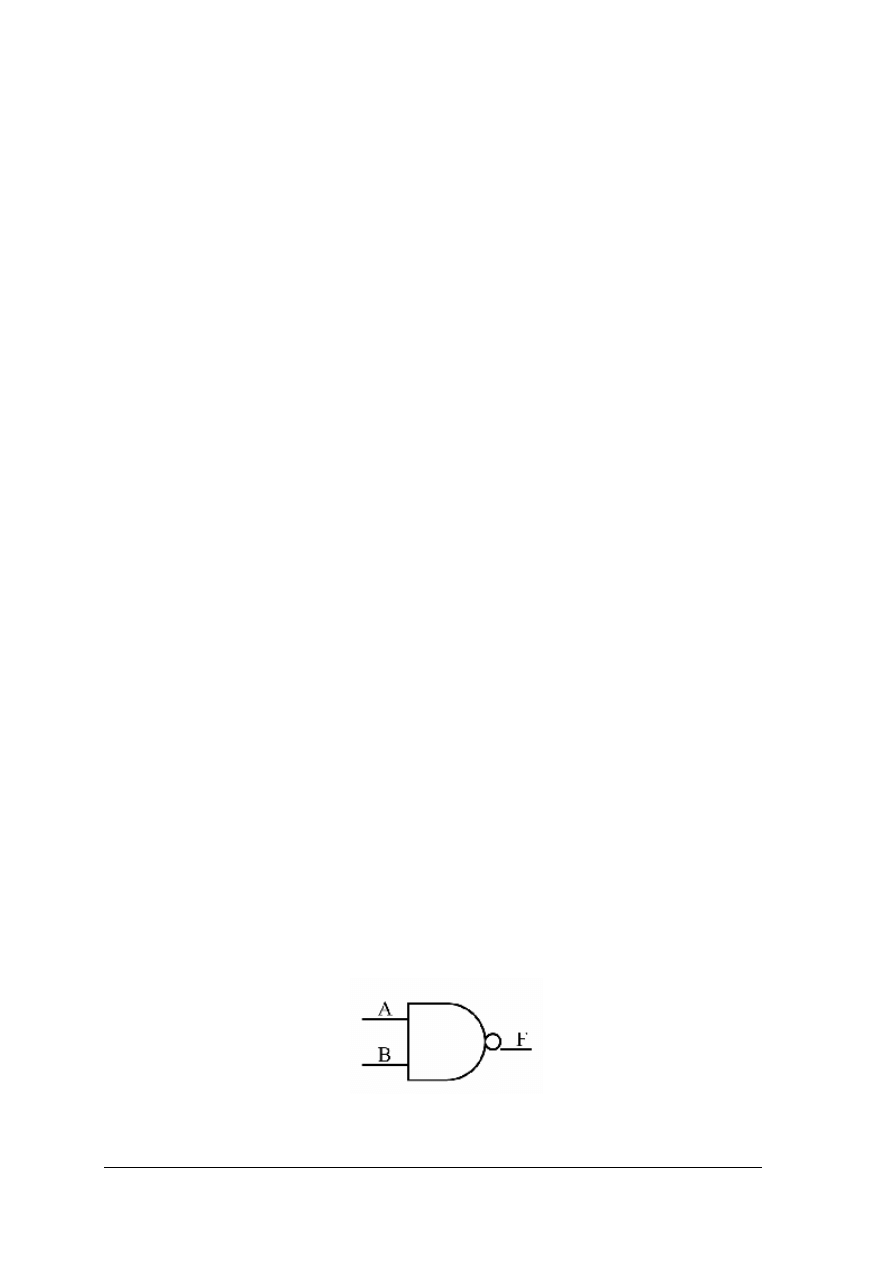

W praktycznym zastosowaniu znajdują się jeszcze inne bramki logiczne. Bramki NAND

i NOR są bramkami uniwersalnymi, co oznacza, że za pomocą wyłącznie jednego typu tych

bramek, można zrealizować każdy układ. Każda z tych bramek też tworzy układ

funkcjonalnie pełny.

Bramki wykonujące tę samą funkcję logiczną mogą różnić się dodatkowymi

parametrami. Bardzo powszechne w zastosowaniu są bramki NAND z otwartym kolektorem,

posiadające możliwość regulacji prądu na wyjściu a poprzez to posiadające większą

obciążalność. Bramki NAND z przerzutnikiem Schmidta charakteryzują się różnymi

napięciami przełączania w zależności od tego czy napięcie wejściowe wzrasta czy maleje [3].

Kolejną grupą są bramki trójstanowe, w których obok stanów „1” i „0” pojawia się stan

wysokiej impedancji HZ – stan, w którym rezystancja bramki > 10

9

Ω. Bramki transmisyjne

obok pracy trójstanowej mają możliwość transmisji dwukierunkowej zarówno sygnałów

cyfrowych jak i analogowych. Więcej informacji na temat tych bramek znajdziesz

w literaturze [3].

Dodatkowe bramki to ExOR i ExNOR, także bardzo często stosowane w praktyce.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

19

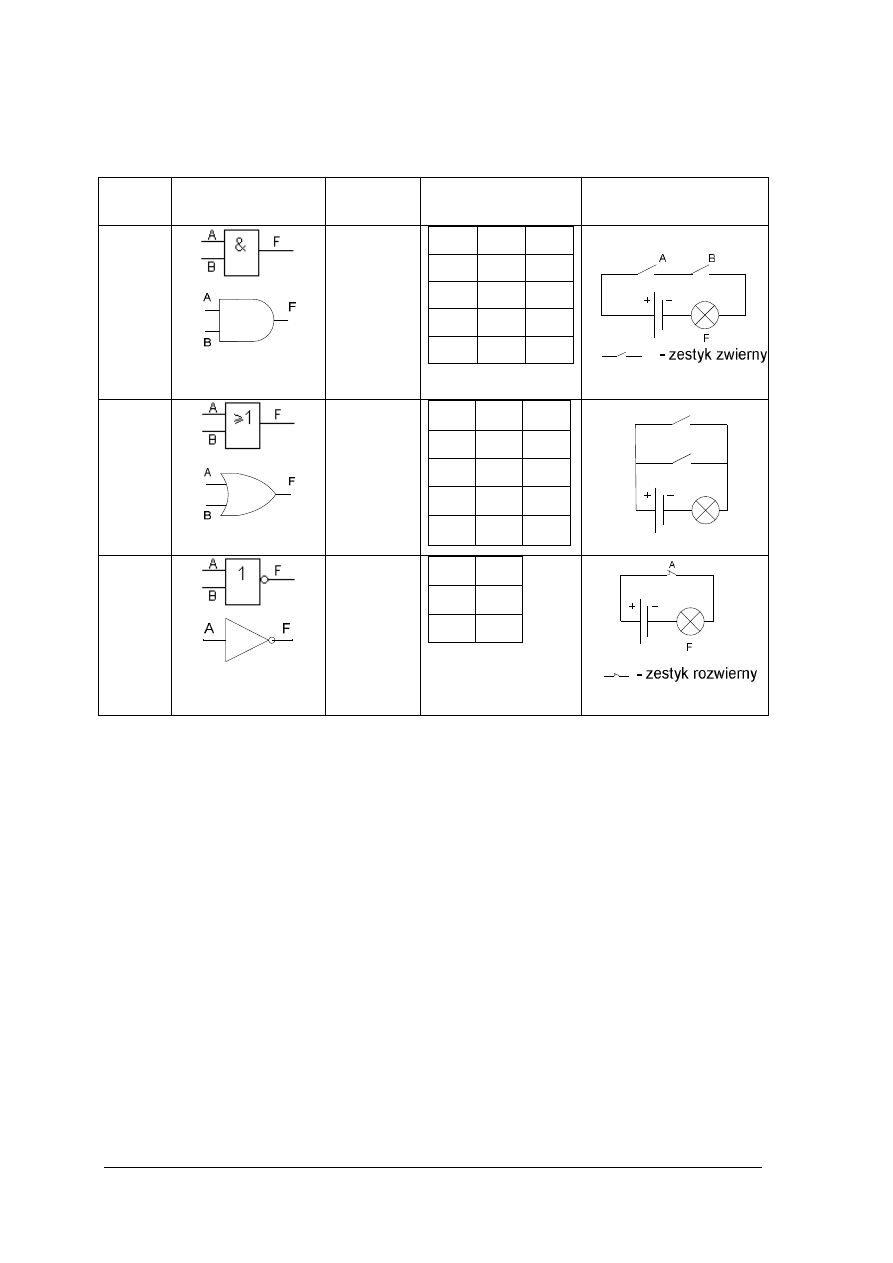

Tabela 7.

Nazwa

bramki

Symbol graficzny

Funkcja

Tabela działania

NAND

F=(A ∙ B)’

Negacja iloczynu

A

B

F

0

0

0

0

1

0

1

0

0

1

1

1

NOR

F=(A+B)’

Negacja sumy

A

B

F

0

0

0

0

1

1

1

0

1

1

1

1

ExOR

F = A’B + AB’

A

B

F

0

0

0

0

1

1

1

0

1

1

1

0

ExNOR

F = A’B’ + AB

A

B

F

0

0

1

0

1

0

1

0

0

1

1

1

Uwaga: W tabeli przedstawiono dwa symbole graficzne każdej bramki – górny, według

normy PN-IEC 617-12 :1995, - dolny, według norm amerykańskich. Oba rodzaje symboli

stosowane są w Polsce.

4.2.1.3. Opis działania układów logicznych

Działanie układu logicznego można opisać za pomocą: opisu słownego, tabeli działania

zwanej też tabelą prawdy, funkcji logicznej i schematu logicznego.

Opis słowny zawiera informacje o ilości wejść i wyjść, znaczeniu „0” i „1” na wejściu

i wyjściu układu oraz jak ma się zachować układ we wszystkich możliwych sytuacjach.

Komentarz słowny możemy zapisać symbolicznie w postaci tabeli działania (tabeli prawdy).

Rozważymy to na przykładzie dwuwejściowej bramki AND – jej działanie opisuje

stwierdzenie: bramka AND ma na wyjściu sygnał logiczny o wartości „1” tylko wtedy, gdy na

obu wejściach jest stan „1”. W tabeli 6 znajdziesz zapis tego komentarza w postaci tabeli

działania oraz funkcji logicznej.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

20

Układ kombinacyjny zwykle jest bardziej złożony i składa się z wielu bramek logicznych

– zapis graficzny sposobu powiązań pomiędzy tymi bramkami nazywamy schematem

logicznym. Analiza działania układów logicznych będzie łatwiejsza, gdy spróbujesz sam

zaprojektować prosty układ.

4.2.1.4. Projektowanie układów logicznych można podzielić na następujące kroki:

1. Wyobraź sobie działanie projektowanego układu. Określ liczbę wejść i wyjść.

2. Zapisz działanie układu w postaci „tabeli prawdy”, sprawdź czy uwzględniłeś wszystkie

możliwe kombinacje sygnałów wejściowych. Liczba kombinacji (K) zależy od liczby

wejść (N) w układzie i wynosi K = 2

N

. Dla układu, który ma dwa wejścia można

utworzyć 4 kombinacje – zobacz tabele działania dla dwuwejściowych bramek

logicznych [Tabela 6 i 7].

3. Na podstawie tabeli wypisz funkcję logiczną, która opisuje działanie projektowanego

układu,

a) pokreśl w tabeli wszystkie wiersze, dla których wartość funkcji na wyjściu jest

równa „1”,

b) każdy podkreślony wiersz zapisz jako iloczyn zmiennych wejściowych (A, B, C, ..)

w taki sposób, że jeśli zmienna jest równa 0 to zapisujemy ją z negacją –

przykładowo A’ a jeśli jest równa 1 to bez negacji – A,

c) zapisz funkcji jest sumą tych iloczynów.

4. Zapisz funkcję w najprostszej postaci. Możesz zastosować w tym celu prawa algebry

Boole’a lub inną metodę minimalizacji. Jedną z metod minimalizacji jest metoda

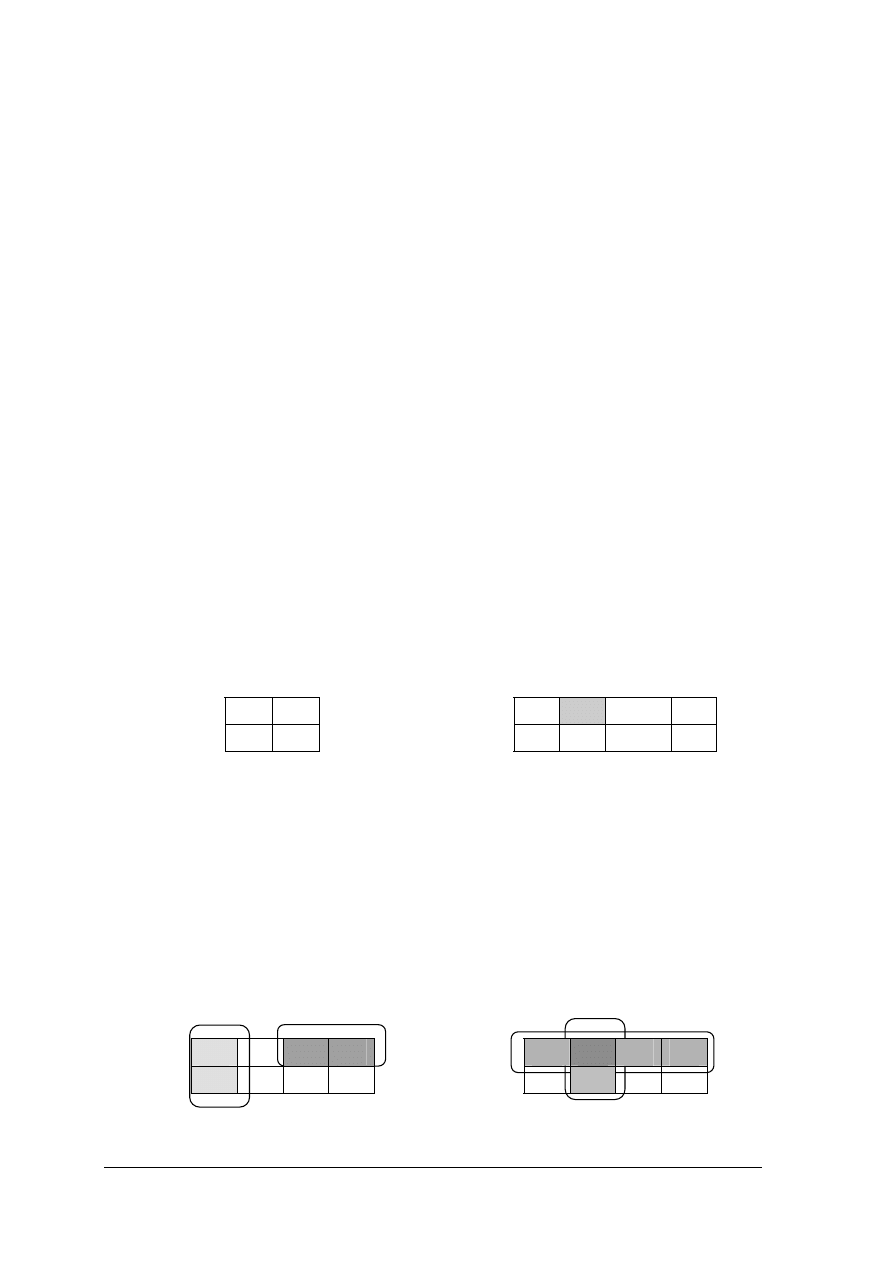

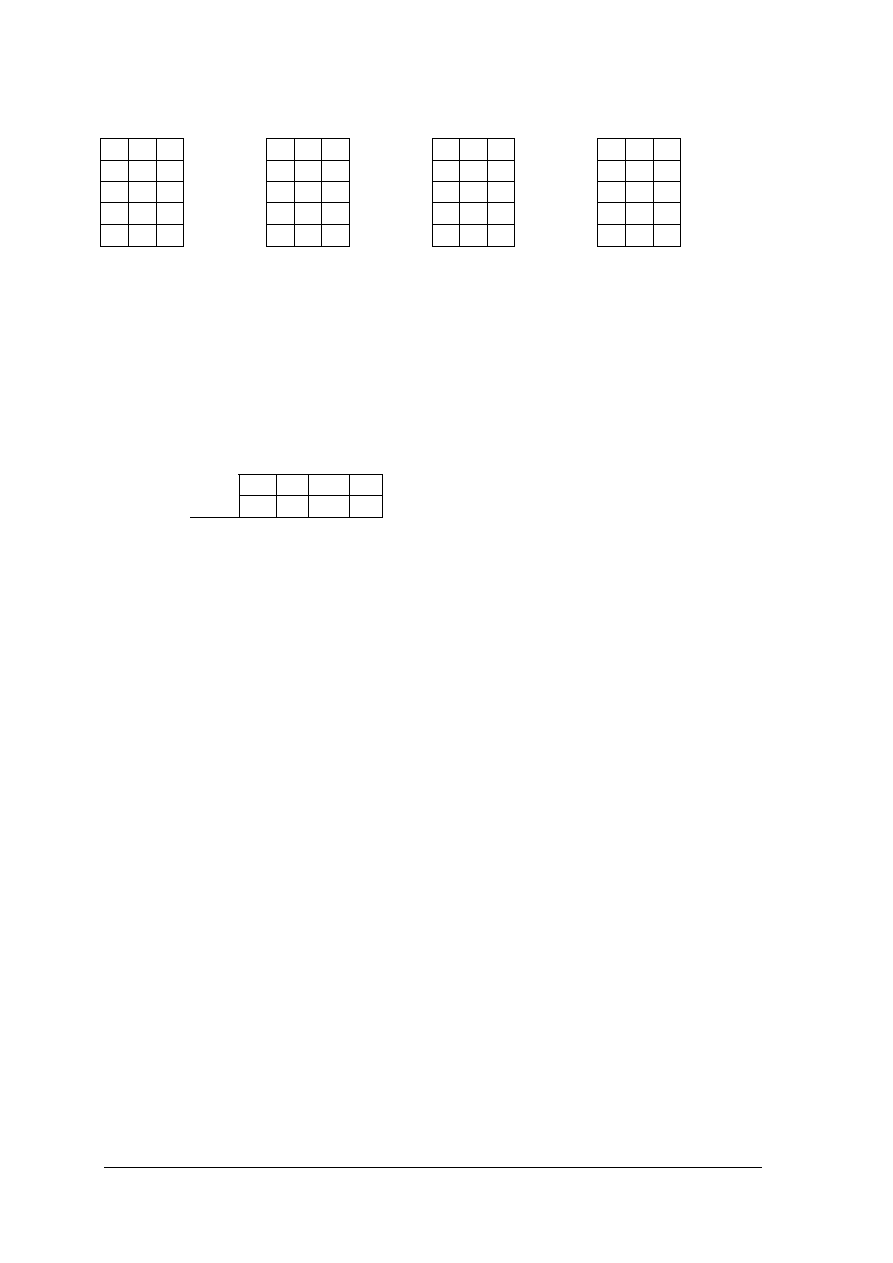

Karnaugh’a. Aby uprościć funkcję metodą Karnaugh’a:

a) wybierz odpowiednią tablicę minimalizacyjną – dla dwóch, trzech lub więcej

zmiennych wejściowych - tyle ile zmiennych ma funkcja, którą chcesz uprościć.

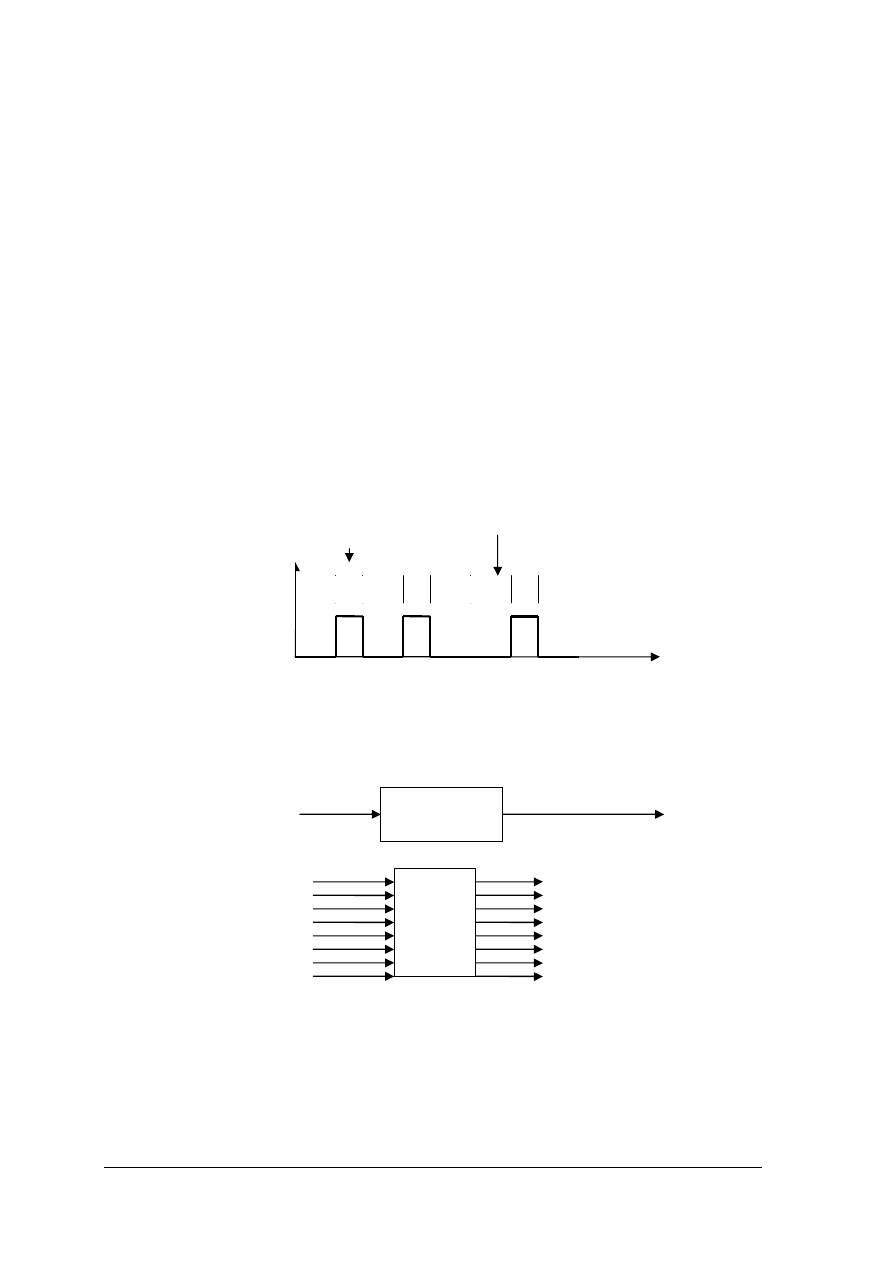

Rys. 5.Tablice minimalizacyjne a) dla funkcji dwóch zmiennych b) dla funkcji trzech zmiennych.

Tablice minimalizacyjne dla większej liczby zmiennych znajdziesz w literaturze [3,6]

b) wpisz do wybranej tablicy wartości funkcji na wyjściu,

Przykład: w zacieniowane pole tablicy (Rys.5b) należy wpisać wartość funkcji

trzywejściowej F(A,B,C) dla następującej kombinacji sygnałów wejściowych A=0,

B=0 i C=1

c) zaznacz obszary w tablicach składające się z sąsiadujących jedynek, których liczba

jest potęgą dwójki: 2

0

=1, 2

1

=2, 2

2

=4, ... staraj się utworzyć jak największe obszary,

Popatrz na przykłady zaznaczonych obszarów w tablicach poniżej (Rys.6).

A/BC 00

01

11

10

b)

A/BC 00

01

11

10

0

1

0

1

1

0

1

1

1

1

1

1

0

1

1

1

0

1

0

0

Rys. 6. Tablice minimalizacyjne z zaznaczonymi obszarami do minimalizacji.

a) dla funkcji dwóch zmiennych, b) dla funkcji trzech zmiennych.

B=0

B=1

b)

BC

BC

BC

BC

A\B 0

1

A\BC 00

01

11

10

A=0

0

A=1

1

F(111)

Tablica dla F (AB)

Tablica dla F(ABC)

a

)

a)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

21

Jedynka wyróżniona najciemniejszym wypełnieniem w prawej tablicy należy

jednocześnie do dwóch obszarów: poziomego, składającego się z czterech jedynek

i pionowego, składającego się z dwóch jedynek. Więcej informacji na temat zaznaczania

obszarów minimalizacyjnych znajdziesz w literaturze [3].

d)

z każdego zaznaczonego obszaru zapisz iloczyn zmiennych wejściowych (ABC),

które w całym obszarze nie zmieniają wartości;

W lewej tablicy (Rys.5) z obszaru składającego się z dwóch jedynek otrzymalibyśmy

B’C’, – ponieważ dla całego obszaru B=0 i C=0. Dla obszaru składającego się z

czterech jedynek w prawej tablicy (Rys.5) otrzymamy A’, ponieważ A w całym

obszarze nie zmienia wartości i jest równe „0”. Dodatkowe przykłady znajdziesz w

literaturze [3, str.49].

e) uproszczony zapis funkcji jest sumą iloczynów otrzymanych z wszystkich

zaznaczonych obszarów. Dla lewej tablicy z rys.5 otrzymamy F = B’C’ + A’B.

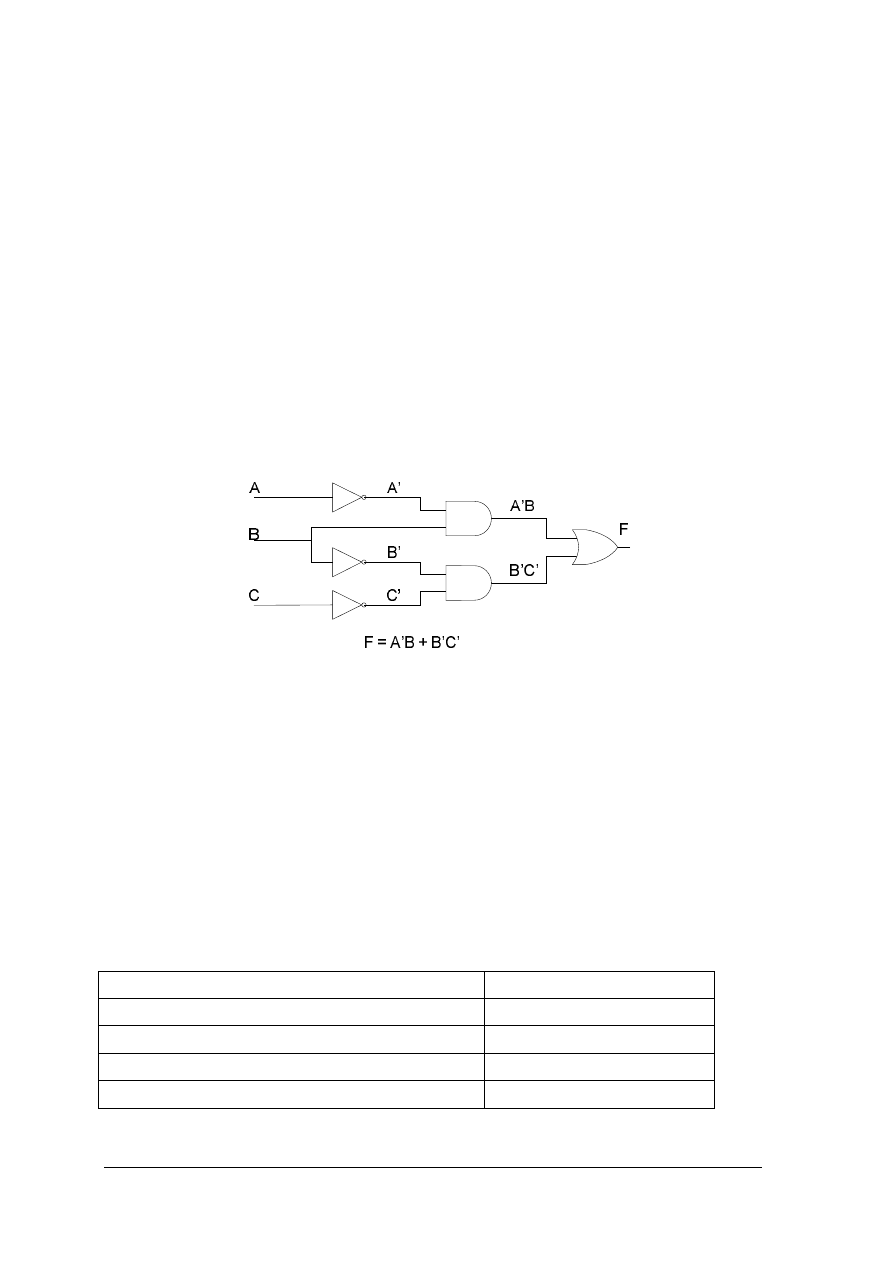

5. Na koniec na podstawie uproszczonej funkcji rysujemy schemat logiczny układu,

zastępując zapis działania logicznego odpowiednią bramką logiczną: negację - bramką

NOT, iloczyn - bramką AND, sumę - bramką OR.

Schemat logiczny dla funkcji F = B’C’ + A’B jest następujący:

Rys. 6. Schemat logiczny układu opisanego funkcją F= A’B + B’C’

W praktyce często potrzebna jest umiejętność zrozumienia działania układu na podstawie

schematu logicznego. Jest to szczególnie ważne w przypadku konieczności wykrywania

usterek w pracy układów. Aby określić przyczynę błędnego działania układu należy:

−

określić na podstawie schematu prawidłowe działanie układu jako całości i każdego

elementu – bramki wchodzącej w jego skład,

−

na podstawie pomiarów stwierdzić sposób działania układu z usterką,

−

porównać otrzymane wyniki z prawidłowymi i dokonać identyfikacji elementu

działającego niepoprawnie.

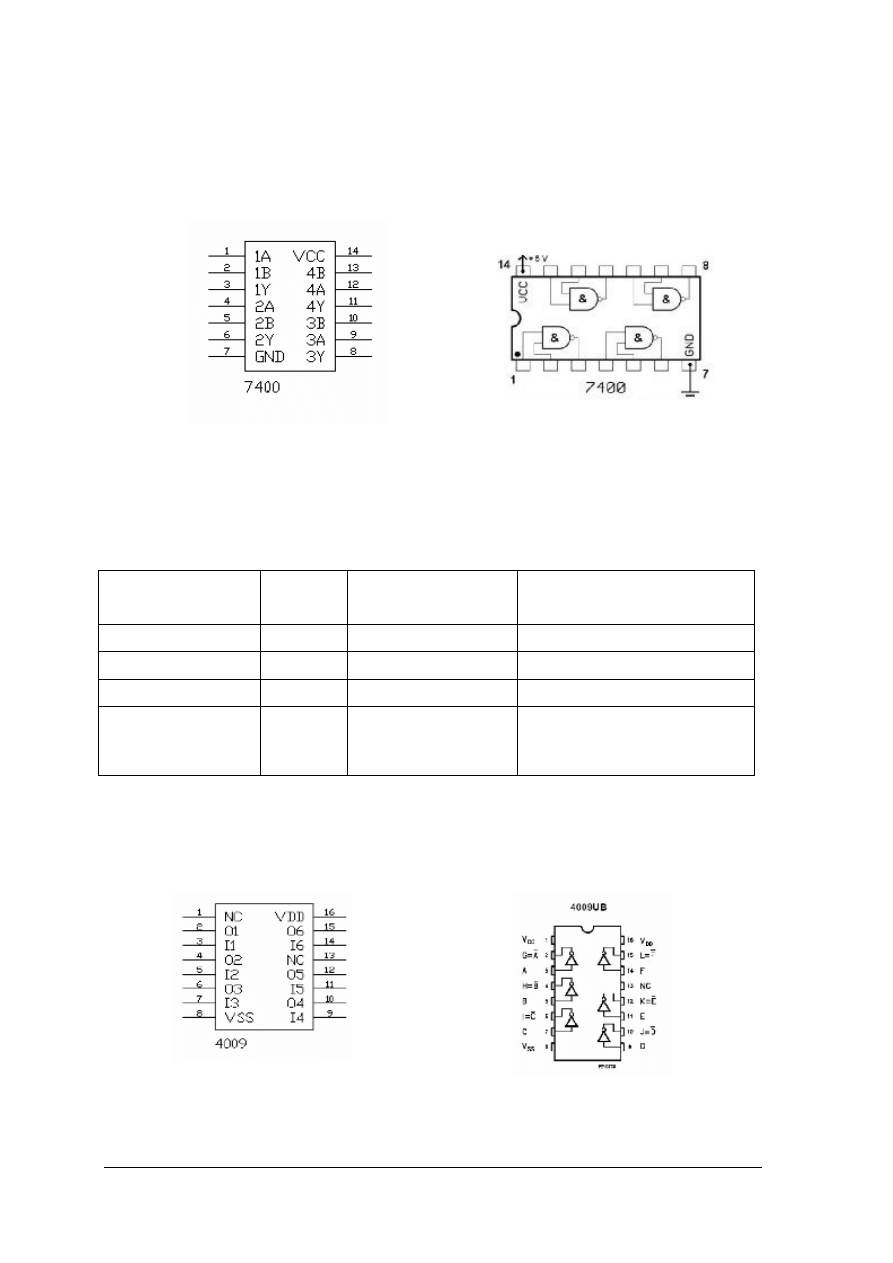

4.2.1.5. Technologia TTL i CMOS produkcji układów scalonych

Układy cyfrowe mogą być wykonane w różnej technologii i różnym stopniu scalenia.

Tabela 8.

Stopień scalenia

Liczba bramek w układzie

SSI – mały stopień scalenia

Do 10 bramek

MSI – średni stopień scalenia

Od 10 do 100 bramek

LSI - duży stopień scalenia

Od 100 do 1000 bramek

VLSI – bardzo duży stopień scalenia

Od 1000 do 10 000

Duży asortyment układów w technologii TTL i CMOS zdecydował o ich dość

powszechnym zastosowaniu. W każdej z tych technologii można wyróżnić szereg serii

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

22

układów. Układy TTL – LS (UCY74LSxx), 4000B (MCY 74xxx) oraz układy ACT, które są

układami CMOS kompatybilnymi z układami TTL to układy najbardziej reprezentatywne

w swoich grupach.

Sposób oznaczania układów przy pomocy symboli katalogowych znajdziesz w literaturze

[3, 8].

Rys. 7. Układ scalony w technologii TTL - UCY 7400N: a) opis wyprowadzeń, b) rozmieszczenie bramek.

Układy scalone TTL i CMOS różnią się przede wszystkim parametrami. Tabela 9

przedstawia porównanie podstawowych parametrów obu technologii. Więcej danych na temat

tych układów szukaj w katalogach i literaturze [3, 8].

Tabela 9.

Parametr

Jednostka

Technologia CMOS

Seria 4000B

Technologia TTL

Seria LS

Napięcie zasilania

V

3 – 18

4,75 – 5, 25

Moc statyczna

nW

10

2 000 000

Czas propagacji

ns

90

10

Margines zakłóceń

%

napięcia

zasilania

30

Około 10

Z porównania tych parametrów wynika, że układy CMOS serii 4000B są wolniejsze ale

pobierają znacznie mniej mocy, mają szeroki zakres napięć zasilających i są bardziej odporne

na zakłócenia.

a)

b)

Rys. 8. Układ scalony w technologii CMOS – 4009: a) opis wyprowadzeń, b) rozmieszczenie bramek.

a)

b)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

23

4.2.2. Pytania sprawdzające

Odpowiadając na pytania, sprawdzisz, czy jesteś przygotowany do wykonania ćwiczeń.

1. Jaki układ nazywamy układem kombinacyjnym?

2. Na jakich wartościach operuje algebra Boole’a?

3. W jakim celu stosujemy aksjomaty algebry Boole’a?

4. Jakie funkcje realizują bramki AND, OR, NOT?

5. Co to znaczy, że bramki tworzą układ funkcjonalnie pełny?

6. Czym się charakteryzują bramki z otwartym kolektorem?

7. Czym się charakteryzują bramki z przerzutnikiem Schmidta?

8. Jakie są sposoby opisu działania układów logicznych?

9. Jak opisać działanie układu logicznego za pomocą tabeli prawdy?

10. W jaki sposób z tabeli prawdy otrzymać funkcje logiczną opisującą działanie układu?

11. Jak uprościć funkcję z zastosowaniem aksjomatów algebry Boole’a?

12. Jak uprościć funkcję metodą Karnaugha?

13. Jak na podstawie funkcji narysować schemat logiczny układu?

14. Jakie podstawowe własności posiadają układy cyfrowe technologii TTL i CMOS?

15. Jak zinterpretować oznaczenie katalogowe układu w technologii TTL i CMOS?

4.2.3. Ćwiczenia

Ćwiczenie 1

Korzystając z praw algebry Boole’a oblicz wartość logiczną wyrażenia:

a) (1 + 1) ∙ (1 + 0) =

b) (A + A’) ∙ B =

c) AA’ + ( B + 1) =

d) (A + B)’ + A’’ =

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z prawami algebry Boole’a ( materiał nauczania pkt.4.2.1),

2) wykonać działanie krok po kroku zwracając szczególną uwagę na poprawne zastosowanie

odpowiednich aksjomatów,

3) sprawdzić poprawność wykonanych działań – jeśli masz trudności zwróć się

o pomoc do nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

literatura [3].

Ćwiczenie 2

Uzupełnij brakujące informacje w następującej tabeli:

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

24

Tabela 10. Bramki logiczne

Nazwa

bramki

Symbol graficzny

Funkcja

Tabela działania

Realizacja

na

przełącznikach

OR

F =

A

B

F

0

0

0

1

1

0

1

1

A

B

F

A

F

0

1

1

0

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z opisem działania poszczególnych bramek logicznych (Materiał nauczania

pkt.4.2.1),

2) wpisać w odpowiednie miejsca tabeli brakujące informacje,

3) sprawdzić poprawność wykonanych działań.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

literatura [3, 4, 8].

Ćwiczenie 3

Wykonaj badanie bramek NOT, NAND, NOR, EXOR - układów scalonych technologii

TTL i CMOS oraz sprawdź działanie układu zmontowanego zgodnie ze schematem

przedstawionym na rys. 6.

a) wyznacz charakterystykę przełączania bramki NOT w technologii TTL Uwy=f (Uwe)

i określ na jej podstawie napięcie przełączania,

b) zmierz wartość napięcia na wyjściu bramki NOT w stanie niskim U

OL

i wysokim U

OH

i porównaj otrzymane wyniki z danymi katalogowymi tego układu,

c) zbadaj poprawność działania pojedynczej bramki układu UCY 7400, UCY 7402, UCY

7486 i 4009 – wyznacz jej tabelę działania i porównaj otrzymane wyniki

z informacjami zawartymi w materiale nauczania i literaturze [8],

d) połącz układ korzystając ze schematu przedstawionego w materiale nauczania rys.6. s.

21. W razie konieczności dokonaj modyfikacji schematu dostosowując go do

dostępnych układów scalonych, na podstawie pomiarów wyznacz jego tabelę

działania, otrzymany wynik porównaj z tabelą prawdy zapisaną na podstawie funkcji –

oblicz wartość logiczną wstawiając do wzoru odpowiednie wartości logiczne A,B,C

tak jak w ćwiczeniu 1a.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

25

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z danymi katalogowymi badanych bramek (Materiał nauczania pkt.4.2.1.4 i

literatura [3,8]),

2) narysować schemat układu do pomiaru charakterystyki przełączania. Odszukaj układ

pomiarowy w literaturze [8] i sprawdź jego poprawność,

3) wykonać pomiary krok po kroku zmieniając napięcie wejściowe i odczytując napięcie na

wyjściu, zapisując jednocześnie w tabeli otrzymane wyniki pomiarów,

4) narysować charakterystykę w odpowiednio dobranym układzie współrzędnych, jeśli masz

z tym problemy poszukaj tej charakterystyki w literaturze [8],

5) wykonać pomiar napięcia w stanie niskim U

OL

i wysokim U

OH

za pomocą woltomierza

lub oscyloskopu,

6) skorzystać z próbnika stanów logicznych, woltomierza lub oscyloskopu do określania

stanu na wyjściu badanej bramki czy układu przy określonej kombinacji stanów

wejściowych,

7) jeśli to możliwe – przećwicz poszczególne kroki, korzystając z programu do symulacji

pracy układów logicznych.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik dla ucznia,

−

stanowisko

laboratoryjne

do

badania

układów

cyfrowych

wyposażone

w podstawowe przyrządy pomiarowe i zestawy układów do badań,

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

literatura [3, 4, 5, 8].

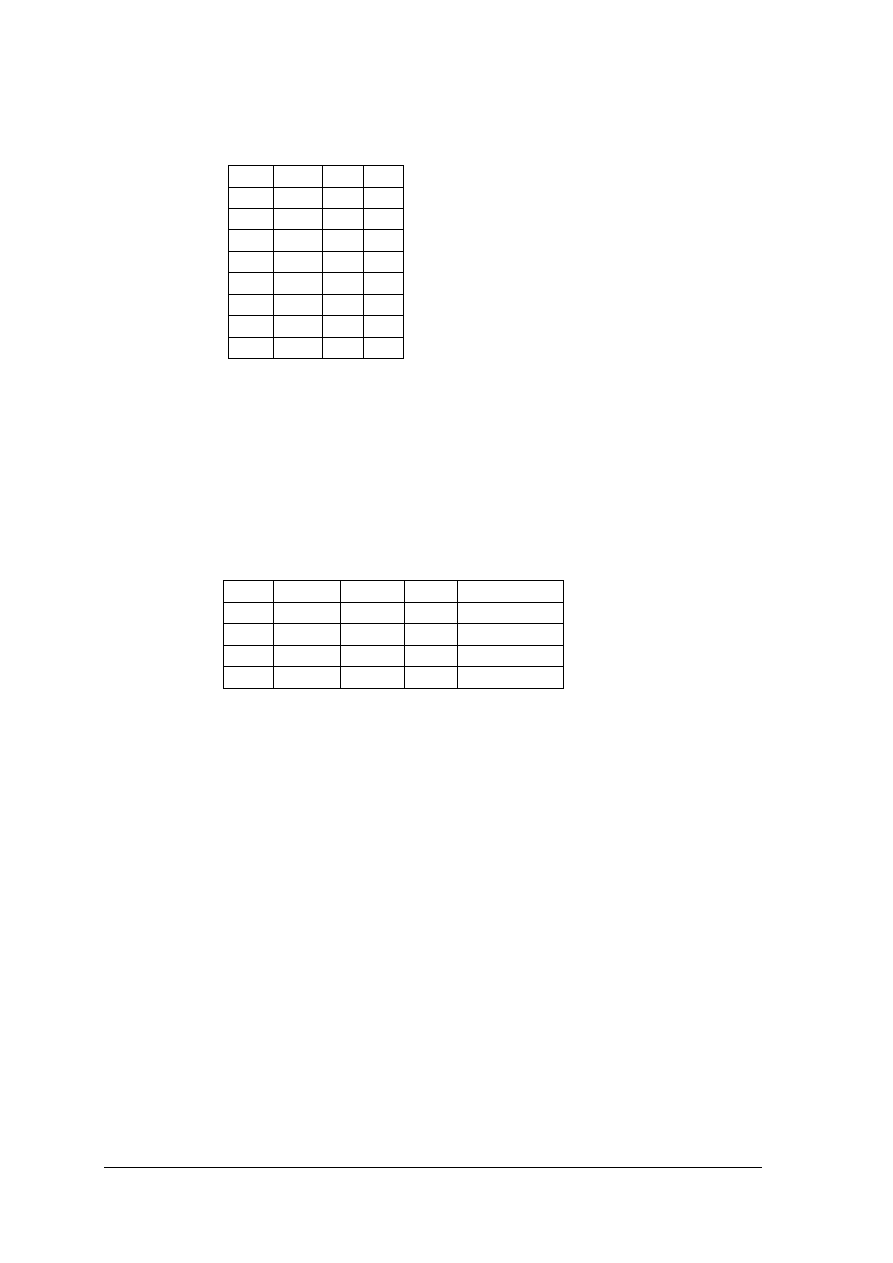

Ćwiczenie 4

Wykonaj badanie działania układu opisanego następującą tabelą prawdy.

Tabela 11. Tabela prawdy

a) zapisz funkcję F(ABC) opisującą działanie układu na podstawie

jego tabeli prawdy,

b) uprość wypisaną funkcję metodą Karnaugh’a.,

c) narysuj schemat tego układu,

d) korzystając z katalogu układów scalonych TTL [2] określ jakie

układy scalone i ile tych układów należy zastosować, aby wykonać

ten układ w praktyce,

e) określ jakim napięciem należy zasilać zaprojektowany układ,

f) wykonaj symulację komputerową działania tego układu, zmontuj

układ rzeczywisty i porównaj działanie układu

z założeniami.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z instrukcją dotyczącą wypisywania funkcji z tabeli działania (Materiał

nauczania pkt.4.2.1.4),

A B C

F

0 0

0

1

0

0

1

1

0

1

0

0

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

26

2) wykonać działanie krok po kroku zwracając szczególną uwagę na poprawny zapis

zmiennych z negacją i bez negacji,

3) sprawdzić poprawność przed rozpoczęciem minimalizacji,

4) wykonać minimalizację zgodnie z instrukcją (Materiał nauczania pkt.4.2.1.4),

5) narysować schemat logiczny tego układu,

6) dobrać układy scalone technologii TTL do jego praktycznej realizacji i określić ich

liczbę,

7) wykonać symulację komputerową działania układu,

8) zmontować układ zgodnie ze schematem.

Wyposażenie stanowiska pracy:

−

stanowisko laboratoryjne do badania układów cyfrowych wyposażone w podstawowe

przyrządy pomiarowe i zestawy układów do badań,

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

przybory do pisania,

−

poradnik ucznia,

−

literatura [3, 4, 6, 8].

4.2.4. Sprawdzian postępów

Tak Nie

Czy potrafisz:

1) opisać działanie układów logicznych różnymi metodami?

¨

¨

2) zastosować aksjomaty algebry Boole’a do upraszczania funkcji

logicznych?

¨

¨

3) uprościć funkcję logiczną metodą tablic Karnaugh’a ?

¨

¨

4) wyjaśnić działanie podstawowych bramek logicznych?

¨

¨

5) dokonać interpretacji podstawowych parametrów układów

scalonych technologii TTL i CMOS?

¨

¨

6) narysować schemat logiczny układu na podstawie funkcji?

¨

¨

7) określić działanie układu na podstawie schematu logicznego?

¨

¨

8) dobrać układy scalone do realizacji wybranej funkcji logicznej?

¨

¨

9) sprawdzić poprawność działania układu logicznego?

¨

¨

10) połączyć układ logiczny zgodnie ze schematem?

¨

¨

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

27

4.3. Komutacyjne i arytmetyczne układy cyfrowe

4.3.1. Materiał nauczania

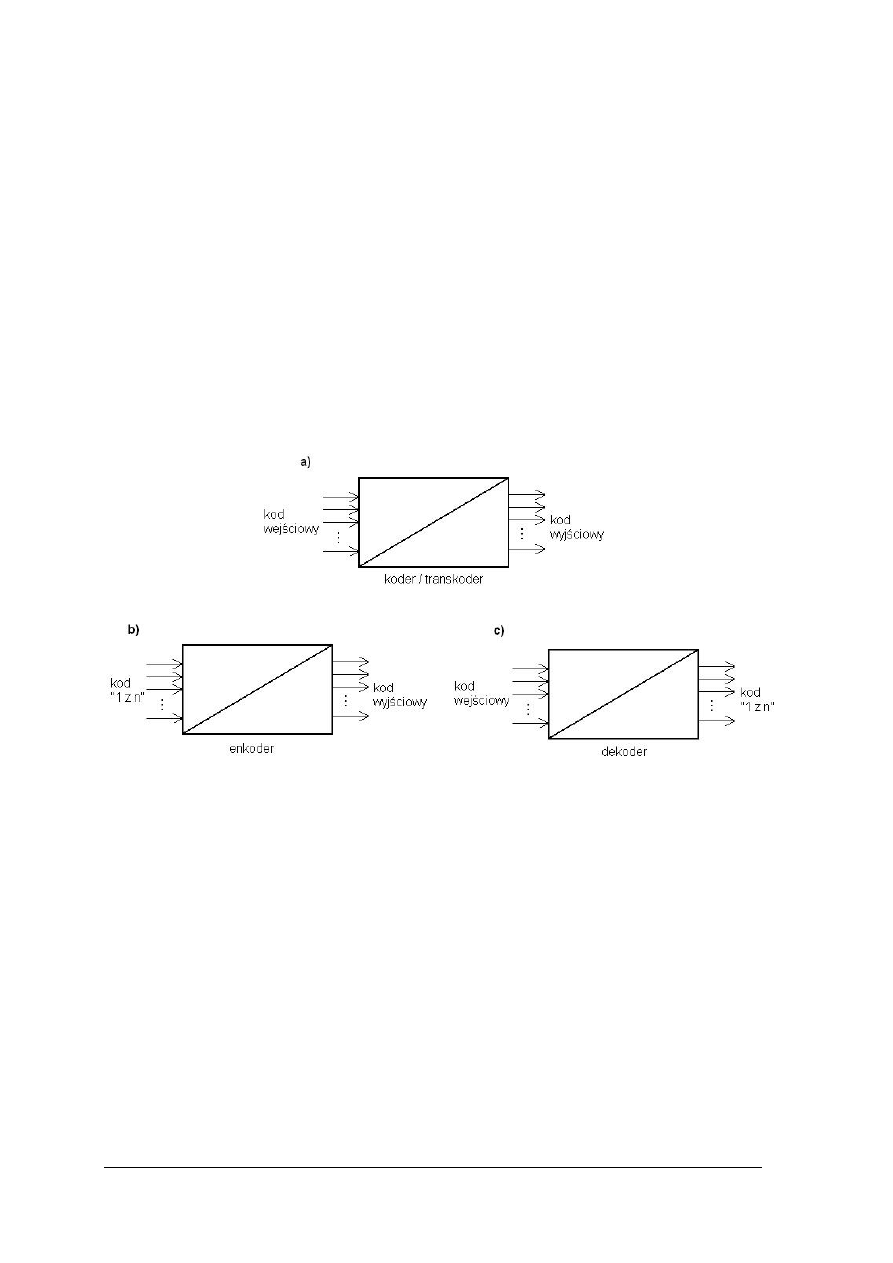

4.3.1.1. Układy zmiany kodu

Układem komutacyjnym nazywamy układ umożliwiający przełączanie sygnałów,

w naszym przypadku będzie chodziło o przełączanie sygnałów cyfrowych. Do grupy tych

układów zaliczamy:

−

kodery/ transkodery, dekodery, enkodery,

−

multipleksery, demultipleksery.

Kodery lub transkodery to układy realizujące proces zamiany kodu wejściowego na inny

zwany wyjściowym, przy czym żaden z tych kodów nie jest kodem „1z n”.

Enkoder to koder, w którym kod wejściowy jest kodem „1z n”, dekoder to koder,

w którym kod wyjściowy jest kodem „1z n”

Rys. 9. Symbole graficzne a) koder, b) enkoder, c) dekoder.

Działanie układów wielowyjściowych opisuje tyle funkcji, ile wyjść posiada układ.

Projektując takie układy postępujemy z każdą funkcją tak, jak to przestawiono

w materiale nauczania w pkt. 4.2.1.4.

Kodery, dekodery, multipleksery i demultipleksery należą do grupy układów średniej

skali integracji. Mogą być one wykonane w technologii TTL lub CMOS. Wraz ze

zwiększeniem skali integracji układów scalonych coraz większy mamy asortyment szybkich

układów CMOS, które ponadto charakteryzują się dużymi obciążeniami i są w pełni zgodne

końcówkowo i oznaczeniowo z układami TTL. Można więc przykładowo, układ TTL 74LS00

zastąpić układem 74 HCT00 lub 74ACT00 z grupy układów CMOS, jednak decyzję tę należy

dodatkowo uzależnić od wyniku analizy parametrów wejściowych i wyjściowych

współpracujących ze sobą bezpośrednio układów. W celu uniknięcia tych problemów

wygodniej jest projektując układ stosować układy jednej technologii.

Więcej informacji na temat parametrów szybkich układów CMOS znajdziesz

w katalogach w wersji drukowanej lub, coraz popularniejszych przez swoją dostępność,

wersjach elektronicznych.

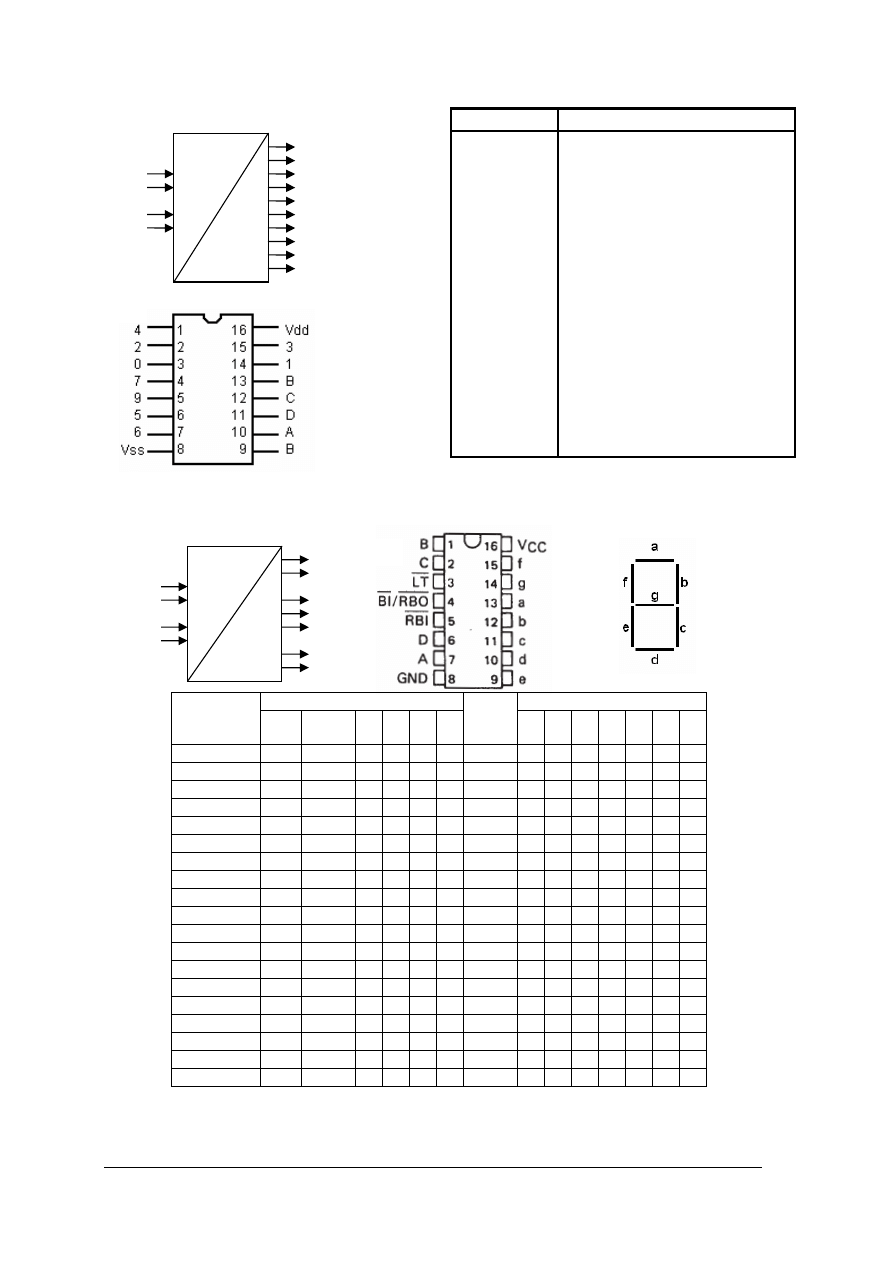

Przykłady układów zmiany kodu: Układ CMOS 4028 - dekoder z kodu BCD na kod „1

z 10”

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

28

A

B

C

D

a

b

c

d

e

f

g

d)

Rys. 10. Dekoder a) symbol graficzny, b) tabela działania, c) rozkład wyprowadzeń.

Układ TTL - 74LS47 – transkoder z kodu BCD na kod wskaźnika siedmiosegmentowego

Wejścia

Wyjścia

Liczba

dziesiętna

lub funkcja

LT

RBI

D C B A

BI /

RBO

a

b

c

d

e

f

g

0

H

H

L

L

L

L

H

L

L

L

L

L

L

H

1

H

X

L

L

L

H H

H L

L

H H H H

2

H

X

L

L

H L

H

L

L

H L

L

H L

3

H

X

L

L

H H H

L

L

L

L

H H L

4

H

X

L

H L

L

H

H L

L

H H L

L

5

H

X

L

H L

H H

L

H L

L

H L

L

6

H

X

L

H H L

H

H H L

L

L

L

L

7

H

X

L

H H H H

L

L

L

H H H H

8

H

X

H L

L

L

H

L

L

L

L

L

L

L

9

H

X

H L

L

H H

L

L

L

H H L

L

10

H

X

H L

H L

H

H H H L

L

H L

11

H

X

H L

H H H

H H L

L

H H L

12

H

X

H H L

L

H

H L

H H H L

L

13

H

X

H H L

H H

L

H H L

H L

L

14

H

X

H H H L

H

H H H L

L

L

L

15

H

X

H H H H H

H H H H H H H

BI

H

L

X X X X L

H H H H H H H

RBI

H

L

L

L

L

L

L

H H H H H H H

LT

L

X

X X X X H

L

L

L

L

L

L

L

Rys. 11. Transkoder z kodu BCD na kod wskaźnika siedmiosegmentowego a)symbol graficzny, b) rozkład

wyprowadzeń, c) segmenty wskaźnika, d) tabela działania.

D C B A 0 1 2 3 4 5 6 7 8 9

0

0

0

0

1 0 0 0 0 0 0 0 0 0

0

0

0

1

0 1 0 0 0 0 0 0 0 0

0

0

1

0

0 0 1 0 0 0 0 0 0 0

0

0

1

1

0 0 0 1 0 0 0 0 0 0

0

1

0

0

0 0 0 0 1 0 0 0 0 0

0

1

0

1

0 0 0 0 0 1 0 0 0 0

0

1

1

0

0 0 0 0 0 0 1 0 0 0

0

1

1

1

0 0 0 0 0 0 0 1 0 0

1

0

0

0

0 0 0 0 0 0 0 0 1 0

1

0

0

1

0 0 0 0 0 0 0 0 0 1

1

0

1

0

0 0 0 0 0 0 0 0 0 0

1

0

1

1

0 0 0 0 0 0 0 0 0 0

1

1

0

0

0 0 0 0 0 0 0 0 0 0

1

1

0

1

0 0 0 0 0 0 0 0 0 0

1

1

1

0

0 0 0 0 0 0 0 0 0 0

1

1

1

1

0 0 0 0 0 0 0 0 0 0

A

B

C

D

0

1

2

3

4

5

6

8

9

a)

b)

c)

c)

a)

b)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

29

Układ ten posiada dodatkowe wejścia sterujące LT’- wejście testujące, BI’/RBO’ –

wejście wygaszania wskaźnika i RBI’ – wejście wygaszania zera. W przypadku łączenia

kaskadowego układów sygnał z wyjścia BI’/RBO’ układu sterującego cyfrą mniej znaczącą

łączymy

z

wejściem

RBI’

układu

sterującego

cyfrą

bardziej

znaczącą

(o większej wadze) [8].

Prosty układ dekodera możemy zaprojektować z bramek logicznych korzystając

z procedury zamieszczonej w materiale nauczania 4.2.1.

4.3.1.2. Multipleksery i demultipleksery

Multiplekser pozwala na przekazanie sygnału z wybranego wejścia danych (na podstawie

adresu)

na

wyjście.

Adres

wejścia

danych

(informacyjnego)

podawany

jest

w kodzie binarnym na specjalne wejścia zwane adresowymi.

Demultiplekser pełni funkcję odwrotną niż multiplekser, to znaczy pozwala na

przekazanie sygnału wejściowego do jednego z wielu wyjść, wskazanego przez informacje

adresową.

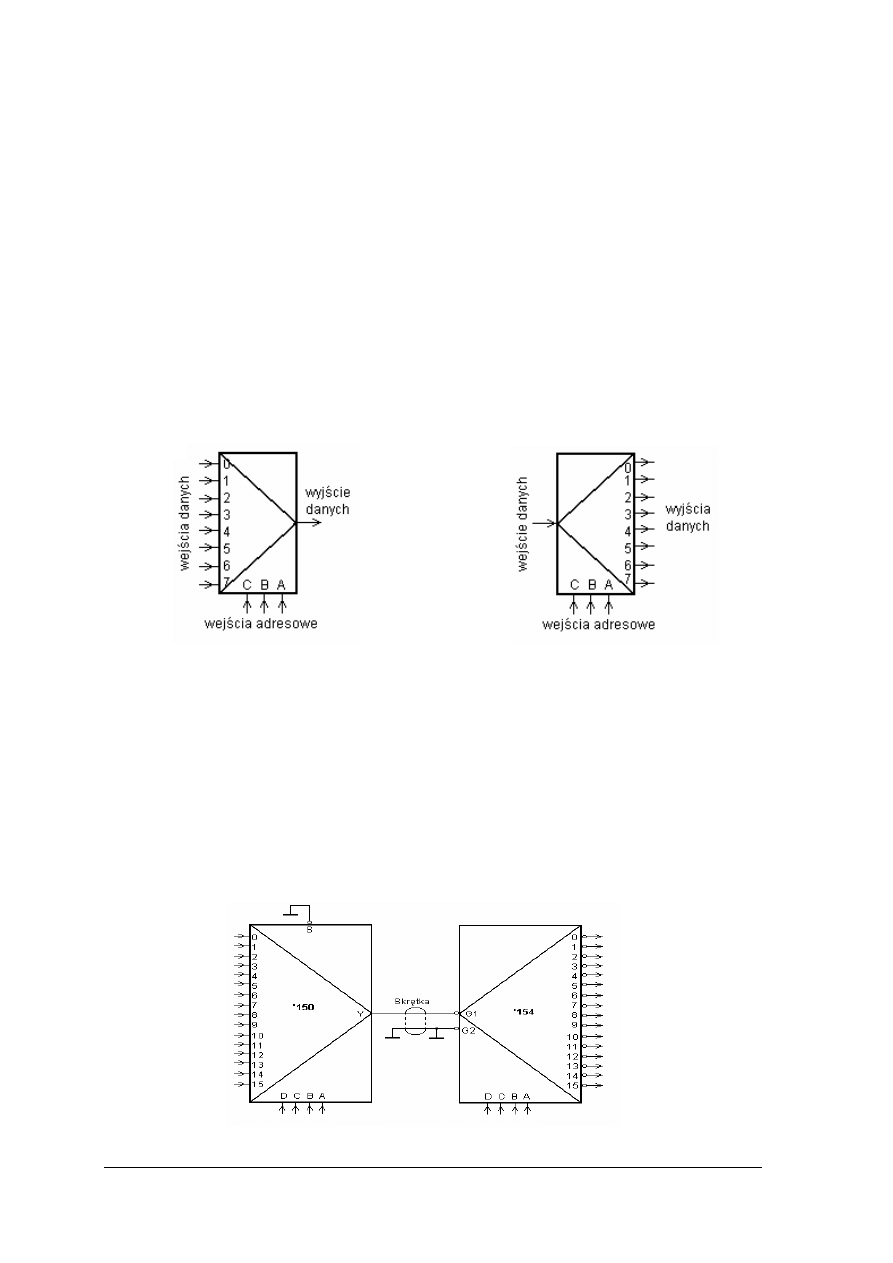

Rys. 12. Symbole graficzne a)multiplekser, b) demultiplekser.

Więcej danych o multiplekserze‘151 „z 8 linii na 1” znajdziesz w literaturze

[3, s. 202] lub w katalogu układów scalonych.[8]. Zwróć uwagę na zadanie, jakie spełnia

w tym układzie wejście strobujące oznaczone S. Wejście to umożliwia blokadę pracy całego

układu.

W transmisji danych cyfrowych stosuje się multipleksowy system przesyłania danych, co

umożliwia przesyłanie jedną linią zamiast wieloma – wielobitowych sygnałów binarnych.

W tym przypadku 16 bitowa informacja podana na wejścia multipleksera zostaje „bit po

bicie” nadawana w linię transmisyjną i odbierana przez demultiplekser. Ponieważ na wejścia

adresowe obu układów podaje się te same adresy, to na wyjściu demultipleksera otrzymuje się

ponownie tę sama 16 bitową informację.

Rys. 13. Multipleksowy system transmisji danych.

a)

b)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

30

Multipleksery i demultipleksery można łączyć ze sobą tworząc układy o większej liczbie

wejść lub wyjść.

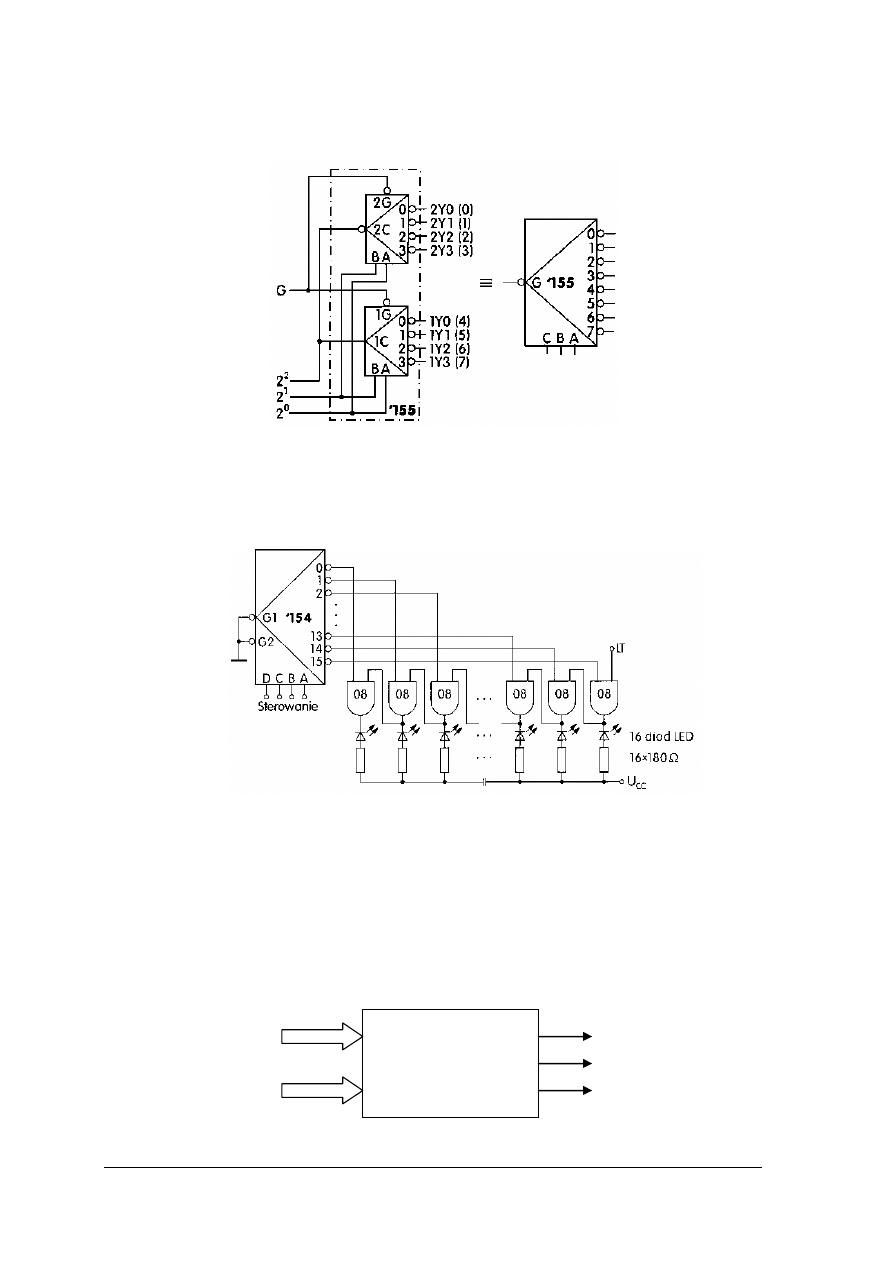

Rys. 14. Demultiplekser 8 wyjściowy zbudowany z dwóch demultiplekserów 4 wyjściowych [3,s. 204].

Multipleksery mają bardzo szerokie zastosowanie. Przykłady zastosowań znajdziesz

w literaturze [3,4]. Poniżej przedstawiony jest przykład sterowania za pomocą

demultipleksera linijką świetlną.

Rys.15. Układ sterujący linijką świetlną [3, s.207].

4.3.1.3. Komparatory

Komparatory służą do porównywania wartości binarnych. Najprostszy komparator

pozwala stwierdzić czy dwie wielkości binarne są sobie równe.

Komparator uniwersalny porównuje liczby i pozwala na uzyskanie odpowiedzi, czy

porównywane liczby binarne są sobie równe lub, która z nich większa czy mniejsza.

Wynikiem porównania jest pojawienie się stanu wysokiego na jednym z wyjść, co wskazuje

na relację jaka jest pomiędzy argumentami A i B

Rys.16. Symbol graficzny komparatora uniwersalnego.

A>B

A=B

A<B

A

B

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

31

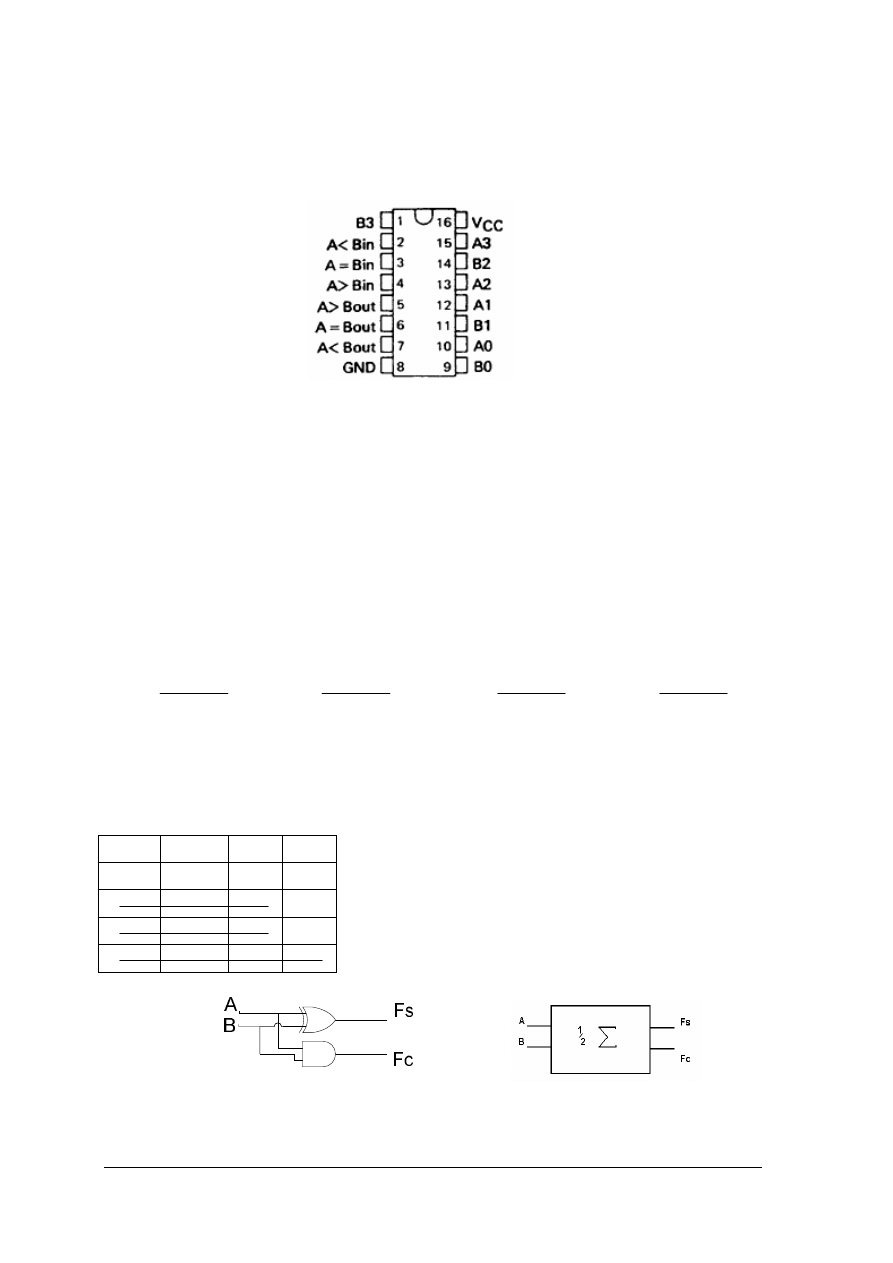

Układem komparatora jest układ TTL 7485 – jest to komparator czterobitowy.

W tym układzie porównywane są czterobitowe argumenty A i B. Zwróć uwagę na dodatkowe

wejścia kaskadowe (wyprowadzenia 2,3,4), które umożliwiają łączenie tych układów w celu

uzyskania możliwości porównywania argumentów o większej liczbie bitów.

Rys. 17. Rozkład wyprowadzeń komparatora uniwersalnego 7485N.

4.3.1.4. Sumatory

Sumatory są układami umożliwiającymi dodawanie wielkości binarnych. Sam proces

dodawania liczb binarnych jest przedstawiony w materiale nauczania 4.1.1. Sumator

umożliwia także wykonywanie odejmowania pod warunkiem, że odjemnik zostanie wcześniej

zakodowany kodem U2. Opis tego kodu znajduje się w literaturze [3, s. 226].

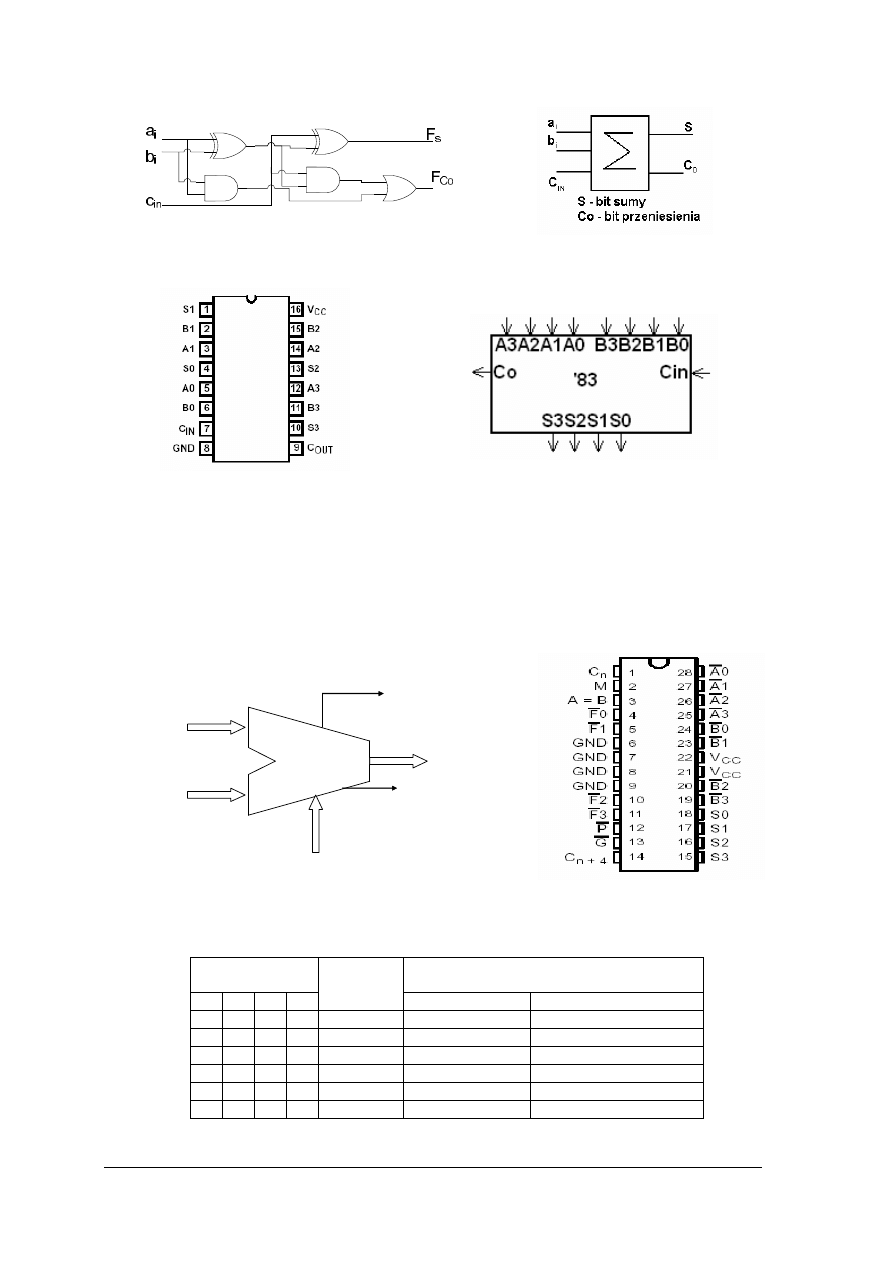

Najprostszym układem sumującym jest półsumator – układ, który umożliwia dodawanie

dwóch liczb jednobitowych.

Aby zaprojektować ten układ musimy wyobrazić sobie jego działanie.

Dodając dwie liczby możemy mieć następujące przypadki:

S – bit sumy, C – bit przeniesienia

Możemy to zapisać w postaci tabeli działania i postępując zgodnie z procedurą wypisać

funkcje opisujące działanie tego układu. F

S

- funkcja sumy, F

C

– funkcja przeniesienia

.

Tabela 12.

Bit A

Bit B

F

S

F

C

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Rys. 18. Półsumator: a) schemat logiczny, b) symbol graficzny.

Dwa połączone półsumatory tworzą układ sumatora umożliwiającego sumowanie dwóch

bitów liczb wielobitowych.

0

(2)

+ 0

S = 0

0

(2)

+ 1

S = 1

1

(2)

+ 0

S = 1

1

(2)

+ 1

S = 0

C =1

F

S

= A’B + AB’ F

C

= AB

Uwaga: odszukaj w tabeli 6 i 7 bramki

logiczne, które realizują funkcje F

S

i F

C.

a)

b)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

32

Rys.19. Sumator: a) schemat logiczny, b) symbol graficzny.

Rys. 20. Sumator czterobitowy ’83: a) rozkład wyprowadzeń, b) symbol graficzny

4.3.1.5. Jednostka arytmetyczno – logiczna ALU

Układem, który umożliwia wykonywanie operacji arytmetycznych i logicznych na

argumentach binarnych jest jednostka arytmetyczno – logiczna, zwana w skrócie ALU.

Najprostszy układ tego typu ‘181 umożliwia wykonywanie 16 operacji arytmetycznych

i 16 logicznych na argumentach czterobitowych. Wyboru wykonywanej operacji dokonuje się

poprzez dobór odpowiedniego pięciobitowego sygnału sterującego [3,4,8].

Rys. 21. a) symbol graficzny, b) rozkład wyprowadzeń ALU 74ACT1181 c) fragment tabeli działania.

Wejścia wyboru

funkcji

Operacje arytmetyczne M = 0

S3 S2 S1 S0

Funkcje

logiczne

M =1

C

n

= 0

C

n

= 1

L

L

L

L

F =A’

F = A

F = A PLUS 1

L

L

L

H

F = (A+B)’ F = A + B

F = (A + B) PLUS 1

L

L

H

L

F = A’B

F = A + B’

F = (A + B’) PLUS 1

L

L

H

H

F = 0

F = MINUS 1

F = ZERO

L

H

L

L

F = (AB)’

F = A’ PLUS AB’ F = A PLUS AB’ PLUS 1

.

…..

…..

…….

a)

b)

A

0

– A

3

B

0

– B

3

F

0

– F

3

S

0

– S

3

M

C

n

A = B

C

n +4

a)

b)

a)

b)

c)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

33

4.3.2. Pytania sprawdzające

Odpowiadając na pytania sprawdzisz, czy jesteś przygotowany do wykonania ćwiczeń.

1. Czym się charakteryzują układy komutacyjne?

2. Do czego służą dekodery?

3. Jaki jest symbol graficzny kodera?

4. Jaka jest tabela działania dekodera z kodu binarnego na kod „1z4”?

5. Czym się różni dekoder od enkodera?

6. Jak zaprojektować dekoder?

7. Jak na podstawie tabeli działania zinterpretować funkcjonowanie układu?

8. Jaka jest zasada działania multipleksera i demultipleksera?

9. Jak rozszerzyć liczbę wejść w multiplekserze?

10. Na czym polega multipleksowy system transmisji danych?

11. Do czego służą komparatory?

12. Jak zinterpretować oznaczenia wyprowadzeń wybranych układów scalonych?

13. Do czego służy sumator?

14. Jak rozszerzyć liczbę bitów argumentów w układach komparatorów i sumatorów?

15. Jaki jest symbol graficzny jednostki arytmetyczno-logicznej?

16. Jakie funkcje realizuje ALU?

4.3.3. Ćwiczenia

Ćwiczenie 1

Zaprojektuj układ dekodera z kodu binarnego na kod „1z 4”.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z instrukcją dotyczącą projektowania układów kombinacyjnych (Materiał

nauczania pkt. 4.2.1.4) oraz tabelami kodów binarnych (Materiał nauczania pkt. 4.1.1.9),

2) wykonać zaplanowane czynności krok po kroku,

3) narysować schemat logiczny projektowanego układu,

4) zbudować układ zgodnie ze schematem w programie symulacyjnym i zaplanować

wysterowanie wejść zgodnie z jego tabelą działania,

5) porównać otrzymane sygnały wyjściowe z zakładanymi – obserwować sygnały

wyjściowe możesz za pomocą wskaźników stanów logicznych lub za pomocą

oscyloskopu wielokanałowego.

Jeśli masz trudności poproś o pomoc nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

literatura [3, 4, 6, 8].

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

34

Ćwiczenie 2

Mając do dyspozycji układ ’47 zaproponuj schemat połączeń umożliwiający

wysterowanie wyświetlacza siedmiosegmentowego

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z zasadą dotyczącą sterowania tym układem wyświetlacza, tabelami kodu

BCD i kodu wskaźnika siedmiosegmentowego oraz tabelą działanie tego układu

(Materiał nauczania pkt. 4.3.1.1 oraz pkt. 4.1.1.9),

2) opracować plan pracy umożliwiający wykonanie ćwiczenia,

3) wykonać zaplanowane czynności krok po kroku,

4) narysować schemat sterowania badanym układem,

5) zbudować schemat w programie symulacyjnym i zaplanować wysterowanie wejść

zgodnie z jego tabelą działania,

6) porównać otrzymane sygnały wyjściowe z zakładanymi – obserwować sygnały

wyjściowe możesz za pomocą przyłączonego wskaźnika siedmiosegmentowego oraz za

pomocą oscyloskopu wielokanałowego,

7) wykonać odpowiednie połączenia w układzie ćwiczeniowym. Sygnały wejściowe możesz

podawać na wejścia za pomocą zadajników stanów logicznych.

Jeśli masz trudności poproś o pomoc nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

stanowisko

laboratoryjne

do

badania

układów

cyfrowych

wyposażone

w podstawowe przyrządy pomiarowe i zestawy układów do badań,

−

literatura [3, 4, 6, 8].

Ćwiczenie 3

Sprawdź poprawność działania półsumatora zbudowanego zgodnie ze schematem

zawartym w materiale nauczania pkt.4.3.1.4.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z zasadą działania tego układu (Materiał nauczania pkt. 4.3.1.4),

2) opracować wykaz czynności umożliwiający wykonanie ćwiczenia,

3) wykonać zaplanowane czynności krok po kroku,

4) wykorzystać program symulacyjny do sprawdzenia poprawności działania półsumatora

poprzez porównanie otrzymanych sygnałów wyjściowych z tabelą działania tego układu,

5) wykorzystać wyposażenie stanowiska laboratoryjnego do sprawdzenia poprawności

działania półsumatora poprzez porównanie otrzymanych sygnałów wyjściowych

z tabelą działania tego układu.

Jeśli masz trudności poproś o pomoc nauczyciela.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

35

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

stanowisko

laboratoryjne

do

badania

układów

cyfrowych

wyposażone

w podstawowe przyrządy pomiarowe i zestawy układów do badań,

−

literatura [3, 4, 6, 8].

Ćwiczenie 4

Mając do dyspozycji katalog układów scalonych określ na podstawie tabeli działania, jaki

kod sterujący należy podać na wejścia sterujące układu ‘181, aby wykonać dodawanie

czterobitowych argumentów wejściowych.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zapoznać się z zasadą sterowania tym układem, (Materiał nauczania pkt.4.3.1.5 oraz [8]),

2) przeanalizować dokładnie tabelę działania zawartą w katalogu,

3) określić żądaną operację i z tabeli wypisać odpowiadający jej stan wejść sterujących,

4) sprawdzić poprawność odpowiedzi poprzez przygotowanie symulacji dla dowolnych

wartości argumentów lub poprzez wykonanie zadania na stanowisku badaniowym.

Wyposażenie stanowiska pracy:

−

przybory do pisania,

−

poradnik ucznia,

−

stanowisko komputerowe z programem do symulacji pracy układów cyfrowych,

−

stanowisko

laboratoryjne

do

badania

układów

cyfrowych

wyposażone

w podstawowe przyrządy pomiarowe i zestawy układów do badań,

−

literatura [3, 4, 6, 8].

4.3.4. Sprawdzian postępów

Tak Nie

Czy potrafisz:

1) opisać różnymi metodami działanie układów zmiany kodu?

¨

¨

2) zaprojektować układ dekodera z kodu binarnego na kod „1z n” ?

¨

¨

3) wyjaśnić działanie multiplekserów i demultiplekserów?

¨

¨

4) połączyć układy multiplekserów w celu zwiększenia liczby wejść ?

¨

¨

5) zinterpretować funkcje poszczególnych wejść i wyjść komparatorów?

¨

¨

6) rozróżnić symbole graficzne sumatorów, dekoderów, multiplekserów

i demultiplekserów?

¨

¨

7) określić działanie wybranego układu na podstawie opisu

wyprowadzeń?

¨

¨

8) wysterować układ logiczny zgodnie z jego tabelą działania?

¨

¨

9) opracować symulacje złożonego układu logicznego?

¨

¨

10) zinterpretować wykresy prezentujące pracę poznanego układu ?

¨

¨

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

36

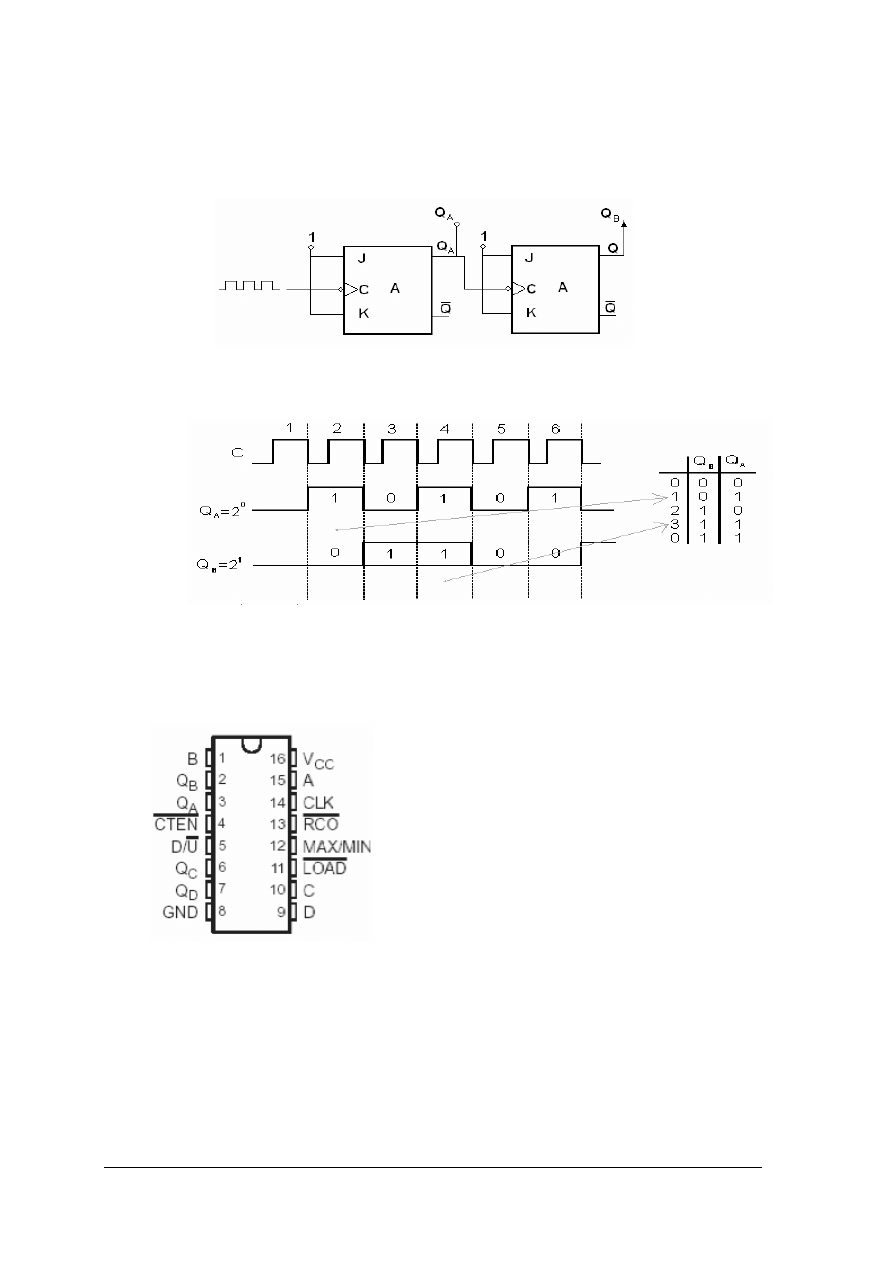

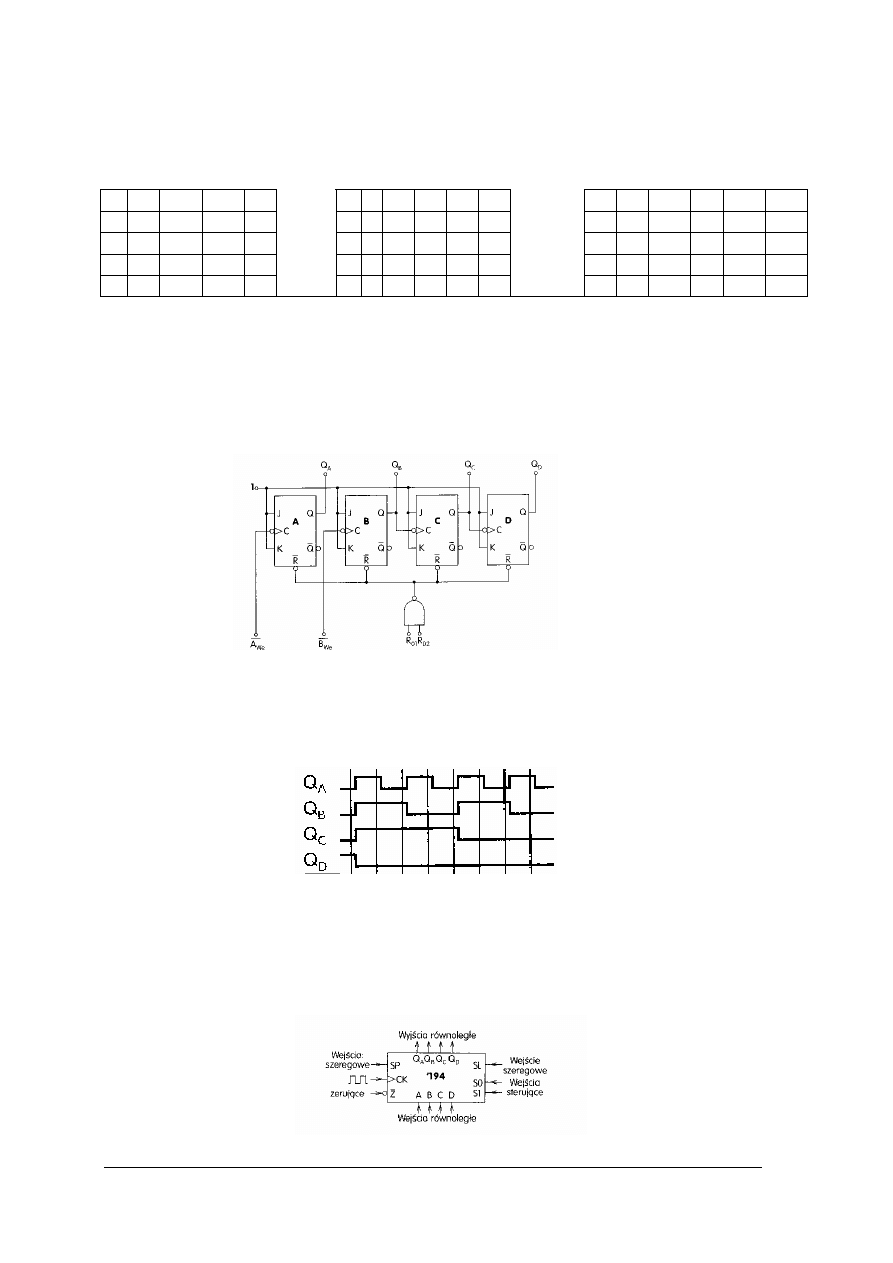

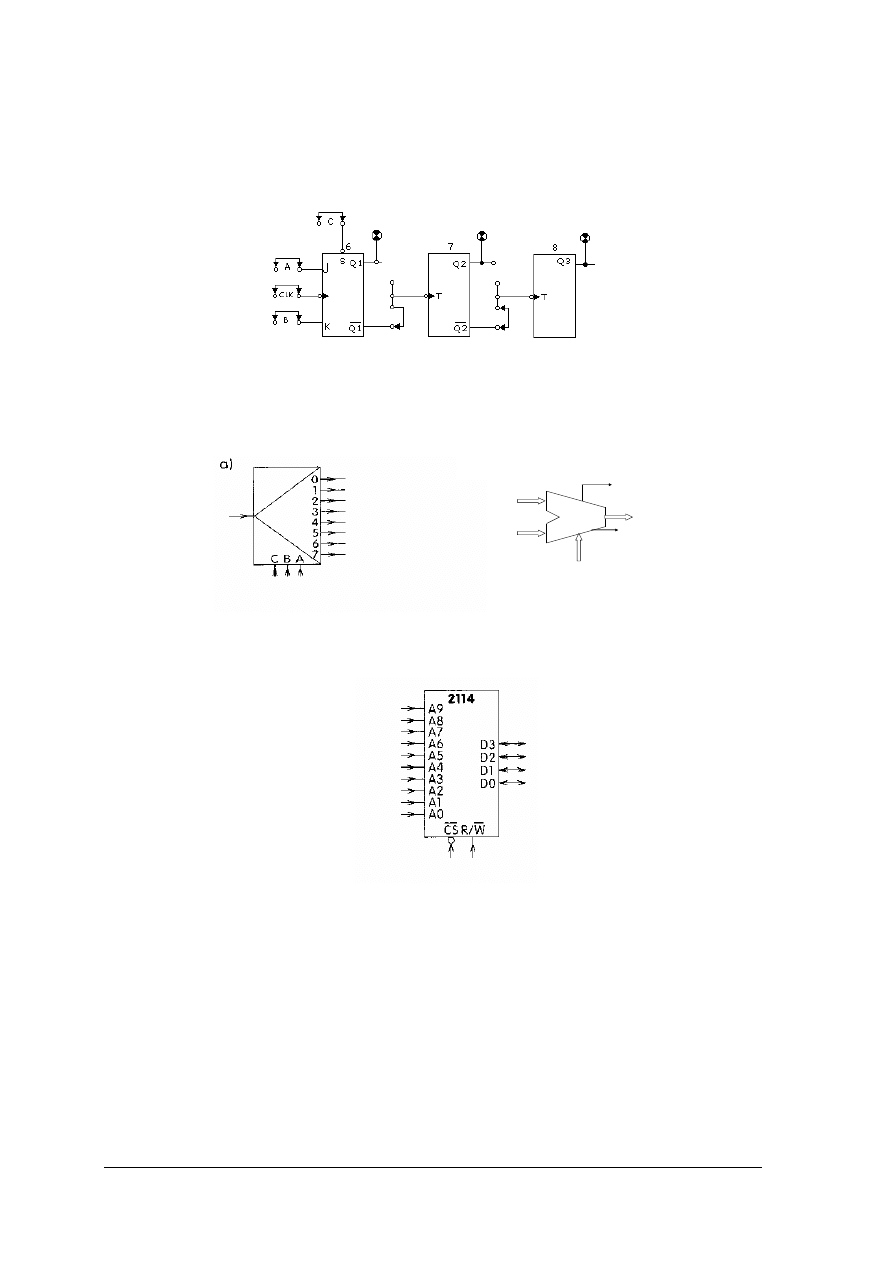

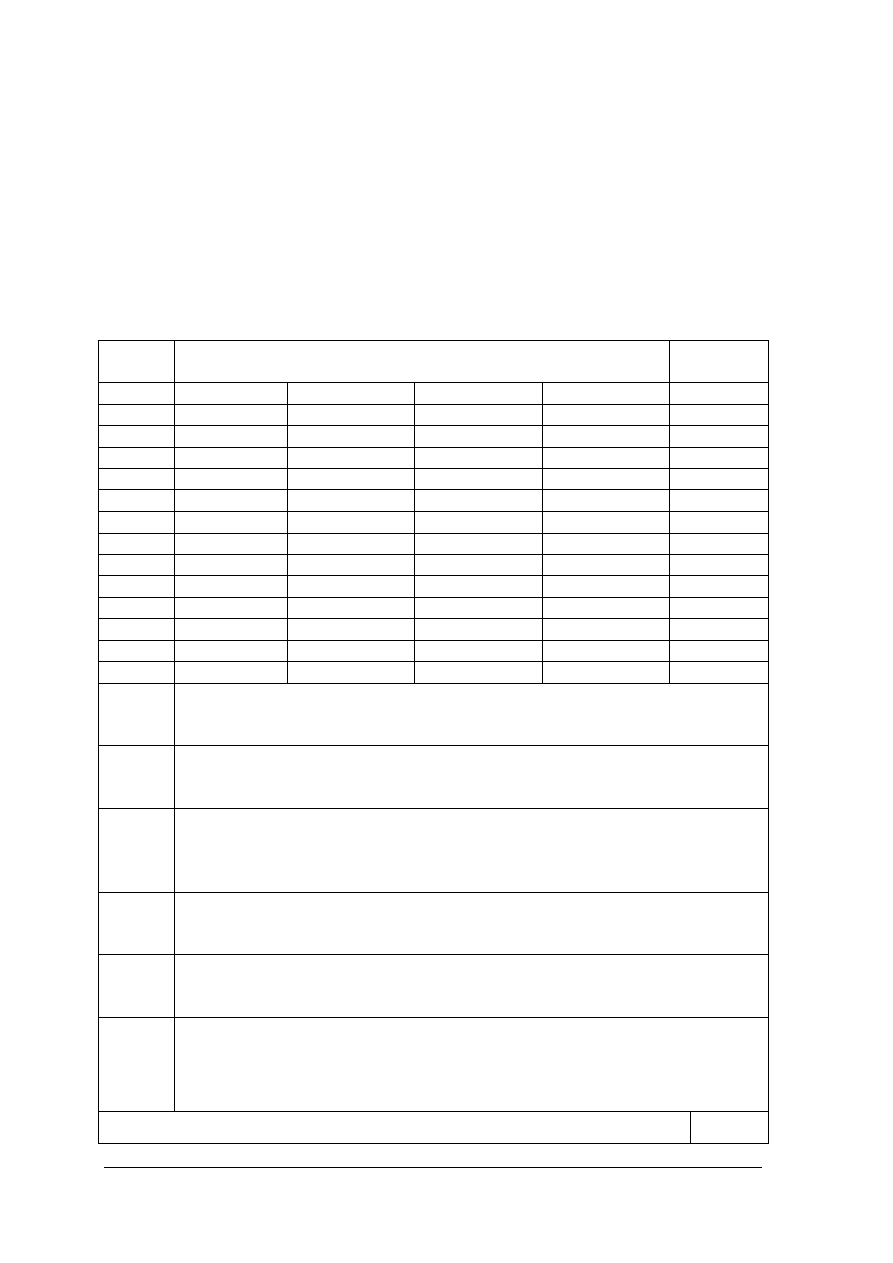

4.4. Układy sekwencyjne - liczniki, rejestry

4.4.1. Materiał nauczania

4.4.1.1. Przerzutniki bistabilne

Przerzutniki należą do grupy układów sekwencyjnych. Układem sekwencyjnym

nazywamy układ, w którym stan na wyjściu zależy nie tylko od stanów na wejściach tego

układu (tak było w przypadku układów kombinacyjnych), ale także od stanu wcześniejszego

na wyjściu (stanem wcześniejszym – poprzednim nazywamy stan układu, jaki istniał przed

podaniem aktualnych sygnałów na wejścia). Przyjmiemy następujące oznaczenia: Q – stan

poprzedni na wyjściu układu, Q

+

- stan

następny na wyjściu układu, Q’ – negacja Q[3,4,6].

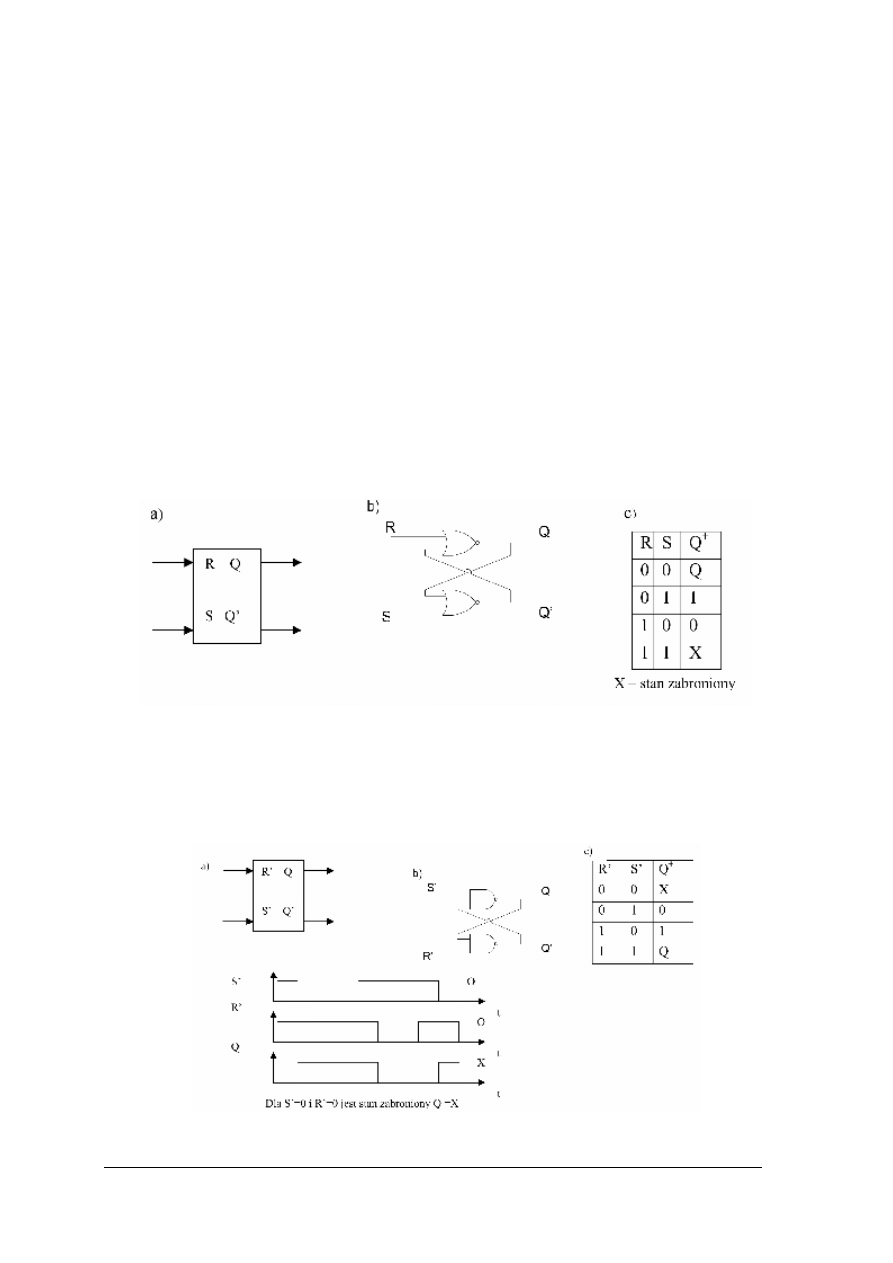

Przerzutnik RS

Najprostszy układ przerzutnika RS można zrealizować z bramek NAND lub NOR.

Nazwa przerzutników pochodzi od nazw wejść – przerzutnik RS ma dwa wejścia

informacyjne S(set) – wejście ustawiające stan wysoki (H, „1”) na wyjściu Q i wejście

R(reset) – ustawiające stan niski (L, „0”) na wyjściu Q.

Rys. 22. Przerzutnik RS na bramkach NOR: a) symbol graficzny, b)schemat logiczny, c) tabela działania.

Przerzutnik może być wykonany z ramek NAND. Jego działanie różni się od

przerzutnika RS wykonanego na bramkach NOR. Wejście ustawiające S powoduje ustawienie

stanu wysokiego na wyjściu Q wtedy, gdy jego stan jest równy zero – mówimy, że w tym

przerzutniku „0” jest stanem aktywnym. Ustawienie Q=0 tez następuje, gdy wejście R = 0.

W symbolu graficznym i w tabeli działania zaznaczamy to pisząc z negacją - S’ i R’.

Rys. 23. Przerzutnik RS na bramkach NAND: a) symbol graficzny, b)schemat logiczny, c) tabela działania, d)

wykresy czasowe.

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

37

Przerzutniki przedstawione powyżej są układami asynchronicznymi, nie posiadają wejść

zegarowych. Zastosowanie synchronizacji pracy układu poprzez wprowadzenie dodatkowego

wejścia zegarowego C (ang. clock) między innymi zwiększa odporność układu na zakłócenia,

eliminując powstawanie błędów w stanach przejściowych.

Ze względu na rodzaj zastosowanej synchronizacji rozróżniamy przerzutniki

synchronizowane zboczem impulsu zegarowego lub poziomem napięcia na wejściu

synchronizującym (są to przerzutniki typu „zatrzask” - „latch”). W przypadku przerzutników

synchronizowanych zboczem impulsu zegarowego rozróżniamy układy synchronizowane

zboczem narastającym lub opadającym. Pokażemy to na przykładach.

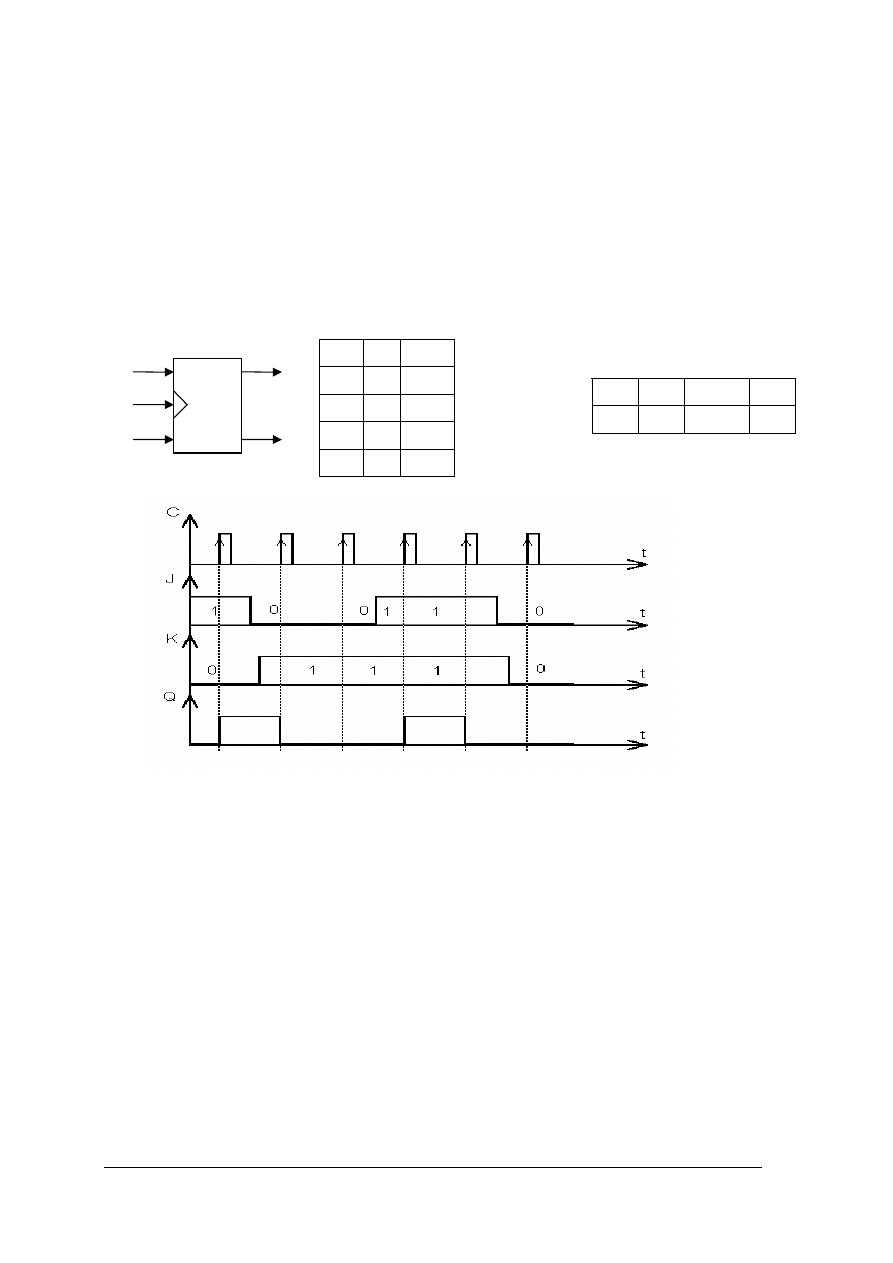

Przerzutnik JK

Rys. 24. Przerzutnik JK: a) symbol graficzny, b) skrócona tabela działania, c) tabela działania, d) wykresy.

Porównaj skrócone tabele działania przerzutnika RS (NOR) i JK. Jak pewnie zauważyłeś

w przerzutniku JK nie ma stanu zabronionego, a dla J=1 i K=1 układ zmienia stan na

przeciwny do tego, w jakim był przed podaniem tych sygnałów wejściowych.

W przypadku przerzutnika synchronicznego zmiana stanu może nastąpić wyłącznie

w obecności właściwego zbocza impulsu zegarowego. Przerzutnik, którego symbol jest na

rys. 23 jest synchronizowany przednim zboczem impulsu zegarowego. Taki rodzaj

synchronizacji w tabeli działania oznaczany jest symbolicznie strzałką w górę [8].

Przerzutnik oprócz wejść informacyjnych (J,K) zegarowego (C lub Clk) może posiadać

wejścia programujące S i R, które są asynchroniczne i działają bez sygnału zegarowego

a ponadto mają wyższy priorytet i blokują pracę pozostałych wejść.

Przerzutniki JK – MS są przerzutnikami typu „master – slave” i pracują w trybie

dwutaktowym. Więcej informacji na ten temat znajdziesz w literaturze [ 3, 4, 8].

J

K

Q

+

0

0

Q

0

1

0

1

0

1

1

1

Q’

Q\JK

00

01

11

10

Q=0

0

0

1

1

Q=1

1

0

0

1

J Q

C

K Q’

Q

+

= Q’J + QK’

Q

+

= 1 gdy Q=0 i J=1 lub Q=1 i K=0

a)

b)

c)

d)

„

Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

38

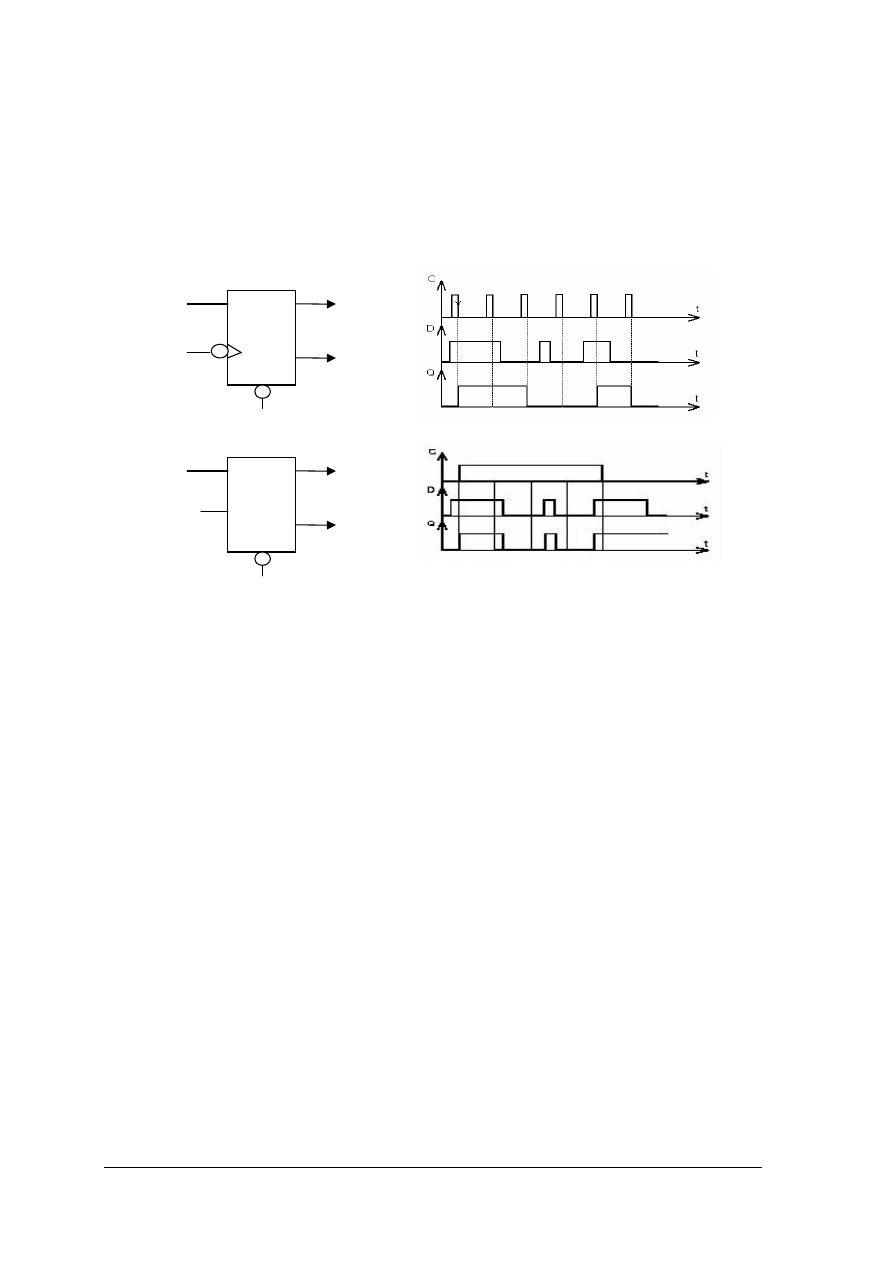

Przerzutnik D

Przerzutniki D występują w dwóch wersjach: z synchronizacją zboczem impulsu

zegarowego lub typu „zatrzask” – z synchronizacją poziomem sygnału zegarowego. Oba

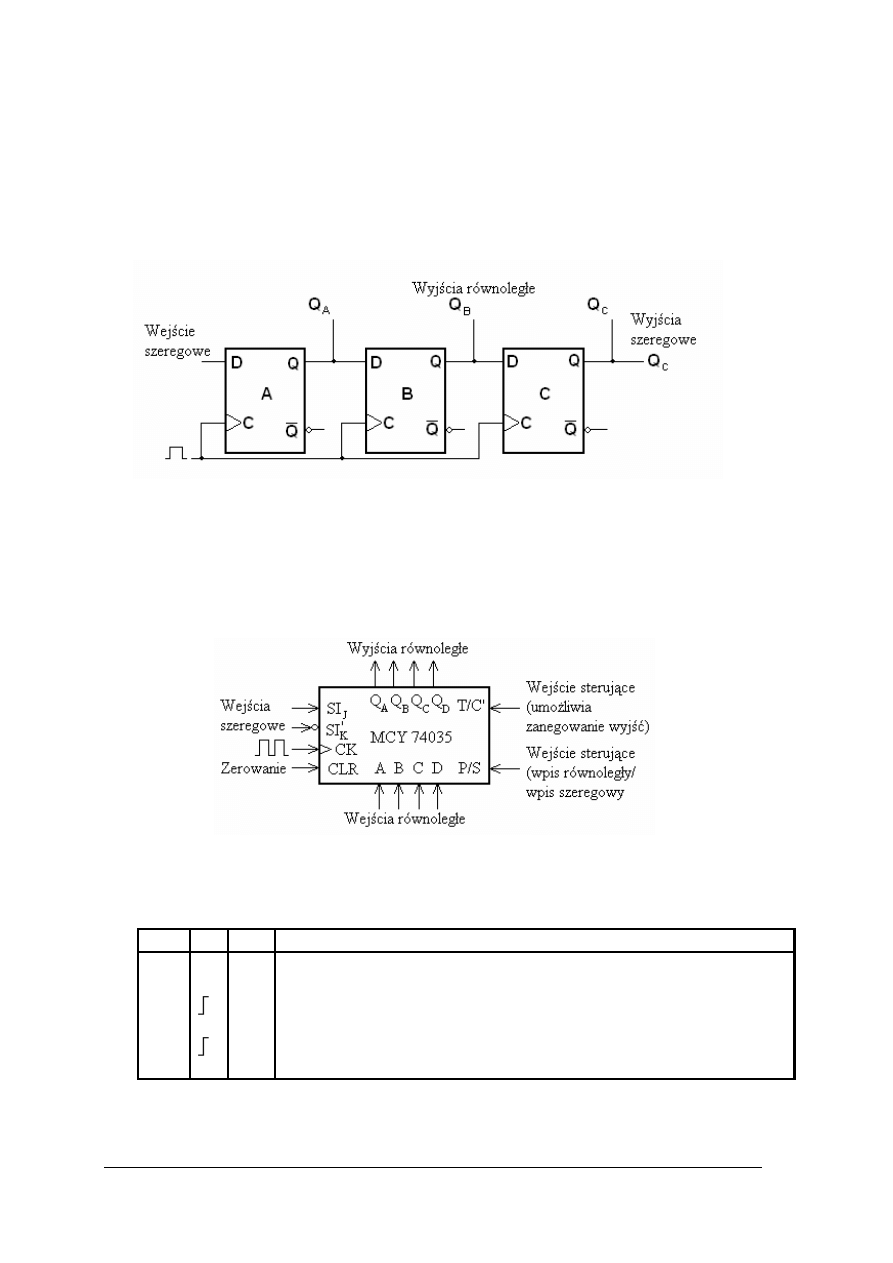

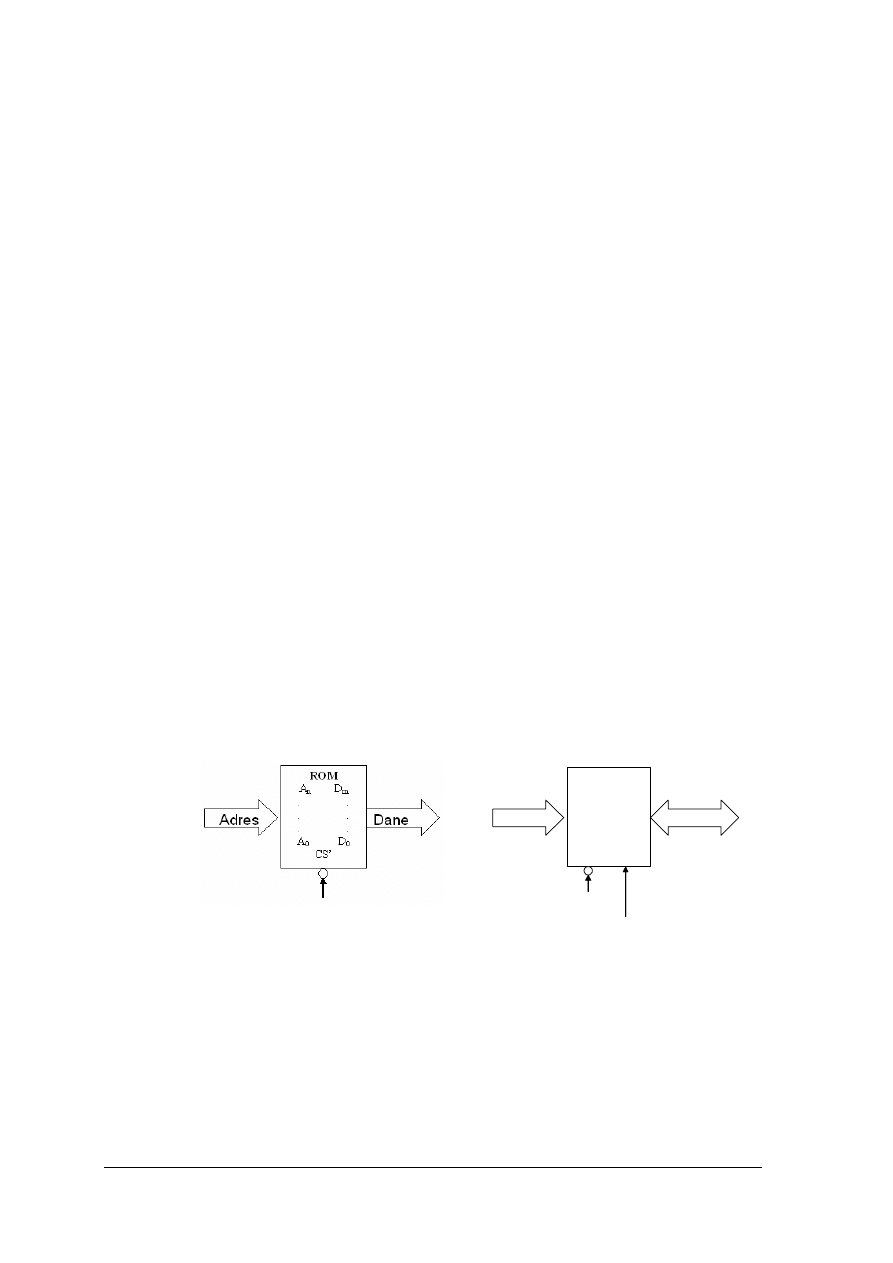

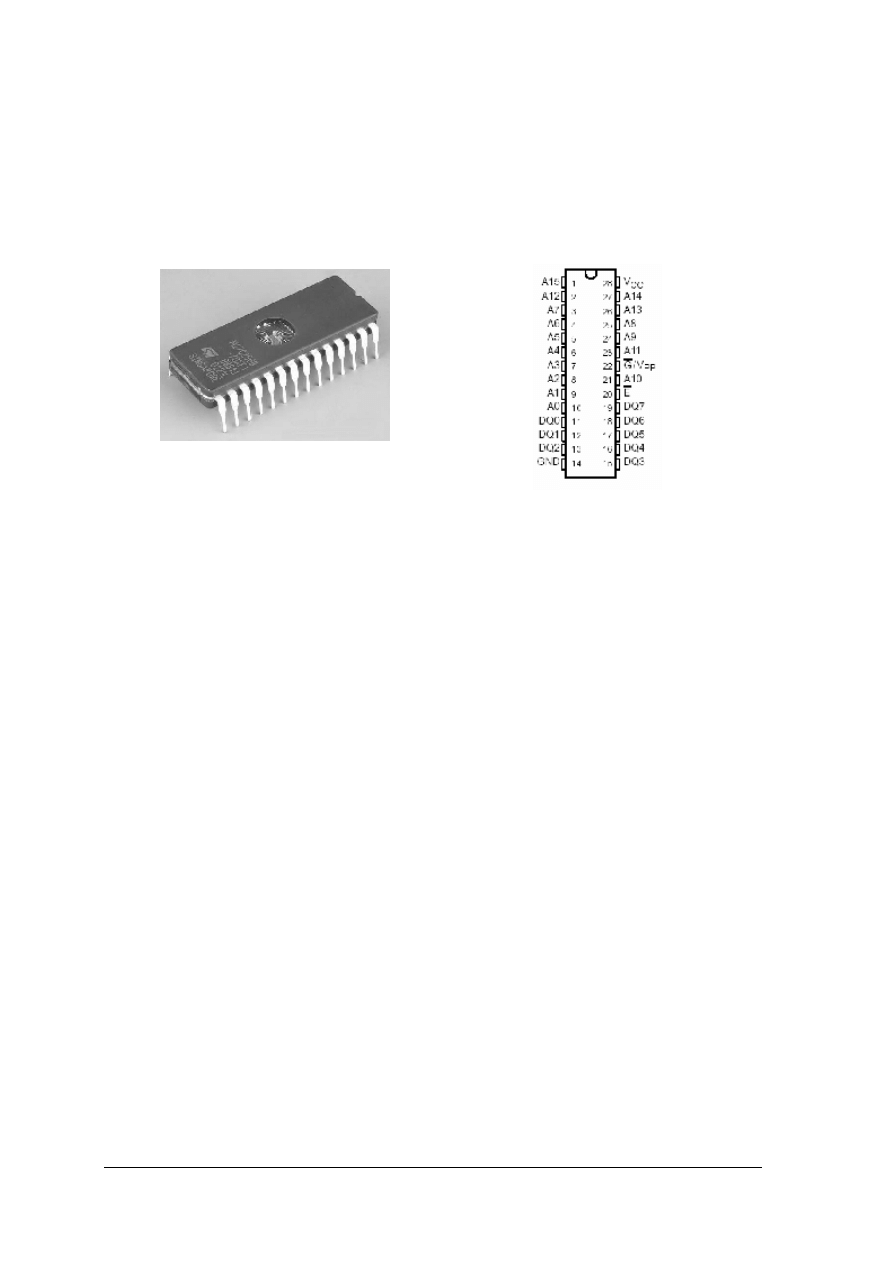

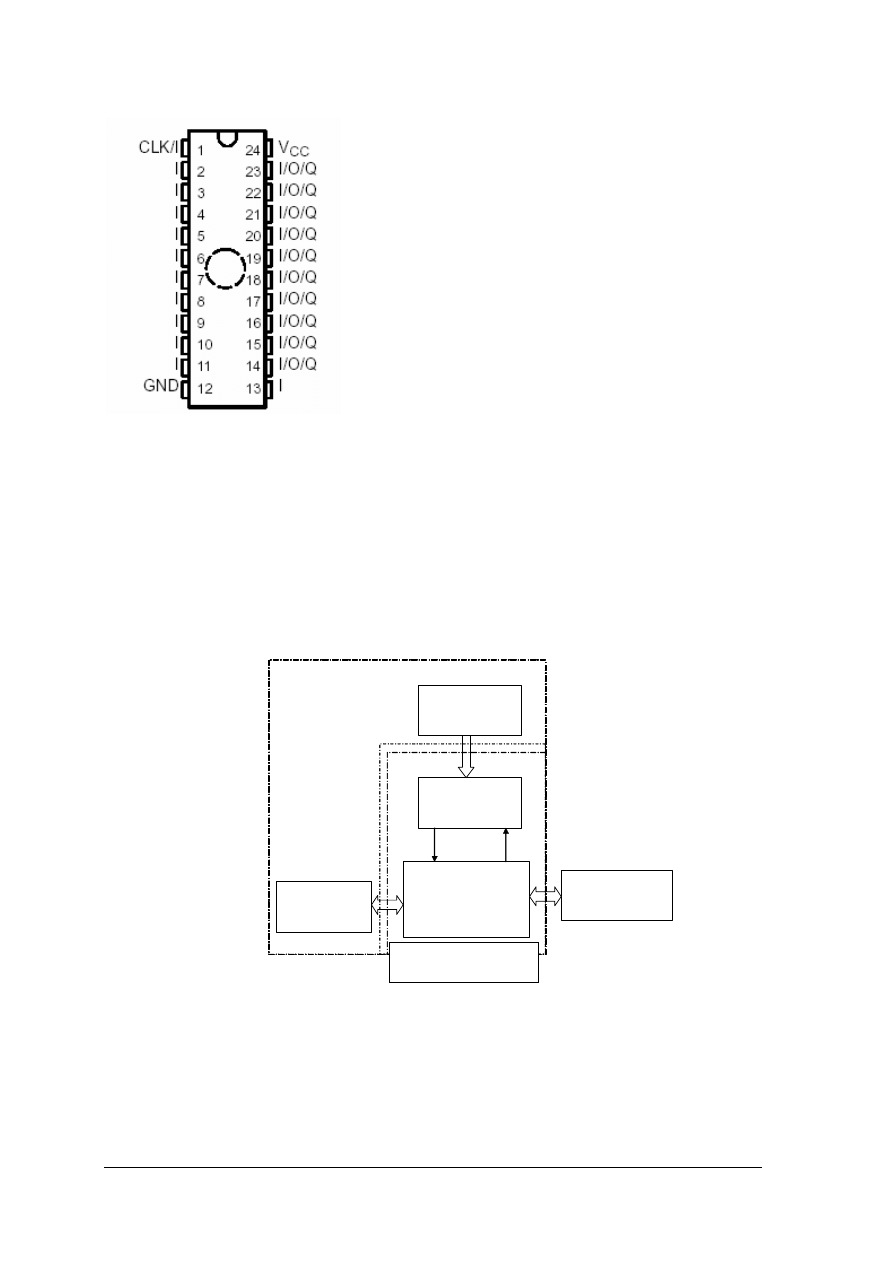

układy działają według tej samej tabeli, jednak wykresy prezentujące ich prace różnią się