Przyszłość mikroelektroniki

Wstęp

1. Technologie układów scalonych

1.1. Podziały technologii układów scalonych

1.2. Technologie układów cyfrowych

1.3. Odmiany i modyfikacje klasycznej technologii CMOS

1.4. Technologia SOI CMOS

2. Rozwój mikroelektroniki

2.1. Czynniki umożliwiające rozwój

2.2. Czynniki ograniczające rozwój

2.3. Subiektywne perspektywy rozwoju

Podsumowanie

Bibliografia

2

Wstęp

To już ostatnim moduł kursu. Przeszliśmy długą drogę, zaczynając od podstawo-

wych pojęć związanych z elektrycznością, przez elementy elektroniki cyfrowej, aż

do układów scalonych. To oczywiście jedynie mały wycinek wielkiej dziedziny wie-

dzy, jaką jest mikroelektronika. Czas więc na pewne podsumowania, uogólnienia

oraz spojrzenie w przyszłość. Zadanie to jest niezwykle trudne, gdyż mikroelektro-

nika to wciąż rozwijająca się dziedzina, w której kilka lat, a często nawet miesięcy

stanowi epokę. Nowe rozwiązania bardzo szybko są wdrażane do użycia, stare bez-

powrotnie znikają. Trudno wskazać w historii ludzkości inną dziedzinę, w której

postęp byłby tak szybki i tak odczuwalny. Dlatego też podsumowania, uogólnie-

nia, a przede wszystkim wiarygodne perspektywy na przyszłość są niezwykle trud-

ne. Często jeden wynalazek całkowicie zmienia wszystko. W module tym spróbuję

podjąć się przedstawienia perspektyw rozwoju mikroelektroniki. Chciałbym, abyś

ten moduł potraktował popularnonaukowo. Nie będę wchodził w żadne szczegó-

ły, raczej będzie to przegląd tego, co obecnie mamy oraz tego, co możemy mieć

w przyszłości.

Zacznę od uzupełnienia wiedzy na temat innych technologii układów scalonych niż

CMOS. Następnie omówię czynniki, dzięki którym możliwy jest postęp oraz te,

które go hamują. Na koniec zaprezentuję krótko nowe drogi, którymi może pójść

mikroelektronika i własną wizję jej dalszego rozwoju.

3

1. Technologie układów scalonych

Zapewne po dotychczasowej lekturze możesz odnieść wrażenie, że mikroelektro-

nika to układy cyfrowe wykonywane w technologii CMOS. Otóż nic bardziej błęd-

nego! Oczywiście najbardziej znaną i najczęściej stosowaną jest CMOS, natomiast

poza nią istnieje ogromna liczba różnych rodzajów technologii układów scalonych.

Niektóre z nich to już niemal zapomniana przeszłość, niektóre to dopiero przy-

szłość, aż wreszcie niektóre to technologie niszowe, czyli stosowane w wąskim za-

kresie. Spróbujmy te technologie usystematyzować.

1.1. Podziały technologii układów scalonych

Poniżej chciałbym przedstawić najważniejsze podziały technologii układów sca-

lonych ze względu na różne charakterystyczne czynniki. Oczywiście jak to za-

wsze w praktyce bywa, wszystkie podziały są głównie po to, aby ładnie wyglądały

w książkach i artykułach, w rzeczywistości stosuje się rozwiązania pośrednie.

Podział ze względu na sposób wykonywania układu

Produkowane układy scalone najszerzej można podzielić na następujące dwie grupy:

— warstwowe, które dalej można podzielić na:

• cienkowarstwowe,

• grubowarstwowe,

— monolityczne,

— hybrydowe.

Układy, którymi zajmowaliśmy się do tej pory to układy monolityczne, a więc wy-

konywane w i na półprzewodnikowej płytce podłożowej. W niej wykonywane są

elementy aktywne, natomiast na jej powierzchni elementy bierne oraz połącze-

nia. Nazwa monolityczne wskazuje na to, że wszystko znajduje się w jednej spójnej

strukturze, którą trudno rozdzielić. Natomiast układy warstwowe, jak sama na-

zwa wskazuje (rys. 1), mają strukturę złożona z różnych poziomów. Wykonywane

są najczęściej na podłożu izolacyjnym, np. na płytce ceramicznej, na którą

nanoszone są kolejne warstwy. Płytka podłożowa, w przeciwieństwie do

układów monolitycznych, stanowi jedynie podłoże mechaniczne i izola-

cję. Nie są w niej wykonywane żadne elementy, tak jak w płytce półprze-

wodnikowej. Nanoszone warstwy mogą mieć przeróżne własności, pełnią

rolę ścieżek przewodzących, elementów biernych, m.in. rezystorów i kon-

densatorów, a także obszarów izolacyjnych. Natomiast elementy aktyw-

ne wytwarzane są osobno i dołączane (dolutowywane) do wytworzonych warstw.

Wykonywane w układach warstwowych elementy bierne, takie jak rezystory czy

kondensatory, mają znacznie lepsze parametry niż wykonane w układach monoli-

tycznych. Rezystory mogą mieć znacznie większe rezystancje, kondensatory znacz-

nie większe pojemności, a do tego te parametry są znacznie bardziej stabilne (nie-

mal niezmienne).

Rysunek 1

Układ warstwowy

4

Osobnym tematem to, jakie to są układy cienkowarstwowe, a jakie grubowarstwo-

we. O tym, co to jest cienka, a co gruba warstwa napisano już nie jeden doktorat,

wielu specjalistów wyrażało swoje opinie i to nierzadko sprzeczne. Często to, co

w chwili obecnej jest cienką warstwą, za kilka lat jest już grubą. Rozróżnienia naj-

lepiej dokonywać, opierając się na sposobie ich wytwarzania, a nie na konkretnych

wartościach. Warstwy cienkie wytwarzane są znanymi ci już metodami: fizyczny-

mi (PVD) lub chemicznymi (CVD). Natomiast warstwy grube wytwarzane są za

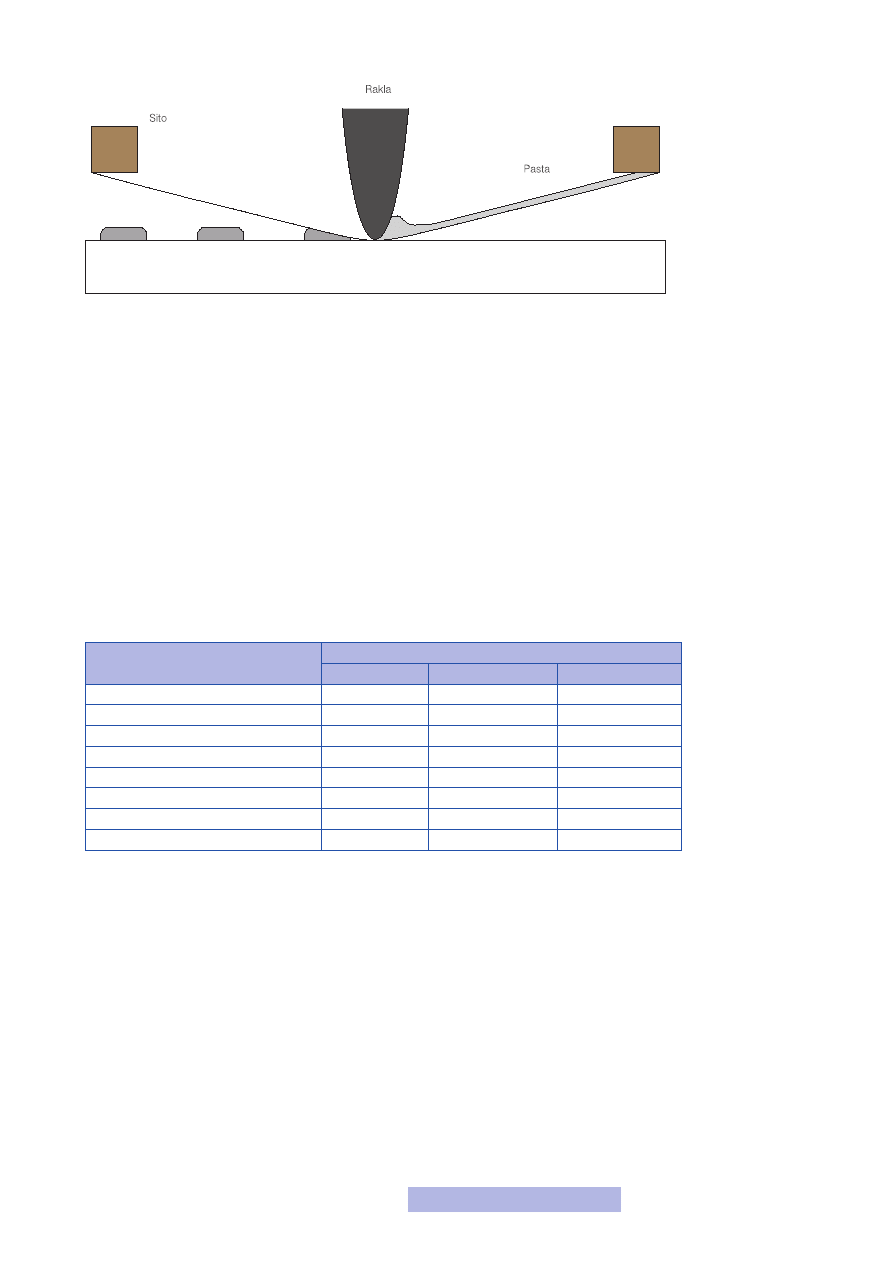

pomocą metody sitodruku (rys. 2). Polega ona na naniesieniu na sito odpowiedniej

pasty (przewodzącej, rezystancyjnej, izolacyjnej) i przeciśnięciu jej na powierzch-

nię płytki. Sito to najczęściej metalowa siatka, odsłonięta w miejscach, w których

ma być naniesiona pasta na płytkę i zasłonięta w pozostałych. Po przeciągnięciu

przez sito rakli, pasta jest umieszczana na płytce i następnie poddawana procesowi

utwardzania, najczęściej w wysokiej temperaturze. I w ten prosty sposób powstają

kolejne warstwy. Wytwarzanie układów grubowarstwowych jest naprawdę proste

— sam miałem okazję własnoręcznie taki układ wykonywać. Oczywistą wadą tej

technologii jest niska dokładność.

Cecha technologii

Technologia

Monolityczna

Cienkowarstwowa

Grubowarstwowa

Upakowanie elementów

Ogromne

Średnie

Małe

Zakresy rezystorów i kondensatorów Małe

Duże

Bardzo duże

Stałość parametrów

Średnia

Bardzo duża

Duża

Częstotliwość pracy

Bardzo duża

Bardzo duża

Duża

Rozpraszana moc

Średnia

Duża

Bardzo duża

Niezawodność

Duża

Duża

Średnia

Koszty uruchomienia produkcji

Ogromne

Średnie

Małe

Koszt układu przy seryjnej produkcji Bardzo mały

Średni

Średni

Zapewne w tej chwili myślisz, że układy scalone warstwowe to pewnie już prze-

szłość — ładnie pasują do podziału, więc dlatego zostały tu umieszczone, a i tak

wszystko wykonywane jest jako układy scalone monolityczne (technologia CMOS

to technologia monolityczna). Otóż nie! Układy warstwowe przez cały czas miały

swoje niszowe zastosowania, natomiast ostatnio przeżywają renesans. Są one łączo-

ne z układami monolitycznymi — na płytce montowane są monolityczne układy,

wykonywane są duże elementy bierne oraz połączenia między nimi. Tak powstaje

tzw. układ hybrydowy, będący połączeniem technologii monolitycznej i warstwo-

wej. Dzięki zastosowaniu układów hybrydowych nie trzeba już dołączać zewnętrz-

nych elementów dyskretnych, dzięki czemu układ staje się tańszy oraz zwiększa się

jego niezawodność. Z zewnątrz układ taki nie różni się praktycznie od zwykłego

scalaka, najczęściej jest również zalewany w żywicy. Hybrydowe układy scalone są

niewątpliwie jedną z prawdopodobnych dróg rozwoju mikroelektroniki. Obecnie

na całym świecie prowadzi się bardzo wiele prac w tej dziedzinie i z tymi układami

wiąże się duże nadzieje na przyszłość.

Rysunek 2

Wytwarzanie układu

grubowarstwowego

Tabela 1

Wady i zalety poszczególnych

technologii scalonych

5

Podział ze względu na rodzaj zastosowanych elementów aktywnych

Innym, bardzo często stosowanym podziałem jest podział ze względu na rodzaj

użytych elementów aktywnych, a konkretniej tranzystorów. Jak pamiętasz, w mo-

dule drugim wyróżniliśmy dwie grupy tranzystorów i w zależności od tego, które

z nich zastosujemy, wyróżniamy układy:

— bipolarne,

— unipolarne,

— hybrydowe.

Technologia CMOS stosuje tranzystory MOS, czyli tranzystory unipolarne, należy

ją więc zaliczyć do technologii unipolarnych. Posiada ona następujące cechy:

— stosunkowo prosta i tania technologia wytwarzania,

— niski pobór mocy,

— bardzo duża gęstość upakowania i łatwość miniaturyzacji,

— akceptowalne częstotliwości pracy,

— łatwość wykonania cyfrowych układach scalonych.

Zwróć szczególnie uwagę na trzy pierwsze cechy, gdyż to one są odpowiedzialne za

obecną popularność i przewagę technologii unipolarnych. Technologia unipolar-

na może naturalnie wykorzystywać także inne tranzystory unipolarne — np. JFET

czy MESFET. Te ostatnie są wykorzystywane przy budowie szybkich układów dla

potrzeb telekomunikacji. Obecnie prowadzi się badania pozwalające na wykony-

wanie w jednym układzie scalonym różnych typów tranzystorów unipolarnych, co

zapewnia jak najlepsze wykorzystanie własności poszczególnych tranzystorów. Na-

tomiast technologia bipolarna posiada następujące cechy:

— dobre własności szybkościowe przy przełączaniu,

— niski poziom szumów,

— stosunkowo skomplikowana technologia wytwarzania (co podnosi koszty),

— wysoki pobór mocy,

— zastosowanie głównie w specjalistycznych układach scalonych.

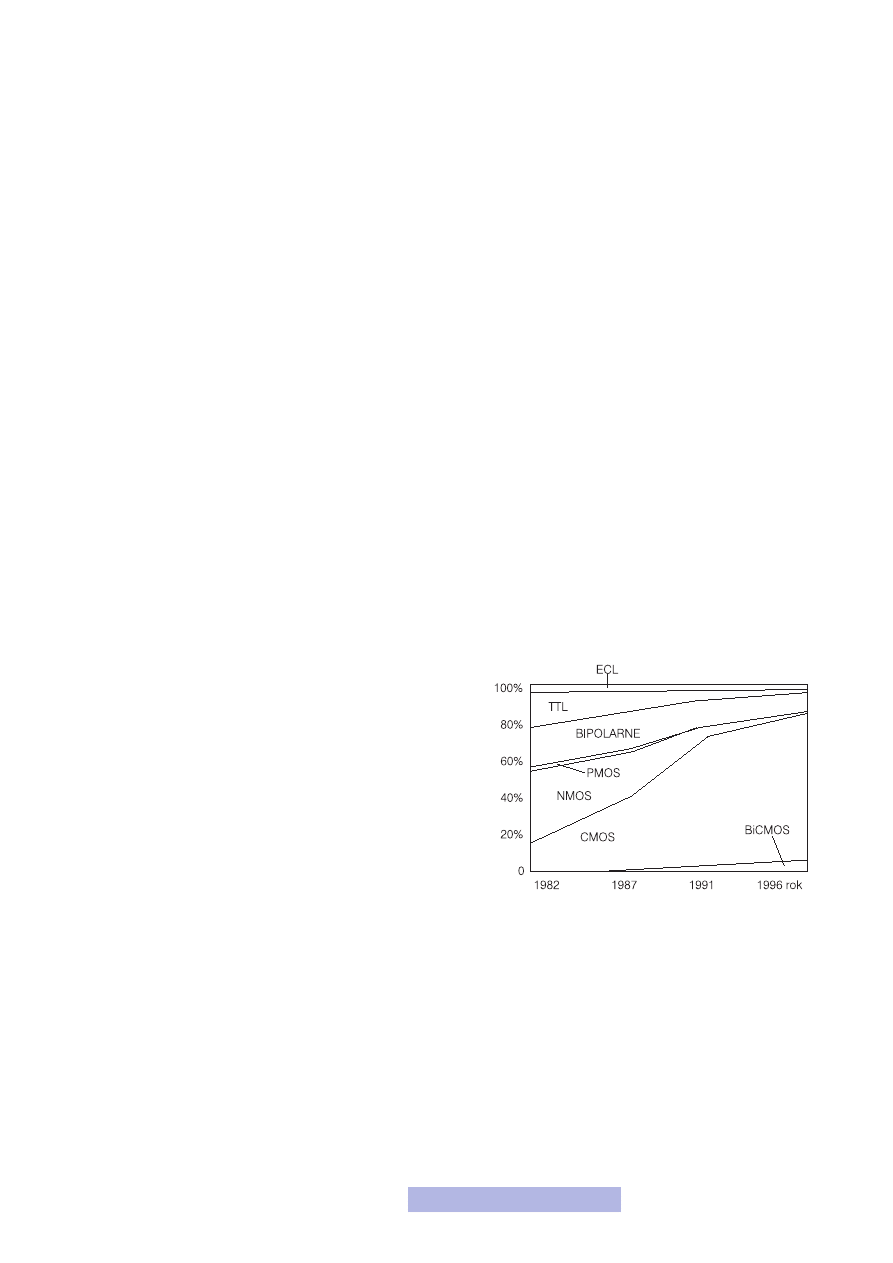

Chciałbym w tym miejscu rozwiać jeden mit, pokutujący

nawet wśród osób zawodowo związanych z elektroniką, że

technologie bipolarne są wolne. Otóż zdecydowanie nie! Są

one szybsze niż unipolarne — najszybsza obecnie technolo-

gia to technologia bipolarna. Mimo tak wielu istotnych za-

let, układy scalone bipolarne mają też dwie bardzo poważne

wady, a mianowicie duży pobór mocy oraz trudności w scala-

niu i miniaturyzacji. Głównie z tych względów technologia ta

cały czas zmniejsza swój udział w rynku układów scalonych

i raczej nie zmieni się to w najbliższym czasie (rys. 3).

Oczywiście najlepiej byłoby wykorzystać zalety obu techno-

logii i nad tym właśnie obecnie prowadzone są prace. Tak po-

wstała technologia hybrydowa, której najbardziej znanym przedstawicielem jest

BiCMOS. Z nią wiązane są duże nadzieje na przyszłość, jeśli chodzi o monolitycz-

ne układy scalone.

Podział ze względu na liczbę elementów

Ostatnim podziałem jest podział ze względu na liczbę elementów znajdujących się

w układzie, czyli tzw. stopień scalenia. Kierując się nim, wyróżniono następujące

grupy:

— SSI (Small Scale Integration) — układy o małym stopniu scalenia, do kilkudzie-

sięciu elementów w strukturze,

— MSI (Medium Scale Integration) — układy o średnim stopniu scalenia, do kilku-

set elementów w strukturze,

Rysunek 3

Udział poszczególnych

technologii w rynku

6

— LSI (Large Scale Integration) — układy o dużym stopniu scalenia, do kilku (a na-

wet często kilkudziesięciu) tysięcy elementów w strukturze,

— VLSI (Very Large Scale Integration) — układy o bardzo dużym stopniu scalenia,

o liczbie elementów przekraczającej sto tysięcy,

— ULSI (Ultra Large Scale Integration) — układy o ogromnym stopniu scalenia,

o liczbie elementów przekraczającej milion.

Podział ten, choć najbardziej obrazowy, jest w praktyce najrzadziej stosowany. Nie

zawsze istnieje przecież potrzeba integracji ogromnej liczby elementów, choć do

tego może zostać użyta technologia bardzo zaawansowana. Zatem podział taki zu-

pełnie nie oddaje zaawansowania użytej technologii. Obecnie przyjęło się, aby mia-

nem VLSI określać po prostu układy scalone.

1.2. Technologie układów cyfrowych

Niewątpliwie najważniejsze dla nas są układy cyfrowe. Do tej pory poznałeś spo-

soby ich projektowania oraz wytwarzania w technologii CMOS. Jest to wiodąca

obecnie technologia (rys. 3) i — póki co — nic nie wskazuje na to, aby ten trend

mógł się w najbliższej przyszłości zmienić. Niemniej jednak nie chciałbym, abyś

pomyślał, że jest to jedyna słuszna technologia. Nic podobnego! Inne technologie

istnieją i mają się całkiem dobrze, ewentualnie nie są już stosowane i mają zasłużo-

ne miejsce w historii elektroniki. Omówienie, nawet pobieżne, każdej z nich, to co

najmniej jeden temat i dlatego chciałbym teraz wymienić i krótko scharakteryzo-

wać najważniejsze z nich.

Technologie bipolarne:

— RTL (Resistor-Transistor Logic) — układy rezystorowo-tranzystorowe, obecnie

nie są już produkowane,

— DCTL (Direct-Coupled Transistor Logic) — układy z tranzystorami sprzężony-

mi bezpośrednio, obecnie nie są już produkowane,

— DTL (Diode-Transistor Logic) — układy diodowo-tranzystorowe, obecnie nie są

już produkowane, ale były bardzo popularne w latach 60. XX w.,

— TTL (Transistor-Transistor Logic) — układy tranzystorowo-tranzystorowe; bar-

dzo popularne w latach 70. i 80. XX w., szczególnie w układach średniego stop-

nia scalenia, przyczyniły się do ogromnego postępu (duża szybkość działania,

szczególnie w przypadku technologii Schottky TTL), obecnie są już coraz rza-

dziej spotykane,

— ECL (Emiter-Coupled Logic) — układy z tranzystorami o sprzężonych emite-

rach, stosowane do dziś w bardzo szybkich układach o małym i średnim stop-

niu scalenia,

— I

2

L (Integrated Injection Logic) oraz I

3

L (Isolierte Integreted Injection Logic)

— układy iniekcyjne, układy bipolarne, które łączącą w sobie zalety technolo-

gii bipolarnej (szybkość przełączania) oraz unipolarnej (mały pobór mocy oraz

duża gęstość upakowania), które mimo tych zalet nie zdobyły do tej pory zna-

czącej pozycji na rynku układów scalonych.

Technologie unipolarne:

— PMOS — układy zbudowane z tranzystorów MOS z kanałem typu Pp i bramką

aluminiową, największą ich zaletą są bardzo niskie koszty wytwarzania, obecnie

nie są już produkowane,

— NMOS — układy zbudowane z tranzystorów MOS z kanałem typu N i bram-

ką polikrzemową, powszechnie stosowane w latach 70. i 80. XX w., obecnie już

coraz rzadziej spotykane,

7

— CTD (Charge-Transfer-Devices) — rodzina układów z przenoszeniem ładunku

(najważniejsza grupa CCD — układy o sprzężeniu ładunkowym), z którą wią-

zano największe, póki co niepotwierdzone, nadzieje,

— CMOS (Complementary MOS) — układy zbudowane z komplementarnych tran-

zystorów MOS z kanałem typu P i N, jest to najpowszechniej obecnie stosowana

technologia (według najnowszych szacunków ponad 90% układów scalonych),

dla której trudno obecnie wskazać konkurencję, mogącą nawet w perspektywie

kilku lat zagrozić jej pozycji,

— SOI CMOS (Silicon On Insulator CMOS) — układy zbudowane w technologii

CMOS na podłożu izolacyjnym, technologia obecnie lansowana jako ta, która

w przyszłości może zastąpić CMOS-y.

Technologie hybrydowe:

— BiCMOS (Bipolar CMOS) — układy zbudowane z tranzystorów bipolarnych,

wykonanych w technologii CMOS, technologia rozwijająca się i trudno przewi-

dzieć perspektywy jej rozwoju.

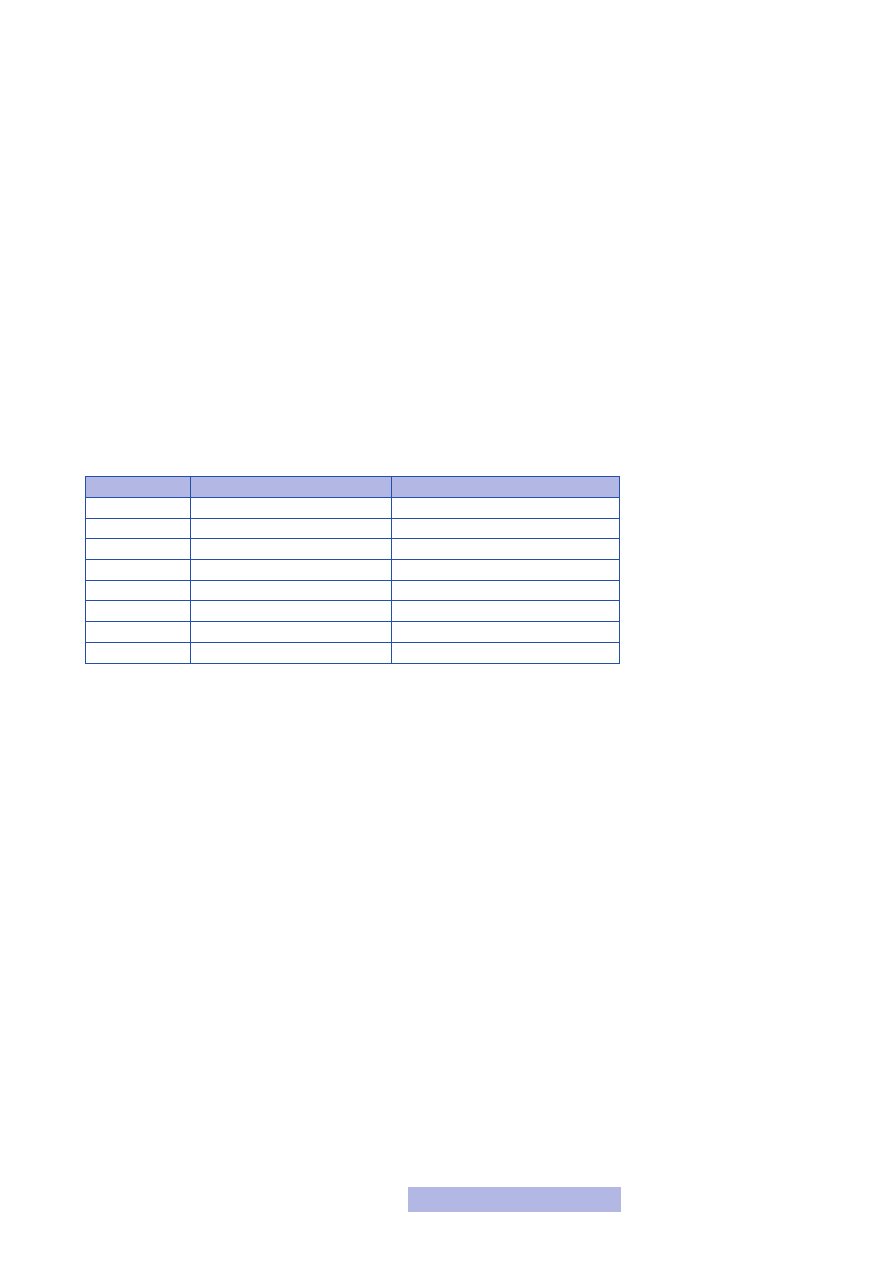

Na podstawie krótkich opisów każdej z technologii trudno oczywiście porównać je

ze sobą. Dlatego w poniższej tabeli zestawione zostały wybrane technologie oraz naj-

ważniejsze dane charakteryzujące każdą z nich — czas opóźnienia oraz straty mocy.

Technologia

Czas opóźnienia bramki [ns]

Straty mocy na bramkę [mW]

TTL

10,0

10,0

Schottky TTL

5,0

2,0

ECL

0,5

50,0

I2L

15,0

0,5

NMOS

12,5

0,5

CMOS

10,0

0,1

SOI CMOS

7,5

0,1

BiCMOS

0,75

1,0

Powyższe dane są już przestarzałe, gdyż pochodzą z lat 90. ubiegłego wieku. Obec-

nie dla technologii CMOS opóźnienia na bramkach są rzędu kilku do kilkunastu

pikosekund (10

–12

), a pozostałe trudno w ogóle odnaleźć. Natomiast tendencje są

niewątpliwie zachowane. Chciałbym, abyś na ich podstawie porównał jak duże są

starty mocy w układach bipolarnych i jednocześnie jak szybkie są one w porówna-

niu do układów unipolarnych.

Reasumując, technologia unipolarna CMOS jest obecnie wiodąca — głównie ze

względu na bardzo dobre możliwości scalania dużej liczby elementów. Technologia

bipolarna, choć lepsza pod względem szybkości, nie pozwala jednak na integrację

zbyt dużej liczby elementów.

Do tej pory w ogóle nic nie mówiliśmy o układach scalonych analogowych. Wy-

nika to po pierwsze z ograniczonej objętości kursu, a po drugie liczba produko-

wanych układów cyfrowych jest procentowo znacznie większa niż układów analo-

gowych. Niemniej jednak chciałbym krótko wyjaśnić co to są układy analogowe.

Otóż są to układy, na wejściach i wyjściach których może pojawić się sygnał o do-

wolnej wartości z określonego przedziału. Jak pamiętasz, w układach cyfrowych

na wejściach i wyjściach mieliśmy 0 lub 1, a z punktu widzenia elektroniki były to

napięcia 0 V lub napięcie zasilania. W układach analogowych na wejściach i wyj-

ściach może pojawić się dowolne napięcie z określonego przedziału. Przykładem

układu analogowego jest choćby wzmacniacz — kiedy na wejściu pojawi się jakiś

sygnał, to na wyjściu jest on odpowiednio wzmocniony (powiększony). Sygnał wej-

ściowy może przyjmować dowolne wartości z podanego zakresu i każdy taki sy-

Tabela 2

Opóźnienia i straty mocy

w różnych technologiach

monolitycznych układów

scalonych

8

gnał zostanie wzmocniony. Innym przykładem układu analogowego jest kompara-

tor analogowy, który ma za zadanie porównanie dwóch sygnałów (stwierdzenie,

który z nich ma np. większą wartość napięcia).

Scalone układy analogowe są zdecydowanie trudniejsze w projektowaniu i anali-

zie działania oraz mają mniejsze znaczenie z punktu widzenia informatyki, dlatego

szczerzej nie będziemy się nimi zajmować. Chciałbym, abyś wiedział, że takie ukła-

dy istnieją i można je wykonywać w formie scalonej.

1.3. Odmiany i modyfikacje klasycznej technologii CMOS

Układy scalone produkowane w technologii CMOS zdominowały współczesną mi-

kroelektronikę, a swoją pozycję zawdzięczają głownie następującym cechom:

— bardzo małemu poborowi mocy,

— możliwościom pracy w szerokim zakresie temperatur,

— możliwościom pracy w szerokim zakresie napięć zasilania,

— dużym marginesom szumów,

— odporności na promieniowanie,

— dużej różnorodności rozwiązań układowych,

— stosunkowo prostej i taniej technologii produkcji.

Naturalnie technologia ta nie jest pozbawiona wad, ale, jako że w tej chwili nie ma

lepszej, jest ona niezagrożonym liderem. Jednak i sama technologia CMOS ule-

ga istotnym i ważnym modyfikacjom. Można wyróżnić trzy podstawowe warianty

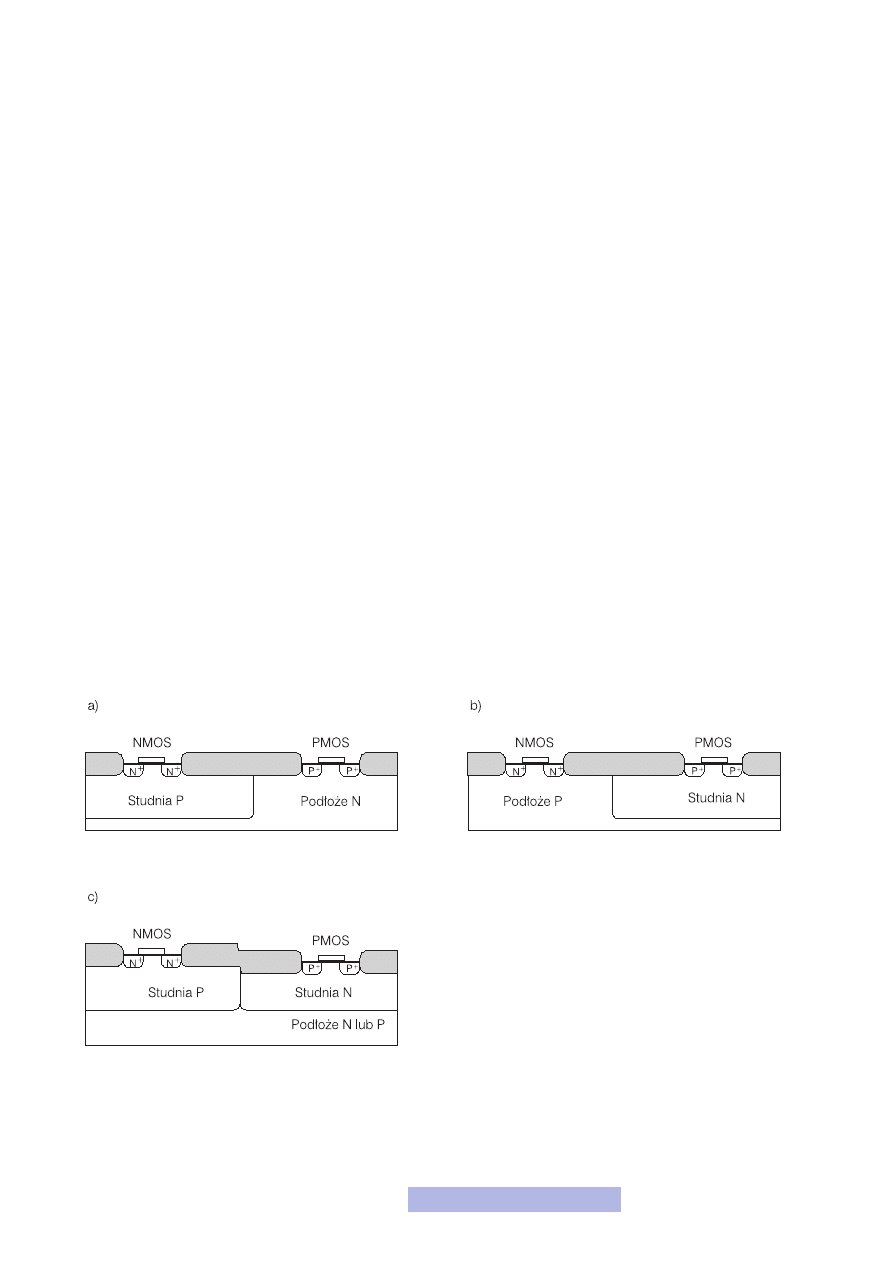

technologii CMOS (rys. 4):

— ze studnią typu P,

— ze studnią typu N,

— z podwójna studnią.

Przedstawiona w module czwartym technologia CMOS to technologia ze stud-

nia typu N. Dwie pierwsze mają obecnie jedynie wartość dydaktyczną, a wszystkie

układy wykonywane są w technologii z podwójną studnią. Takie podejście wyni-

ka z reguł skalowania i konieczności coraz silniejszych domieszkowań podłoży obu

Rysunek 4

Warianty technologii CMOS

9

tranzystorów. Płytki podłożowe mają w takim wypadku zbyt małą koncentrację do-

mieszek i dlatego należy wykonywać dodatkowe studnie. Co więcej, takie rozwiąza-

nie gwarantuje mniejsze oddziaływanie poszczególnych przyrządów na siebie.

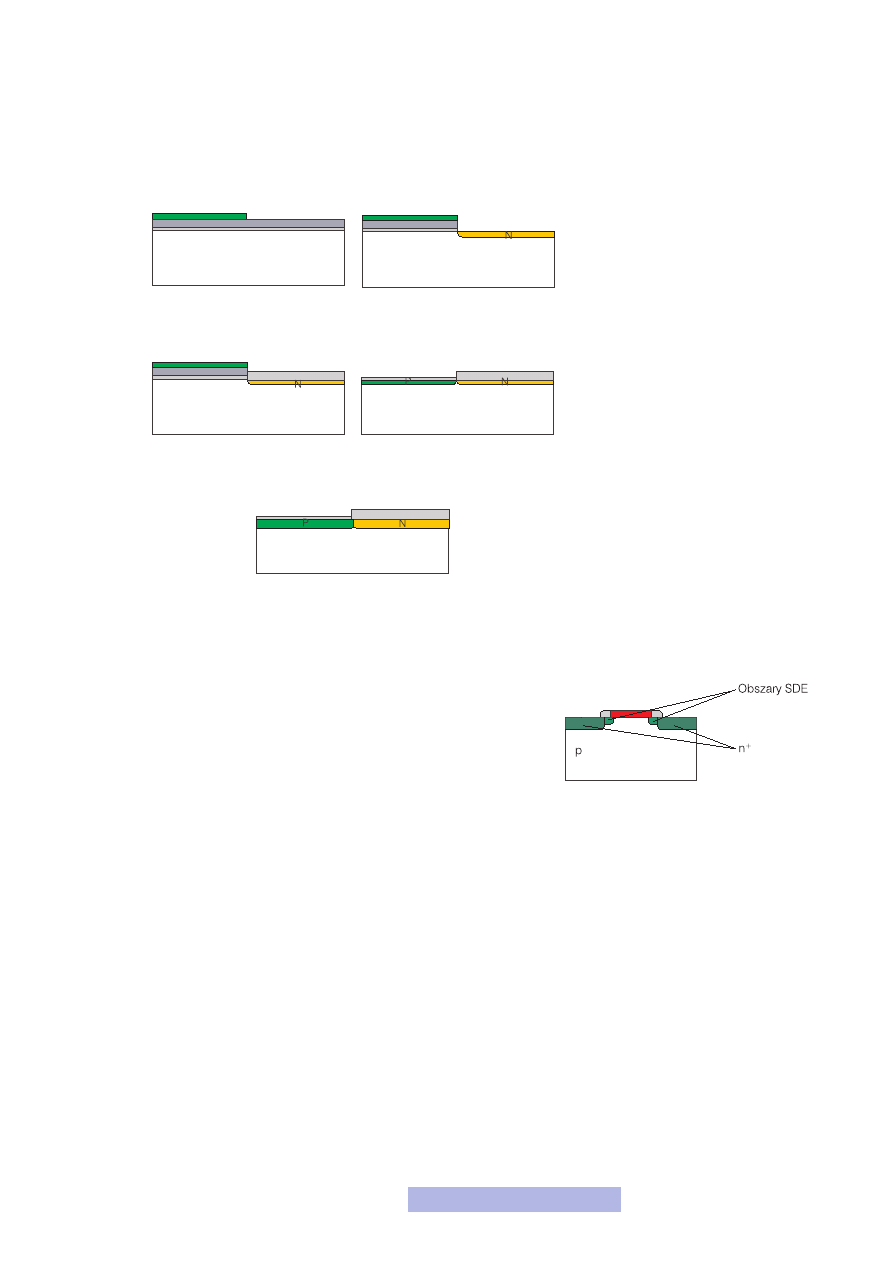

W przypadku technologii z podwójną studnią proces technologiczny należy zacząć

od wytworzenia dwóch studni, co pokazują poniższe rysunki:

1. Nałożenie fotorezystu,

maskowanie, naświetlanie

i wywołanie

2. Wytrawienie tlenku i azotku

krzemu, a następnie implan-

tacja studni typu N

3. Wytworzenie warstwy

grubego tlenku

4. Usunięcie fotorezystu,

wytrawienie azotku krzemu

oraz implantacja studni typu P

5. Wygrzewanie

Dalej proces przebiega analogicznie jak w przypadku technologii z pojedynczą

studnią.

Kolejną ważną modyfikacją jest zastosowanie, zamiast klasycznych tran-

zystorów MOS, tranzystorów LDD MOS (Lightly Doped Drain), czy-

li rozszerzenia klasycznego MOS-a o obszary słabego domieszkowa-

nia w obszarach źródła i drenu (rys. 6). Obszary te noszą nazwę SDE

(Source Drain Extension). Są wprowadzane, aby wyeliminować tzw.

efekt gorących nośników. Zainteresowanych tym zagadnieniem odsyłam

do literatury.

Tak więc możesz wyobrazić sobie jak bardzo w rzeczywistości komplikuje się przed-

stawiony w module czwartym proces produkcji komórki elementarnej CMOS. Wy-

konując małe tranzystory, musisz użyć wymienionych wyżej modyfikacji i nie tylko

ich! Takich zmian i dodatków jest w rzeczywistości znacznie więcej. Przedstawio-

ne powyżej są najważniejszymi i dotyczą jedynie zmian w budowie układów. Nato-

miast bardzo wiele modyfikacji wynika ze zmiany procesu wytwarzania pewnych

elementów. Przykładem może być technologia LOCOS wytwarzania tlenków polo-

wych. Ogólnie — im więcej modyfikacji, tym bardziej komplikuje się procesor wy-

twarzania. Dochodzą kolejne etapy produkcji, kolejne procesy technologiczne, co

z jednej strony powoduje zwiększenie kosztów, a z drugiej zmniejszenie niezawod-

ności. Jednak chcąc produkować coraz mniejsze elementy, trzeba koniecznie te mo-

dyfikacje wprowadzać i nie ma od tego odwrotu.

Rysunek 5

Wytwarzanie podwójnej studni

Rysunek 6

Tranzystor z SDE

10

1.4. Technologia SOI CMOS

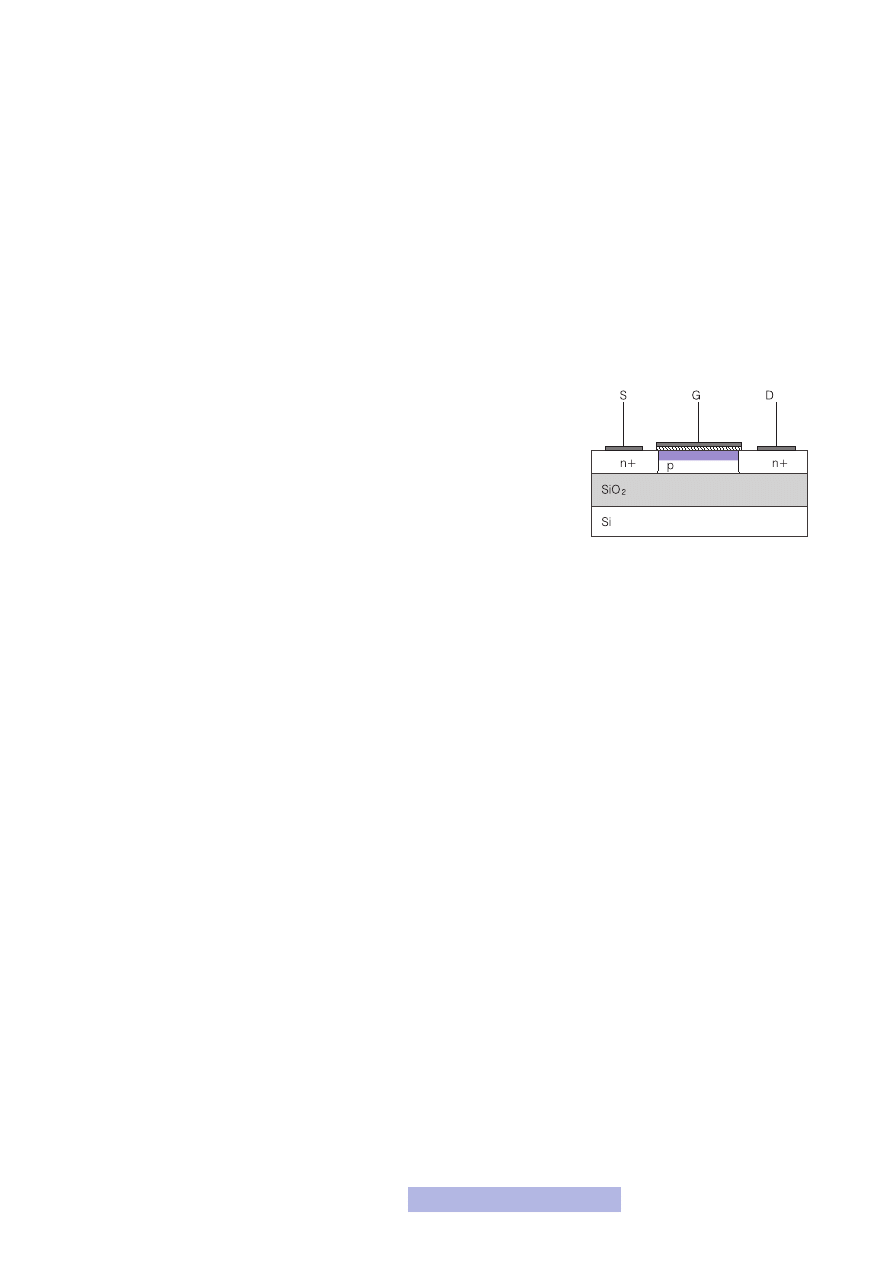

Technologia SOI CMOS (Silicon On Insulator CMOS) stanowi rozwinięcie kla-

sycznej technologii CMOS i umożliwia wyeliminowanie jej niektórych wad i ogra-

niczeń, zapewnia także sporo całkiem nowych możliwości. Wywodzi się ona z za-

proponowanej już w latach 60. XX w. technologii SOS (Silicon On Sapphire), opra-

cowanej wówczas dla potrzeb przemysłu militarnego. Miała ona zapewnić odpor-

ność na promieniowanie oraz większa szybkość działania, jednak ze względu na

bardzo wysokie koszty nigdy nie znalazła zastosowania na masową skalę. Teraz

jednak takie możliwości się otwierają, a ograniczenia powodowane przez klasycz-

nego CMOS-a, dają dodatkową motywację do prac nad tą technologią. Technolo-

gii SOI CMOS chciałbym poświęcić trochę więcej uwagi niż pozostałym rozwią-

zaniom, gdyż osobiście uważam ją za technologię, o której niedługo studenci będą

uczyli się jako o technologii podstawowej.

Cała zmiana w stosunku do klasycznej technologii CMOS polega tylko

(a może i aż) na zmianie podłoża (rys. 7). W klasycznej technologii przy-

rząd wykonywany jest w jednolitej płytce podłożowej. Natomiast w tech-

nologii SOI przyrządy wykonywane są w cienkiej monokrystalicznej war-

stwie krzemu oddzielonej od reszty podłoża krzemowego warstwą izolacyj-

ną, którą najczęściej jest po prostu dwutlenek krzemu. Pozostałe procesy

wytwarzania przyrządów są identyczne jak w przypadku klasycznej techno-

logii CMOS. Zmiana wydawałoby się niewielka, jednak jej konsekwencje są

ogromne, a mianowicie:

— całkowite wyeliminowanie efektu zatrzaskiwania oraz niektórych elementów

pasożytniczych,

— zmniejszenie powierzchni złącz, dzięki czemu uzyskuje się mniejsze prądy upły-

wu oraz wzrost szybkości działania (np. dzielnik częstotliwości zrealizowany

w technologii SOI jest dwukrotnie szybszy i zużywa dwukrotnie mniej mocy niż

wykonany klasycznie),

— możliwość pracy w zakresie wyższych temperatur (nawet do 400

o

C), a co za

tym idzie, poprawa jakości i niezawodności przyrządów,

— wzrost odporności na promieniowanie (średnio około stukrotny w stosunku do

klasycznych rozwiązań),

— gęstsze upakowanie,

— redukcja wpływu efektów krótkiego kanału, a co za tym idzie lepsze możliwo-

ści minimalizacji,

— możliwość tworzenia zupełnie nowych przyrządów, tzw. tranzystorów VI-MOS

(Volume Inversion MOS),

— możliwość tworzenia układów trójwymiarowych (3D), co pozwala na uzyskanie

niezwykle dużej gęstości upakowania oraz na redukcję połączeń.

Łatwo zauważyć, iż technologia SOI oferuje zupełnie nowe możliwości, korzystając

jednocześnie z dotychczasowych osiągnięć technologii CMOS. Jeśli tylko zmienisz

podłoże i nic więcej, to już uzyskujesz lepszy efekt. A jeśli jeszcze dodatkowo zop-

tymalizowałbyś układy pod tę technologię, poprawa byłaby zwielokrotniona. Za-

pewne w tym momencie zapytasz czemu nie wykonuje się w takim razie układów

w tej technologii. Odpowiedz tkwi w... podłożach. Są one stosunkowo trudne do

wytworzenia i drogie. Niby zmiana polega tylko na wprowadzeniu dodatkowego

tlenku, ale okazuje się, że w praktyce nie jest to takie proste do wykonania. Jednak

w tej dziedzinie również obserwuje się znaczny postęp. Powstają zupełnie nowe

metody produkcji, wśród których należy wymienić następujące:

— SIMOX (Separation by Implanted Oxygen) — polega na implantacji jonów tlenu

na określoną głębokość do wnętrza płytki krzemowej, a następnie wygrzewa-

niu, w wyniku którego powstaje warstwa tlenku krzemu; jest to niewątpliwie

Rysunek 7

Budowa tranzystora SOI MOS

11

najbardziej rozwinięta i najpopularniejsza technologia, jednak jej wadami są:

konieczność stosowania kosztownych implantatorów, powstawanie uszkodzeń

sieci krystalicznej oraz wprowadzania dodatkowych zanieczyszczeń,

— BESOI (Bonded-Etched SOI) — polega na zgrzewaniu dwóch płytek, z których

przynajmniej jedna ma utleniona powierzchnię; wadą metody są duże straty ma-

teriałowe oraz uzyskiwanie stosunkowo grubych warstw krzemu,

— ELO (Epitaxial Lateral Overgrowth) — polega na epitaksjalnym wzroście war-

stwy krzemu na tlenku; jej wadą są trudności z uzyskaniem jednorodności war-

stwy oraz koszty; technologia ta jest najczęściej stosowana przy produkcji ukła-

dów trójwymiarowych,

— ZMR (Zone Melting Recrystallization) — polega na nanoszeniu na izolator war-

stwy polikrzemu, która następnie pod wpływem temperatury ulega rekrystali-

zacji w krzem monokrystaliczny; jej wady są takie same jak w przypadku ELO,

— FIPOS (Full Isolation by Porous Oxidized Silicon) — polega na przekształceniu

warstwy krzemu w krzem porowaty i jego utlenieniu w trakcie procesów two-

rzeni przyrządów, np. utleniania bramkowego; jest to najdoskonalsza techno-

logia, jednak jej wadą jest to, że podłoże jest wytwarzane w trakcie procesów

technologicznych tworzenia przyrządów.

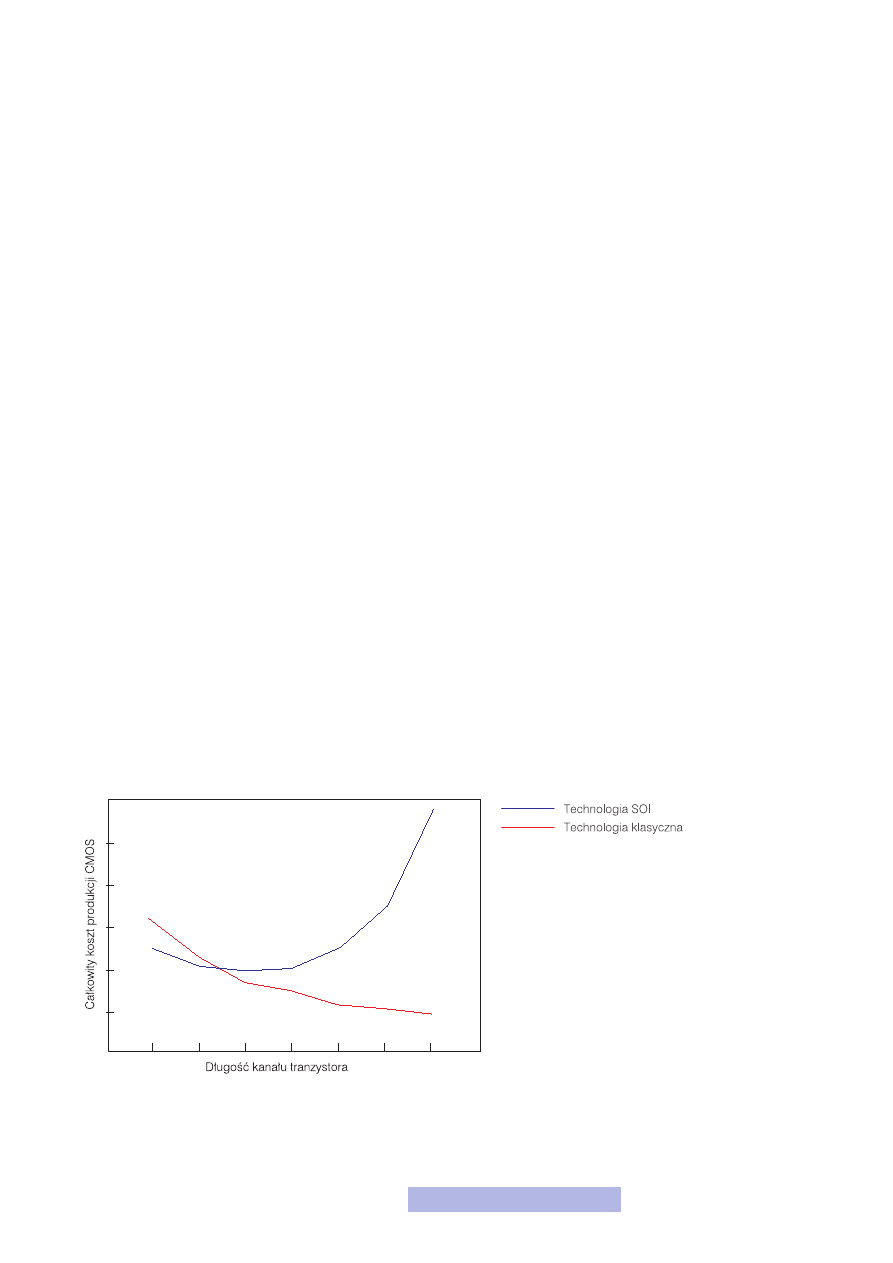

Trudno obecnie wnioskować na temat przyszłości i perspektyw rozwoju techno-

logii SOI, choć coraz częściej i odważniej jest ona lansowana jako następca kla-

sycznej technologii CMOS. Z całą odpowiedzialnością można natomiast stwier-

dzić, iż technologia ta bardzo dynamicznie rozwija się, wzbudzając coraz większe

zainteresowanie. Co ważne, powoli wychodzi ona z laboratorium i „kieruje się”

w stronę fabryk i komercyjnych laboratoriów rozwojowych. Niewątpliwie najwięk-

szą przeszkodą jest obecnie cena, a dokładniej koszty i rozmiary podłoży. Jednak

wraz z jej upowszechnianiem ceny niewątpliwie będą malały. Co więcej, koszty

produkcji małych tranzystorów w technologii SOI są zbliżone, a nawet nieco niż-

sze niż w technologii klasycznej (rys. 8). Tak więc koszty zbliżone, a parametry

lepsze. Co więcej, dalej jest to technologia CMOS, a więc zaprojektowane topo-

grafie nie będą wymagały istotnych zmian, wszystkie istniejące już projekty będzie

można bez przeszkód i większych zmian wykonać. A co dla ciebie ważne: wszystko

czego się do tej pory nauczyłeś w trakcie kursu, będzie aktualne w nowej technolo-

gii! Układy będzie projektowało się identycznie, a wykonywało bardzo podobnie.

Można więc wykorzystać dotychczasową infrastrukturę, wiedze i doświadczenie.

Myślę, że są to wystarczające argumenty, aby zainteresować się technologią SOI.

Rysunek 8

Koszty produkcji tranzystorów

12

2. Rozwój mikroelektroniki

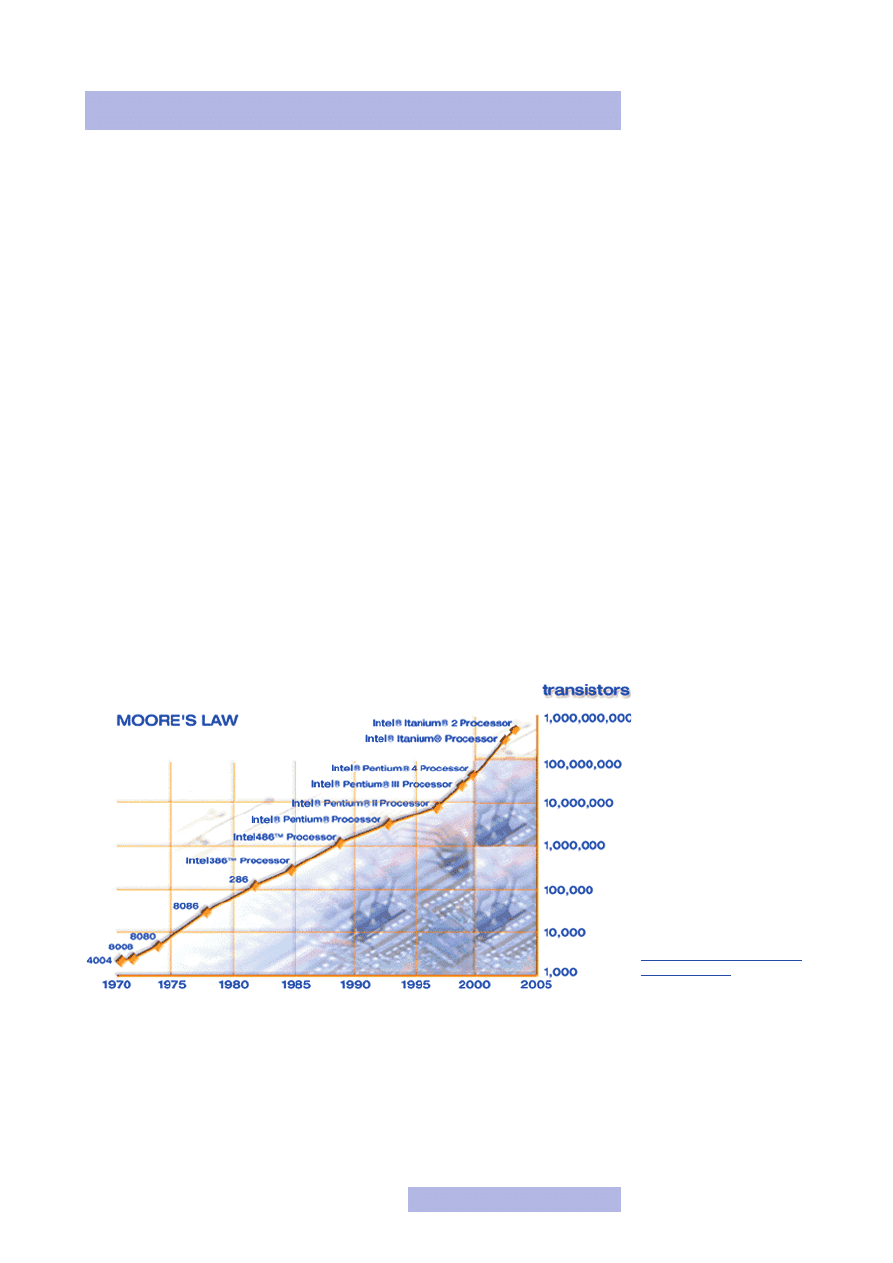

Rozwój mikroelektroniki można opisywać wieloma wskaźnikami. Najbardziej

„medialna” i przemawiająca do wyobraźni jest liczba elementów w największym

układzie scalonym, dostępnym w danym okresie na rynku. Jest to o tyle miarodaj-

ny wskaźnik, że wraz ze wzrostem liczby elementów w układzie muszą być one co-

raz mniejsze, musi być między tymi elementami coraz więcej połączeń, a więc może

on dość dobrze określić stopień zaawansowania technologii. Jednak wskaźnik ten

nie byłby tak popularny, gdyby nie tzw. prawo Moore’a. Pod koniec lat 60. ubiegłe-

go wieku Gordon Moore dostrzegł prawidłowość, że liczba elementów w układach

scalonych podwaja się co 12 miesięcy (rys. 9). Trzeba obiektywnie przyznać, że nie

jest to jakieś wielkie i zaawansowane odkrycie, ale dzięki niemu Moore przeszedł

na zawsze do historii mikroelektroniki. To bardzo „silna” zasada, oznaczająca, że

co roku można nabyć dwukrotnie większy układ, a co za tym idzie — dwukrot-

nie wydajniejszy, dwukrotnie szybszy, i co bardzo ważne — niemal za te same pie-

niądze. Chciałbym, abyś zwrócił uwagę, że jest to zasada o charakterze wykład-

niczym. Zatem w następnym roku jest dwa razy lepiej niż w poprzednim! Osobi-

ście nie znam drugiej tak dynamicznie rozwijającej się dziedziny. Trafiającą do wy-

obraźni analogią jest porównanie do przemysłu samochodowego — gdyby rozwijał

się on tak jak mikroelektronika, to na jednej łyżeczce paliwa samochód mógłby

przejechać kilkaset kilometrów z prędkością bliską prędkości dźwięku.

Prawo Moore’a sprawdzało się do końca lat 70. XX w., po czym zostało skorygo-

wane. Stwierdzono, że liczba elementów podwaja się co 18 miesięcy i w tej wersji

obowiązuje ono do dnia dzisiejszego.

Na pewno w tym momencie zadajesz sobie pytania: jak długo jeszcze będzie trwał

ten postęp, jakie są granice rozwoju i jak daleko się od nich znajdujemy, czy wy-

stąpią trudności, z którymi nie będziemy potrafili sobie poradzić. To niezwykle

ważne, ale i bardzo trudne pytania, na które na pewno nie istnieje jednoznaczna

odpowiedź.

Rysunek 9

Prawo Moore’a

Źródło: Intel. Witryna internetowa.

http://www.intel.com/technology/

stan z 2 października 2006 r.

13

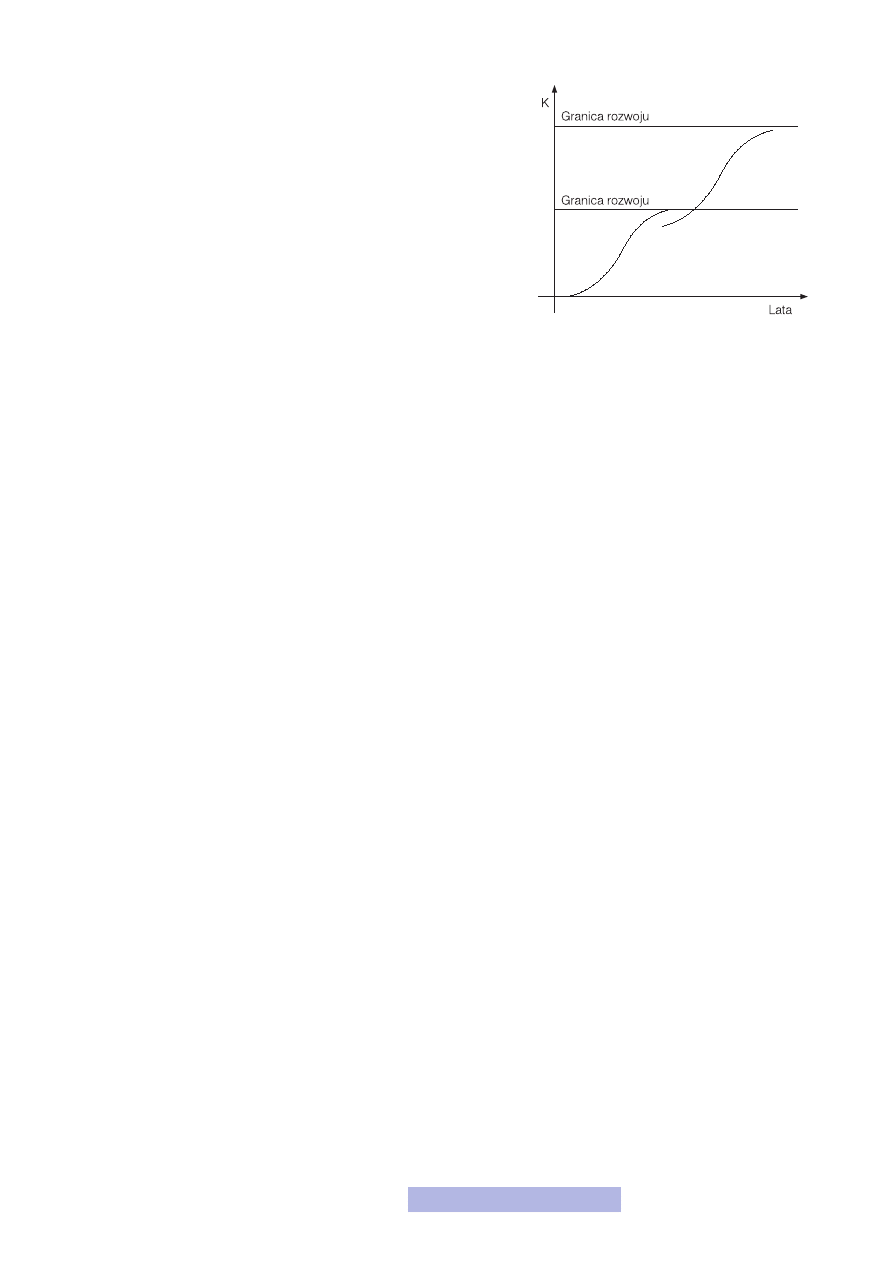

Najczęściej rozwój jakiejś dziedziny obrazuje się za pomocą tzw.

krzywej logistycznej (rys. 10). Co taka krzywa pokazuje? Powstaje

nowa technologia, jest w fazie badań w wąskiej grupie badaczy, roz-

wój jest stosunkowo powolny. Następnie zostaje ona upowszechnio-

na, trafia „pod strzechy” i wówczas obserwuje się ogromny rozwój,

wynikający z zainteresowania i pracy ogromnej ilości osób. Następ-

nie technologia zaczyna się nasycać. Nie obserwuje się już znacznego

postępu, powstają tylko drobne zmiany pozwalające jeszcze na drob-

ną poprawę, ale to wszystko. W międzyczasie powoli powstaje nowa

technologia, która w pewnym momencie zastąpi tę starą, już wysy-

caną i po jej upowszechnieniu obserwuje się znowu dynamiczny po-

stęp i tak w koło. W teorii wszystko ładnie wygląda, lecz w praktyce

otwartą kwestią pozostaje to, jak wskazać miejsce, w którym znajdu-

je się aktualnie stosowana technologia. Gdybyśmy potrafili wskazać to miejsce, ła-

two można by było powiedzieć: inwestujemy w obecną technologię, bo tkwi w niej

jeszcze dużo możliwości, ewentualnie czekamy na następną technologię. W przy-

padku mikroelektroniki już nie raz wróżono jej nasycenie i pokazywano trudności

nie do pokonania. Jednak póki co zawsze pojawiało się rozwiązanie, które pozwa-

lało na dalszy dynamiczny rozwój. Obecnie mikroelektronika również znajduje się

na rozdrożu. Z jednej strony wydaje się, że istnieje jeszcze zapas możliwości współ-

czesnej technologii, z drugiej zaś piętrzą się coraz większe trudności. Dlatego tak

trudno jest podać wiarygodne perspektywy na przyszłość.

2.1. Czynniki umożliwiające rozwój

Postęp w mikroelektronice, jak zresztą w przypadku większości dziedzin, wynika

z oddziaływania dwóch podstawowych czynników:

— ekonomicznego — zapotrzebowania na nowe rozwiązania ze strony społeczeń-

stwa i gospodarki, przy akceptowalnej wysokości kosztów nowych rozwiązań,

opłacalności inwestycji i pozytywnym wpływie na inne działy gospodarki,

— technicznego — fizycznych możliwościach rozwoju.

Oczywiście obydwa czynniki wpływają silnie na siebie. Pokonywanie kolejnych ba-

rier technicznych kosztuje, co negatywnie wpływa na cenę finalnego produktu oraz

na opłacalność produkcji, ale rynek potrzebuje nowych, lepszych rozwiązań, za co

jest gotów zapłacić. Powstaje więc dodatnio sprzężona spirala rozwoju.

W trakcie tego kursu poznałeś proces wytwarzania układów scalonych. Czas zatem

odpowiedzieć sobie na pytanie, w których miejscach tego procesu można mówić

o postępie i na czym on dokładnie polega. Otóż czynniki techniczne odpowiedzial-

ne za rozwój mikroelektroniki można podzielić na dwie grupy:

— technologiczne,

— konstrukcyjne i koncepcyjne.

Oczywiście obie te grypy nie są niezależne. Można wymyślić nową koncepcję, któ-

ra będzie z punktu widzenia technologii nie do wykonania, a z drugiej strony wy-

brać taką technologię, w której absolutnie nie da się wykonać danej konstrukcji.

Ale zajmijmy się po kolei poszczególnymi grupami.

Czynniki technologiczne

Wśród czynników technologicznych należy wymienić trzy od lat wiodące i uzupeł-

niające się nurty:

— wzrost powierzchni struktur,

Rysunek 10

Krzywa logistyczna

14

— wzrost powierzchni płytek podłożowych,

— zmniejszenie rozmiarów pojedynczych przyrządów.

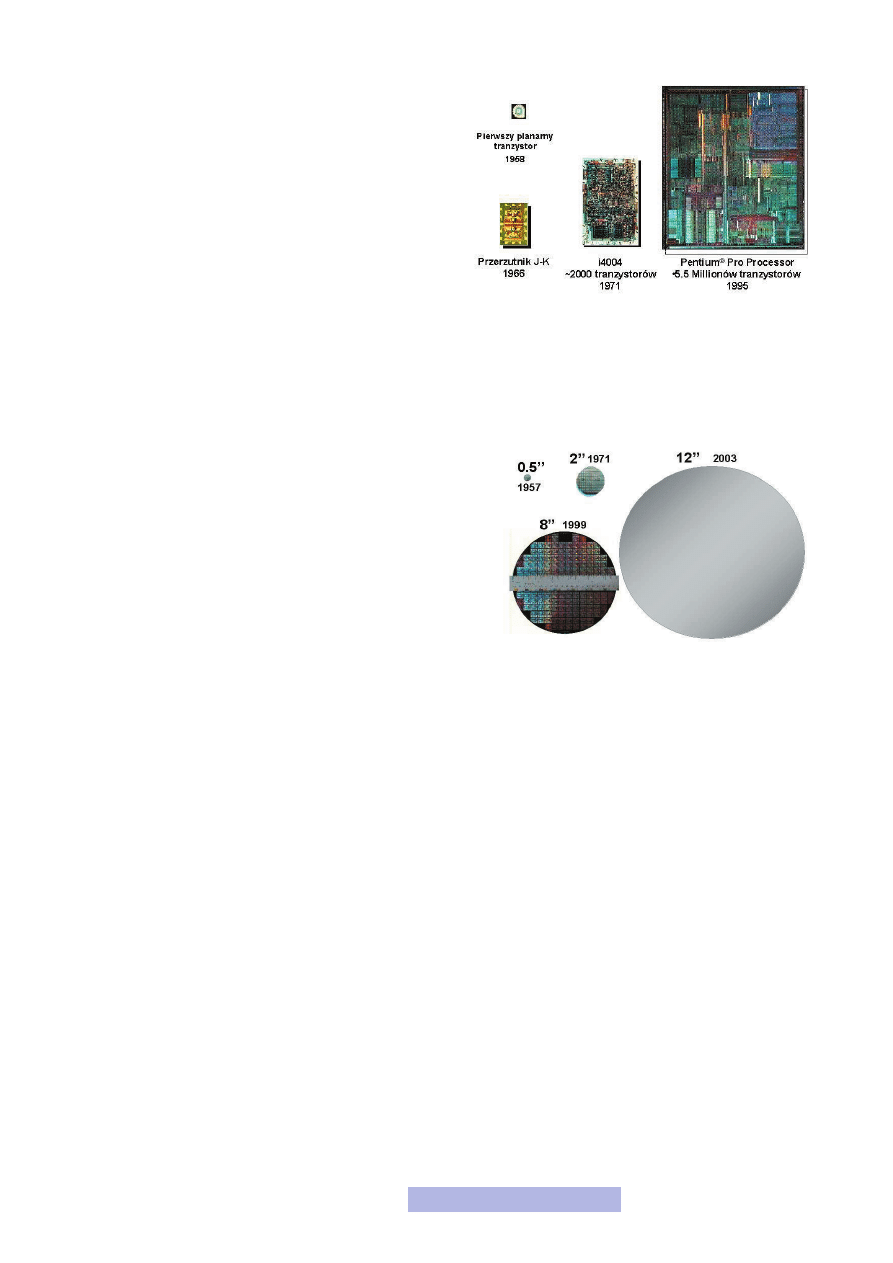

Wzrost powierzchni struktur wynika wprost ze wzrostu

liczby elementów oraz połączeń między nimi w jednym

układzie (rys. 11). Oczywiście wzrost ten nie jest pro-

porcjonalny do wzrostu liczby elementów. Okazuje się,

że liczba elementów wzrasta szybciej niż zmniejsza się

ich rozmiar — dlatego struktury rosną. Z drugiej strony

możliwość tego wzrostu wynika z udoskonalenia tech-

nologii, a więc możliwości wykonania ogromnej ilości

poprawnie działających tranzystorów i połączeń między

nimi. Tutaj największy udział ma postęp w procesie litografii, choć naturalnie udo-

skonalanie wszystkich procesów ma również istotne znaczenie.

Drugim, bardzo ważnym czynnikiem jest wzrost powierzchni płytek podłożowych

(rys. 12). Dzięki temu, że mamy do dyspozycji większą powierzchnię, możemy

wykonywać w jednym cyklu produkcyjnym więcej układów i to o większej po-

wierzchni. Dzięki temu zdecydowanie obniża koszty produkcji. Musisz pamiętać,

że koszty produkcji to głównie koszty procesów technologicz-

nych, płytki podłożowe są bardzo tanie. Mając do dyspozycji

większą powierzchnię i dostosowując procesy, tak aby wyko-

rzystać całą dostępną powierzchnię płytki, możesz wytworzyć

większą liczbę struktur, nie zmieniając liczby procesów! Za-

tem koszt jednostkowy układu radykalnie spada. Wzrost po-

wierzchni płytek podłożowych jest możliwy dzięki udosko-

naleniu technologii ich produkcji — szczególnie możliwości

spowolnienia procesu wyciągania i obrotu słupa krzemowe-

go w metodzie Czochralskiego oraz procesu cięcia na płytki.

Postęp w tej dziedzinie jest stosunkowo powolny, aczkolwiek

bardzo systematyczny. Należy przypuszczać, że w najbliższej przyszłości będzie on

utrzymany, choć rozmiary obecnie dostępnych podłoży krzemowych zaspokaja-

ją wymagania producentów układów scalonych. Wraz ze wzrostem powierzchni

rośnie także ich jakość. Płytki maja ogromna czystość, niewyobrażalnie małą licz-

bę defektów, a ich ceny są bardzo niskie. Tak więc w tej dziedzinie postęp będzie

nadal widoczny, aczkolwiek nie będzie miał już takiego znaczenia jak kiedyś. Zu-

pełnie inna sytuacja panuje w dziedzinie innych niż krzemowe podłoży, np. dla

technologii SOI czy wykonanych z innych materiałów półprzewodnikowych. Pod-

łoża są małe, drogie i często kiepskiej jakości. Tutaj nadal oczekuje się znacznego

postępu, który może radykalnie zmienić sytuację w mikroelektronice i wyznaczyć

nowy kierunek rozwoju.

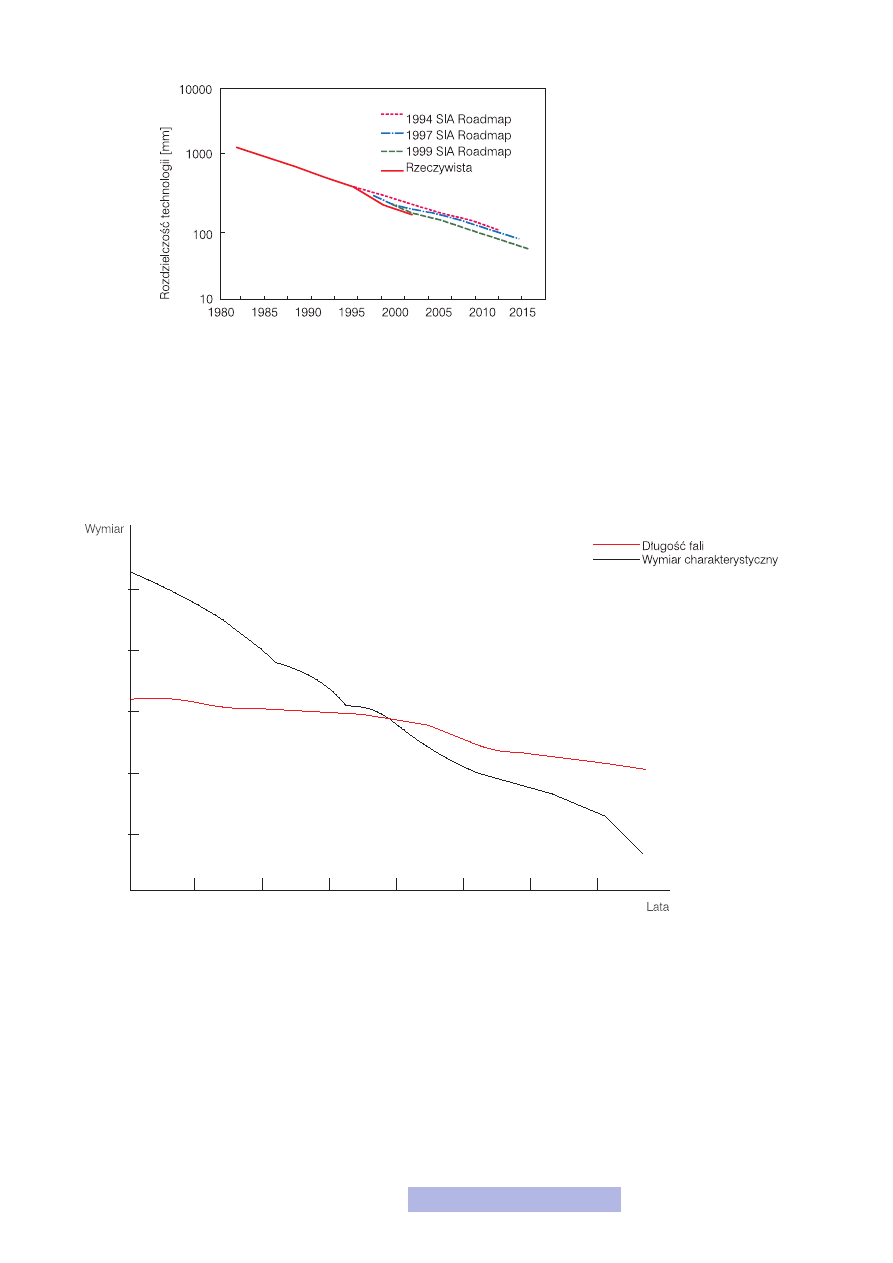

Ostatni z czynników, a więc miniaturyzacja, jest najważniejszy i postęp w tej dzie-

dzinie ma największy wpływ na rozwój mikroelektroniki. O ile powierzchnie

struktur oraz powierzchnie płytek podłożowych wzrosły na przestrzeni ostatnich

30 lat kilka-, a nawet kilkanaście razy, o tyle pojedyncze przyrządy zmalały set-

ki, a nawet tysiące razy. Tematyka skalowania przyrządów została szerzej opisana

w poprzednim module i nie będę już do niej wracał. Przypomnę tylko, że głównym

motorem postępu w tej dziedzinie jest postęp w procesie odwzorowywania kształ-

tów. W procesie litografii stosowane są coraz krótsze długości fal elektromagne-

tycznych, a nawet strumienie cząstek. Wprowadzono dodatkowe zabiegi technolo-

giczne, np. OPC (Optical Proximity Correction) czy PSM (Phase-Shift Masks), które

pozwalają uzyskać jeszcze lepszą dokładność. Dzięki temu postęp w procesie lito-

grafii jest znacznie szybszy niż wynikałoby to jedynie ze zwiększania dokładności

wykonania masek oraz zmniejszania długości fali naświetlającej (rys. 13).

Rysunek 11

Wzrost powierzchni struktur

Rysunek 12

Wzrost powierzchni płytek

15

Oczywiście sama litografia to nie wszystko. Trzeba również zmodyfikować i ulep-

szyć proces trawienia. Najważniejszym elementem tych zmian jest droga ku więk-

szej anizotropowości i selektywności. Było to możliwe dzięki zastosowaniu trawie-

nia suchego i jego bardzo dobrej kontroli. Dodatkowe zabiegi, takie jak wspomaga-

nie plazmą czy równoległe trawienie mokre i suche, zwielokrotniły postęp. Dzię-

ki powyższym rozwiązaniom rozwój w dziedzinie odwzorowywania kształtów jest

znacznie szybszy niż wskazywałoby na to prawo Moore’a oraz przewidywania spe-

cjalistów (rys. 14).

Sam proces odwzorowywania kształtów nie wystarczyłby, aby z powodzeniem móc

miniaturyzować elementy elektroniczne. Co z tego, że można wytworzyć cienki

tlenek bramkowy, jeśli miałby on wiele defektów i zanieczyszczeń i nie spełniał

roli jako izolator? Ewentualnie co nam po ścieżce, która ma tyle wad, że nie może

przewodzić prądu. Dlatego bardzo duży wpływ na możliwość miniaturyzacji ma

również poprawa jakości materiałów. Podstawą są płytki podłożowe, o których

czystości i jakości powiedzieliśmy już w czwartym module. Ale nie tylko — trze-

ba również zwiększać czystość i jakość wytwarzanych warstw tlenków, metaliza-

cji, pasywacji itd. Jest to możliwe dzięki lepszej kontroli procesu technologicznego

oraz używaniu niezwykle wysokiej jakości substratów (gazów, odczynników che-

micznych itd.).

Rysunek 13

Postęp w rozdzielczości litografii

Rysunek 14

Wymiar charakterystyczny

16

Trudno jednak obecne ocenić jaki będzie wpływ zmniejszania wymiarów na roz-

wój mikroelektroniki w przyszłości. Dotychczasowe prognozy nie sprawdzały się,

były zbyt pesymistyczne (rys. 13). Cały czas pokonywane są kolejne bariery, które

wydawało się, iż mogą ten postęp zatrzymać, a już na pewno wyhamować. Do tej

pory miniaturyzacja jest najważniejszym czynnikiem odpowiedzialnym za rozwój!

Na pewno dalszy postęp w tej dziedzinie jest jeszcze możliwy, choć jednocześnie

należy zaznaczyć, że coraz więcej kosztuje.

Czynniki konstrukcyjne i koncepcyjne

Drugą istotną grupę czynników umożliwiających rozwój stanowią nowe rozwiąza-

nia konstrukcyjne oraz koncepcyjne. Wśród nich należy wymienić:

— modyfikacje istniejących struktur,

— poszukiwanie nowych materiałów,

— poszukiwanie całkowicie nowych struktur oraz wykorzystywanie nowych zja-

wisk fizycznych.

Należy śmiało powiedzieć, że do tej pory powyższe czynniki nie decydowały o roz-

woju mikroelektroniki. Koncepcje używanych przyrządów oraz układów powsta-

ły kilkadziesiąt lat temu i praktycznie przetrwały do dnia dzisiejszego. Moim zda-

niem w powyższych obszarach należy upatrywać największych szans na dalszy roz-

wój mikroelektroniki.

Jeśli chodzi o modyfikacje istniejących struktur, to jedyną do tej pory istotną zmia-

ną jest wprowadzenie omawianych wcześniej obszarów SDE do tranzystora MOS.

Poza tym nic więcej istotnego nie stało się w tej dziedzinie. A możliwości są spore.

Najbardziej obiecującą jest obecnie omówiona wcześniej technologia SOI. Rów-

nież duże możliwości stoją przed wykorzystaniem złącz z barierą Schottky’ego. Do

tej pory w ogóle nie poruszaliśmy tego ważnego w technologii półprzewodniko-

wej zagadnienia. Jak wiesz, złącze PN ma własności prostujące, tzn. w jedną stronę

przewodzi prąd, a w drugą blokuje. Okazuje się, że podobne własności może mieć

złącze MS (metal–półprzewodnik od ang. Metal-Semiconductor). Złącze MS to po

prostu połączenie metalu i półprzewodnika. Można je wykonać na dwa sposoby:

— jako złącze omowe,

— jako złącze prostujące.

W większość przypadków zależy nam, aby złącze nie miało żadnego wpływu na

działanie przyrządu, chcemy, aby prąd „gładko” przepływał z metalu do półprze-

wodnika i w drugą stronę. Mówi się wówczas o złączu omowym. Wszystkie do-

tychczas przedstawione przyrządy miały wyłącznie złącza omowe.

Natomiast niekiedy zależy nam na złączu prostującym. Wykonując odpowiednio

kontakt metal–półprzewodnik, można sprawić, że złącze to będzie w przewodziło

tylko w jedną stronę, a w drugą blokowało. Wówczas otrzymujemy po prostu dio-

dę. Takie złącze jest często nazywane złączem z barierą Schottky’ego. Do tej pory

prostujące złącza MS były wykorzystywane do budowy diod Schottky’ego. Są to

normalne diody, takie jak poznane już diody PN. Ich największą zaletą są bardzo

duże szybkości pracy. Jednak okazuje się, że te złącza można wykorzystać do budo-

wy tranzystorów nazwanych SB-MOS (Schottky Barrier MOS). W module czwar-

tym przedstawiłem budowę tranzystora MOS. Jak pamiętasz, były tam dwa do-

mieszkowania: pod źródłem i drenem, które tworzyły dwie diody. Skoro mają to

być dwie diody, to czemu nie zastąpić ich właśnie dwoma prostującymi kontaktami

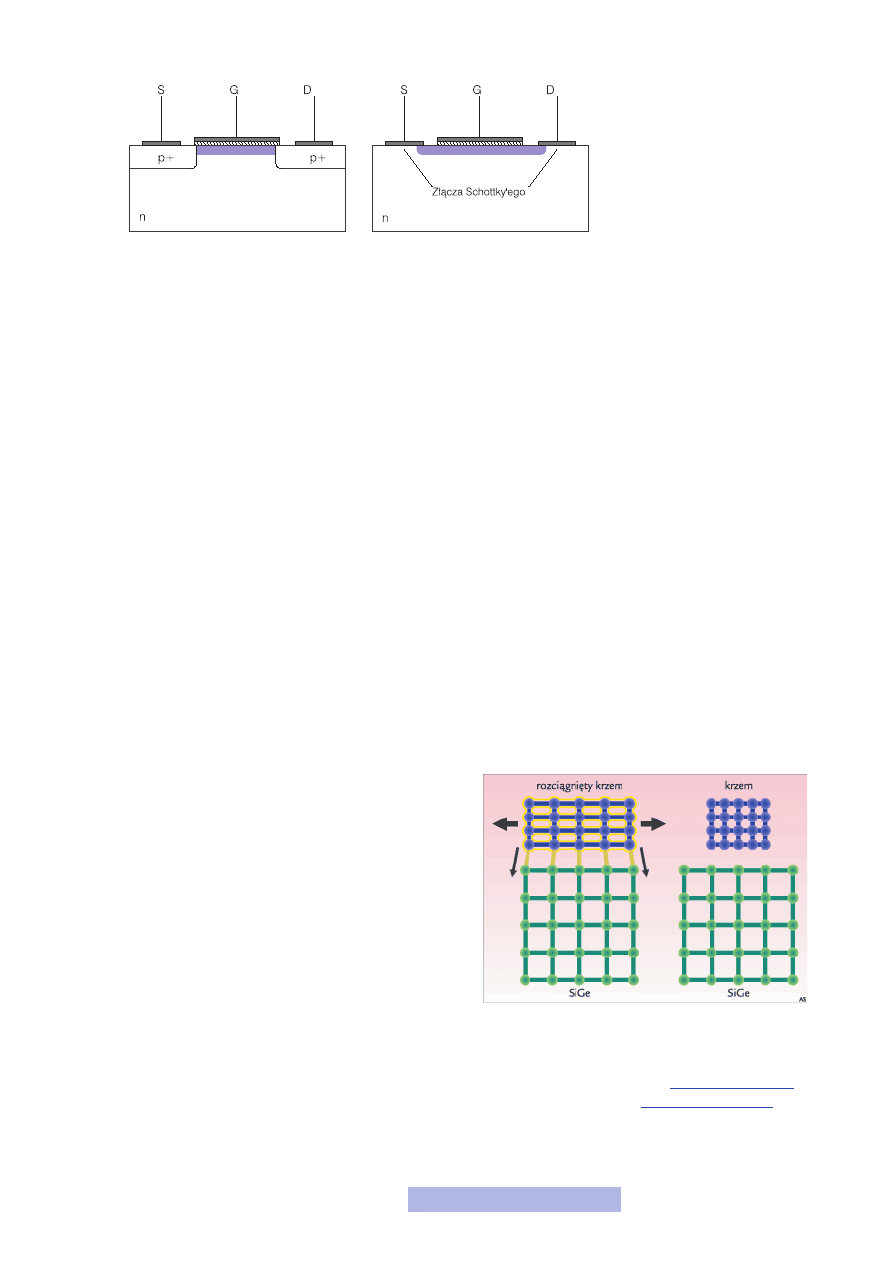

MS? I tak właśnie zbudowany jest tranzystor SB-MOS (rys. 15).

17

Obecnie prowadzone są zakrojone na szeroką skalę prace nad takimi przyrządami.

Unia Europejska stworzyła nawet specjalny program SODAMOS, w którym biorą

również udział ośrodki naukowe z Polski. Tranzystory z barierą Schottky’ego mają

co prawda gorsze parametry niż klasyczne MOS-y, ale za to ich budowa jest o wiele

prostsza, nie trzeba wykonywać domieszkowań pod kontaktami i obszarów SDE.

Zmniejsza to radykalnie liczbę litografii, a przez to redukuje koszty i podnosi nie-

zawodność. Dzięki temu mamy całkowicie nowe możliwości w dziedzinie miniatu-

ryzacji. Co więcej, zasada działania takiego przyrządu jest identyczna jak klasycz-

nego MOS-a. Pewnie zastanawiasz się czemu w takim razie SB-MOS-y już dawno

nie weszły do użycia. Okazuje się, że są problemy technologiczne z wykonaniem

dużej liczby złączy prostujących o podobnych parametrach. Ale nad tym właśnie

pracuje się na świecie i należy przypuszczać, że niedługo trudności te mogą zostać

pokonane.

Takich modyfikacji można wymieniać jeszcze wiele i zapewne z czasem będzie się

ich pojawiać coraz więcej. Te, które opisałem powyżej są moim zdaniem najważ-

niejsze i mogą w przyszłości być powszechnie wykorzystywane. Co więcej, myślę,

że właśnie w tym segmencie modyfikacji należy poszukiwać dalszych szans na roz-

wój w najbliższej przyszłości.

Kolejnym bardzo ważnym czynnikiem mogącym umożliwić rozwój są nowe mate-

riały. Na początku historii elektroniki półprzewodnikowej wiodącym materiałem

był german. Jednak dość szybko do elektroniki wprowadzony został krzem, który

całkowicie ją zdominował. W jakichś specjalnych zastosowaniach można jeszcze

spotkać przyrządy wykonane z germanu czy jakiś innych półprzewodników, ale

są to wyjątki. Obecnie krzem jest absolutnie wiodącym materiałem w elektronice,

a szczególnie w mikroelektronice. Pozostałe materiały półprzewodnikowe mają je-

dynie niszowe znaczenie. Ale czy tak musi być w przyszło-

ści? A może właśnie metodą na dalszy rozwój jest zmiana

materiału półprzewodnikowego?

Obecnie możliwości krzemu jako materiału półprzewodni-

kowego zbliżają się do granic. Chcielibyśmy, aby nośniki

mogły poruszać się szybciej i szybciej tej prędkości nabie-

rały, aby przyrządy mogły pracować w wyższych tempera-

turach, aby miał lepszą przewodność cieplną i lepiej odpro-

wadzały ciepło, aby wytrzymywał większe napięcia itd. Li-

sta potrzeb jest długa, a możliwości krzemu ograniczone.

Co gorsza, w tej dziedzinie niewiele można poprawić, takie

są własności krzemu. Można zastosować zabiegi technolo-

giczne, które mogą pewne parametry poprawić, ale nie są to zmiany epokowe, lecz

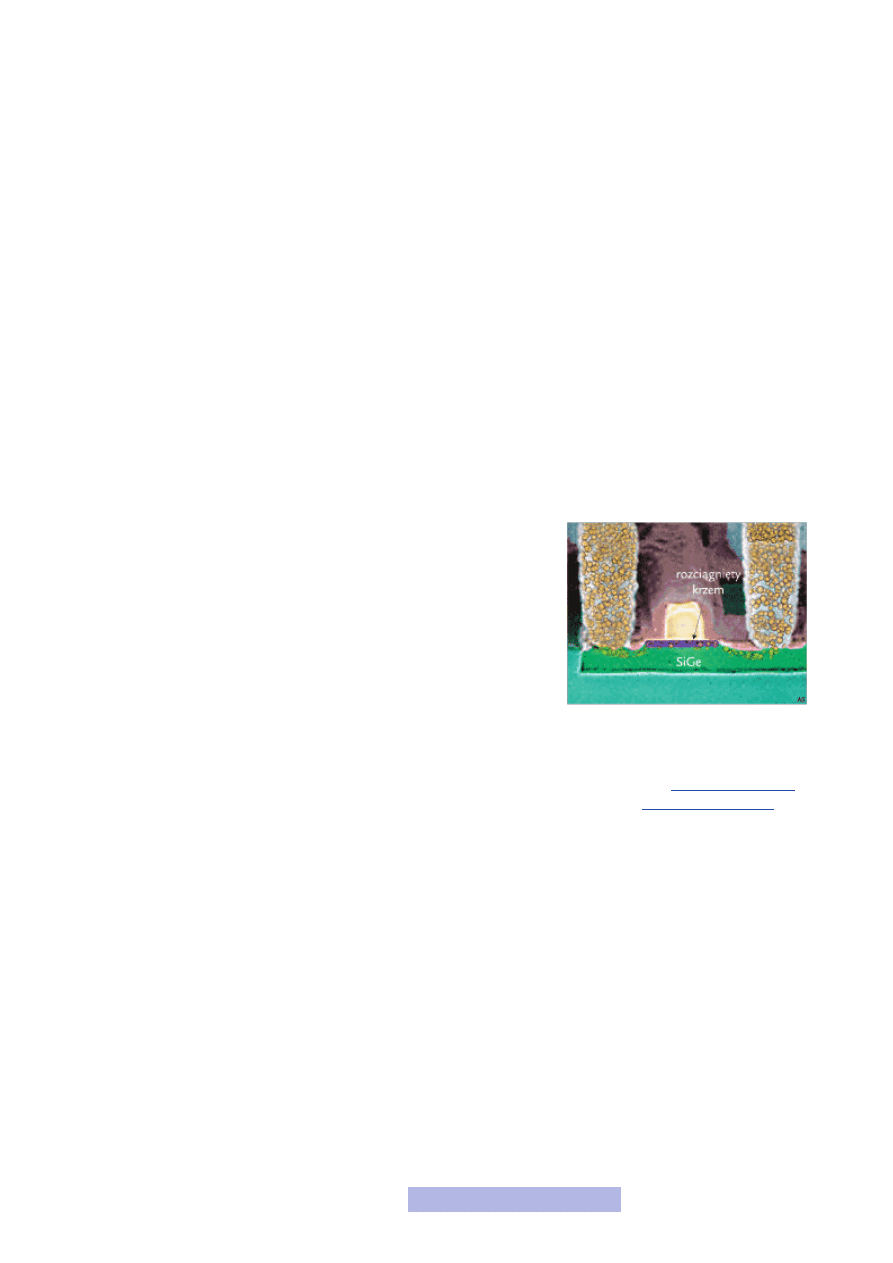

raczej kosmetyczne. Przykładem takiego zabiegu jest rozciąganie krzemu (strained

silicon). Polega ono na zwiększeniu odległości między atomami w siatce krystalicz-

nej (rys. 16). Dzięki temu ładunki mogą poruszać się z większymi prędkościami

i szybciej je osiągać. Osobnym i poważnym problemem jest to, jak w praktyce taki

krzem rozciągnąć.

Rysunek 15

Klasyczny MOS a SB-MOS

Rysunek 16

Rozciągnięty krzem

Źródło: PCkurier. Witryna interne-

towa.

,

stan z 2 października 2006 r.

18

Zabiegi ulepszające krzem często nie wystarczają. Wówczas trzeba wziąć inne,

nowe materiały półprzewodnikowe. Poszukiwania trwają i wśród najlepszych kan-

dydatów należy wymienić:

— krzemogerman (SiGe),

— węglik krzemu (SiC),

— arsenek galu (GaAs),

— azotek galu (GaN),

— związki indu: InP (fosforek indu), InGaAs itd.

Zwróć uwagę, że wszystkie wymienione powyżej materiały to już nie pojedynczy

pierwiastek, lecz dwu- lub nawet trójskładnikowe związki. Okazuje się, że nie tylko

pojedyncze pierwiastki, ale także związki mają własności materiału półprzewod-

nikowego. Co więcej, własności te są lepsze niż w przypadku materiałów półprze-

wodnikowych jednoskładnikowych. Dodatkowo związki dwu- i więcej składniko-

we pozwalają na uzyskanie tzw. heterostruktur. Jest to połączenie na jednym pod-

łożu materiałów o różnych własnościach, np. Si oraz SiGe. Heterostruktury dają

całkiem nowe możliwości tworzenia przyrządów, których nie jesteśmy w stanie

uzyskać w związkach jednoskładnikowych. Niestety zyski wynikające ze stosowa-

nia dwu- i więcej składnikowych związków okupione są znacznymi trudnościami

technologicznymi i kosztami.

Zajmijmy się teraz krótką charakterystyką wymienionych powyżej materiałów.

Pierwszym jest krzemogerman, a więc związek dwóch typowych materiałów pół-

przewodnikowych. Oba pierwiastki należą do IV grupy układu okreso-

wego. SiGe był na początku stosowany głównie w technologii bipolar-

nej do budowy tranzystorów bipolarnych oraz tranzystorów z heterozłą-

czami. Dość szybko dobre własności tranzystorów krzemogermanowych

wykorzystano w technologii BiCMOS. Dość długo jednak SiGe opierał

się technologii układów scalonych wysokiej skali integracji, gdyż trud-

no było w nim uzyskać małe rozmiary oraz wysoką gęstość upakowania.

Przełomem było dopiero połączenie technologii Si i SiGe. Obecnie krze-

mogerman jest powszechnie i komercyjnie stosowany w klasycznej tech-

nologii CMOS (rys. 17). Umożliwia on wytworzenie w kanale tranzysto-

ra MOS rozciągniętego krzemu. Dzięki temu, że odległości między ato-

mami w sieci krystalicznej SiGe są większe niż w Si, nałożona warstwa krzemu roz-

ciąga się. W ten sposób tworzy się kanał, w którym nośniki mogą poruszać się szyb-

ciej, a to oznacza możliwość tworzenia szybszych układów (głównie procesorów).

Technologia krzemogermanu w połączeniu z rozciągniętym krzemem jest już obec-

nie powszechnie stosowana w rozwiązaniach komercyjnych. Co więcej, wiodące

firmy technologiczne (głównie AMD) inwestują ogromne pieniądze w rozwój tech-

nologii. Należy przypuszczać, że technologia ta nie przyniesie znaczącego przeło-

mu, jednak w najbliższej przyszłości umożliwi dalszy postęp w mikroelektronice.

Drugim wymienionym związkiem jest SiC (węglik krzemu). Wykonuje się z niego

papier ścierny. Poza swoimi dobrymi własnościami mechanicznymi ma również

doskonałe własności jako półprzewodnik. Przede wszystkim ma bardzo szeroką

przerwę energetyczną, dzięki czemu może być wykorzystywany w układach pra-

cujących w wysokich temperaturach. Do tego w porównaniu do krzemu ma znacz-

nie lepszą przewodność cieplną oraz większą szybkość ruchu nośników. Obecnie

węglik krzemu jest powszechnie stosowany w elektronice wysokotemperaturowej,

a do świata mikroelektroniki dopiero zaczyna zaglądać. Największym problemem,

jak w przypadku większość nowych materiałów, są bardzo drogie i małe płytki

podłożowe. Do tego płytki te zawierają wiele defektów, wśród których najtrudniej-

sze do wyeliminowania są tzw. mikropory. Ponadto występują ogromne trudno-

ści technologiczne, związane m.in. z domieszkowaniem, wytwarzaniem kontaktów

omowych, tworzeniem warstwy izolatora na powierzchni itp.

Rysunek 17

Tranzystor MOS Si/SiGe

Źródło: PCkurier. Witryna interne-

towa.

,

stan z 2 października 2006 r.

19

Technologia SiC, choć bardzo obiecująca, jeśli chodzi o układy scalone, do tej pory

nie wyszła poza laboratoria i pokoje badaczy. Nie wydaje się, aby ten stan rzeczy

mógł w najbliższej przyszłości ulec radykalnej zmianie — gdyby tak się jednak sta-

ło, to sama zmiana materiału umożliwiłaby ogromny postęp.

Kolejnym kandydatem na „nowy” materiał półprzewodnikowy jest GaAs (arsenek

galu). Słowo nowy nie bez powodu zostało wzięte w cudzysłów, gdyż GaAs zna-

ny jest już od dawna na rynku materiałów półprzewodnikowych. Ma doskonałe

własności, jeśli chodzi o zmiany szybkości nośników, do tego ma większą prze-

rwę energetyczną niż krzem. Wadą jest niestety gorsza przewodność cieplna, która

utrudnia uzyskanie dużej gęstości upakowania. Jednak największym problemem,

podobnie jak w przypadku SiC, są płytki podłożowe oraz trudności technologicz-

ne z ich obróbką. Podłoża są małe i drogie. Obecnie z arsenku galu wykonuje się

niezbyt skomplikowane układy scalone, w których krytycznym parametrem jest

częstotliwość pracy. Innym ważnym zastosowaniem GaAs jest budowa elementów

optoelektronicznych, a więc źródeł i detektorów promieniowania. Wykorzystując

arsenek galu, można na jednej płytce podłożowej zintegrować zarówno elementy

elektroniczne, jak i optyczne. Zważywszy na to, że coraz więcej sygnałów przesy-

łanych jest drogą optyczną (światłowody), takie podejście jest jak najbardziej wska-

zane. W przypadku krzemu takich możliwości niestety nie mamy. Prace nad GaAs

trwają już bardzo długo i do tej pory nie nastąpił żaden przełom. Obecnie GaAs

ma swoje małe, ale pewne miejsce na rynku mikroelektroniki i taki stan powinien

się utrzymać. Nie spodziewam się, aby w najbliższej przyszłości miał on zastąpić

krzem jako podstawowy materiał półprzewodnikowy.

Pozostałe związki, a więc GaN, InGaAs, InP, to już odległa przyszłości. Są to ma-

teriały mające świetne parametry, jednak praktycznie nie są stosowane ze względu

na brak tanich i dużych płytek podłożowych. Sytuacja w ich przypadku jest jeszcze

gorsza niż przy GaAs i SiC. Obecnie GaN jest stosowany głównie do wytwarzania

elementów optoelektronicznych, a więc laserów oraz detektorów optycznych. Te-

stowo wytwarzane są pojedyncze elementy elektroniczne, jednak są to tylko próby,

które jeszcze długo nie wyjdą poza laboratoria. Sytuacja wygląda podobnie w przy-

padku związków indu. A związki te mogą mieć świetlaną przyszłość ze względu na

możliwość łatwego tworzenia heterostruktur. Co więcej InP zapewnia obecnie naj-

wyższą częstotliwość pracy, nawet do kilkuset GHz! Niestety w tej chwili parame-

try te są całkowicie nieosiągalne dla powszechnego, komercyjnego wykorzystania.

Wiele osób już kilka lat temu wróżyło koniec ery technologii krzemowej. Jednak

krzem jak był, tak do dzisiaj jest i moim zdaniem jeszcze długo będzie technolo-

gią wiodącą. Potwierdzają to również coraz ostrożniejsze opinie ekspertów, którzy

jeszcze kilka lat temu nie dawali mu żadnych szans. Choć znamy wiele materiałów

o lepszych parametrach, to jednak krzem jest najtańszy i najdostępniejszy. Co wię-

cej, dysponujemy dopracowaną i wydajną technologią jego obróbki. Oczywiście

należy poszukiwać nowych materiałów, ten fakt nie podlega dyskusji. Moim zda-

niem najbliższe lata będą jednak należały do technologicznego ulepszania krzemu

i dalszego zbliżania się do granic jego możliwości. Na taki kierunek rozwoju wska-

zują również koncerny technologiczne, które dalej inwestują w technologie krze-

mowe (głównie SOI i Si/SiGe).

Nowe materiały to nie tylko podłoża i nie tylko nowe półprzewodniki. Poszukiwa-

ne są także nowe materiały do budowy bramki tranzystora MOS, ścieżek itp. Obec-

nie jako izolator bramkowy stosowany jest dwutlenek krzemu. Nie ma on jednak

jakichś szczególnie dobrych własności, dlatego poszukuje się materiałów mogących

go zastąpić. Problemem jest oczywiście sposób jego umieszczenia na powierzch-

ni krzemu. Z dwutlenkiem krzemu nie było takiego problemu, gdyż powstawał

on z podłoża, był więc naturalnie z nim związany. Obecnie prowadzone są pra-

ce nad wieloma materiałami mającymi zastąpić SiO

2

, jednak przełomu nie widać.

20

Jeśli chodzi o elektrodę bramkową, to dość szybko aluminium zostało zastąpione

przez polikrzem. Aluminium przestało być również wiodącym materiałem do bu-

dowy ścieżek przewodzących. Obecnie są one najczęściej wykonywane z miedzi,

choć i tutaj poszukuje się cały czas nowych materiałów. Miedź ma świetne parame-

try elektryczne, natomiast są z nią trudności technologiczne. W przeciwieństwie

do podłoży półprzewodnikowych postęp w dziedzinie pozostałych materiałów jest

widoczny i wydaje się, że będzie trwał nadal.

Ostatnim czynnikiem mogącym umożliwić dalszy rozwój jest tworzenie nowych

struktury oraz wykorzystywanie nowych zjawisk fizycznych. To bardzo szeroki te-

mat, któremu mógłbym poświęcić osobny moduł, a nawet kurs. Jednak wówczas

raczej nie mówiłbym o mikroelektronice, lecz o optoelektronice, nanoelektronice,

spitronice, nanotechnologii itp. Jako że ten kurs poświęcony jest wyłącznie mikro-

elektronice, pominę szersze omówienie tego zagadnienia. Chciałbym tylko, abyś

wiedział, że poza pracami nad udoskonalaniem istniejących obecnie technologii

wielu naukowców pracuje nad całkowicie nowymi rozwiązaniami — nad zupełnie

inaczej działającymi tranzystorami (a może to już nie będą w ogóle tranzystory),

wykorzystaniem całkowicie innych zjawisk niż przetwarzanie sygnałów elektrycz-

nych. Wydaje mi się, że wyniki tych prac nie opuszczą murów laboratoriów wcze-

śniej jak za kilka-, kilkanaście lat, może nawet później. Z jednej strony możliwości

są ogromne, wręcz trudne do wyobrażenia. Z drugiej, technologia, która umożli-

wiłaby wytworzenia takich struktur i to w skali komercyjnej jest obecnie niedo-

stępna i trudno sobie wyobrazić, aby w tej dziedzinie miało się coś szybko zmienić.

Niemniej jednak to bardzo ważny czynnik i w nim należy upatrywać szans na po-

stęp w następnych dekadach.

2.2. Czynniki ograniczające rozwój

Do tej pory poznałeś czynniki, które umożliwiły i dalej umożliwiają rozwój mikro-

elektroniki. Zapewne odniosłeś wrażenie, że postęp odbywał się głównie na płasz-

czyźnie technologii. I to jest słuszne wrażenie. Tak naprawdę od 30 lat nie zmieniły

się budowane przyrządy i układy, wiodącym materiałem jest krzem. Cały postęp to

czynniki technologiczne, a więc miniaturyzacja i scalanie coraz większej liczby ele-

mentów. Czy to nie przypomina ci dokładnie definicji mikroelektroniki?

Na pewno zadajesz sobie pytanie, ile jeszcze może trwać postęp. Jak bardzo można

zmniejszać tranzystory, jak dużo można ich umieścić i połączyć, tak aby wszystko

pracowało poprawnie? Cóż, sam chciałbym znać odpowiedź na to pytanie, a nie-

stety nie znam i wątpię, aby ktokolwiek wiążąco potrafił jej udzielić. Nawet naj-

więksi sceptycy w tej dziedzinie są bardzo ostrożni w formułowaniu hipotez. Przy-

gotowując się do pisania tego modułu, zgromadziłem ok. 100 artykułów na ten te-

mat napisanych przez największych specjalistów — trudno znaleźć w nich konkre-

ty. I wcale mnie to nie dziwi!

Spróbujmy jednak podejść do tematu ograniczeń podobnie jak do czynników wzro-

stu, a więc usystematyzujmy je. Zmniejszenie lub nawet zahamowanie tempa roz-

woju może wynikać z:

— braku wiedzy,

— braku zainteresowania,

— ograniczeń ekonomicznych,

— barier technicznych.

21

W przypadku mikroelektroniki na pewno żaden z dwóch pierwszych czynników

nie jest tym, który obecnie czy w przyszłości mógłby wpłynąć na tempo rozwoju.

Wiedza w dziedzinie fizyki dotycząca zjawisk w skali mikro- czy nanometrowej

wielokrotnie przekracza nasze potrzeby. Wiemy więcej niż potrzeba. Co do dalsze-

go zainteresowania mikroelektroniką i to przez coraz większą grupę osób, nie mam

żadnych wątpliwości. Zatem ewentualnych przyczyn należy szukać w dwóch pozo-

stałych czynnikach. Dyskusję na temat ograniczeń natury ekonomicznej, podobnie

jak w przypadku czynników wzrostu, pominę. Skupię się natomiast na najciekaw-

szych dla nas czynnikach technicznych. Można je podzielić na:

— ograniczenia fizyczne,

— bariery technologiczne,

— ograniczenia w złożoności układów.

Pierwsze grupa, a więc ograniczenia fizyczne wynikają z podstawowych praw i za-

sad fizyki. Tych barier niestety pokonać nie możemy w żaden sposób, dlatego są

one często nazywane ograniczeniami fundamentalnymi. Przykładem takiego ogra-

niczenia jest choćby prędkość światła. Czego byśmy nie robili, nigdy nic nie będzie

poruszało się szybciej niż światło. Na podstawie praw fizyki można wyliczyć m.in.

jaka może być maksymalna prędkość pracy układu, minimalna wartość napięcia

zasilania oraz minimalne rozmiary tranzystora MOS (przy których ma on jeszcze

szanse działać) itd. Nie chciałbym wchodzić w szczególnych tych obliczeń, gdyż

opierają się one na nie najłatwiejszych do zrozumienia prawach mechaniki kwanto-

wej

1

. Natomiast myślę, że najbardziej zainteresują cię uzyskane wyniki:

— maksymalna częstotliwość pracy układu — ok. 30 THz, czyli 30 000 GHz,

— minimalne napięcie zasilania — ok. 0,1 V,

— minimalna grubość tlenku bramkowego — ok. 0,3 nm,

— minimalna długość kanału tranzystora — ok. 0,6 nm.

Tych barier raczej nie uda się nam przekroczyć, ale na szczęście jeszcze dość dale-

ko od nich się znajdujemy. Zresztą sam porównaj otrzymane minimalne wymia-

ry z wymiarami tranzystora podanymi w module piątym. Tak więc możliwości są

jeszcze spore, lecz na przeszkodzie stają pozostałe dwa czynniki, a więc możliwości

technologiczne oraz złożoność układów.

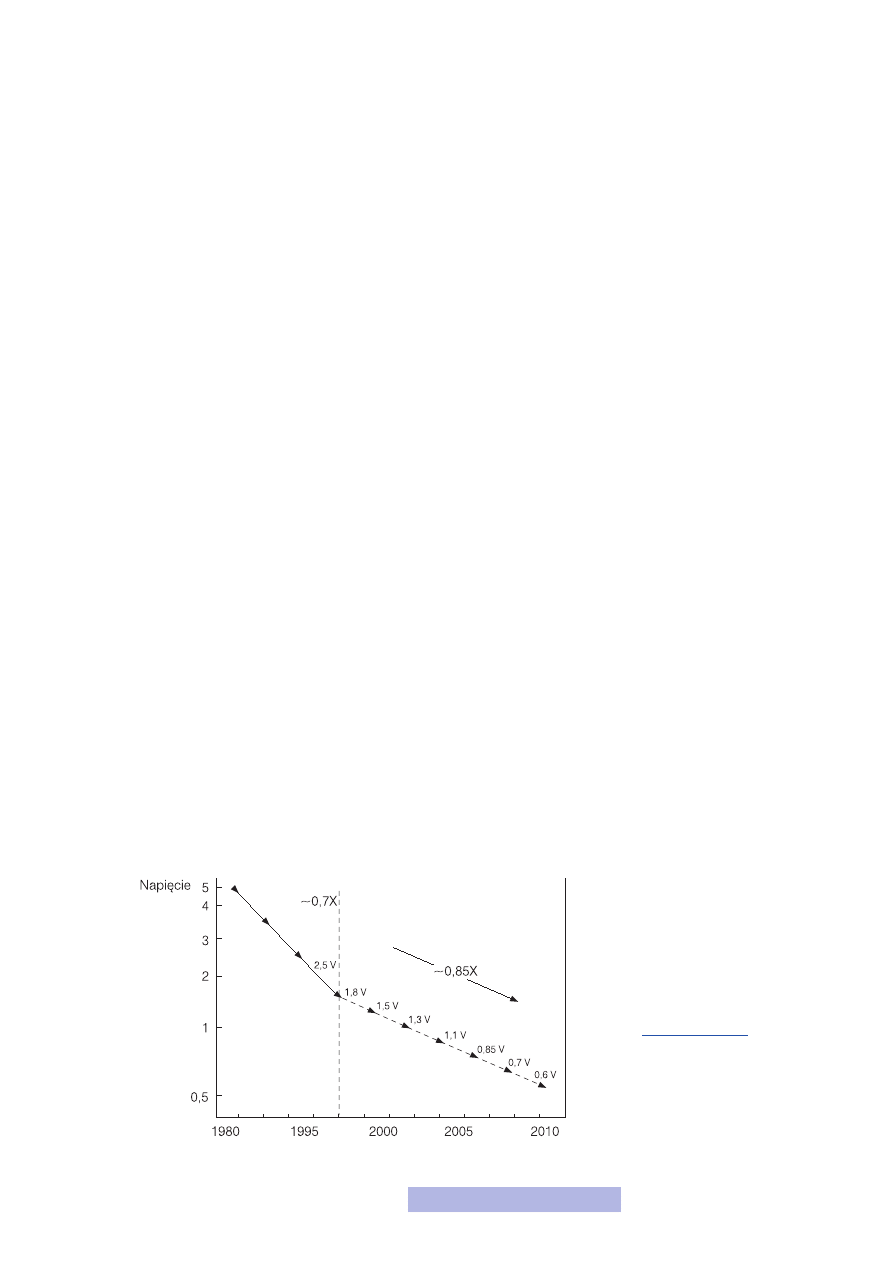

Zanim przejdę do omówienia kolejnych ograniczeń, zatrzymam się jeszcze na chwi-

lę przy napięciu zasilania. Otóż reguły skalowania mówią, że wraz ze zmniejsza-

niem tranzystora, napięcie to należy również zmniejszać. Z drugiej strony w mo-

dule piątym powiedzieliśmy, że im wyższe napięcie zasilania, tym szybciej działają

układy. Trudno zatem pogodzić te dwie tendencje. W rzeczywistości napięcie zasi-

lania spada, ale nie tak szybko jak wymiary tranzystora (rys. 18). Tak tendencja jest

możliwa głównie dzięki poprawie jakości wykonywanego tlenku bramkowego.

1

Zainteresowani znajdą je

choćby w artykule: Jaku-

bowski A., 1995: Mikro-

elektronika krzemowa

— dokąd zmierzamy?,

„Elektronika”, r. 36, 2.

Rysunek 18

Napięcie zasilania

w układach scalonch

22

Na temat barier technologicznych już wielokrotnie wspominałem w trakcie całego

kursu. Przypomnę tylko, że największym ograniczeniem technologicznym jest pro-

ces litografii. Duże problemy są także z trawieniem. Musisz sobie uświadomić, że

jeden 1 nanometr to ok. 4 warstwy atomów krzemu! Próbując odwzorować, a po-

tem wytrawić kształty rzędu kilku czy nawet kilkudziesięciu nanometrów, w rze-

czywistości usuwasz kilkanaście, kilkadziesiąt warstw atomów! To wręcz niewia-

rygodne. Pracując z tak małymi wielkościami, dużym problemem jest także proces

domieszkowania oraz wytwarzanie cienkich warstw. Przecież współczesne tlenki

bramkowe mają wymiary poniżej 2 nm, a więc ok. dziesięciu warstw atomowych.

To chyba najlepiej obrazuje jak ogromna musi być precyzja wykonania i jak za-

awansowaną technologią obecnie dysponujemy.

Przykłady trudności technologicznych mógłbym mnożyć, gdyż przy wymiarach

rzędu nanometrów nie ma już łatwych zadań. Póki co, potrafimy sobie z tymi za-

daniami radzić i dalej miniaturyzować elementy. Owszem postęp w tej dziedzinie

nie jest już tak dynamiczny jak jeszcze kilka lat temu, ale nadal trwa i moim zda-

niem nadal trwać będzie.

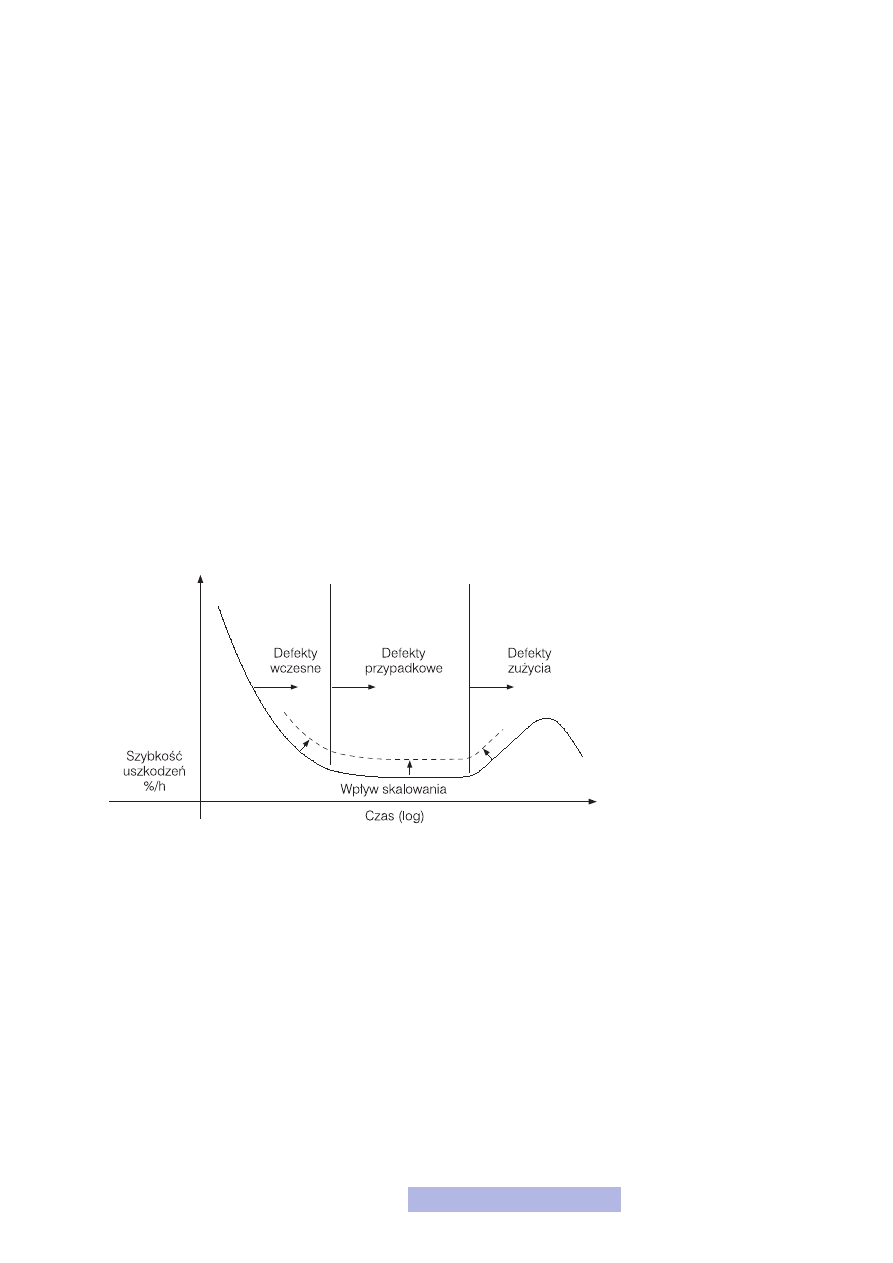

Do tej pory mówiliśmy wyłącznie o pozytywnych stronach miniaturyzacji. Ale są

i negatywne. Najważniejszymi jest spadek uzysku i niezawodności (rys. 19). Nie-

stety łatwiej jest popełnić błąd, budując tak małe przyrządy. Wystarczy, że choć je-

den z tranzystorów spośród setek milionów będzie uszkodzony i cały wyproduko-

wany układ można wyrzucić do kosza. Co więcej, małe elementy są bardziej podat-

ne na uszkodzenia w trakcie działania układu. To niestety bardzo podnosi koszty

produkcji i późniejszej eksploatacji.

Jakby na przekór wszystkim opisanym powyżej obawom, w 2001 roku firma Intel

zaprezentowała działający tranzystor z kanałem o długości 20 nm! A więc cztero-

krotnie mniejszy niż dotychczas produkowane (rys. 20). Oglądając jego zdjęcia,

widzisz zapewne na jego powierzchni chropowatości. To są już właśnie pojedyn-

cze atomy, ten działający tranzystor zbudowany jest z kilkudziesięciu warstw ato-

mów i działa. Choć do dziś nie wszedł on do seryjnej produkcji, to jednak uważam,

że fakt jego istnienia dobrze wróży na przyszłość i daje nadzieję na dalszy postęp

w dziedzinie technologii.

Rysunek 19

Wpływ skalowania

na niezawodność

23

Ostatnie z wymienionych ograniczeń wynikają ze złożoności projektowanych ukła-

dów, a konkretnie — ze wzrostu liczby elementów oraz połączeń między nimi.

Jeszcze kilka lat temu czynniki te nie odgrywały ważniejszej roli i często nawet

o nich nie mówiono. Obecnie okazuje się, że są one najpoważniejszym zagrożeniem

dla dalszego rozwoju. Moim zdaniem nawet większym niż trudności technologicz-

ne. Należy do nich zaliczyć:

— wpływ połączeń,

— odprowadzenie energii cieplnej.

Okazuje się, że szybkość rozchodzenia się sygnału w połączeniach jest niewystar-

czająca. Przeprowadźmy prosty rachunek. Sygnał w połączeniach w układzie sca-

lonym rozchodzi się z prędkością ok. 108 m/s, a więc trzykrotnie wolniej niż świa-

tło. Współczesne procesory pracują z częstotliwościami ok. 3 GHz, a więc w trak-

cie jednego cyklu procesora sygnał może przebyć drogę ok. 3 cm! To naprawdę

bardzo mało, zwłaszcza, że długości połączeń w układach cały czas rosną. Do tego

sygnał jest zniekształcany w trakcie transmisji po ścieżkach, co może prowadzić

do dodatkowych błędów. Jak widać, problem jest poważny i nie widać — póki co

— jego rozwiązania. Został zmieniony materiał, z którego wykonywane są połą-

czenia, optymalizuje się rozłożenie elementów w strukturze, tak aby ścieżki miały

jak najmniejszą długość. Jednak zgodnie z prawem Moore’a, liczba elementów ro-

śnie i nadal będzie rosła, a co za tym idzie i liczba połączeń. Może się okazać, że

właśnie połączenia staną na przeszkodzie dalszego rozwoju.

Jednym z ciekawszych rozwiązań tego problemu, nad którym miałem okazję oso-

biście pracować, jest zastosowanie połączeń optycznych. Brzmi to bardzo futury-

stycznie, ale rozwiązanie polega na zbudowaniu wewnątrz układu scalonego świa-

tłowodów, którymi będą transmitowane sygnały. Dzięki temu znacznie wzrosłaby

prędkość transmisji i jej jakość. Innymi możliwymi rozwiązaniami są: zastosowa-

nie transmisji radiowej, ewentualnie wykorzystanie do budowy połączeń nadprze-

wodników. Wszystkie te koncepcje są jednak jeszcze w fazie badań, natomiast pro-

blem połączeń jest widoczny już obecnie i to w komercyjnych zastosowaniach.

Drugi z czynników to odprowadzenie mocy z układu. Otóż w układach cyfrowych,

szczególnie w trakcie ich przełączania, następuje wydzielanie mocy. Na tranzysto-

rach i na ścieżkach jest napięcie, płynie przez nie prąd, więc zgodnie ze wzorami

z modułu drugiego musi wydzielać się moc. Z naszego punktu widzenia moc ta jest

produktem całkowicie ubocznym. Dla nas liczą się tyko napięcia na wyjściach. Jed-

nak coś z tą mocą trzeba począć. Jeśli nie zrobimy nic, to spowoduje ona wzrost

temperatury, a to może w najlepszym wypadku doprowadzić do błędnego działa-

nia układu, a w najgorszym do jego uszkodzenia. Dlatego trzeba ją odprowadzić.

We współczesnych procesorach klasy Pentium IV jest to ok. 100 W. Zważywszy,

że struktura ma wymiar kilku czy kilkunastu milimetrów, możesz sobie wyobra-

zić jaki to problem. A jeśli nie, spróbuj dotknąć włączoną żarówkę 100 W. A teraz

pomyśl, że taką energię musisz odprowadzić z prostokącika o wymiarach kilku czy

kilkunastu milimetrów. I tu pojawia się problem jak to zrobić. Do tej pory stoso-

Rysunek 20

Tranzystor MOS

z kanałem 20 nm

Źródło: Intel. Witryna internetowa.

ftp://download.intel.com/techno-

logy/silicon/

, stan z 2 październi-

ka 2006 r.

24

wane były najczęściej radiatory, często wspomagane wymuszonym obiegiem po-

wietrza (mówiąc inaczej — z wiatraczkiem). Okazuje się, że to już nie wystarcza.

Obecnie powoli wchodzi do użytku chłodzenie cieczowe. Jednak i ono niedługo

może okazać się niewystarczające. A problemem będzie narastał, gdyż coraz więk-

sze częstotliwości, wzrost liczby elementów i połączeń, zmniejszanie wymiarów

tranzystorów i ścieżek, to coraz większe starty mocy. Problem staje się coraz po-

ważniejszy i w tej kwestii również ciągle poszukuje się nowych rozwiązań. Jedną

z ciekawych koncepcji, nad którą również miałem okazję osobiście pracować, jest

chłodzenie mikrokanałowe. Polega ono na wytworzeniu dużej liczby maleńkich

kanalików, którymi przepuszczana jest ciecz. Takie chłodzenie okazuje się bardzo

efektywne, lecz niestety drogie w praktycznym zastosowaniu.

2.3. Subiektywne perspektywy rozwoju

Podsumowując niniejszy temat, chciałbym podzielić się moimi subiektywnymi opi-

niami na temat dalszego rozwoju mikroelektroniki.

W najbliższych latach raczej nie powinniśmy spodziewać się jakiegoś wielkiego

przełomu w dziedzinie mikroelektroniki. Wiodącą technologią pozostanie CMOS,

a wiodącym materiałem półprzewodnikowym krzem. Mam nadzieje, że do komer-

cyjnych produktów wejdzie technologia SOI oraz technologia wykorzystująca tran-

zystory ze złączami Schottky’ego (choć prawdopodobieństwo tego drugiego jest

mniejsze). Proces miniaturyzacji będzie nadal postępował, lecz już nie tak dyna-

micznie jak w ostatnich latach. Zapas technologii w tej dziedzinie jeszcze istnie-

je, ale niestety jego wykorzystanie będzie coraz więcej kosztowało. Natomiast na

pewno będzie rosła liczba elementów w układach scalonych. Tendencję tę potwier-

dzają choćby ostatnie rozwiązania w dziedzinie procesorów. Nie zmieniają się już

tak bardzo częstotliwości pracy, natomiast produkowane są procesory wielordze-

niowe, które mają na jednym układzie kilka niezależnych procesorów. Dodatkowo

wyposażane są one w układy pozwalające lepiej wykorzystać ich możliwości (np.

intelowskie HT), zwiększaniu ulegają szerokości szyn (z 32 na 64 i więcej bitów),

pamięci itd. A to wszystko wiąże się ze zwiększaniem liczby elementów. Dużą prze-

szkodą mogą tu być połączenia oraz konieczna do odprowadzenia moc. Myślę jed-

nak, że znajdą się odpowiednie rozwiązania, które te problemy rozwiążą.

Natomiast nie spodziewałbym się zapowiadanego od dawna „zmierzchu” krzemu

i zastąpienia go innym materiałem półprzewodnikowym. Podobnie nie wydaje mi

się, aby pojawiły się i były stosowane nowe rozwiązania układowe, ewentualnie

nowe przyrządy. Może technologia BiCMOS spróbuje to zmienić, ale to też nic

pewnego. BiCMOS był już wykorzystywany w latach 90. XX w. m.in. do budowy

procesora Pentium Pro, jednak później powrócono do klasycznego CMOS-a. Rów-

nież nie wiązałbym w najbliższym czasie nadziei z nanotechnologią. Choć dzie-

dzina ta jest bardzo silnie promowana — zarówno w środowisku naukowym, jak

i w mediach — to jednak jej rozwiązania są bardzo dalekie od komercyjnych zasto-

sowań. Jeśli w segmencie nowych koncepcji i rozwiązań miałoby się coś zmienić,

to myślę, że stanie się to na styku elektroniki i optyki, a więc liczyłbym na większe

wykorzystanie rozwiązań optoelektronicznych.

Reasumując, w mojej opinii najbliższa przyszłość będzie należała do projektantów

układów scalonych. To ich praca będzie miarą postępu, i to w większym stopniu

niż technologów. Większą uwagę będzie poświęcało się starannemu projektowaniu

oraz optymalizacji. Tym samym upatruję dużych możliwości dla osób z pogranicza

informatyki i elektroniki.

25

Podsumowanie

To już koniec naszego kursu. Przeszliśmy razem naprawdę długą drogę, zaczynając

od samych podstaw, a więc od pojęć związanych z elektrycznością, przez podstawy

elektroniki cyfrowej, aż do układów scalonych. Tej ostatniej kwestii poświęciliśmy

najwięcej uwagi. Poznałeś zasady projektowania oraz wykonywania układów sca-

lonych w technologii CMOS. Co więcej, w trakcie projektu masz możliwości sa-

modzielnego wykonania i przebadania prostego układu scalonego. Ostatni moduł

poświęciliśmy przyjrzeniu się mikroelektronice i jej przyszłości. Zawarłem w nim

bardzo wiele (choć mało szczegółowych) informacji. Najbardziej zależało mi, abyś

„osłuchał” się z pewnymi pojęciami, aby nie były ci one obce, kiedy spotkasz je,

czytając literaturę. Z drugiej strony chciałem, abyś krytycznym okiem spojrzał na

szanse i zagrożenia, które stoją przed mikroelektroniką w najbliższej przyszłości.

W trakcie całego kursu mówiłem o rzeczach, które są dla mnie wielką życiową pa-

sją i dlatego wielu rzeczom poświęciłem może zbyt dużo, a za mało miejsca. Nie-

mniej jednak, jeśli cokolwiek cię zainteresowało, zachęcam do dalszego samodziel-

nego kształcenia w tej dziedzinie — naprawdę warto. Choć wiem, że jesteś infor-

matykiem, mam nadzieję, że udało mi się cię przekonać, że wiedza z dziedziny mi-

kroelektroniki jest ci potrzebna, a już na pewno nie zaszkodzi. Nie wiem, czy po

skończeniu tego kursu jeszcze kiedykolwiek zainteresujesz się mikroelektroniką.

Jeśli tak, to będzie mój największy sukces.

26

Bibliografia

1. Beck R., 1991: Technologia krzemowa, PWN, Warszawa.

2. Europractice. Witryna internetowa.

, stan z 26 wrze-

śnia 2006 r.

3. IBM. Witryna internetowa.

, stan z 26 września 2006 r.

4. Intel. Witryna internetowa.

, stan z 26 września 2006 r.

5. International Technology Roadmap for Semiconductors. Witryna internetowa.

, stan z 26 września 2006 r.

6. Kalisz J., 1998: Podstawy elektroniki cyfrowej, Wydawnictwa Komunikacji

i Łączności, Warszawa.

7. Marciniak W., 1984: Przyrządy półprzewodnikowe i układy scalone, Wydaw-

nictwa Naukowo-Techniczne, Warszawa.

8. Marciniak W., 1991: Przyrządy półprzewodnikowe MOS, Wydawnictwa Na-

ukowo-Techniczne, Warszawa.

9. Massucci J., 2001: Projekt Milenium, Wydawnictwo Amber sp. z o. o., Warszawa.

10. Napieralska M., Jabłoński G., 2002: Podstawy mikroelektroniki, Wydawnic-

twa PŁ, Łódź.

11. University of California, Berkeley. Witryna internetowa.

, stan z 26 września 2006 r.

Document Outline

- Przyszłość mikroelektroniki

Wyszukiwarka

Podobne podstrony:

Modul 4 Technologie mikroelektroniczne

Modul 2 Podstawowe elementy stosowane w mikroelektronice

Modul 2 Mikroekonomiczne podstawy dokonywania wyborow ekonomicznych przez przedsiebiorstwa

przyszlosciowe zawody

modul I historia strategii2002

Komunikacja Moduł (2)

23 Metody montażu w mikroelektronice

Moduł IV WŁADZA W013

MODUŁ POWIETRZE

Modul 1 Misja, strategia, planowanie

więcej podobnych podstron