✃

DATENBLATT

6/99

AT90S2313

Mikroprozessoren und Peripherie

11.009c

AT90S2313

Mikroprozessoren und Peripherie

11.009a

DATENBLATT

6/99

35

Elektor

6/99

Port D (PD0...PD6)

Port D ist ein bidirektionaler 7-bit-I/O-Port mit internen

Pullup-Widerständen. Die Ausgangsbuffer von Port D kön-

nen 20 mA aufnehmen (sink). Wird eine Leitung von Port

D als Eingang benutzt und ist der betreffende interne Pul-

lup-Widerstand aktiviert, fließt extern Strom nach Masse.

Die Leitungen von Port D können auch bestimmte speziel-

le Funktionen des AT90S2313 übernehmen; näheres im

Datenblatt des Herstellers.

RESET

Reseteingang: Low an diesem Anschluß für die Dauer von

mindestens zwei Maschinenzyklen bei laufendem Taktos-

zillator setzt den AT90S2313 zurück.

XTAL1

Eingang des als Taktoszillator schaltbaren invertierenden

Verstärkers und Eingang der internen Taktsignalverarbei-

tung.

XTAL2

Ausgang des als Taktoszillator schaltbaren invertierenden

Verstärkers.

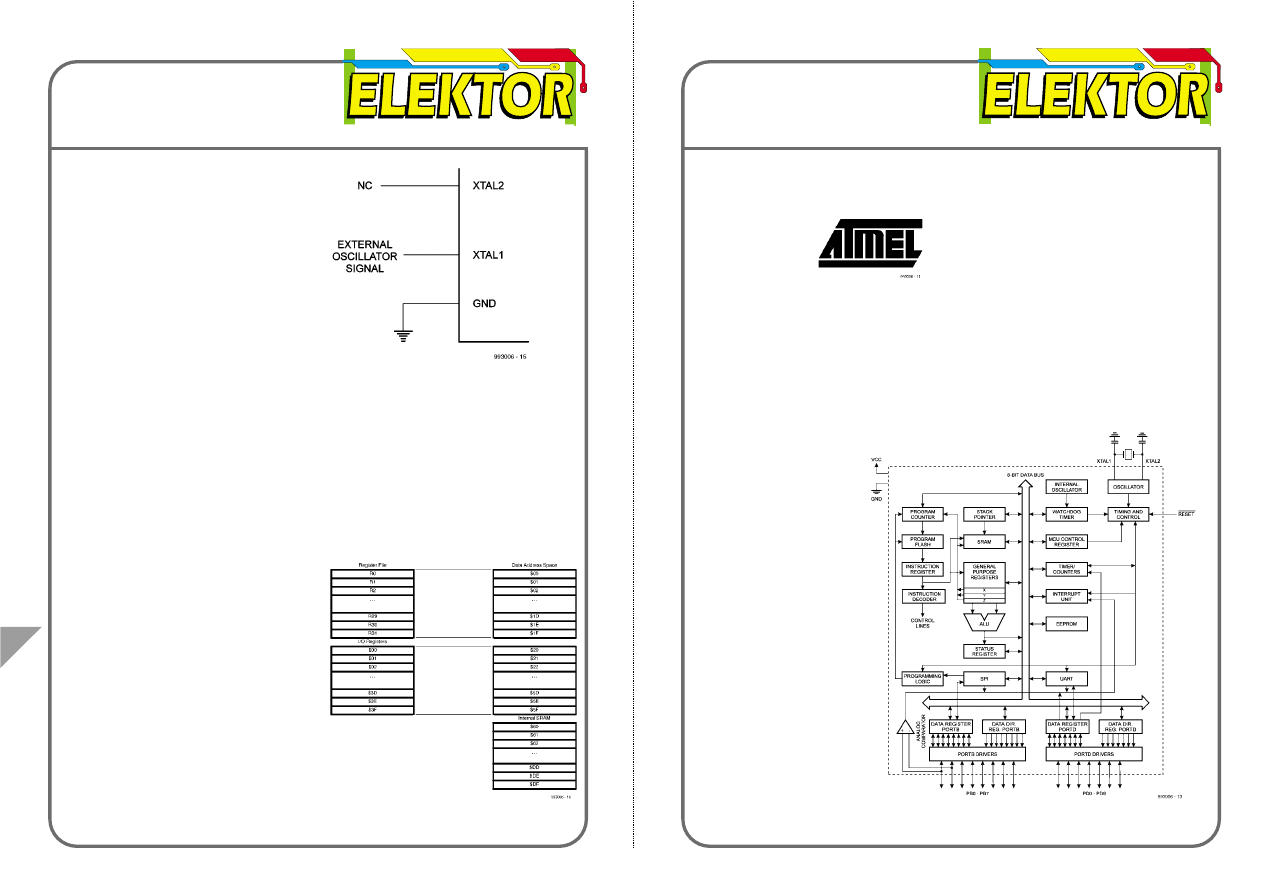

Quarz-Oszillator

XTAL1 und XTAL2 sind Eingang und Ausgang eines inver-

tierenden Verstärkers, der wie in Bild 2 dargestellt als Takt-

oszillator geschaltet werden kann. Verwendbar ist sowohl

ein Quarz als auch ein Keramikschwinger. Beim Betrieb

mit externem Taktsignal bleibt XTAL2 offen, und XTAL1

wird wie Bild 3 zeigt mit der Taktsignalquelle verbunden.

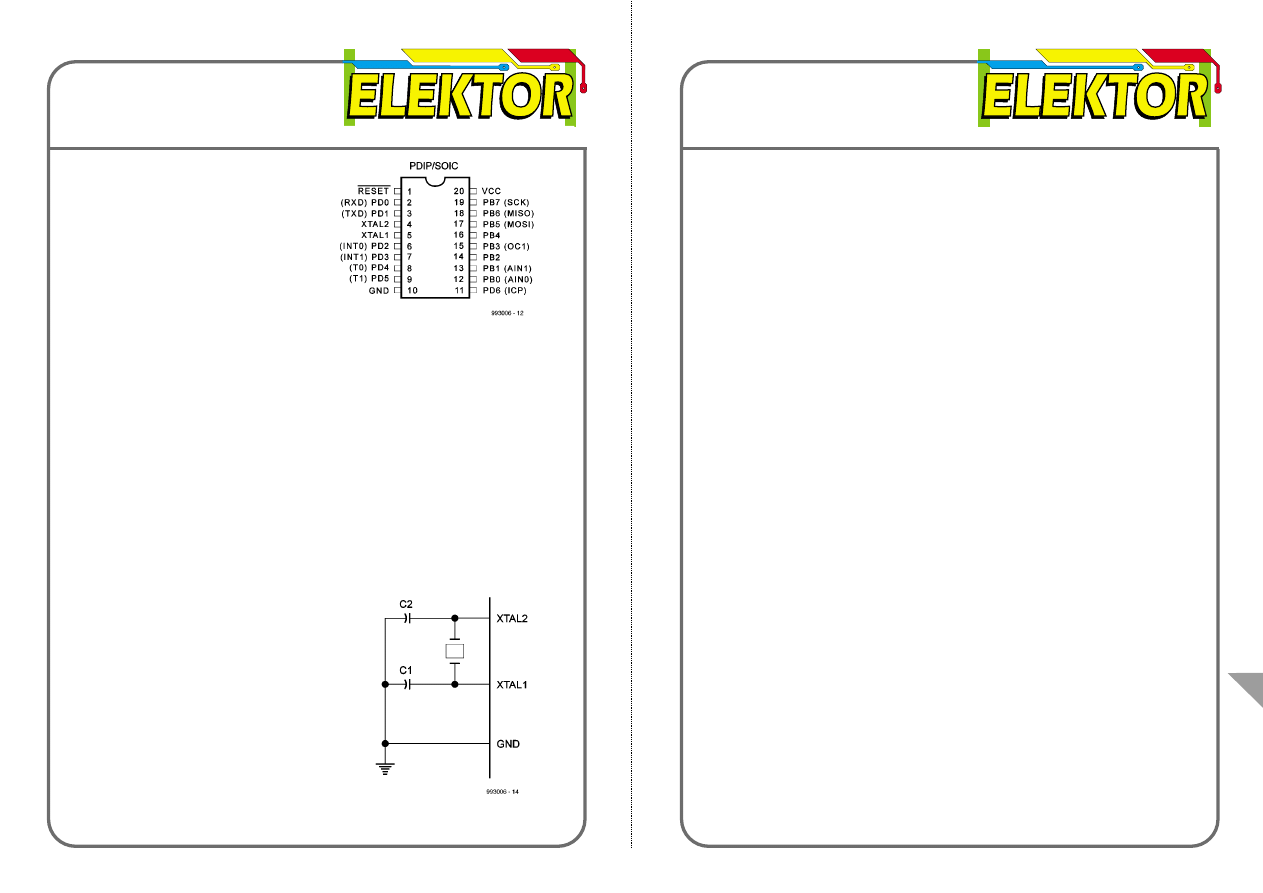

SRAM Datenspeicher

Aus Bild 4 ist die Datenspeicherorganisation des

AT90S2313 ersichtlich.

Die 224 Datenspeicheradressen sind auf die Arbeitsregi-

ster, die I/O-Register und den SRAM Daten speicher ver-

teilt. Die ersten 96 Adressen gehören zu den Arbeitsregi-

stern und I/O-Registern, die restlichen 128 zum SRAM-

Datenspeicher.

Auf den Datenspeicher können folgende Adressierarten

angewendet werden: Direkt, Indirekt, Indirekt mit Displace-

ment, Indirekt mit Prädekrement und Indirekt mit Postin-

krement. Bei den indirekten Adressierungsarten müssen

die Pointer in den Registern R26...R31 der Registerbank

stehen.

Die direkte Adressierung ist auf alle Adressen des SRAM

Datenspeichers anwendbar.

Mit der Adressierungsart ”Indirekt mit Displacement” sind

63 Speicherplätze erreichbar, die Basisadresse muß in den

Registern Y und Z stehen.

Bei den indirekten Adressierungsarten mit Prädekrement

bzw. Postinkrement werden die Register X, Y und Z dekre-

mentiert bzw. inkrementiert.

Auf die 32 Arbeitsregister, 64 I/O-Register und 128 byte

SRAM Datenspeicher des AT90S2313 kann in allen

genannten Adressierungsarten direkt zugegriffen werden.

AT90S2313

8-bit-Mikrocontroller mit 2 Kbyte Flash-Speicher

Hersteller:

Atmel Inc.

Internet: www.atmel.com

Email: avr@atmel.com

Distributoren:

A: Codico, Tel.: 01 / 86 30 50

CH: Anatec, Tel.: 041 / 7 48 32 32

D: Ineltek, Tel.: 073 21 / 93 85 - 0

MSC Vertrieb, Tel.: 0 72 49 / 9 10 - 0

Eigenschaften:

➥ AVR High Performance Low Power RISC Architektur

➥ 118 leistungsstarke Befehle, großteils in einem Taktzy-

klus

➥ 2 Kbyte Flash-Speicher, lösch-

und herunterladbar

- SPI Serielles Interface zum

Programm-Download

- Lebensdauer: 1.000

Schreib/Lese-Zyklen

➥ 128 byte EEPROM

- Lebensdauer: 100.000

Schreib/Lese-Zyklen

➥ 128 byte internes RAM

➥ 32 x 8 Arbeitsregister zur allge-

meinen Verwendung

➥ 15 programmierbare I/O-Leitun-

gen

➥ V

CC

= 2,7...6,0 V

➥ Vollständig statischer Betrieb

möglich:

- 0...10 MHz bei 4,0...6,0 V

- 0...4 MHz bei 2,7...6,0 V

➥ Bis zu 10 MIPs bei 10 MHz Takt

➥ Ein 8-bit-Timer/Zähler mit separa-

tem Vorteiler

➥ Ein 16-bit-Timer/Zähler mit sepa-

ratem Vorteiler, Compare- und

Capture-Modus

➥ Vollduplex UART

➥ Einstellbare 8-, 9- oder 10-bit-

Pulsbreitenmodulation

➥ Externe und interne Interruptquel-

len

➥ Programmierbarer Watchdog-Timer mit integriertem

Oszillator

➥ Integrierter Analogkomparator

➥ Bereitschafts- und Energiesparbetrieb

➥ Programmsperre für Softwaresicherheit

➥ 20-poliges Gehäuse

Anwendungsbeispiel:

WAV-Player, Elektor 02/99

Kurzbeschreibung:

Der AT90S2313 ist ein in CMOS-Technologie gefertigter 8-

bit-Mikrocontroller, der auf einer erweiterten RISC-Architek-

tur mit der geschützten Bezeichnung AVR basiert. Da fast

alle leistungsstarken Befehle in nur einem Taktzyklus abge-

arbeitet werden, erreicht der AT90S2313 einen Durchsatz

Bild 1. Funktionsschema AT90S2313

Bild 3. Steuerung durch externes Taktsignal

Bild 4. SRAM-Organisation

✃

AT90S2313

Mikroprozessoren und Peripherie

11.009d

AT90S2313

Mikroprozessoren und Peripherie

11.009b

DATENBLATT

6/99

DATENBLATT

6/99

36

Elektor

6/99

von 1 MIPS/MHz. Damit ist dem Entwickler ein optimaler

Kompromiß zwischen Leistungsaufnahme und Arbeitsge-

schwindigkeit möglich.

Durch die AVR-Architektur werden 32 universell verwend-

bare Arbeitsregister mit einem erweiterten Befehlssatz

kombiniert. Alle Register sind mit der Arithmetik-Logik-

Einheit (ALU) direkt verbunden, so daß auf zwei unabhän-

gige Register mit nur einem Befehl (in einem Taktzyklus)

zugegriffen werden kann. Da die AVR-Architektur den Pro-

grammcode sehr effizient nutzt, ist der erreichte Durch-

satz konventionellen CISC-Controllern bis zum Faktor 10

überlegen.

Der AT90S2313 hat folgende Eigenschaften: 2 Kbyte in der

Schaltung programmierbarer Flash-Speicher, 128 byte

EEPROM, 128 byte SRAM, 15 universelle I/O-Leitungen,

32 Arbeitsregister für allgemeine Verwendung, flexible

Timer/Zähler mit Compare-Funktionen, Verarbeitung inter-

ner und externer Interrupts, programmierbarer serieller

UART, programmierbarer Watchdog-Timer mit internem

Oszillator, serieller SPI-Port zum Flash-Speicher-Download

sowie zwei softwaresteuerbare Energiespar-Betriebsarten.

Im Idle-Modus wird die CPU abgeschaltet, während das

SRAM, die Timer/Zähler, der SPI-Port und das Interruptsy-

stem in Funktion bleiben. Beim Power-Down-Modus wer-

den die Registerinhalte gerettet und der Oszillator angehal-

ten, alle übrigen Funktionen sind bis zum nächsten Inter-

rupt oder Hardware-Reset deaktiviert.

Der Controller wird von Atmel in High-Density Non-Volati-

le Speichertechnologie gefertigt. Die Neuprogrammierung

des integrierten Flash-Speichers kann über den seriellen

SPI-Port in der Schaltung oder mit einem externen Pro-

grammiergerät auf konventionelle Weise durchgeführt

werden.

Die 8-bit-CPU mit erweitertem RISC-Befehlssatz und der

im System programmierbare Flash-Speicher machen den

AT90S2313 zu einem leistungsstarken, flexiblen und

kostengünstigen Mikrocontroller für zahlreiche Anwendun-

gen. Die Hard- und Software-Entwicklung wird von einem

umfangreichen Tool-Angebot unterstützt: Unter anderem

stehen C-Compiler, Makro-Assembler, Programm-Debug-

ger und -Simulatoren, In-circuit-Emulatoren und Evaluati-

on-Kits zur Verfügung.

Anschlußbeschreibung:

VCC

Betriebsspannung.

GND

Masse.

Port B (PB0...PB7)

Port B ist ein bidirektionaler 8-bit-I/O-Port. Die Portleitun-

gen können einzeln (bitweise) mit internen Pullup-Wider-

ständen verbunden werden. Die Leitungen PB0 und PB1

dienen auch als positiver Eingang (AIN0) und negativer

Eingang (AIN1) des integrierten analogen Komparators.

Die Ausgangsbuffer von Port B können 20 mA aufnehmen

(sink) und dadurch LEDs direkt steuern. Wird eine Leitung

von Port B als Eingang benutzt und ist der betreffende

interne Pullup-Widerstand aktiviert, fließt extern Strom

nach Masse. Die Leitungen von Port B können auch

bestimmte spezielle Funktionen des AT90S2313 überneh-

men; näheres im Datenblatt des Herstellers.

I/O-Adressen

Der I/O-Adreßraum des AT90S2313 ist wie folgt definiert:

Adresse

Bezeichnung

Funktion

$3F ($5F)

SREG

Status Register

$3D($5D)

SPL

Stack Pointer Low

$3B($5B)

GIMSK

General Interrupt Mask Register

$3A($5A)

GIFR

General Interrupt Flag Register

$39 ($59)

TIMSK

Timer/Counter Interrupt Mask Register

$38 ($58)

TIFR

Timer/Counter Interrupt Flag Register

$35 ($55)

MCUCR

MCU General Control Register

$33 ($53)

TCCR0

Timer/Counter 0 Control Register

$32 ($52)

TCNT0

Timer/Counter 0 (8-bit)

$2F ($4F)

TCCR1A

Timer/Counter 1 Control Register A

$2E ($4E)

TCCR1B

Timer/Counter 1 Control Register B

$2D($4D)

TCNT1H

Timer/Counter 1 High Byte

$2C($4C)

TCNT1L

Timer/Counter 1 Low Byte

$2B($4B)

OCR1H

Output Compare Register 1 High Byte

$2A($4A)

OCR1L

Output Compare Register 1 Low Byte

$25 ($45)

ICR1H

T/C 1 Input Capture Register High Byte

$24 ($44)

ICR1L

T/C 1 Input Capture Register Low Byte

$21 ($41)

WDTCR

Watchdog Timer Control Register

$1E ($3E)

EEAR

EEPROM Address Register

$1D($3D)

EEDR

EEPROM Data Register

$1C($3C)

EECR

EEPROM Control Register

$18 ($38)

PORTB

Data Register, Port B

$17 ($37)

DDRB

Data Direction Register, Port B

$16 ($36)

PINB

Input Pins, Port B

$12 ($32)

PORTD

Data Register, Port D

$11 ($31)

DDRD

Data Direction Register, Port D

$10 ($30)

PIND

Input Pins, Port D

$0C($2C)

UDR

UART I/O Data Register

$0B($2B)

USR

UART Status Register

$0A($2A)

UCR

UART Control Register

$09 ($29)

UBRR

UART Baud Rate Register

$08 ($28)

ACSR

Analog Comparator Control und Status Register

Alle I/O- und sonstigen peripheren Funktionen werden über Adressen im I/O-Adressenbereich gesteuert. Beim Zugriff auf

die I/O-Ports mit den Befehlen IN und OUT werden Daten zwischen der aus 32 Universalregistern bestehenden Register-

bank und den I/O-Registern kopiert. Die I/O-Register im Bereich $00...$1F sind mit den Befehlen SBI und CBI direkt bita-

dressierbar. Der Zustand einzelner Bits kann in diesem Bereich mit den Befehlen SBIS und SBIC abgefragt werden. Nähe-

res zu den Befehlen ist im Datenblatt des Herstellers zu finden.

Bei Anwendung der I/O-spezifischen Befehle IN, OUT, SBIS und SBIC sind die Adressen $00...$3F gültig. Zu diesen

Adressen ist der Wert $20 zu addieren, falls die I/O-Register als SRAM adressiert werden. Die SRAM-Adressen sind in

der Liste in Klammern angegeben.

Die Funktionen der diversen I/O- und Peripherie-Steuerregister werden im Datenblatt des Herstellers ausführlich erläutert.

Anschlußbelegung

Bild 2. Taktoszillatorschaltung

Wyszukiwarka

Podobne podstrony:

Datenblatt KRC4

Datenblaetter im Web

EuroSprinter ES64 U4 2009 DE Datenblatt Laenderpakete CZ HR H PL SK SLO

EuroSprinter ES64 U4 2009 DE Datenblatt Laenderpakete A CH D I NL

Datenblatt iXSeries inventux DE

datenblatt jetnet3005 SCSL5NQEFRRAQNXGD5JIHJOVKGB526VCFKXEYHQ

fetch datenblatt attiny26

fetch datenblatt 24c64

HCM12T Datenblatt Web

AVR091 Replacing AT90S2313 with ATtiny2313

Programowanie atmela AT90S2313, LAKI, cyfra krack, Unloper

fetch datenblatt cny70

Datenblatt STC Messung inventux EN

Datenblatt 118

fetch datenblatt lm358

Datenblatt KRC4

Datenblaetter im Web

Datenblatt 2SA1930, 2SC5171

więcej podobnych podstron