ś

Sterowanie wyświetlacza

LCD typu HD44780

LCD typu HD44780

Wyświetlacz LCD

1

Laboratorium Projektowania Systemów Cyfrowych AGH WFiIS

2013‐10‐07

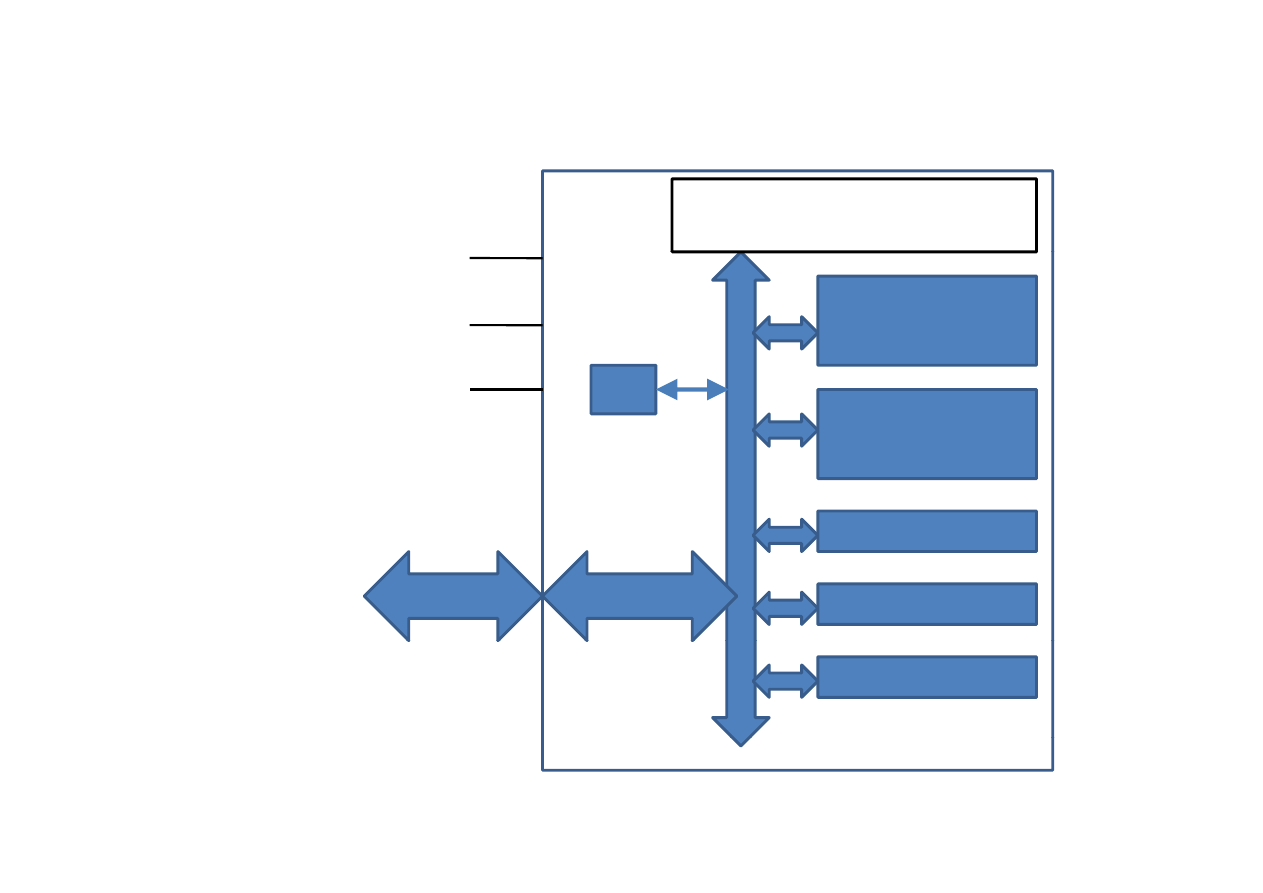

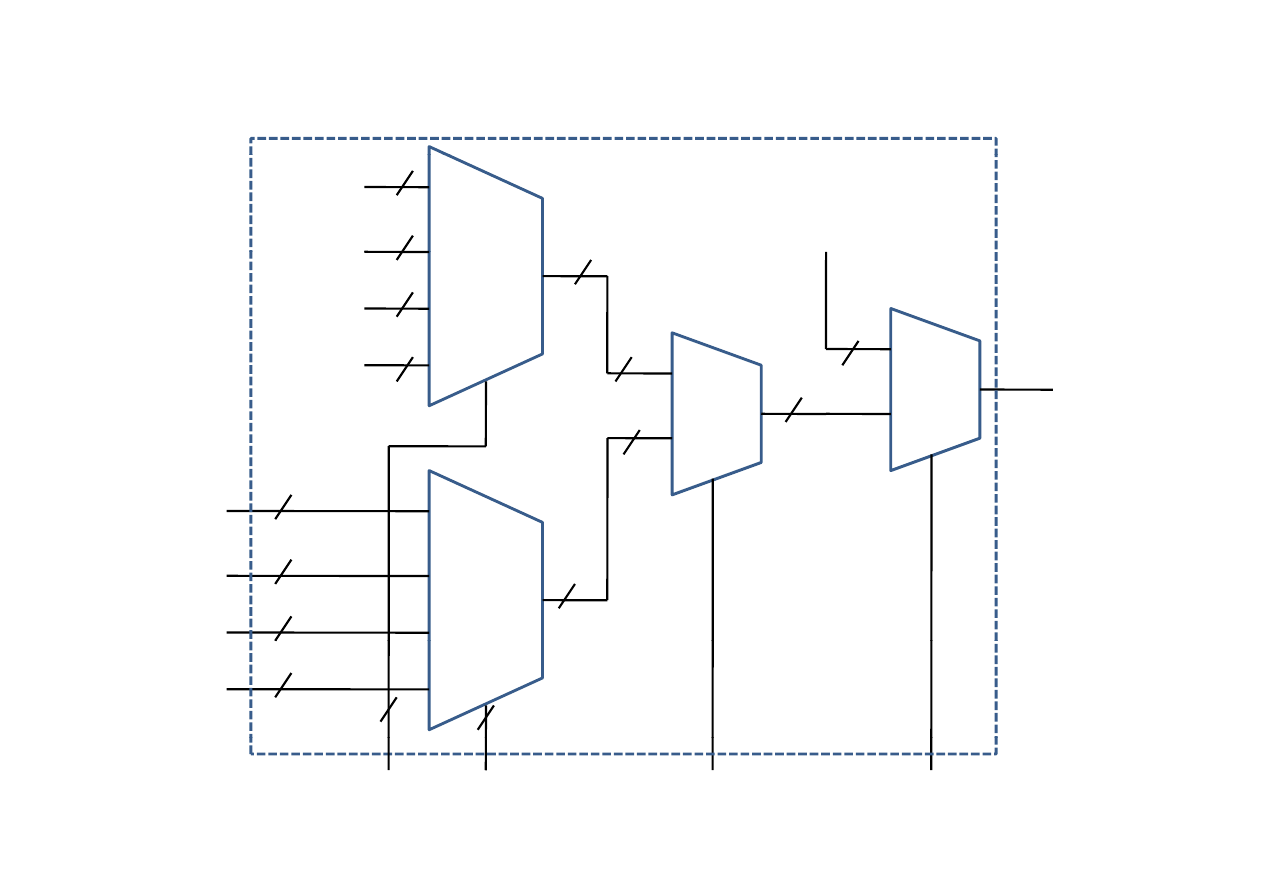

Matrycowy moduł LCD

Wyświetlacz LCD

E

RW

CG RAM

RS

DD RAM

BF

DB[7:0]

Licznik Adresu

DB[7:0]

Rejestr Danych

Rejestr Komendy

BF – Busy Flag –

Wyświetlacz LCD

2

typ HD44780

y

g

znacznik zajętości magistrali

2013‐10‐07

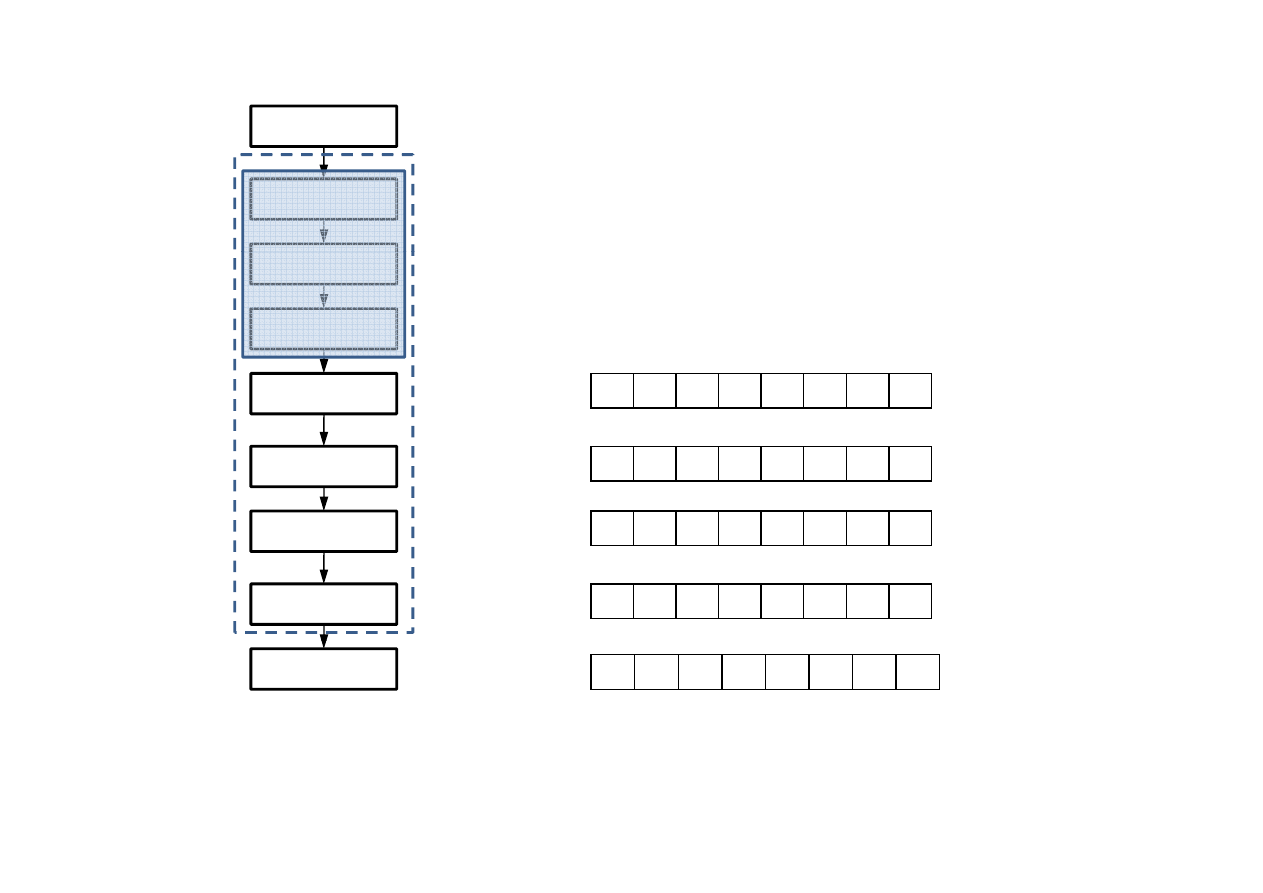

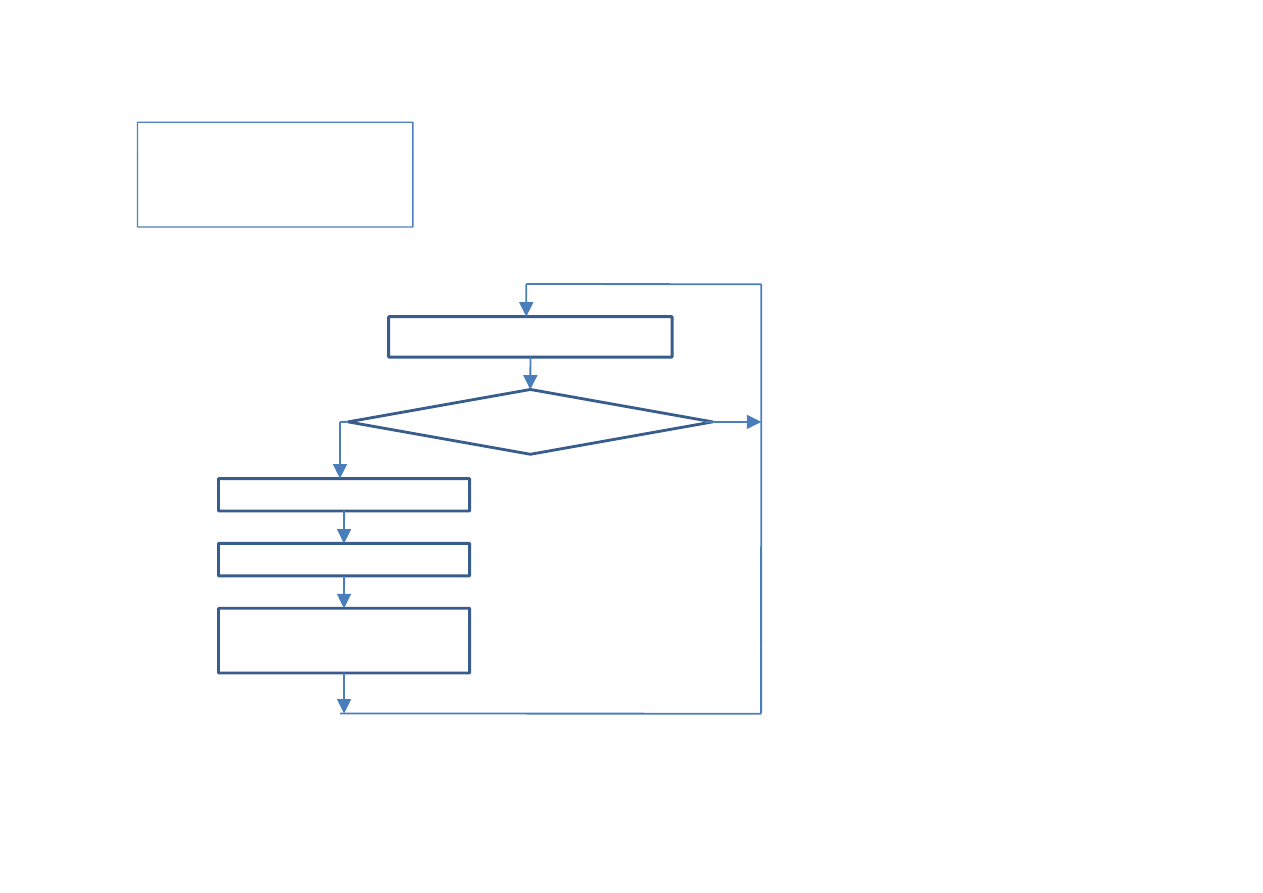

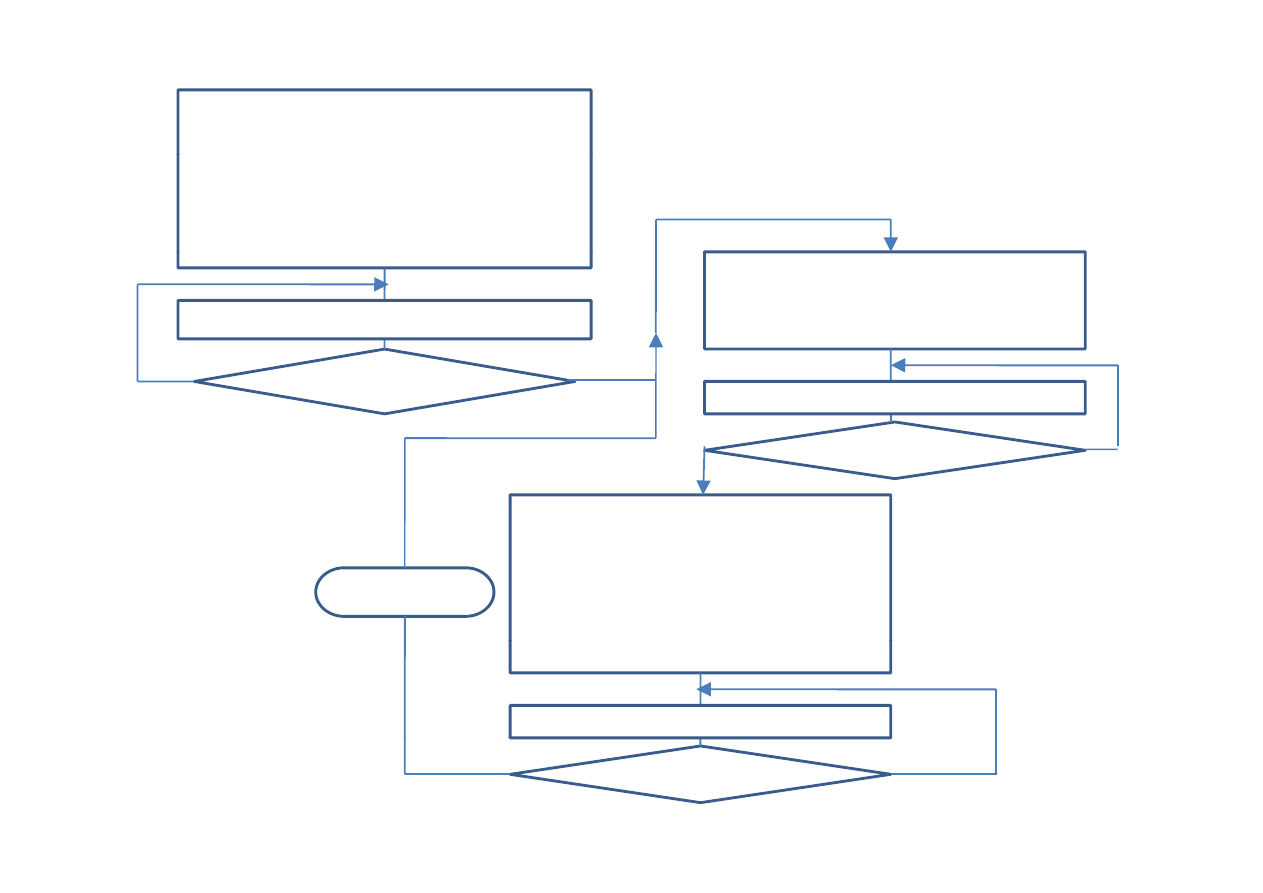

Power On

≥15ms

Incjalizacja modułu LCD

38H

≥4,1ms

uenc

e

38H

38H

≥40µs

≥100µs

R

ese

t Seq

DL – 8 bit (1) 4 bit0)

38H

Function set

0

0

1

DL

N

F

X

X

≥40µs

R

ID – increment(1),

d

t0)

DL – 8 bit (1), 4 bit0)

N –2 lines(1), 1 line(0)

F – 5*7 dots(0)

06H

Entry mode

0

0

0

0

0

1

ID

S

≥40µs

0EH

Display on/off

0

0

0

0

1

D

C

B

≥40µs

D – display on(1), off(0)

C – cursor on(1), off(0)

B blink on(1) off(0)

decrement0)

S – shift on(1), off(0)

p y

/

µ

01H

Display clear

0

0

0

0

0

0

0

1

≥1,64ms

B ‐ blink on(1), off(0)

CCH

Set DD RAM

address

≥40µs

1

A6

A5

A4

A3

A2

A1

A0

CCH

oznacza ostatnie cztery widoczne pozycje w drugiej linii

Wyświetlacz LCD

3

2013‐10‐07

CCH

oznacza ostatnie cztery widoczne pozycje w drugiej linii.

Proces inicjalizacji ‐ komendy:

reset sequence

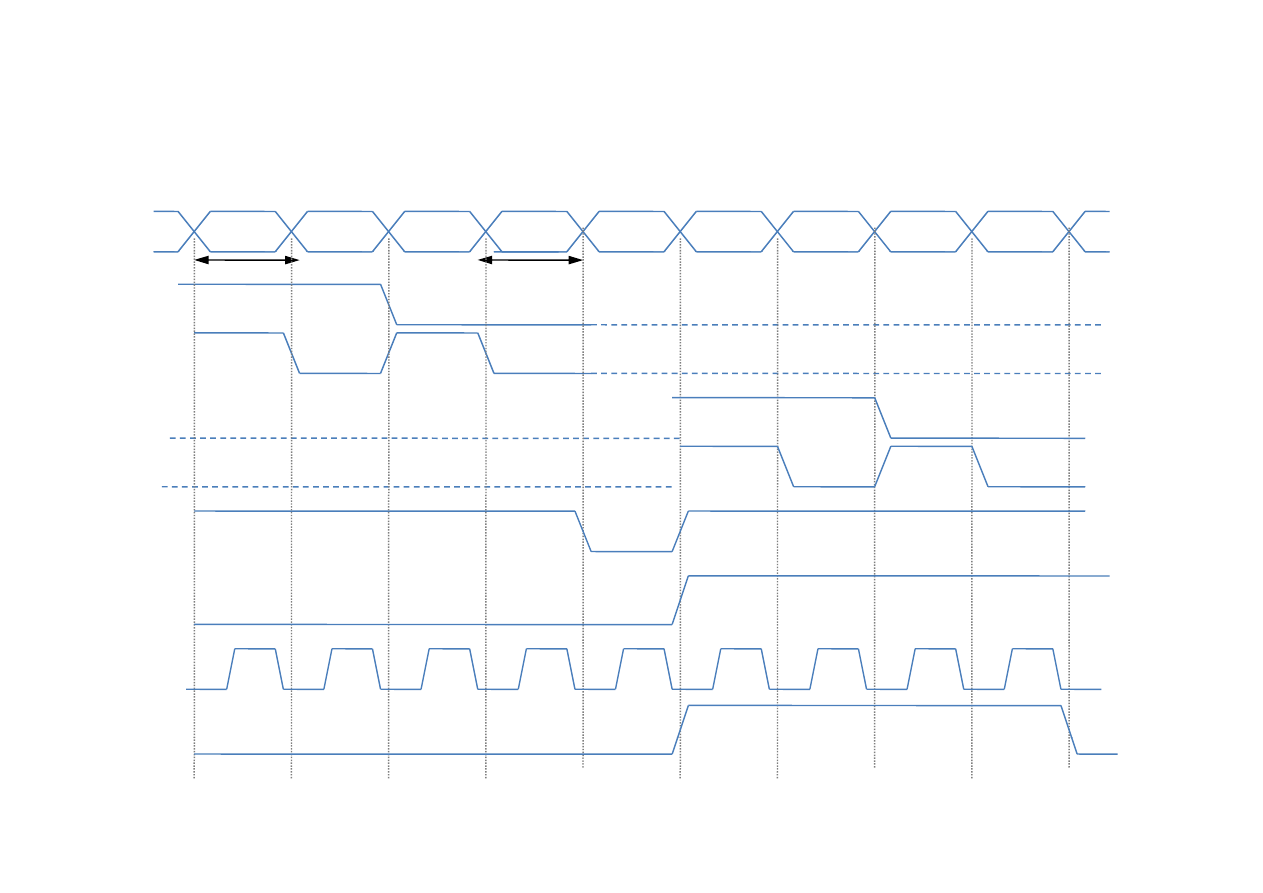

Przebiegi czasowe

DB

38

06

0E

01

CC

39

35

33

31

Na wyświetlaczu pojawią się

cyfry: 9, 5, 3, 1

reset sequence

&

function set

entry

mode

display

on

display

clear

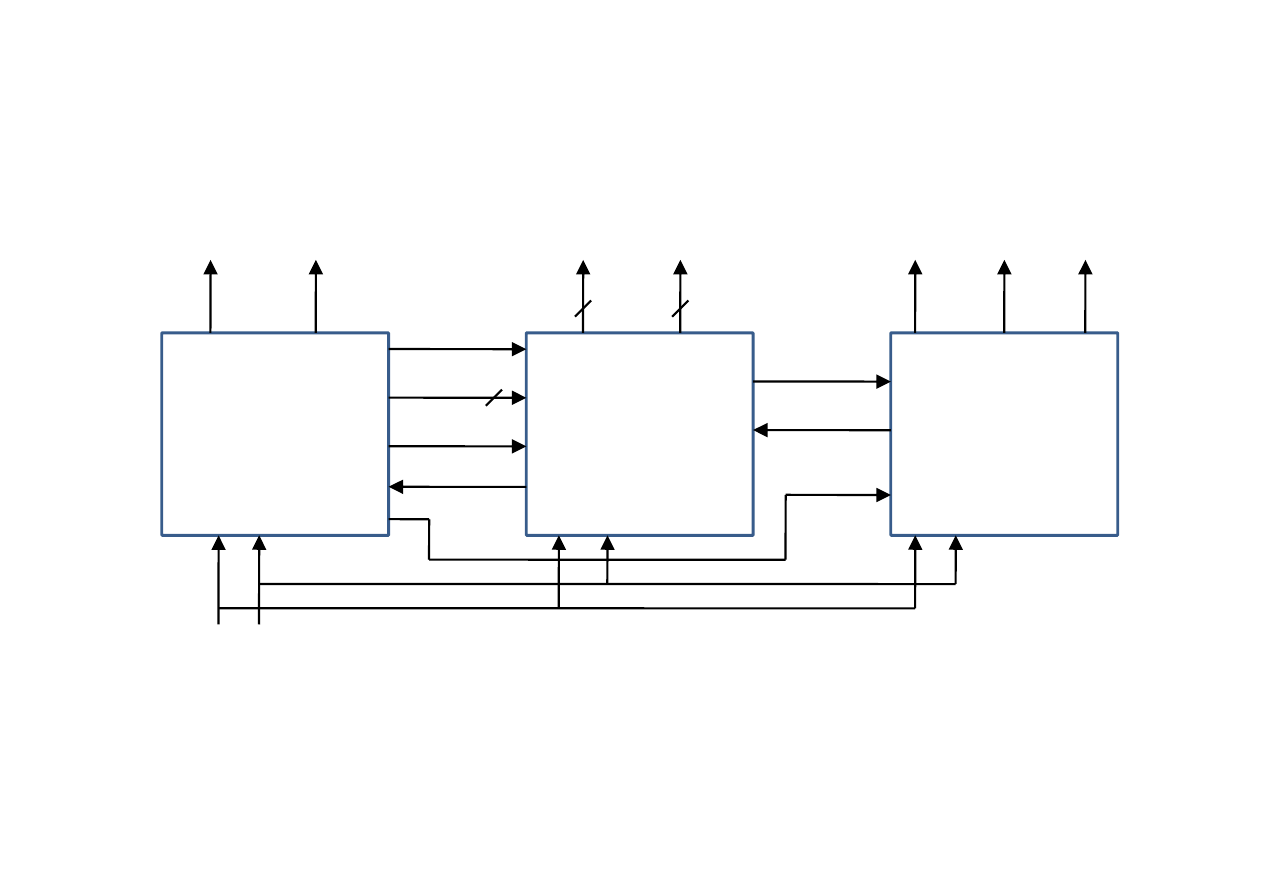

Adres

DD RAM

init_sel

[1:0]

>4,3ms

>1,6ms

3

2

1

0

[1:0]

mux_sel

3

2

1

0

[1:0]

DB sel

3

2

1

0

_

data_sel

E

RS

Wyświetlacz LCD

4

RS

2013‐10‐07

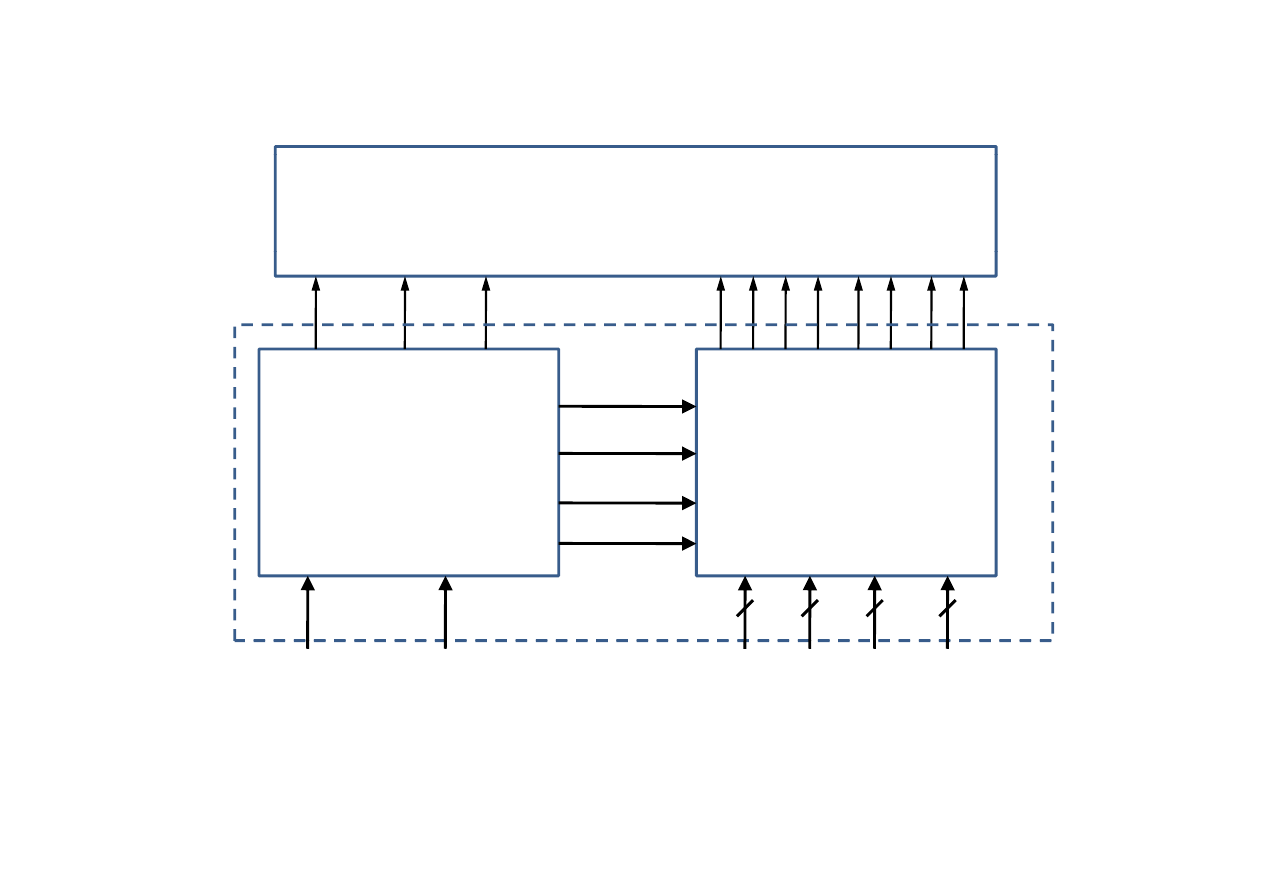

16 x 2 matryca LCD

D

B7

B

D6

D

B5

B

D4

D

B3

B

D2

D

B1

B

D0

R

W

R

S

D

B

D

B

D

B

D

B

E

R

R

E_out RW_out RS_out

LCD ontroller

DB_out[7:0]

DB_sel

mux_sel

LCD_controller

LCD_dp

t3

t0

data_sel

init_sel

count3 – count0

4

4

4

4

LCD_driver

Dane do wyświetlenia

reset

clk_1ms

5

Wyświetlacz LCD

2013‐10‐07

LCD_dp

0

1

Clear

6’b000001

Display on

6’b001110

init_reset_mux

8’hcc

6

Set DD RAM address

1

2

0

Entry mode

6’b000110

Function set

6’b111000

6

{2’b00,init_reset_mux}

Wyjście z FPGA

6

6

3

0

1

0

1

DB_out

Function set

6 b111000

Stałe inicjalizacji

8

8

8

data outx

yjśc e

do wyświetlacza

6

0

1

count3

{4’b0011 counter mux}

8

data_outx

4

1

2

count2

count1

4

{4 b0011,counter_mux}

4

4

2

3

count0

counter_mux

4

4

2

2

init_sel

mux_sel

data_sel

DB_sel

6

Wyświetlacz LCD

2013‐10‐07

2

Wyjście z FPGA

do wyswietlacza

Do modułu ścieżki danych

LCD dp

E

_out

R

W_out

R

S_out

do wyswietlacza

t_sel

_sel

a_sel

sel

Do modułu ścieżki danych

LCD_dp

lcd_enable

E

R

R

ini

mux

dat

DB_

2

2

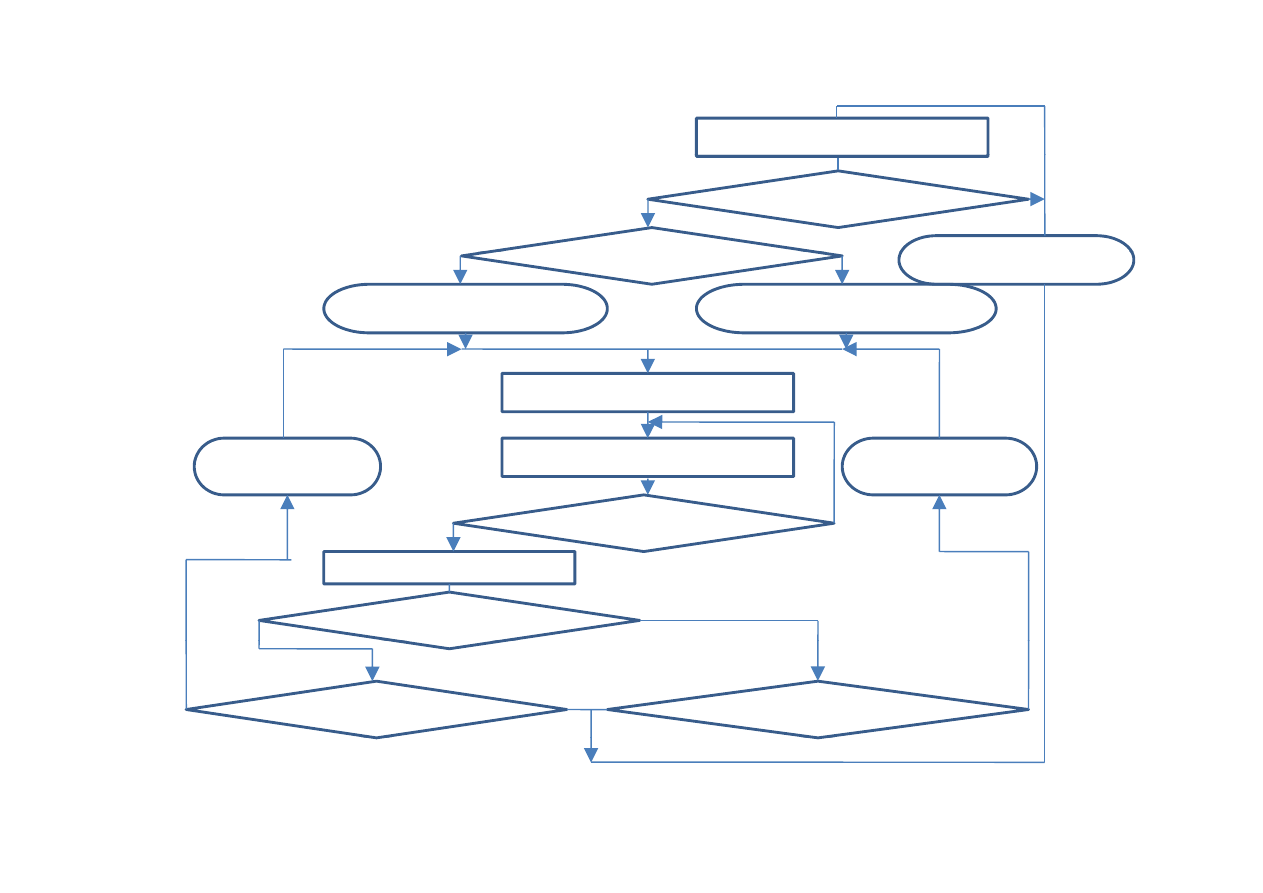

main controller

lcd init refresh

write cycle

lcd_cnt

mode

wr_enable

wr_finish

2

_

_

_

_ y

lcd_finish

reg_sel

reset clk 1ms

_

LCD_INIT=1

LCD_REF=0

INIT CONST NO 4

REF DATA NO 4

Proponowane parametry:

7

Wyświetlacz LCD

2013‐10‐07

INIT_CONST_NO=4

REF_DATA_NO=4

write_cycle

assign

g

RS_out=reg_sel

RW_out=0

wr finish=0

idle

wr_enable?

_

1

0

E_out=1

init

E_out=0

Eout

endwr

wr_finish=1

8

Wyświetlacz LCD

2013‐10‐07

lcd_finish=0

idle

LCD_init_refresh

lcd_enable?

d ?

l d fi i h 1

0

1

1

0

mode?

mux_sel<=lcd_cnt

init_sel<=lcd_cnt

lcd_finish=1

wr_enable=1

data

i it

l

l

wr_enable=0

data1

wr_finish?

init_sel<=

init_sel-1

mux_sel<=

mux_sel-1

1

0

mode?

endlcd

1

0

mux_sel?

init_sel?

1

0

1

9

Wyświetlacz LCD

2013‐10‐07

lcd_enable=1

lcd_cnt=INIT_CONST_NO – 1

main_controller

idle

DB_sel=1

data_sel=0

reg_sel=0

mode=LCD INIT

lcd_enable=1

lcd_cnt=0

DB_sel=0

mode LCD_INIT

0

addr

lcd_enable=0

init

l d fi i h?

lcd_finish?

1

1

0

0

lcd_enable=0

addr1

lcd_finish?

lcd_enable=1

lcd cnt=REF DATA NO – 1

ref

lcd_cnt=REF_DATA_NO

1

DB_sel=1

data_sel=1

reg_sel=1

reg_sel=0

mode=LCD_REF

lcd_enable=0

ref1

lcd_finish?

1

0

10

Wyświetlacz LCD

2013‐10‐07

Wyszukiwarka

Podobne podstrony:

HD44780 LCD id 199910 Nieznany

Budowa monitora LCD id 94314 Nieznany (2)

How to Use a Graphic LCD id 206 Nieznany

3 LCD LCD MSP430 id 755238 Nieznany (2)

CRT LCD PDP OLED DLP id 120436 Nieznany

parametry lcd crt id 349183 Nieznany

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

LTC1729 id 273494 Nieznany

D11B7AOver0400 id 130434 Nieznany

więcej podobnych podstron