Architektura komputerów

Procesory superskalarne

Procesor superskalarny

●

Termin superskalarny określa

procesory, które mogą wykonywać dwie

lub więcej instrukcje skalarne

(arytmetyczne, logiczne) jednocześnie.

●

Rozwiązanie to stosuje się w

nowoczesnych procesorach w celu

zwiększenia wydajności.

Ograniczenia

Następujące ograniczenia uniemożliwiają

równoległe wykonywanie instrukcji:

●

zależność danych

●

zależność proceduralna

●

konflikt dotyczący zasobów

●

zależność wyjściowa

●

antyzależność

Zależność danych

add r1,r2

mov r3,r1

Drugi rozkaz może być pobrany i zdekodo-

wany, ale nie może być wykonany zanim

nie zostanie wykonany pierwszy rozkaz,

ponieważ potrzebne są dane tworzone

przez pierwszy.

Zależności proceduralne

●

Obecność rozgałęzień w sekwencji

rozkazów ma jeszcze większy wpływ na

potok superskalarny, niż na

pojedynczy.

●

Straty spowodowane przez

rozgałęzienie mogą być jeszcze

większe, ponieważ więcej jest

wykonywane w jednostce czasu.

Konflikt dotyczący zasobów

●

Konflikt dotyczący zasobów polega na

jednoczesnym rywalizowaniu dwóch

instrukcji o te same zasoby.

Przykładami takich zasobów są:

–

pamięć

–

magistrale

–

kanały wejścia-wyjścia

●

Takie konflikty mogą być rozwiązywane

przez zwielokratnianie zasobów lub

odpowiednią organizację.

Zależność wyjściowa

●

W przykładowym kodzie:

R3:=R3 op R5

(I1)

R4:=R3+1

(I2)

R3:=R5+1

(I3)

R7:=R3 op R4

(I4)

●

Rozkaz I3 nie jest zależny od I1, ale nie

może być wykonany przed nim, gdyż

wówczas I4 będzie miał niewłaściwą

zawartość rejestru R3.

Antyzależność

R3:=R3 op R5

(I1)

R4:=R3 + 1

(I2)

R3:=R5 + 1

(I3)

●

Wykonywanie rozkazu I3 nie może być

zakończone, zanim nie zostanie rozpoczęte

wykonywanie rozkazu I2 i nie zostaną

pobrane jego argumenty.

●

I3 aktualizuje rejestr R3, który jest źródłem

argumentu dla rozkazu I2.

●

Ograniczenie jest podobne do zależności

danych, lecz na odwrót: drugi rozkaz

niszczy wartość używaną przez pierwszy.

Wpływ zależności

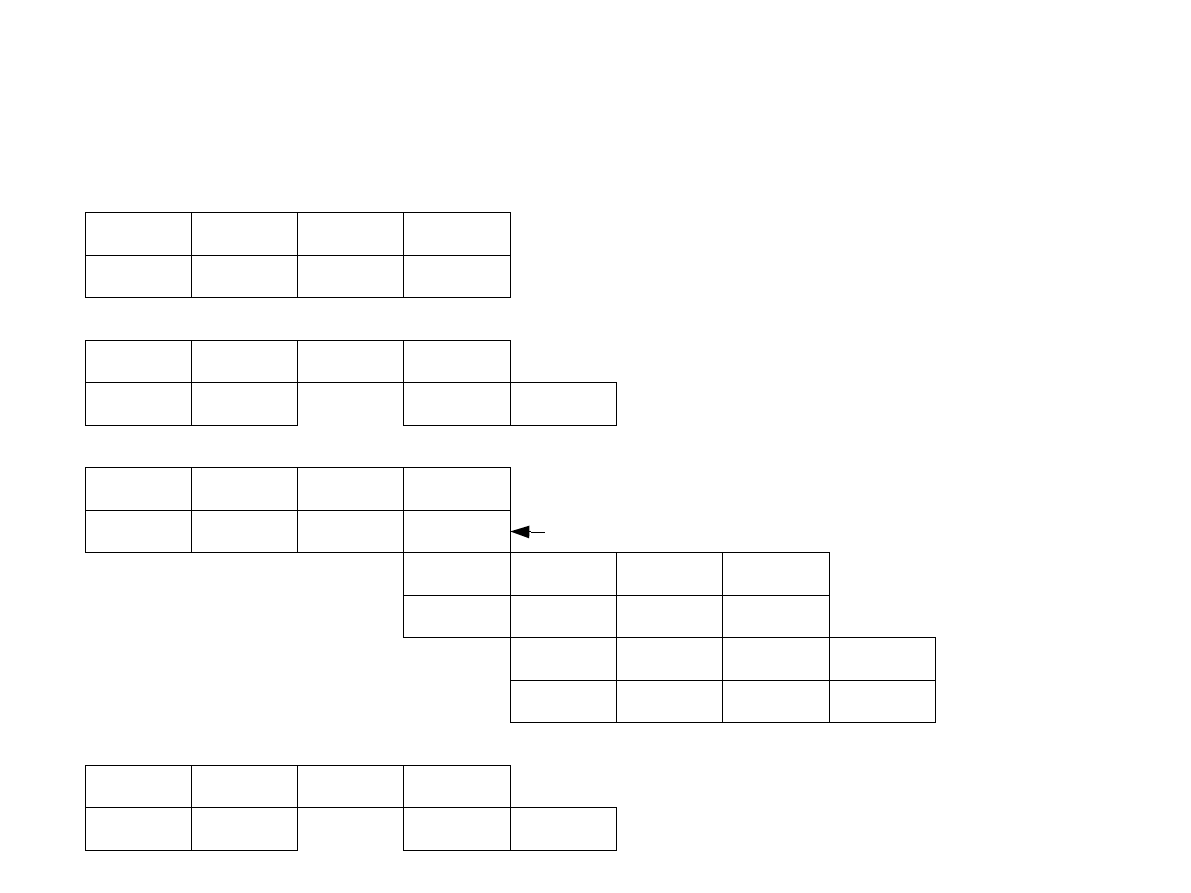

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r1

r2

Brak zależności

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r1

r2

Zależność danych

(r2 wykorzystuje dane

obliczone przez r1)

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r1

r2

Zależność proceduralna

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r3

r4

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r1

r2

Konflikt dotyczący

zasobów

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

Pobieranie

rozkazu

Dekodo-

wanie

Wykony-

wanie

Zapis

opóźniony

r5

r6

rozgałęzienie

Kolejność wykonania

rozkazów

●

Kolejne wydawanie połączone z

kończeniem w zmienionej kolejności.

–

Jeżeli rozkaz wykonuje się dłużej niż jeden cykl,

jego wyniki mogą być osiągalne później, niż

kolejnego rozkazu.

●

Zmieniona kolejność wydawania i

kończenia.

–

Wykorzystujemy bufor zdekodowanych

rozkazów zwany oknem rozkazu.

–

Jednostka wykonawcza pobiera dowolny rozkaz

z okna pod warunkiem spełnienia ograniczeń.

Przemianowanie rejestrów

Metoda eliminowania konfliktów

antyzależności i zależności wyjściowej

przez powielenie zasobów.

R3

b

:=R3

a

op R5

a

R4

b

:=R3

b

+ 1

R3

c

:=R5

a

+ 1

R7

b

:=R3

c

op R4

b

Użycie innego fizycznego rejestru R3c w rozkazie

I3 zapobiega antyzależnośći w drugim rozkazie

oraz zależności wyjściowej w pierwszym. Dzięki

temu I3 może być wykonany natychmiast.

Procesor PowerPC 620

●

Procesor PowerPC 620 zawiera sześć

niezależnych jednostek wykonawczych:

–

jednostkę rozkazów

–

trzy jednostki całkowitoliczbowe

–

jednostkę ładowania/zapisu

–

jednostkę zmiennopozycyjną

●

Procesor może jednocześnie

wykonywać do 4 rozkazów: 3

całkowitoliczbowe i 1

zmiennopozycyjny.

PowerPC 620 cd

●

Procesor zawiera układy przewidywania

rozgałęzień, bufory przemianowania

rejestrów oraz stacje rezerwowe

wewnątrz jednostek wykonawczych.

●

Procesor ten może wykonywać do 4

nierozstrzygniętych rozkazów

rozgałęzień.

●

Przewidywanie skoków oparte jest na

tablicy historii zawierającej 2048

zapisów. Skuteczność przewidywań: 90%.

Wyszukiwarka

Podobne podstrony:

ArchKomp CISC RISC Wyklad PKos Stud

Mat dla stud 2

Wyklad 1' stud

Metabolizm kkw tł stud

archkomp 08

strukturalnaMinuchina stud

Tętnice szyjne sem dla stud II

ZO NST 14 ĆW1CZ 1, 2 STUD F F3

kosztkapitału4 stud

6 Mielizna stud nowy

CEMENTY stud

Audyt personalny 1a stud

więcej podobnych podstron