Architektura Komputerów

Komputery o strukturach CISC i RISC

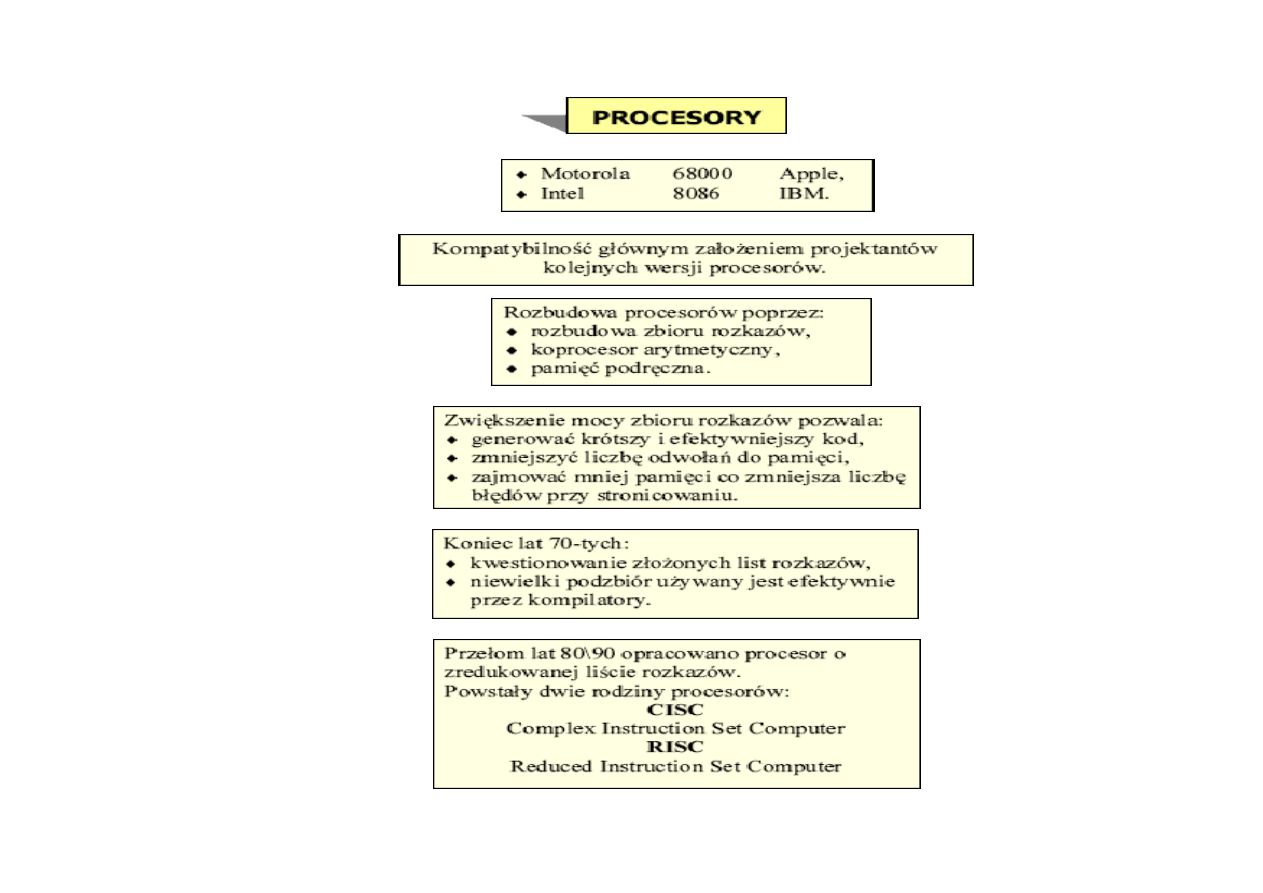

Wzrost złożoności list rozkazów – dominujący trend

w architekturze komputerów w latach 60. i 70. XX wieku

Przyczyny:

• pamięci komputerów były (zwłaszcza początkowo) małe, wolne i

drogie

• rozwój rodzin komputerów (IBM 360 i 370, PDP 8, 11, VAX, Intel

x86, MC 68000)

• popularne mikroprogramowane układy sterujące (łatwe w

rozbudowie)

• dążenie do uproszczenia kompilatorów

– teza: im więcej będzie rozkazów maszynowych

odpowiadających instrukcjom języków wyższego poziomu tym

lepiej

– model obliczeń pamięć – pamięć

Architekturę tych komputerów określono jako CISC

(Complex Instruction Set Computers)

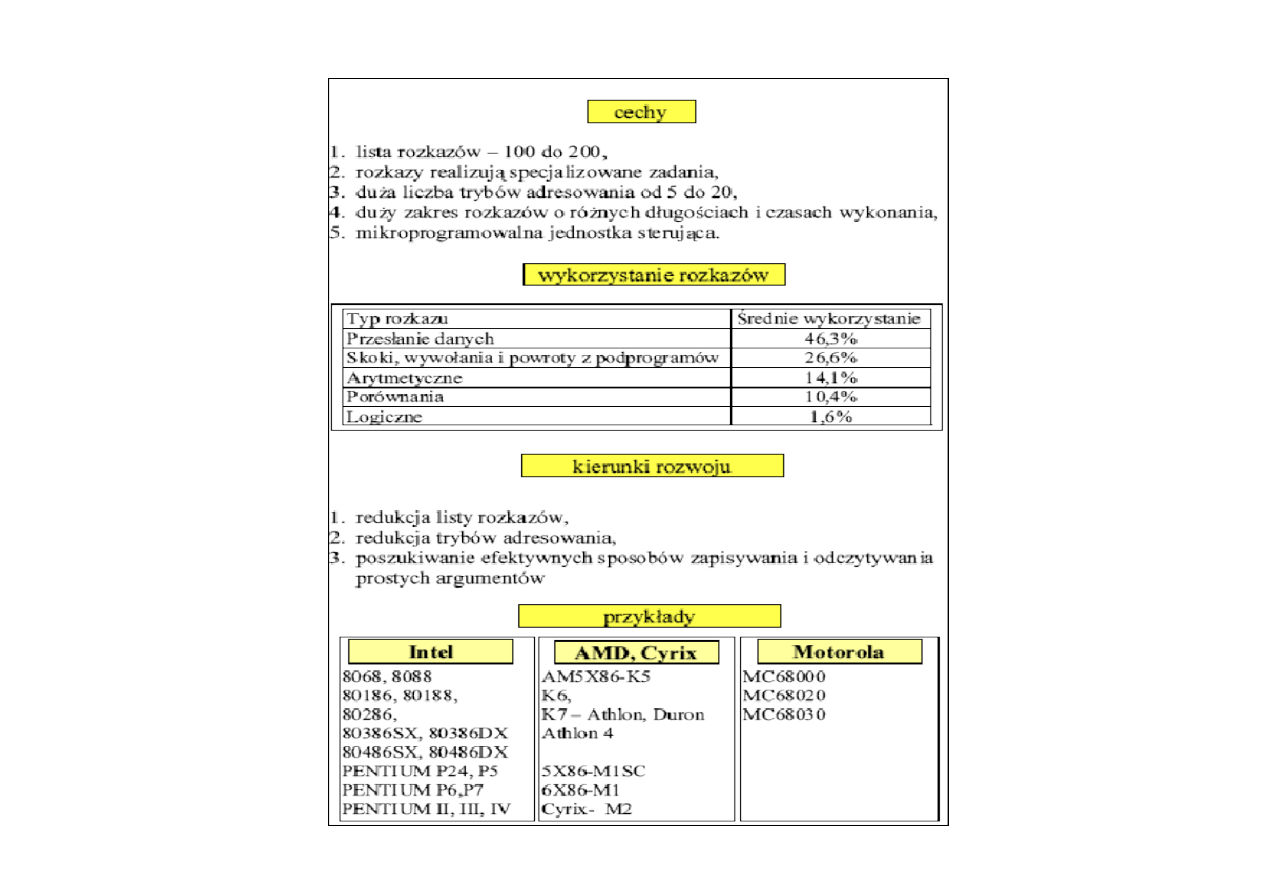

Cechy architektury CISC:

• duża liczba rozkazów (VAX – 303)

• duża liczba trybów adresowania (kilkanaście, VAX – 22)

• duży rozrzut cech rozkazów w zakresie:

– złożoności

– długości (1- kilkanaście bajtów, VAX – 57 B)

– czasów wykonania

• model obliczeń pamięć – pamięć

• mikroprogramowane układy sterujące

• przerost struktury sprzętowej

• mało efektywne wykorzystanie lista rozkazów

Przykłady mało efektywnego wykorzystania listy

rozkazów:

§

VAX

20% najbardziej złożonych rozkazów odpowiadało

za 60% kodu mikroprogramów, a te 20%

stanowiło 0,2% wywołań wszystkich rozkazów;

§

MC68020

71% rozkazów nie używanych w badanym zestawie

programów;

§

25% rozkazów zajmowało 95 % czasu wykonania

badanych programów

CISC

(Complex Instruction

Set Computers)

Według architektury CISC były tworzone pierwsze procesory,

które wyposażano w pełny zestaw instrukcji mający zapewnić

im wykonanie każdego polecenia użytkownika (programu). Z

czasem okazało się jednak, że w 80 procentach wypadków

było wykorzystywanych tylko 20 procent dostępnych instrukcji,

a pozostałe tylko sporadycznie. Zaowocowało to bardziej

zaawansowaną architekturą o nazwie RISC. Wszystkie

procesory montowane w „pecetach”, np. Pentium czy K6,

bazują na architekturze typu CISC. Ang. Complex Instruction

Set Computing - obliczenia z rozbudowanym zestawem

instrukcji.

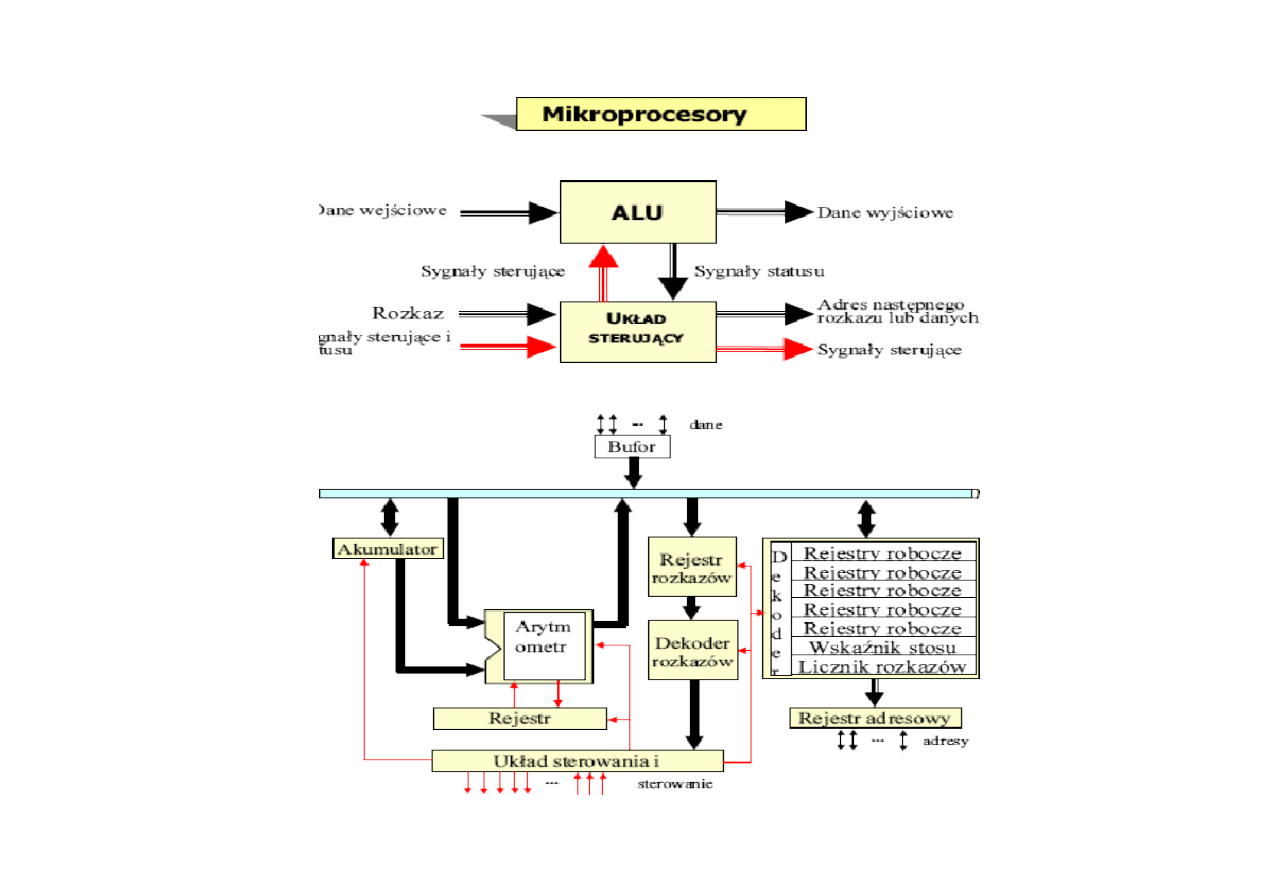

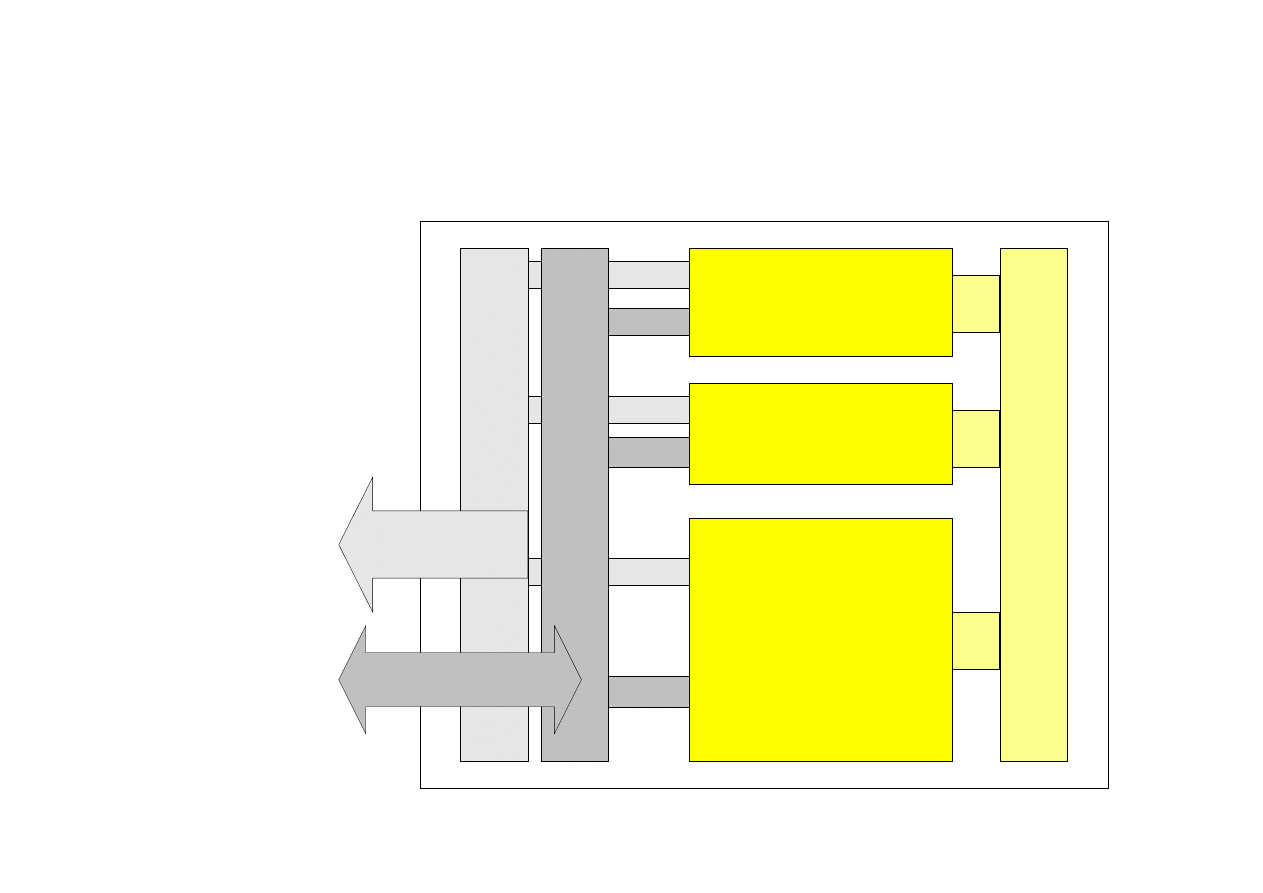

CISC

Budowa mikroprocesora typu

CISC Complete Instruction

Set Computer

ALU

Arithmetic Logic

Unit

KOPROCESOR

REJESTRY:

UNIWERSALNE

EAX,EBX,... ESI, EDI

SEGMENTOWE

CS, DS, ES, SS

SPECJALNE

EIP, SR

ADRES

(20/21,

32)

DANE

(32)

MAGISTRALA

ADRESOWA

MAGISTRALA

DANYCH

WEWN

Ę

TRZNA

MAGISTRALA DANYCH

CISC

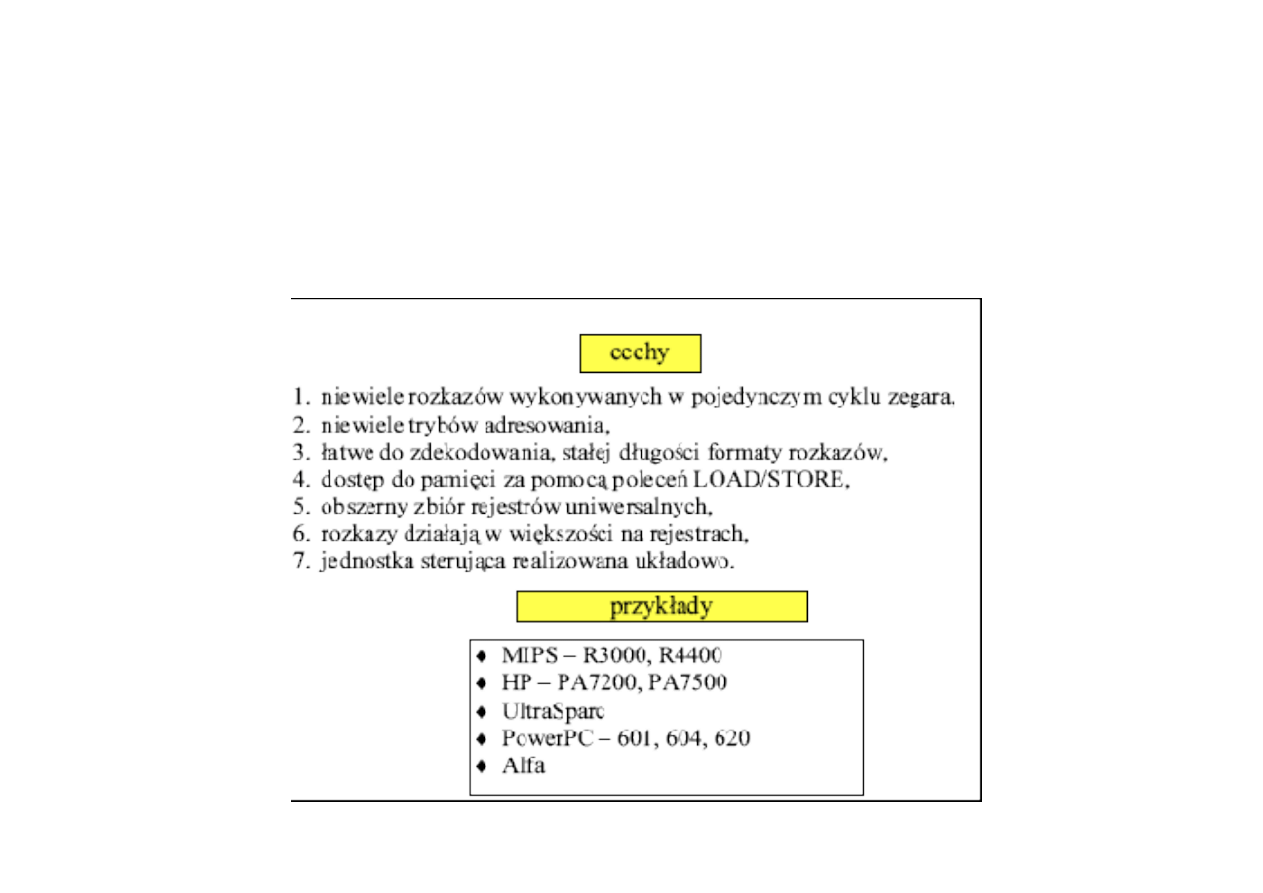

Rodzaj architektury procesora, według

której produkowane są najnowocześniejsze i

najbardziej wydajne procesory, w którym

obliczenia mają zredukowany zestaw instrukcji.

Częstotliwość taktowania podawana w MHz, lub

w GHz

RISC

RISC

((Reduced

Reduced Instruction

Instruction

Set

Set Computers

Computers))

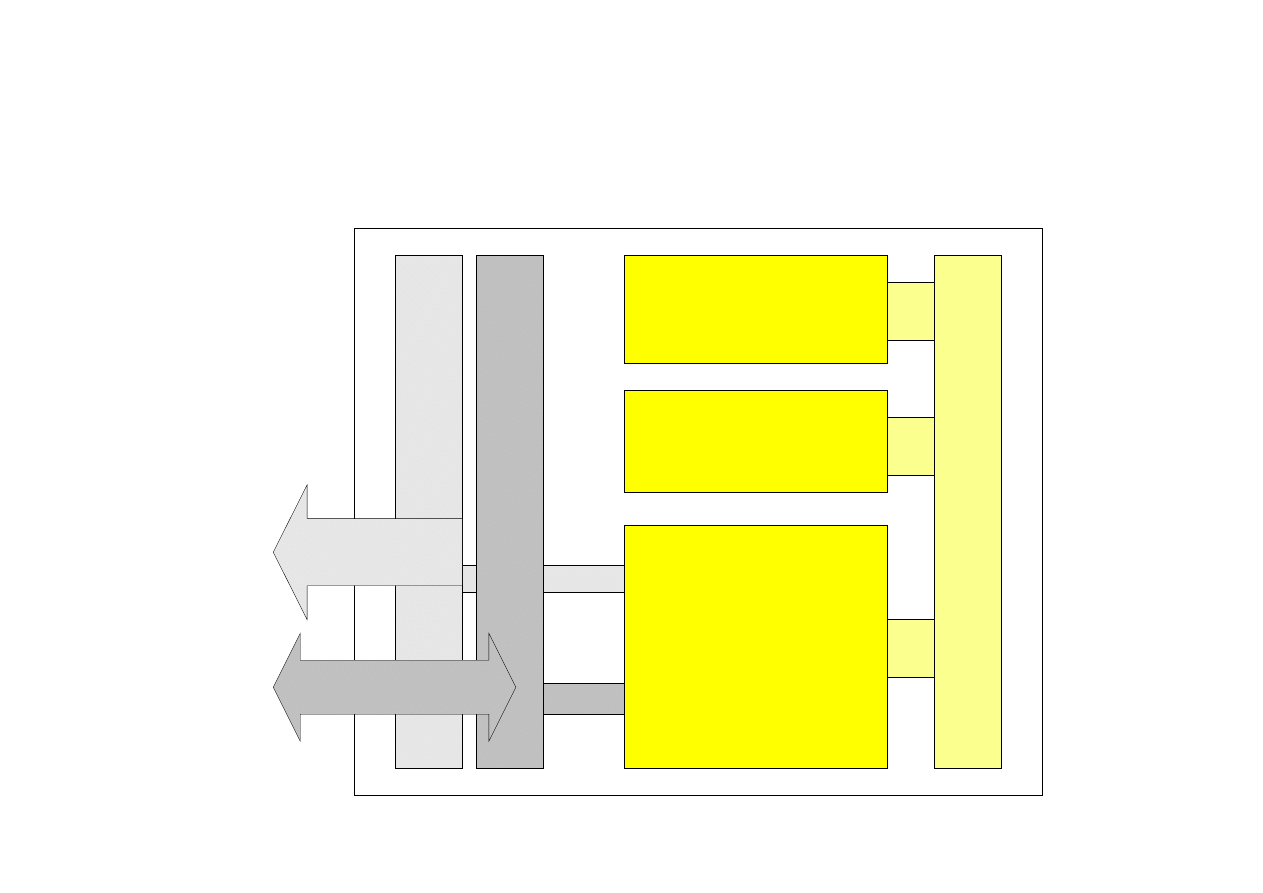

RISC – Reduced Instruction Set Computers

ALU

Arithmetic Logic

Unit

KOPROCESOR

REJESTRY:

UNIWERSALNE

EAX,EBX,... ESI, EDI

SEGMENTOWE

CS, DS, ES, SS

SPECJALNE

EIP, SR

ADRES

(20/21,

32)

DANE

(32)

MAGISTRALA

ADRESOWA

MAGISTRALA

DANYCH

WEWN

Ę

TRZNA

MAGISTRALA DANYCH

Budowa mikroprocesora typu

RISC

Reduced Instruction

Set Computer

Podstawowe różnice pomiędzy

CISC a RISC

®

CISC

®

rozbudowane instrukcje

®

operacje arytmetyczne

bezpośrednio na

lokalizacjach w pamięci

®

możliwość

zawansowanego

programowania w języku

maszynowym

®

różna długość instrukcji

®

często występujące

instrukcje - 8 bitów

®

rzadsze, rozbudowane

instrukcje o większej

długości

®

znaczne różnice czasu

wykonania poszczególnych

instrukcji

®

RISC

®

znacznie ograniczony

zestaw instrukcji

®

operacje ALU tylko na

rejestrach

®

prosty tryb adresowania -

uproszczone odwołania do

pamięci

®

wszystkie instrukcje

identycznej długości (32

bity)

®

znacznie prostsza

konstrukcja procesora

Początki RISC

(Reduced Instruction Set Computers)

1) IBM 801

(1975) - poszukiwanie optymalnej listy rozkazów

IBM RT-PC (1986)

IBM RS/6000

2) D. Patterson (Berkeley Univ.) RISC I (1980)

RISC II (1981)

SPARC (1987) Sun

3) J. Hennessy (Stanford Univ.) MIPS

(1981)

MIPS R2000

(1986) SGI

4) Motorola MC 88000 (1988)

5) HP Precision Architecture (PA-RISC)

(1989)

Motywacja rozwoju pierwszych procesorów

RISC:

wykonanie mikroprocesora o funkcjach pełnego

ówczesnego procesora

Procesor RISC I

(1980)

D. Patterson (Berkeley University)

Założenia projektowe:

• Wykonanie jednego rozkazu w jednym cyklu

maszynowym

• Stały rozmiar rozkazów – uproszczenie metod

adresacji

• Model obliczeń rejestr – rejestr: komunikacja z

pamięcią operacyjną tylko za pomocą rozkazów

LOAD i STORE.

• Wsparcie poprzez architekturę języków wysokiego

poziomu.

Wyszukiwarka

Podobne podstrony:

JBZ Wyklad2 dla stud

Wykład dla stud zaocznych 20 12 2008

JBZ Wyklad 3 dla stud

wykład 3 skrót stud Gierusz 2

Wykład dla stud zaocznych 20 12 2008

wykład 2 skrót stud Gierusz 2

Wyklad 1' stud

ETH wykład wyniki0 do stud

Wykład IX dla stud, Wykład IX

ArchKomp Superskalarne Stud WSBCieszyn

Relacje i funkcje ćw 2(2), stud, I semsetr, ALGEBRA, Ćwicenia i wyklady

Wyklad 1 CIAGI 2012 13 wer stud

MFW2011 stud, Podręczniki i materiały dydaktyczne, wykłądy

Rach bankowa wyklad rozliczenia pieniezne stud

więcej podobnych podstron