2W0

Procesory sygnałowe i układy peryferyjne

systemów CPS

Powstanie i rozwój technologii procesorów DSP

Współczesne dziedziny zastosowań

Obecny rynek DSP

2W1

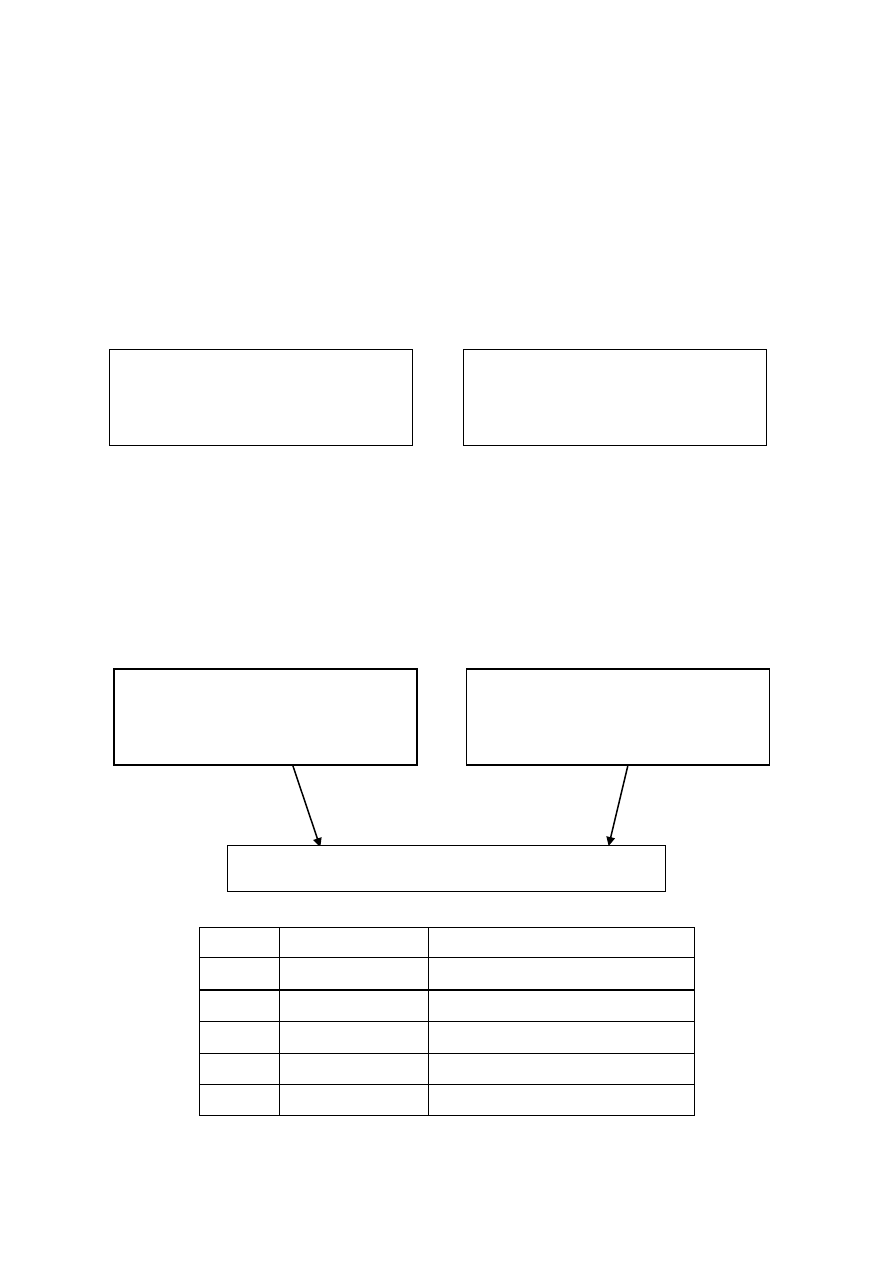

POCZĄTKI DSP

Przekształcenie Fouriera

Przekształcenie Laplace’a

Dyskretne Przekształcenie Fouriera

Przekształcenie Z

(Discrete Fourier Transform

– DFT)

Algorytm Cooley’a i Tukey’a

Szybkie Przekształcenie Fouriera

(Fast Fourier Transform

– FFT)

1971

Lincoln FDP

Lincoln Laboratory

1973

Lincoln LSP/2

Lincoln Laboratory

1980

S2811

American Microsystem

1980

2920

Intel

1980

PD7720

Nippon Electric Company (NEC)

1982

TMS32010

Texas Instruments

Przekształcenie sygnałów

cyfrowych z dziedziny czasu

na dziedzinę częstotliwości

Aparat matematyczny opisu

sygnałów i układów cyfrowych

Rozwój algorytmów

cyfrowego przetwarzania

sygnałów

Rozwój technologii szybkich

układów scalonych wielkiej

skali integracji

Pierwsze układy procesorów sygnałowych

2W2

Obroty rynku DSP w dolarach US

1995 rok

– ok. 2 miliardy USD

1997 rok

– ok. 4 miliardy USD

1999 rok

– ok. 7 miliardów USD

2001 rok

– ok. 10 miliardów USD

…

2010 rok

– ok. 18 miliardów USD

Tradycyjny podział procesorów DSP

Zmiennoprzecinkowe

większa precyzja

większy zakres dynamiki

krótszy czas wdrożenia

Stałoprzecinkowe

niższy koszt

mniejszy pobór mocy

Tendencje rozwojowe w dziedzinie

Procesorów

migracja w kierunku DSP

migracja do arytmetyki zmiennoprzecinkowej

wzrost możliwości obliczeniowych

redukcja poboru mocy

2W3

Typowe przykłady zastosowań

urządzenia audio, hi-fi

urządzenia video

telefonia bezprzewodowa

modemy

wideofony

zabawki

przetwarzanie obrazów

grafika 3D

Kodowanie przebi

egów

Kompresja objętości

danych

mowy

obrazów

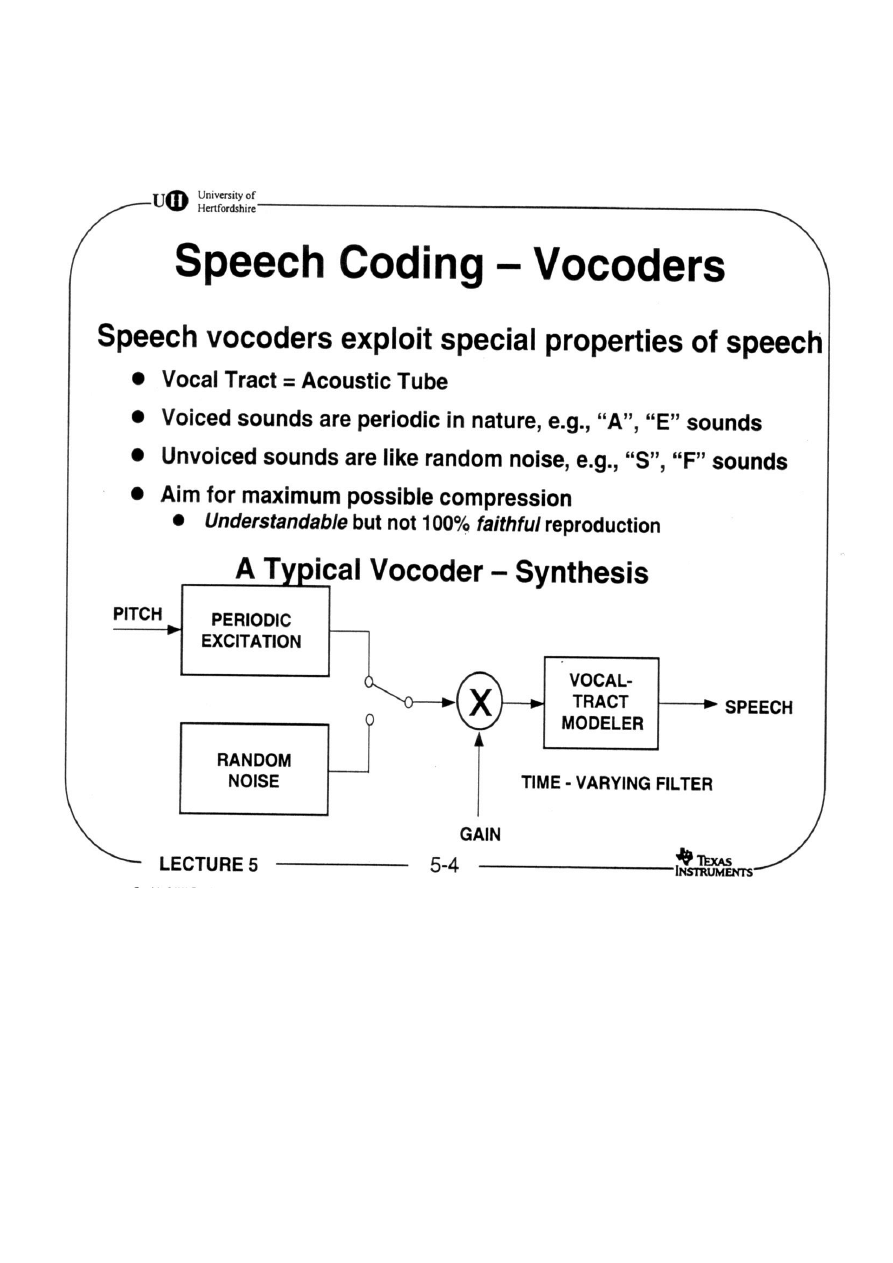

Kodowanie

sygnałów mowy

wykorzystanie charakterystycznych cech mowy

-

okresowość

-

różnice pomiędzy głoskami dźwięcznymi

i bezdźwięcznymi

Kodowanie

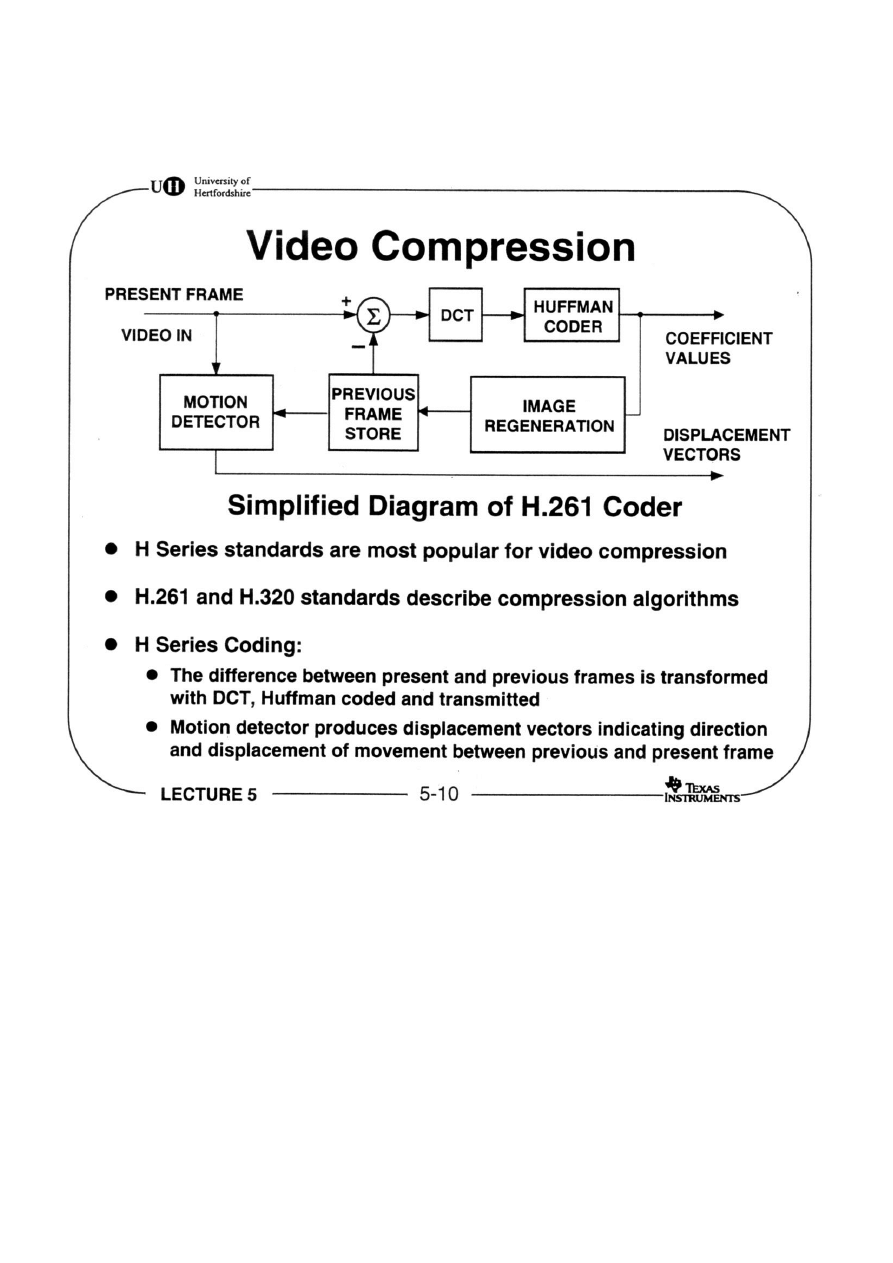

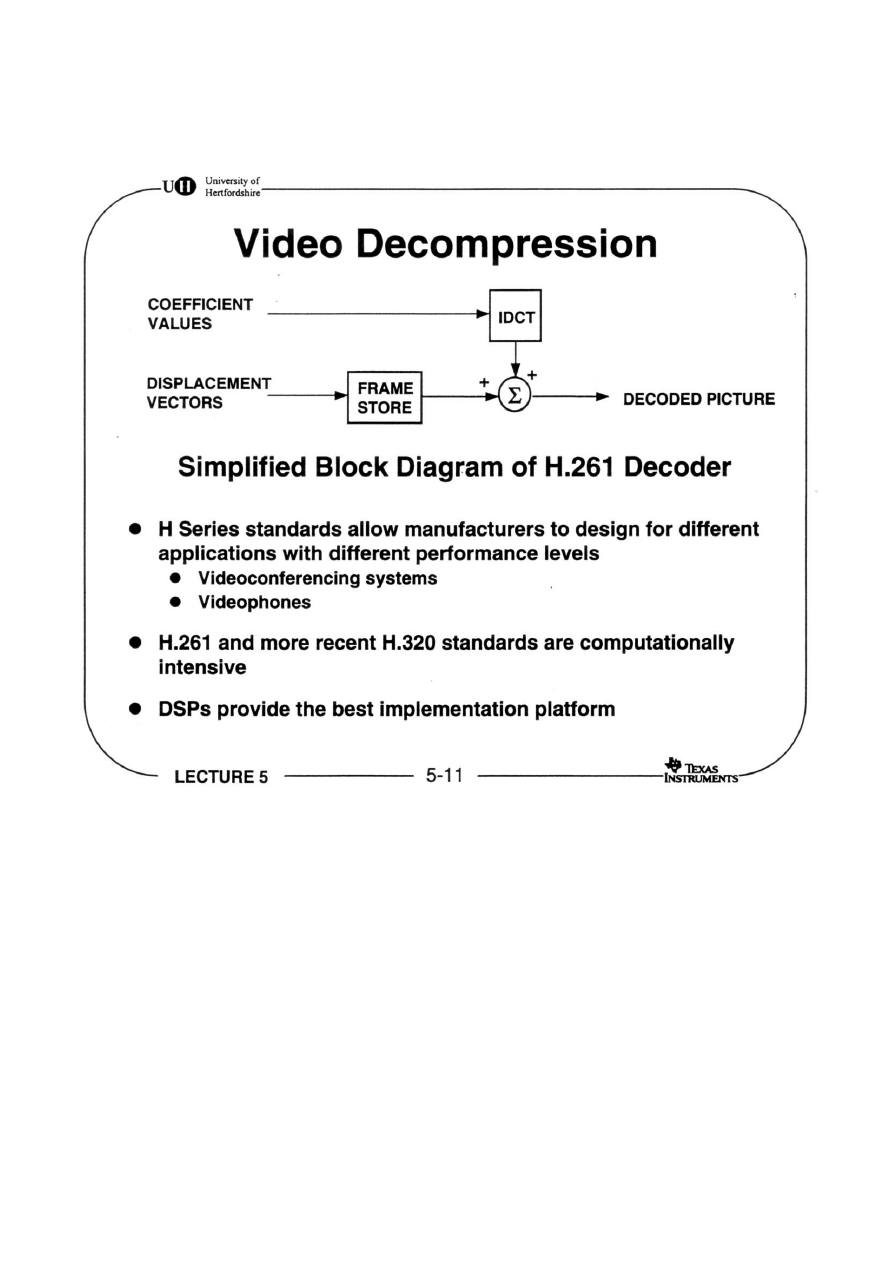

obrazów

wykorzystanie

transformat sygnału

informacja o różnicy pomiędzy ramkami obrazu

kombinacje kodowania mowy i obrazu w aplikacjach

video

2W4

Kodowanie mowy (

Vo

ice

coder

–

vocoder

)

2W5

Kodowanie obrazów

Najwięcej informacji zawarte jest w składowych

nisko-

częstotliwościowych sygnału;

Koder przekształcający chroni informację zawartą w zakresie

dolnych częstotliwości;

Pomijany są małe współczynniki transformaty, bez znaczącej

utraty jakości sygnału;

Powszechnie stosuje się dyskretne przekształcenie kosinusowe

(DCT

– Discrete Cosine Transform);

Kodowanie daje redukcję objętości danych i zmniejsza

wymagania na przepustowość kanału transmisyjnego;

W dziedzinie kodowania obrazów stosuje się 3 podstawowe

standardy:

H

-

kompresja sygnałów wideo o ograniczonej jakości;

JPEG - kompresja

obrazów nieruchomych;

MPEG -

kompresja obrazów ruchomych pełnej jakości.

2W6

2W7

2W8

Ocena szybkości DSP

Najpopularniejsze parametry oceny szybkości procesorów:

MIPS - Million Instructions per Second

ilość milionów rozkazów na sekundę wykonywanych

przez procesor, ilość wewnętrznych cykli rozkazowych.

Pytanie: Co realizują poszczególne rozkazy?

MOPS - Million Operations per Second

ilość milionów operacji na sekundę Całkowita liczb

operacji wliczając dostęp do pamięci, operacje przesyłu

danych, operacje wejścia/wyjścia.

MFLOPS - Million Floating Point Operations per Second

ilość milionów operacji zmiennoprzecinkowych

na sekundę.

MMAC - Million Multiply and Accumulate

ilość milionów operacji MAC na sekundę.

Benchmarks -

czasy realizacji podstawowych algorytmów DSP.

2W9

Światowi potentaci rynku DSP

1. Texas Instruments

2. Freescale Semiconductor (Motorola)

3. Agere/LSI

4. Analog Devices

Procesory firmy Analog Devices

ADSP-21xx

16-

bitowy format stałoprzecinkowy

ADSP-21xxx

32-bitowy format zmiennoprzecinkowy

(SHARC)

32-

bitowy format stałoprzecinkowy

TigerSHARC

32-, 40-bitowy format zmiennoprzecinkowy

8-, 16-, 32-

bitowy format stałoprzecinkowy

Blackfin

16-bito

wy format stałoprzecinkowy

DSP + RISC

Procesory firmy Agere

DSP-16xxx

16-

bitowy format stałoprzecinkowy

DSP-32xx

32-bitowy format zmiennoprzecinkowy

Procesory firmy Freescale:

DSP568xx/568xxE

16-

bitowy format stałoprzecinkowy

DSP563xx i 566xx

24-b

itowy format stałoprzecinkowy

DSP96xxx

32-bitowy format zmiennoprzecinkowy

MSC81xx

16-

bitowy format stałoprzecinkowy (ALU)

32-bitowa jednostka komunikacyjna RISC

2W10

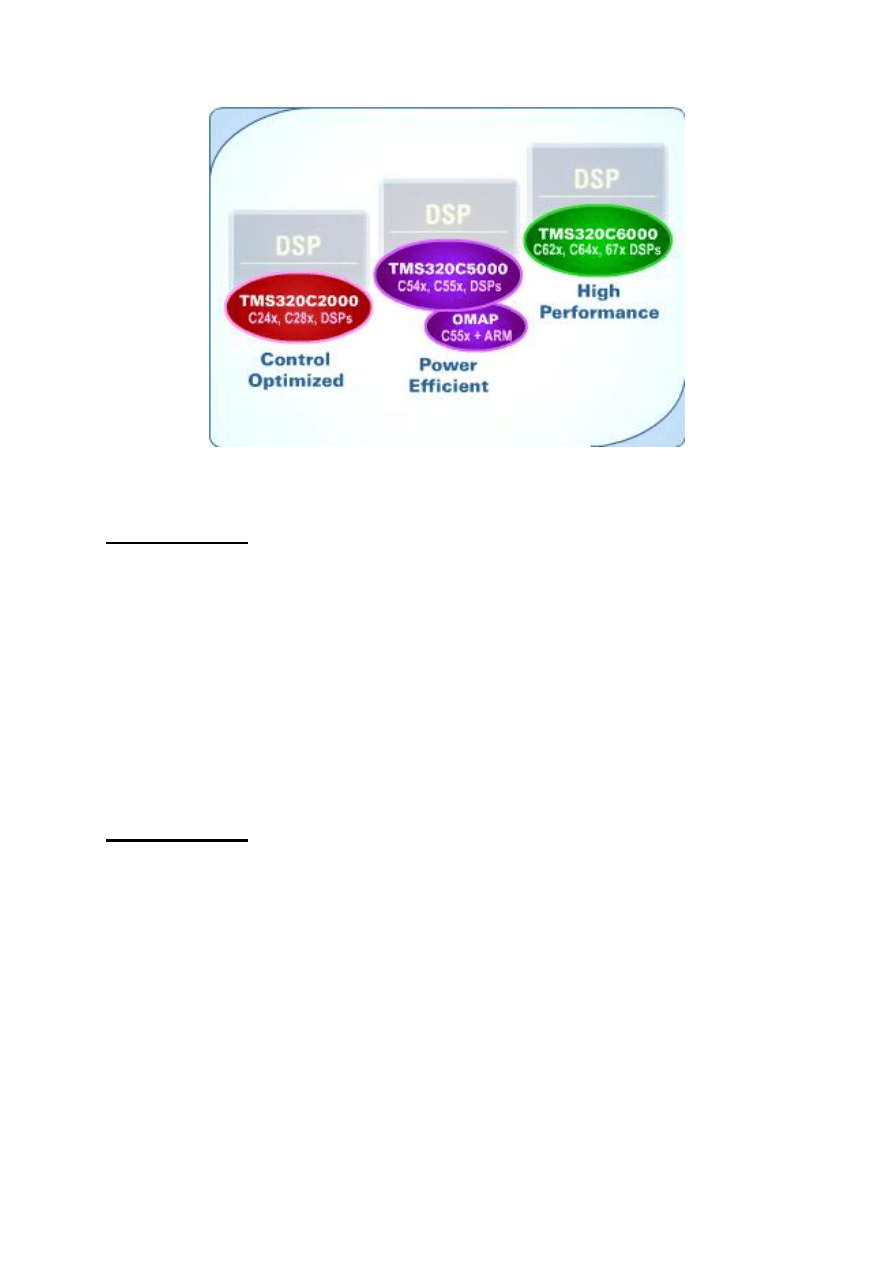

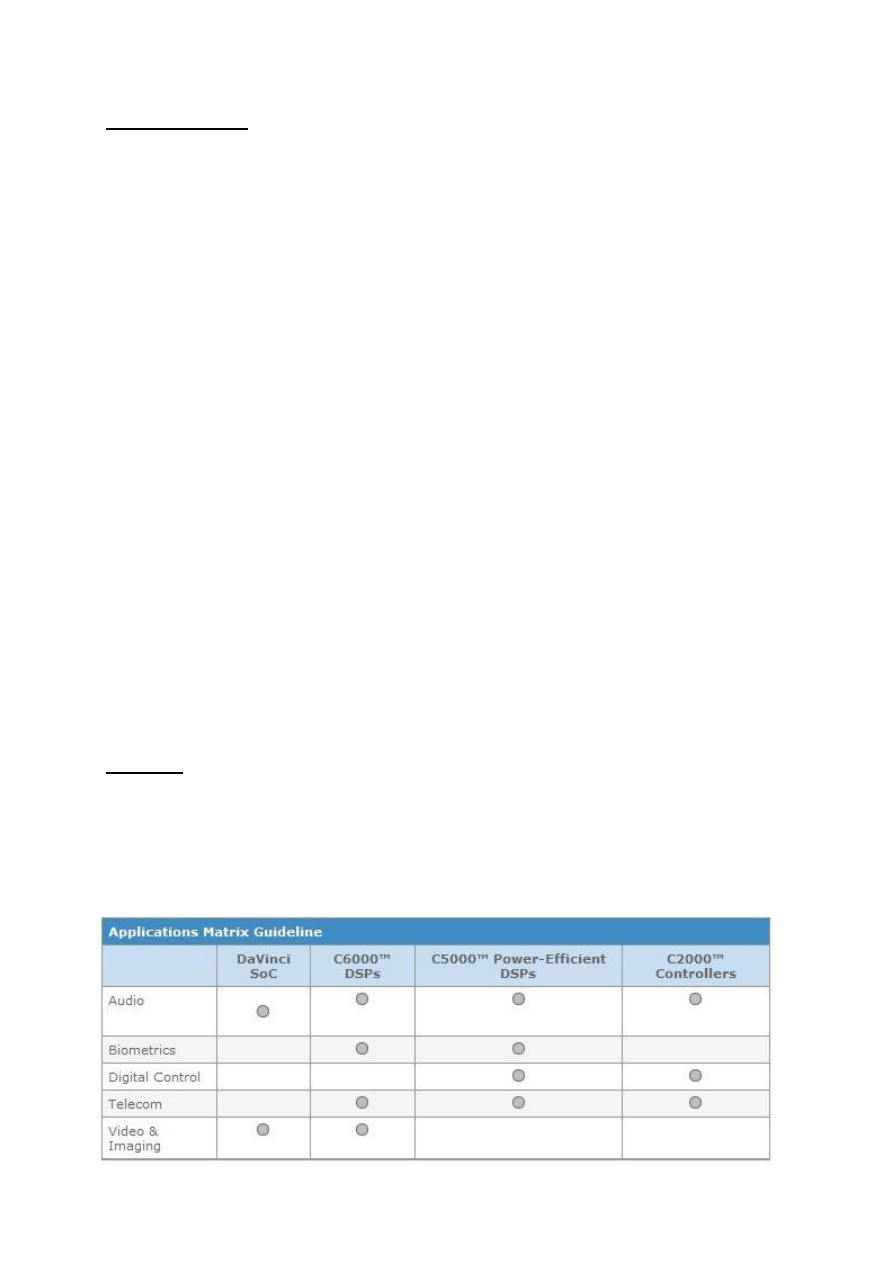

Platformy sprzętowo-programowe firmy Texas Instruments

TMS320C2000

– Digital Signal Controllers

Połączenie MCU o dużej mocy i sprawności obliczeniowej

z

możliwościami układów cyfrowego sterowania

W

budowane aplikacje przemysłowe, np.:

automatyka przemysłowa

sterowanie silników cyfrowych (krokowych)

cyfrowe źródła zasilania

czujniki inteligentne

TMS320C5000

– Power Efficient DSPs

Przemysłowy standard niskiego poboru mocy

Zaawansowane,

automatyczne zarządzanie mocą

Urządzenia osobiste i przenośne, np.:

cyfrowe odtwarzacze muzyczne

telefonia VoIP/DECT

odbiorniki GPS

p

rzenośne urządzenia medyczne

czytniki linii papilarnych

2W11

TMS320C6000

– High Performance DSPs

TMS320C67x / C672x - Floating Point DSPs

O

ptymalizacja wydajności i sprawności działania

Przemysłowy standard najbardziej zaawansowanego Optimizera

dla kompilatora C i asemblera

Wysok

iej jakości komercyjne i profesjonale aplikacje audio

Zobrazowanie cyfrowe

Grafika 3D

TMS320C64xx, TMS320C62x - Fixed Point DSPs

Połączenie wysokiej jakości i efektywności cenowej

Przemysłowy standard szybkości procesorów stałoprzecinkowych

Infrastruktury bezprzewodowe i telekomunikacyjne

Przetwarzanie

obrazów i systemy zobrazowania

Transkodowanie audio i video

Servery video konferencji

HDTV, HD Radio

Zobrazowanie medyczne

DaVinci

– Digital Media Processors

Technologia DaVinci - zintegrowany pakiet proce

sorów,

oprogramowania i narzędzi dla producentów sprzętu video

Optymalizowane dla aplikacji cyfrowego video

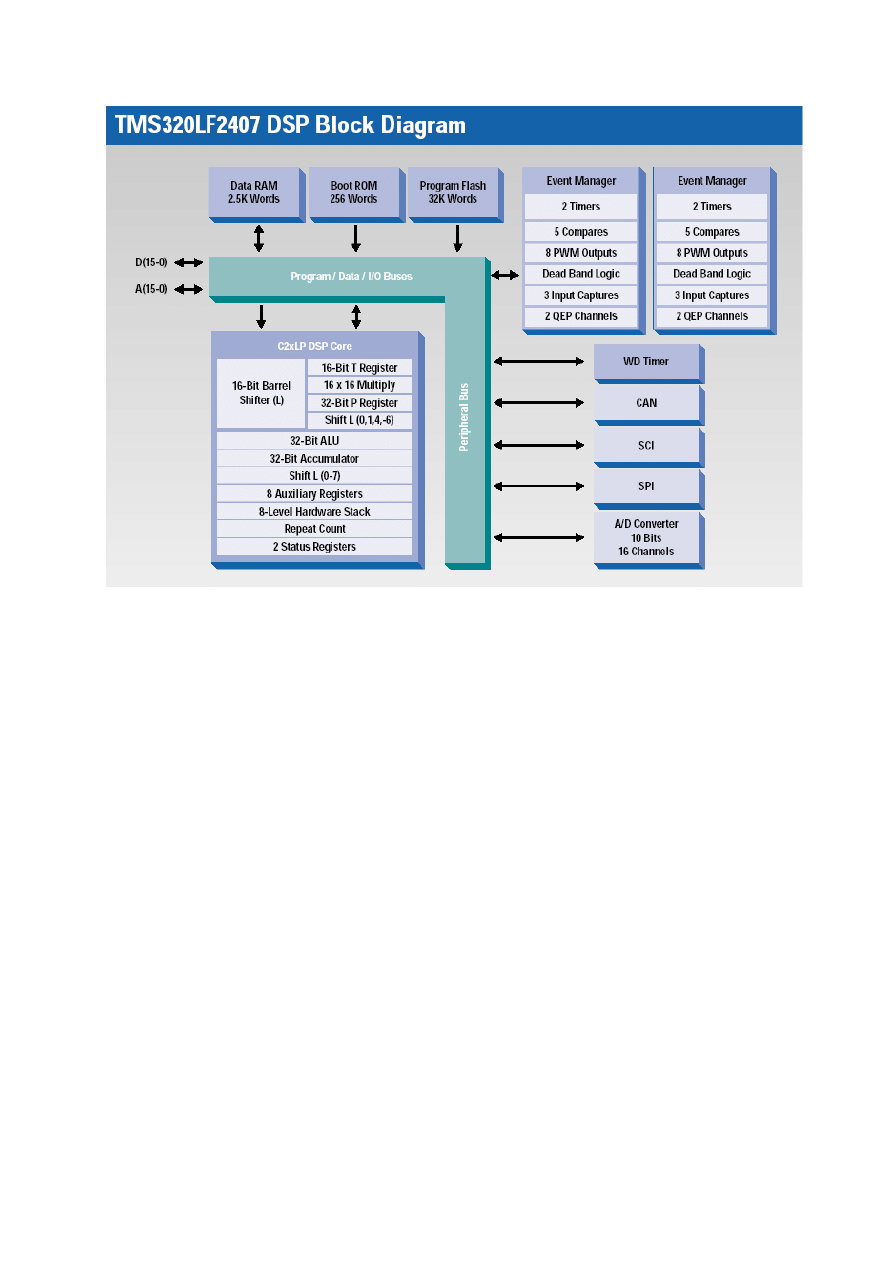

2W12

zmodyfikowana architektura harwardzka

jednostka przetwarzająca (core):

- 16-

bitowy układ mnożący

- 16-bitowy rejestr przesuwny

- 32-bitowa ALU

- 32-bitowy akumulator

-

zbiór rejestrów pomocniczych

obszar pamięci wewnętrznej:

- 32K-

słów pamięci programu, typu FLASH

-

256 słów pamięci ROM z bootloaderem

-

2,5K słów pamięci danych RAM

interfejsy:

- synchroniczny interfejs szeregowy (SPI)

- asynchroniczny interfejs szeregowy (SCI)

- magistrala CAN

10-bitowy, 16-

kanałowy przetwornik a/c

dwie jednostki zarządzania zdarzeniami

do 4 timerów 16-bitowych, 1 Watch-Dog timer, do 16 kanałów PWM

emulator standardu JTAG

do 40 MIPS

2W13

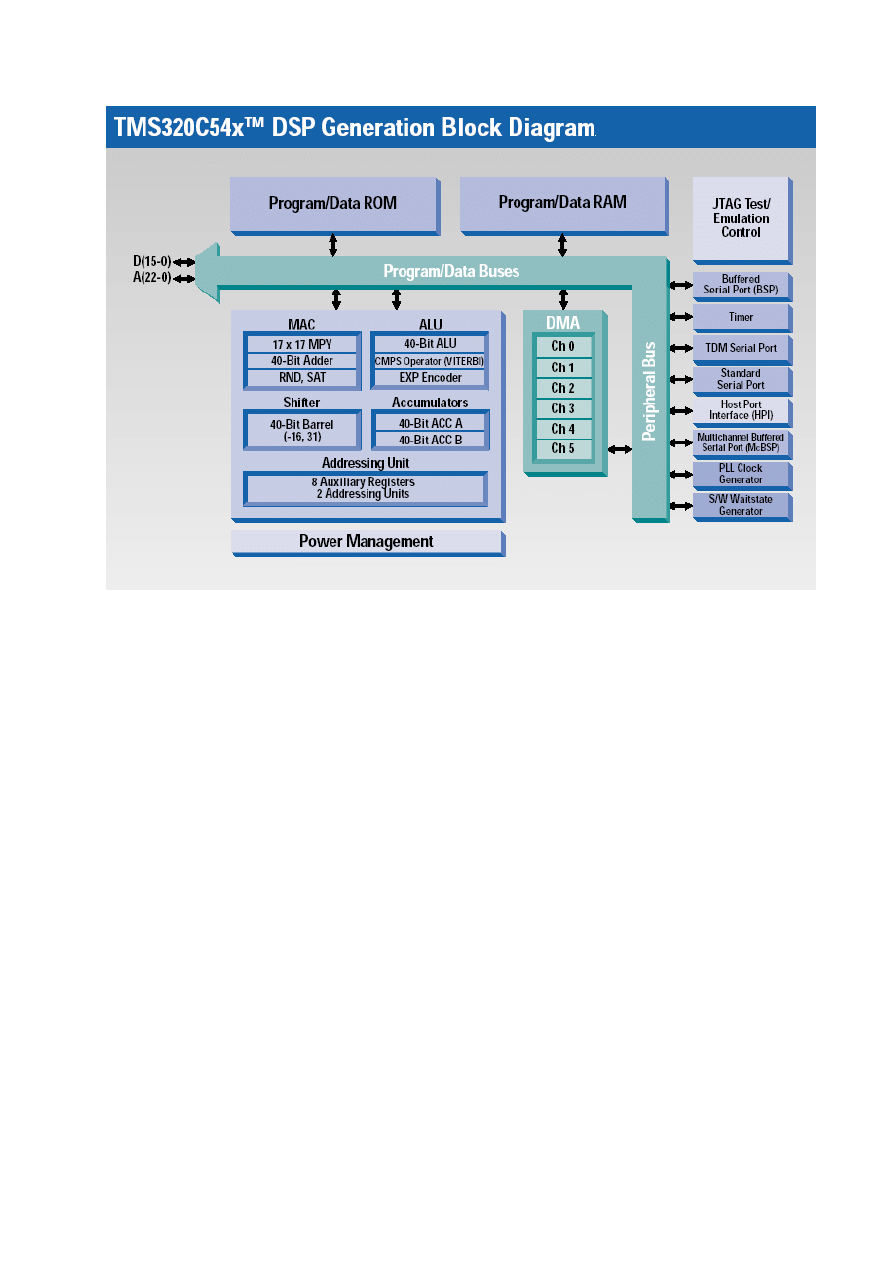

zmodyfikowana architektura harwardzka

od 1

do 4 jednostek przetwarzających

każda jednostka przetwarzająca (core) posiada:

- 17-

bitowy układ mnożący

- 40-

bitowy układ sumujący

- 40-

bitową ALU

- dwa 40-bitowe akumulatory

-

8 rejestrów pomocniczych;

- dwa generatory adresu

- 40-bitowy rejestr przesuwny

4 magistrale wewnętrzne - 1 magistrala programu, 3 magistrale danych

rozbudowane interfejsy:

- standardowy port szeregowy (SSP)

- buforowany port szeregowy (Buffered Serial Port - BSP)

-

wielokanałowy, buforowany port szeregowy (Multichannel BSP)

-

multipleksowany port szeregowy z podziałem czasowym

(TDM - Time-Division Multiplexed)

-

port równoległy komputera nadrzędnego (HPI - Host Port Interface)

wspomaganie operacji na liczbach zmiennoprzecinkowych

zaawansowane funkcje z

arządzania energią

do 160 MIPS (1 core)

2W14

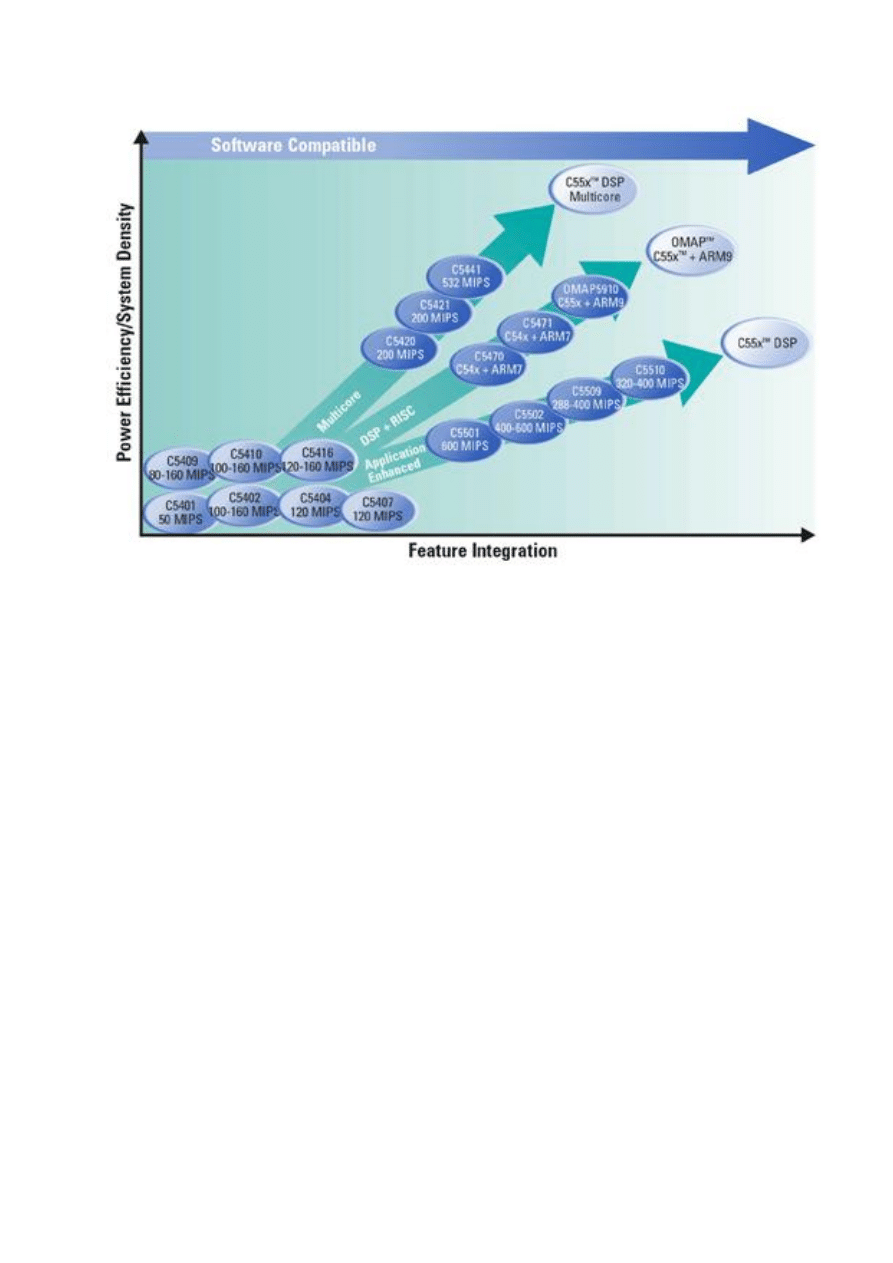

Droga rozwoju platformy C5000

2W15

Zastosowane modyfikacje w generacji C55x:

technologia

zmiennej długość słowa instrukcji

(Variable Instruction Length Architecture)

umożliwia operowanie na instrukcjach 8-, 16-, 32-, 48-bitowych

podwójny układ mnożący

podwójna jednostka arytmetyczno-logiczna ALU

4 akumulatory

możliwość wykonania 2 instrukcji w jednym cyklu maszynowym

3 magistrale odczytu danych

2 magistrale zapisu danych

zaawansowane technologie redukcji poboru mocy

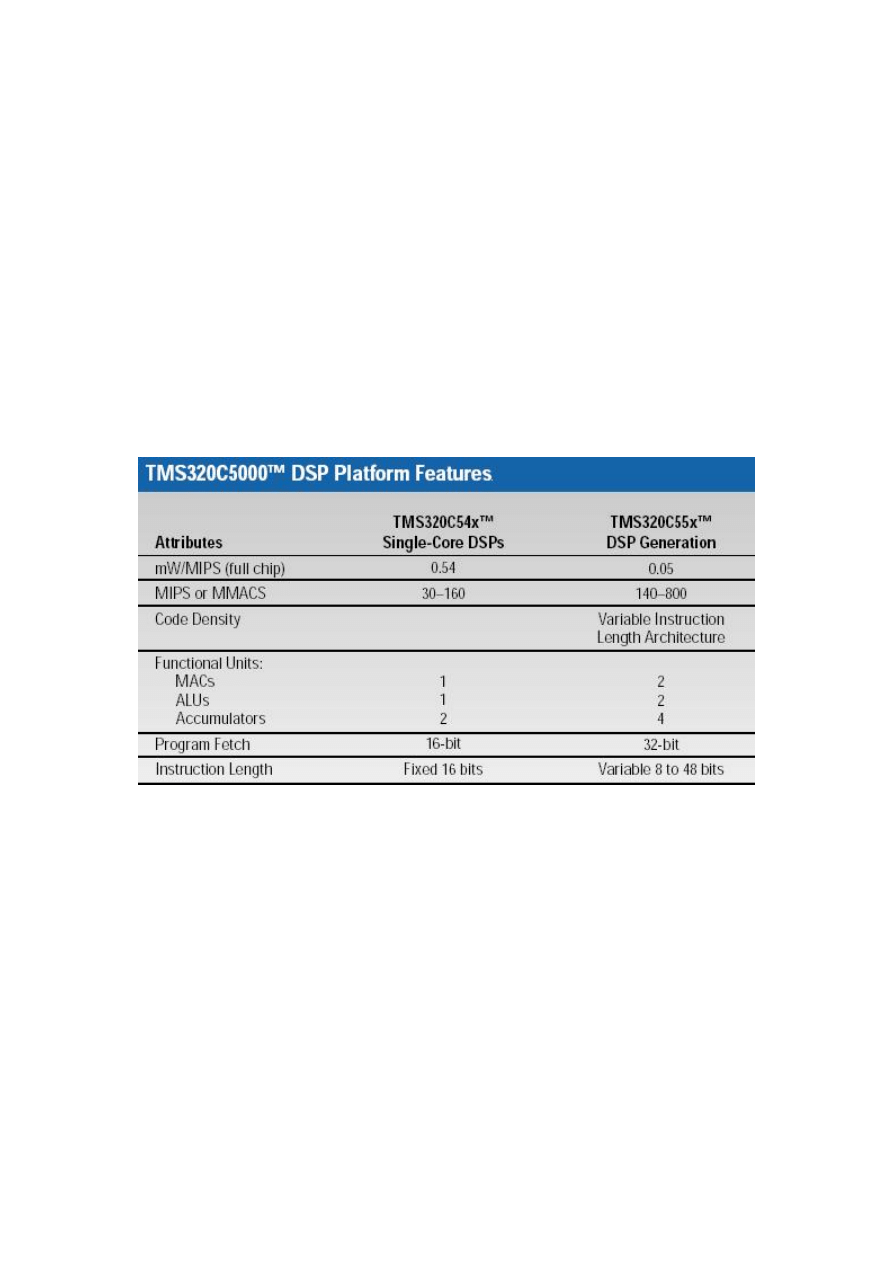

Zestawienie porównawcze generacji C54x i C55x

2W16

Platforma C6000 opiera się na 3 typach układów:

TMS320C62x stałoprzecinkowe procesory o architekturze 16/32-bitowej

(32-

bitowe słowo instrukcji, 16-bitowe mnożenie);

TMS320C64x s

tałoprzecinkowe procesory stanowiące rozwinięcie

układu C62x;

TMS320C67x 32-bitowe procesory zmiennoprzecinkowe.

Charakterystyka procesorów platformy C6000:

zaawansowana technologia

bardzo długiego słowa instrukcji

advanced Very Large Instruction Word - VelociTI.1, VelociTI.2;

architektura typu ładuj/zapisz (load/store) - wszystkie operacje

wykonywane na rejestrach;

zaawansowane kontrolery zarządzania danymi i wykonaniem programu;

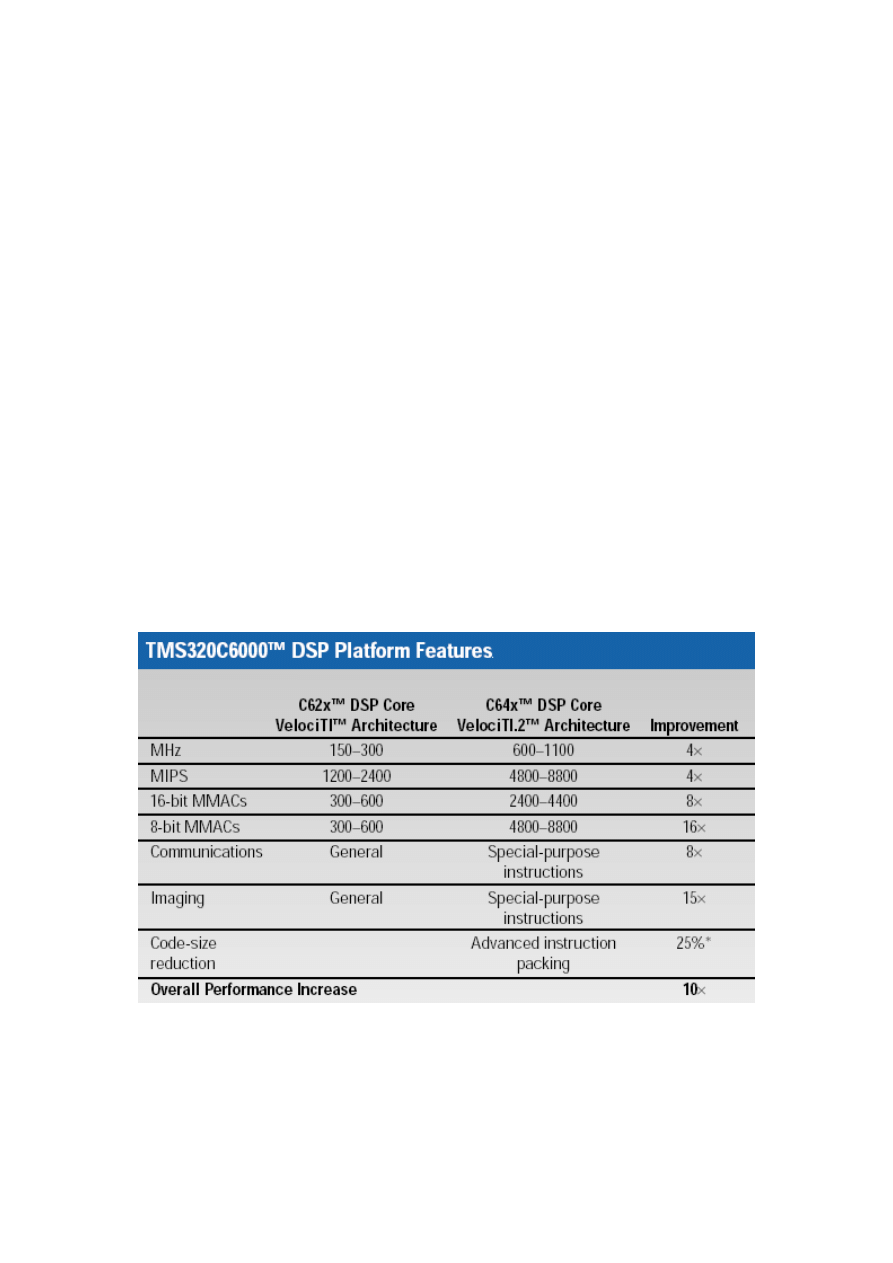

Zesta

wienie porównawcze generacji C62x i C64x

Wyszukiwarka

Podobne podstrony:

ENERGOELEKTRONICZNY ZESTAW DYDAKTYCZNY Z PROCESOREM DSP

W4 Proces wytwórczy oprogramowania

WEWNĘTRZNE PROCESY RZEŹBIĄCE ZIEMIE

Proces tworzenia oprogramowania

Proces pielęgnowania Dokumentacja procesu

19 Mikroinżynieria przestrzenna procesy technologiczne,

4 socjalizacja jako podstawowy proces spoeczny

modelowanie procesˇw transportowych

Proces wdrazania i monitoringu strategii rozwoju

Wykorzystanie modelu procesow w projektowaniu systemow informatycznych

wyklad 12nowy procesy elektrodowe i korozja

33 Przebieg i regulacja procesu translacji

więcej podobnych podstron