AKADEMIA GÓRNICZO–HUTNICZA

WYDZIAŁ ELKTROTECHNIKI,

AUTOMATYKI, INFORMATYKI I ELEKTRONIKI

PROJEKT nr 6

Podstawy Sterowania Logicznego

PROGRAMOWALNY DZIELNIK

CZĘSTOTLIWOŚCI

PROWADZĄCY: WYKONANIE:

dr inż. Andrzej Ożadowicz Monika Turowska

Kamil Chemicz

Marek Brdej

Kraków, styczeń 2012

1. WPROWADZENIE

1.1 Cel projektu:

Celem projektu jest opracowanie układu dzielnika częstotliwości o zadanym współczynniku

podziału.

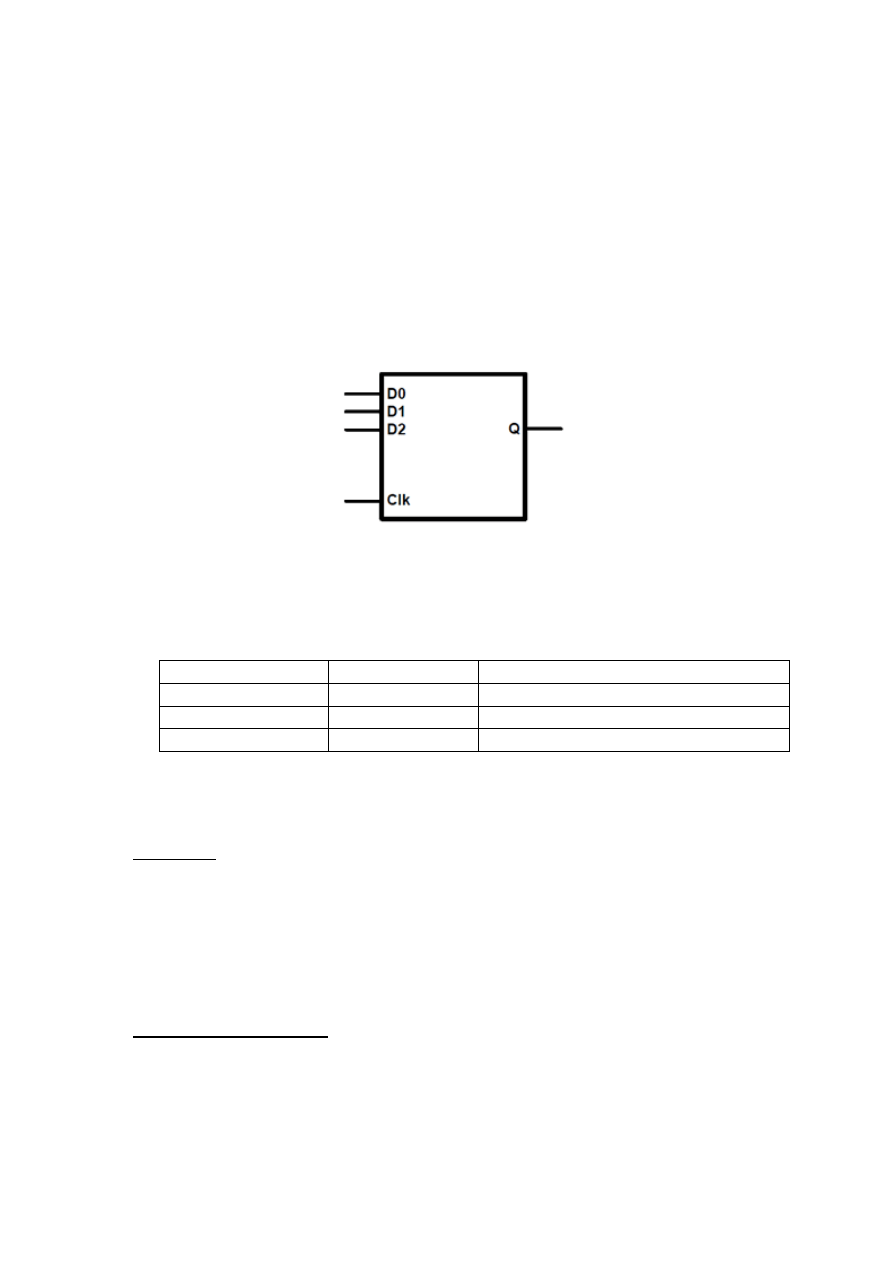

1.2 Schemat blokowy, wejścia i wyjścia układu:

Schemat blokowy dzielnika częstotliwości jest pokazany na rysunku 1.

Rys. 1. Schemat blokowy dzielnika

1.3 Wejścia i wyjścia układu:

W tabeli 1 są zestawione wejścia i wyjścia bloku.

Sygnały (y)

We/Wy

Opis

D0-D2

We

Współczynnik podziału (liczba 3-bitowa)

Clk

We

Zegar

Q

Wy

Wyjście sygnału

Tabela 1. Sygnały wejściowe i wyjściowe

1.4. Przerzutniki:

Przerzutnik - jest to podstawowy element pamiętający każdego układu cyfrowego,

przeznaczonego do przechowywania i ewentualnego przetwarzania informacji. Przerzutnik

współtworzy najniższe piętro struktury układu i zdolny jest do zapamiętania jednego bitu

informacji.

Przerzutniki dzielimy na:

synchroniczne

asynchroniczne

Przerzutniki synchroniczne - takie, których praca jest sterowana jednym, wspólnym

przebiegiem zegarowym. Określa on chwile, w których stany wejść oddziałują na układ.

Chwile te są wyznaczane przez zbocze dodatnie bądź ujemne przebiegu taktującego, dlatego

mówimy o synchronizacji układu zboczem narastającym lub opadającym. W chwilach tych

stan innych wejść nie powinien się zmieniać.

Przerzutniki asynchroniczne - nie pracują z podłączonym wspólnym przebiegiem

zegarowym, każdy może być taktowany innym sygnałem.

Są one mniej odporne na zakłócenia niż układy synchroniczne.

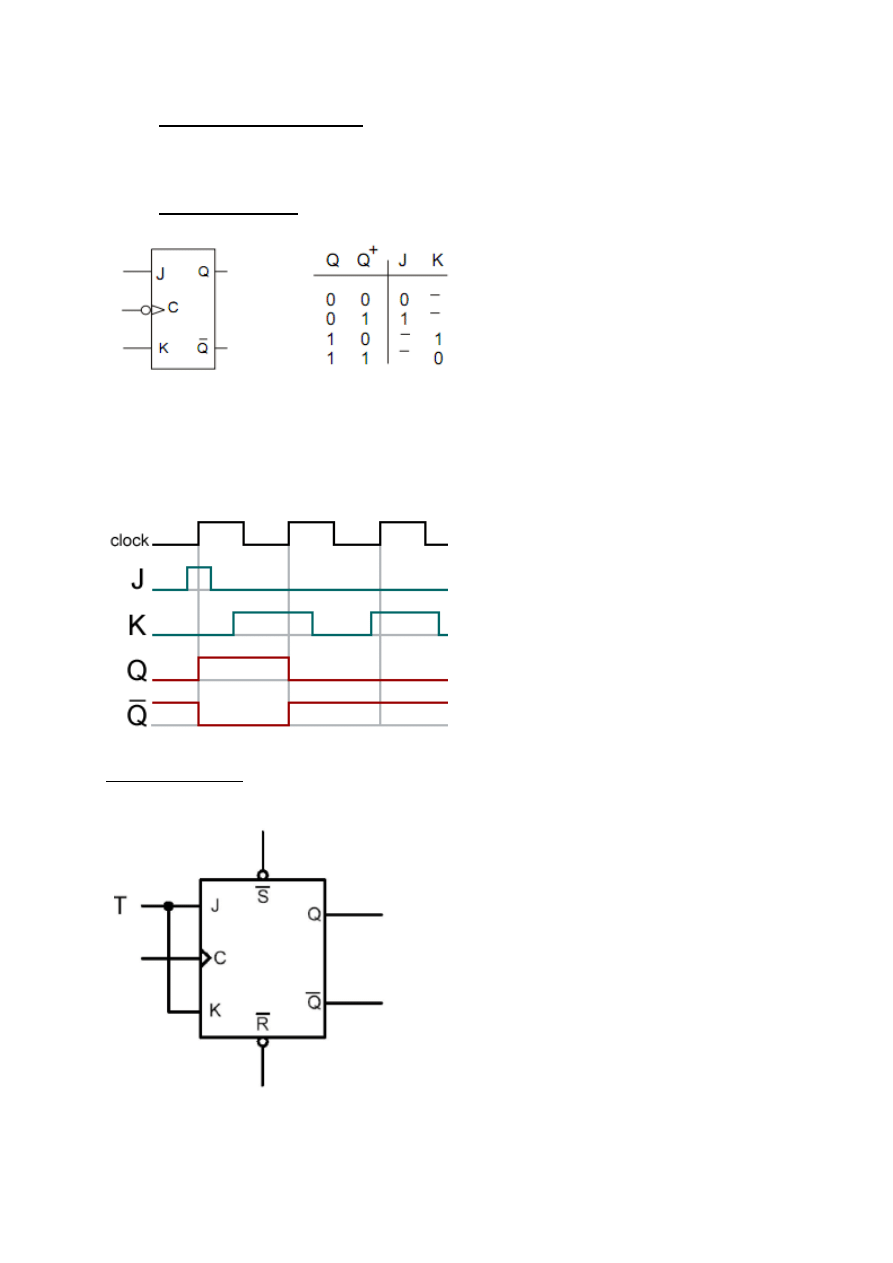

Przerzutnik typu JK:

Symbol graficzny oraz tablicę wzbudzeń przedstawia rysunek:

Przerzutnik ma dwa wejścia informacyjne oznaczone literami J i K oraz wejście

zegarowe C.

Przerzutnik reaguje w chwili narastającego (lub opadającego) zbocza zegara.

Jeśli wejście J=1, to nastąpi przełączenie wyjścia Q na stan 1. Jeśli na wejściu K=1, następuje

przełączenie wyjścia Q na stan 0.

Przerzutnik typu T:

Przerzutnik typu T to taki przerzutnik, który po

podaniu wartości logicznej 1 na wejście T i

wyzwoleniu zboczem sygnału zegarowego, zmienia

stan wyjść na przeciwny. Podanie 0 na wejście T

powoduje zachowanie bieżącego stanu

przerzutnika.

W naszym układzie został on stworzony poprzez

modyfikację przerzutnika JK tak jak na schemacie

obok.

2. REALIZACJA PROJEKTU

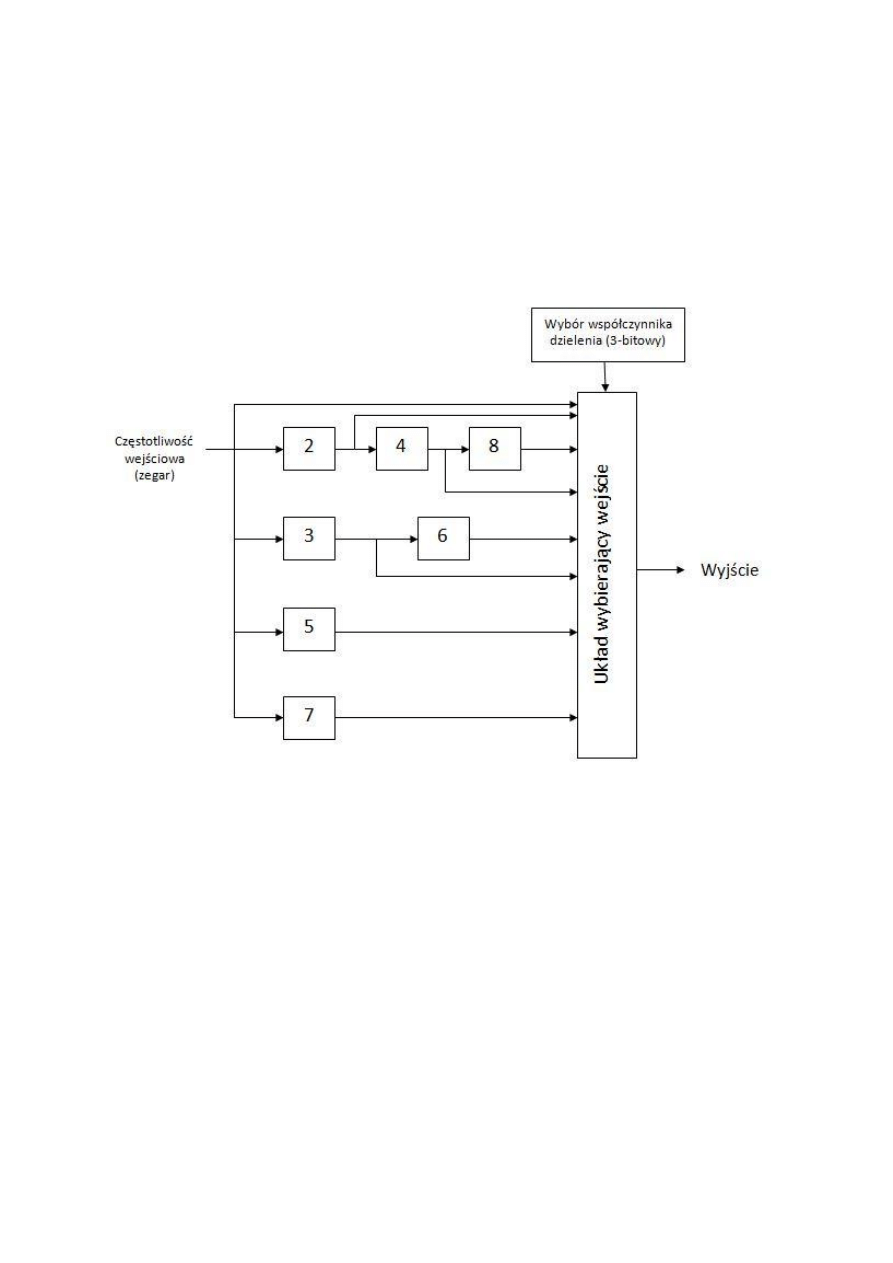

2.1 Idea działania układu i funkcjonalny schemat blokowy:

Dzielnik zrealizowany został na przerzutnikach typu JK. Częstotliwość wejściowa zostaje

dzielona przez wybrany współczynnik deklarowany na trzech bitach. Dzielnik umożliwia

dzielenie częstotliwości przez dowolną liczbę naturalną do ośmiu.

W celu zaprezentowania działania układu został on przedstawiony w postaci bloczków

pełniących różne funkcje, które odpowiednio połączone tworzą funkcjonalną całość.

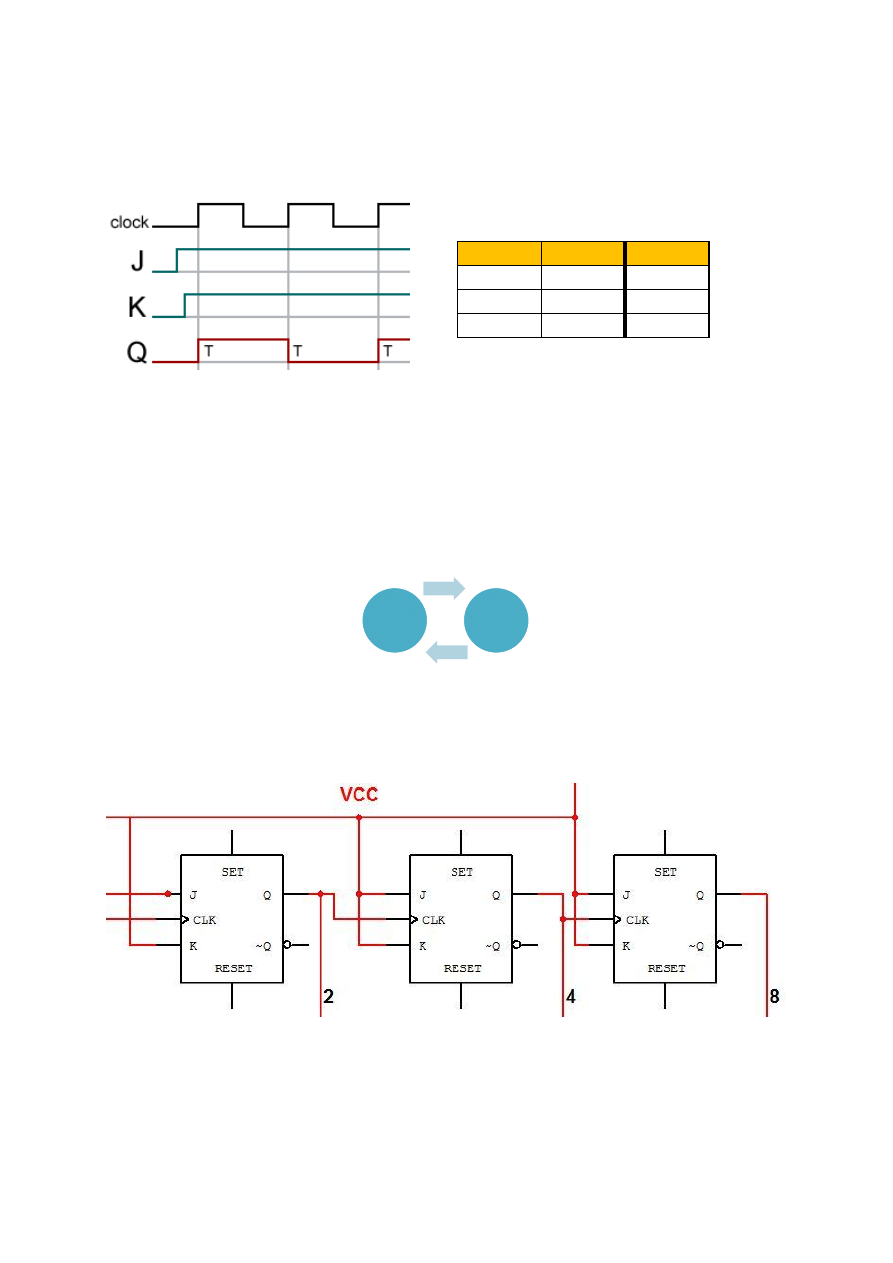

2.2 Dzielniki przez 2, 4, 8:

Dzielnik częstotliwości przez 2 został zrealizowany w bardzo prosty sposób dzięki użyciu

jednego przerzutnika typu T (zrealizowanego na przerzutniku JK).

Przerzutnik w takim połączeniu reaguje przy wysokich stanach na wejściach J i K zmieniając

stan wyjścia Q na przeciwny tylko przy zboczu narastającym (lub opadającym), co zależy od

konstrukcji dzielnika.

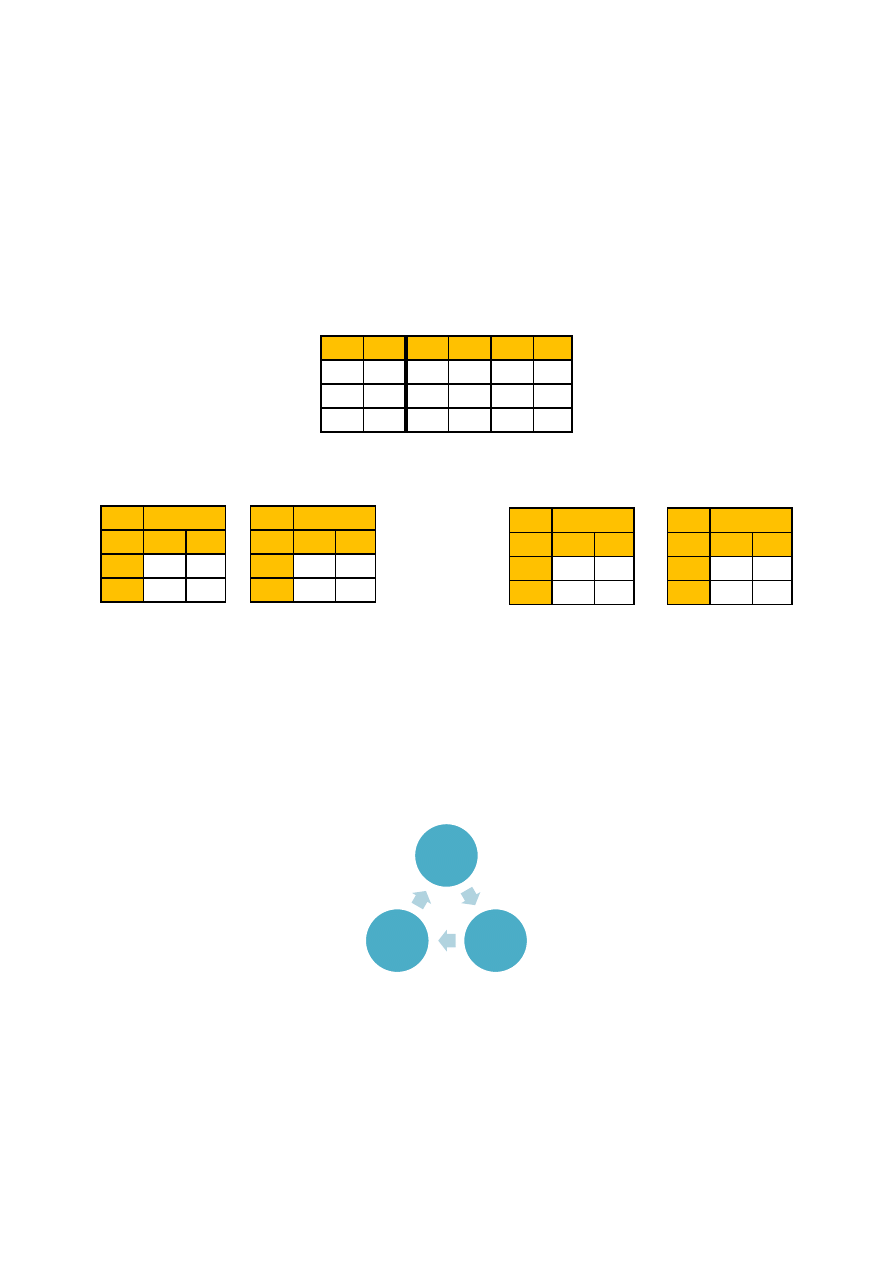

Graf przejść:

Dzielniki przez kolejne potęgi 2 możemy otrzymać, w bardzo prosty sposób, łącząc

przerzutniki łańcuchowo:

0

1

Q

Q+

JK

0

0

0

0

1

1

1

0

1

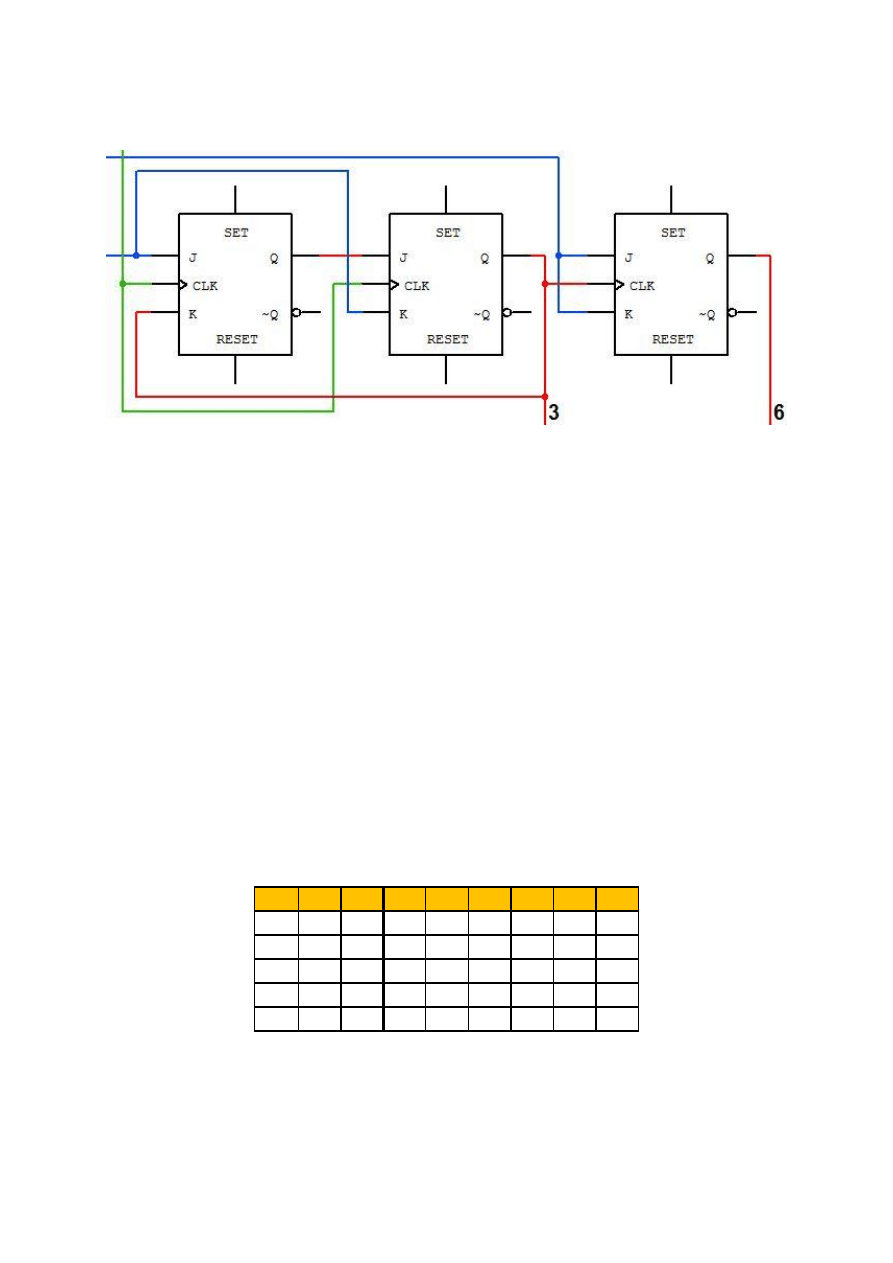

2.3 Dzielniki przez 3, 6:

Tworząc dowolny dzielnik, w pierwszym kroku obliczamy potrzebną liczbę przerzutników ze

wzoru:

x ≤ 2

n

gdzie:

x - współczynnik dzielenia,

n - liczba przerzutników

Z powyższego wzoru wynika, iż dla dzielnika przez 3 musimy użyć dwóch przerzutników.

Następnym krokiem jest utworzenie tablicy prawdy dla układu:

Q1

Q0

J1

K1

J0

K0

0

0

0

-

1

-

0

1

1

-

-

0

1

1

-

1

-

1

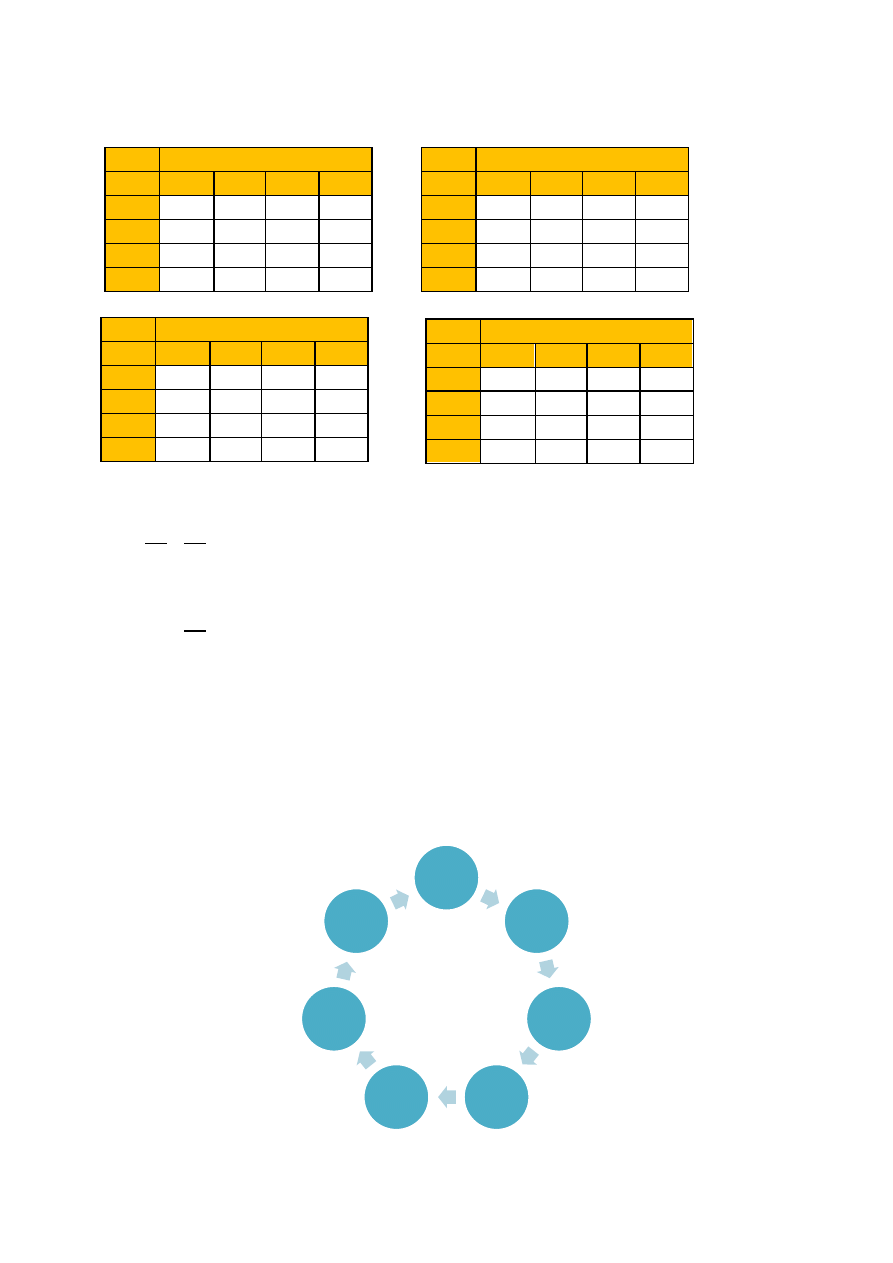

Na jej podstawie tworzymy tablice Karnaugh’a dla każdego wejścia obydwu przerzutników:

Równania wejść:

J0 = 1

K0 = Q1

J1 = Q0

K1 = 1

Graf przejść:

0

0

0

1

1

1

J0

Q0

Q1

0

1

0

1

-

1

-

-

K0

Q0

Q1

0

1

0

-

0

1

-

1

J1

Q0

Q1

0

1

0

0

1

1

-

-

K1

Q0

Q1

0

1

0

-

-

1

-

1

Wejścia i wyjścia przerzutników łączymy zgodnie z równaniami:

Dzielnik przez 6 zrealizowaliśmy poprzez kombinację układu dzielącego przez 3 i przez 2.

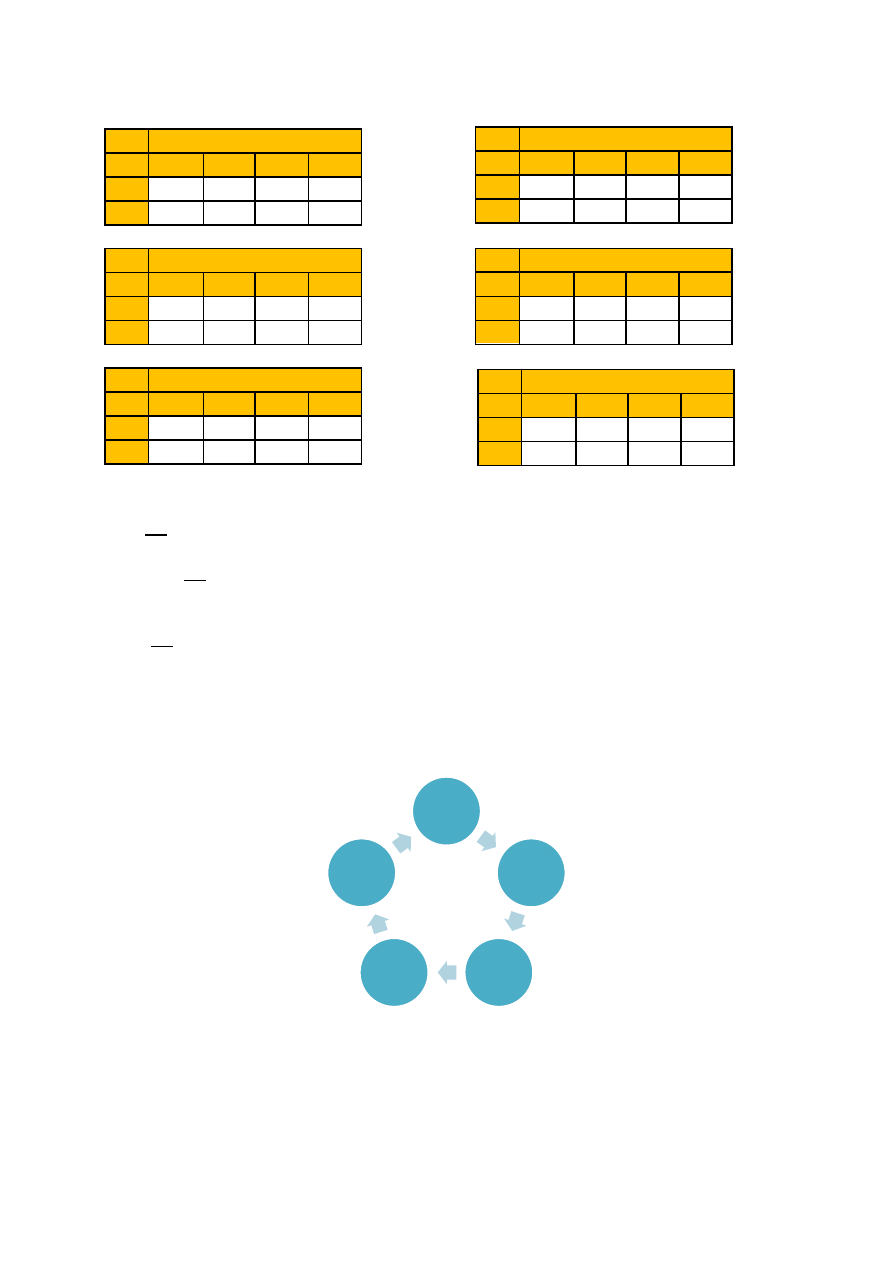

2.4 Dzielnik przez 5:

Dzielnik tworzony sposobem analogicznym jak w punkcie 2.3.

W tym przypadku potrzebujemy 3 przerzutniki. Zwiększa nam to tablicę prawdy, a co za tym

idzie ilość tablic

Karnaugh’a oraz równań wejść.

Tablica prawdy

:

Q2

Q1

Q0

J2

K2

J1

K1

J0

K0

0

0

0

0

-

0

-

1

-

0

0

1

0

-

1

-

-

1

0

1

0

1

-

-

0

0

-

1

1

0

-

0

-

1

1

-

1

0

1

-

1

0

-

-

1

Tablice

Karnaugh’a:

J0

Q1Q0

Q2

00

01

11

10

0

1

-

-

0

1

-

-

-

1

J1

Q1Q0

Q2

00

01

11

10

0

0

1

-

-

1

-

0

-

J2

Q1Q0

Q2

00

01

11

10

0

0

0

-

1

1

-

-

-

-

Równania wejść:

Graf przejść:

0

01

0

10

1

10

1

01

0

00

K0

Q1Q0

Q2

00

01

11

10

0

-

1

-

-

1

-

1

-

-

K1

Q1Q0

Q2

00

01

11

10

0

-

-

-

0

1

-

-

-

1

K2

Q1Q0

Q2

00

01

11

10

0

-

-

-

-

1

-

1

-

0

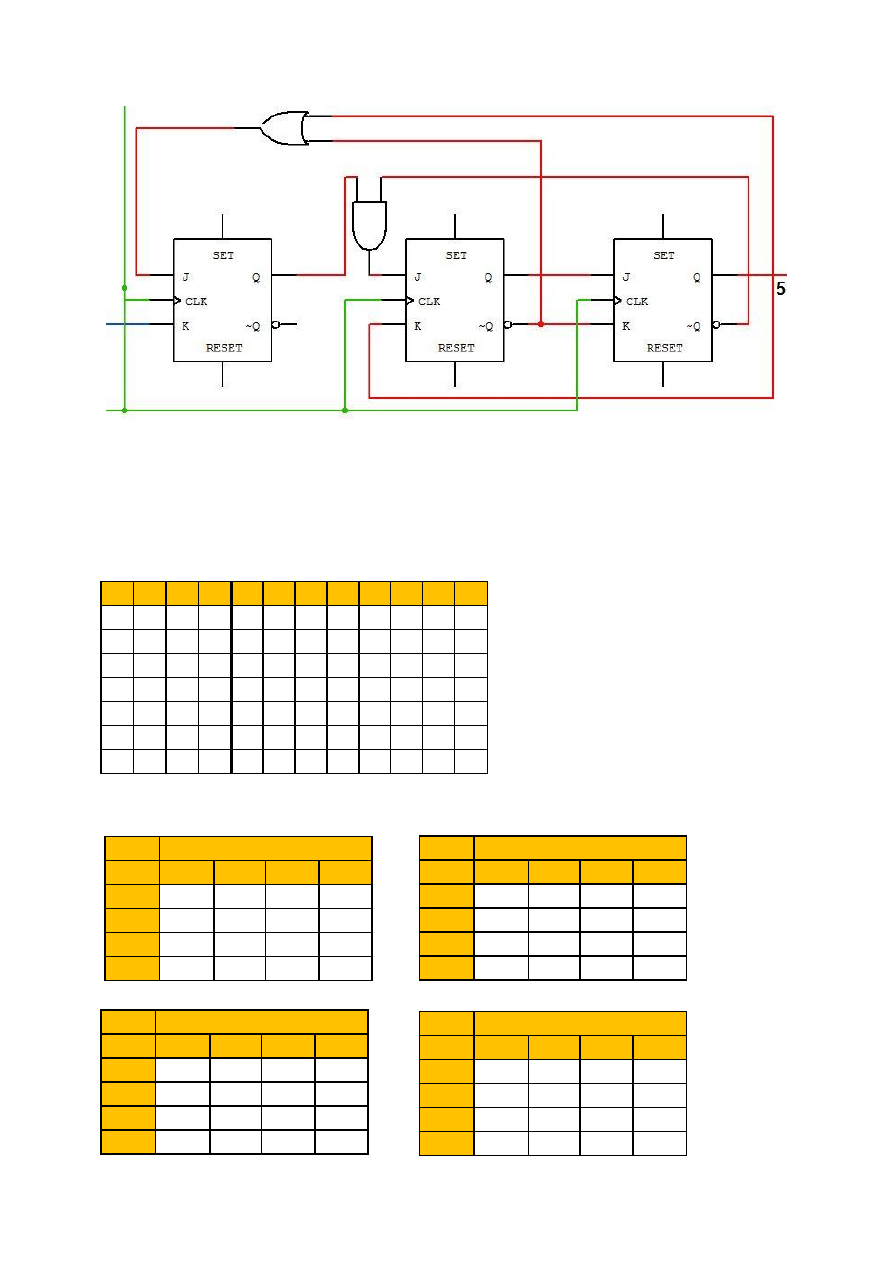

2.5 Dzielnik przez 7:

Dzielnik tworzony sposobem analogicznym, w tym przypadku potrzebujemy 4 przerzutniki.

Tablica prawdy

:

Tablice

Karnaugh’a:

J0

Q1Q0

Q3Q2

0

1

11

10

00

1

-

-

0

01

0

-

-

-

11

-

-

-

-

10

1

-

-

0

Q3 Q2 Q1 Q0 J3 K3 J2 K2 J1 K1 J0 K0

0

0

0

0

0

-

0

-

0

-

1

-

0

0

0

1

0

-

0

-

1

-

-

1

0

0

1

0

0

-

1

-

-

1

0

-

0

1

0

0

1

-

-

1

0

-

0

-

1

0

0

0

-

0

0

-

0

-

1

-

1

0

0

1

-

0

0

-

1

-

-

1

1

0

1

0

-

1

0

-

-

1

0

-

K0

Q1Q0

Q3Q2

00

01

11

10

00

-

1

-

-

01

-

-

-

-

11

-

-

-

-

10

-

1

-

-

J1

Q1Q0

Q3Q2

00

01

11

10

00

0

1

-

-

01

0

-

-

-

11

-

-

-

-

10

0

1

-

-

K1

Q1Q0

Q3Q2

00

01

11

10

00

-

-

-

1

01

-

-

-

-

11

-

-

-

-

10

-

-

-

1

J2

Q1Q0

Q3Q2

00

01

11

10

00

0

0

-

1

01

-

-

-

-

11

-

-

-

-

10

0

0

-

0

Równania wejść:

Graf przejść:

0

000

0

001

0

010

0

100

1

000

1

001

1

010

K2

Q1Q0

Q3Q2

00

01

11

10

00

-

-

-

-

01

1

-

-

-

11

-

-

-

-

10

-

-

-

-

J3

Q1Q0

Q3Q2

00

01

11

10

00

0

0

-

0

01

1

-

-

-

11

-

-

-

-

10

-

-

-

-

K3

Q1Q0

Q3Q2

00

01

11

10

00

-

-

-

-

01

-

-

-

-

11

-

-

-

-

10

0

0

-

1

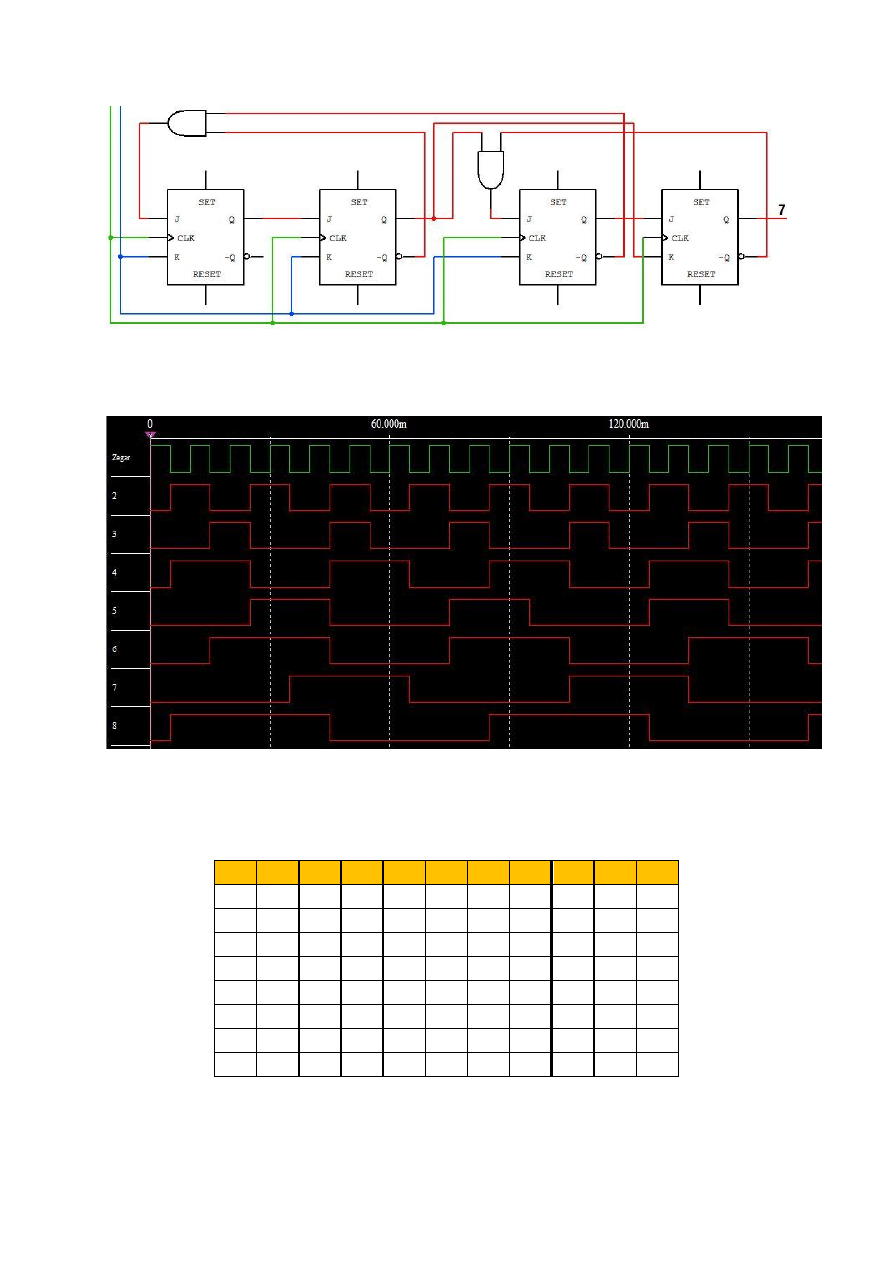

2.6. Przebiegi czasowe w zaprojektowanym układzie:

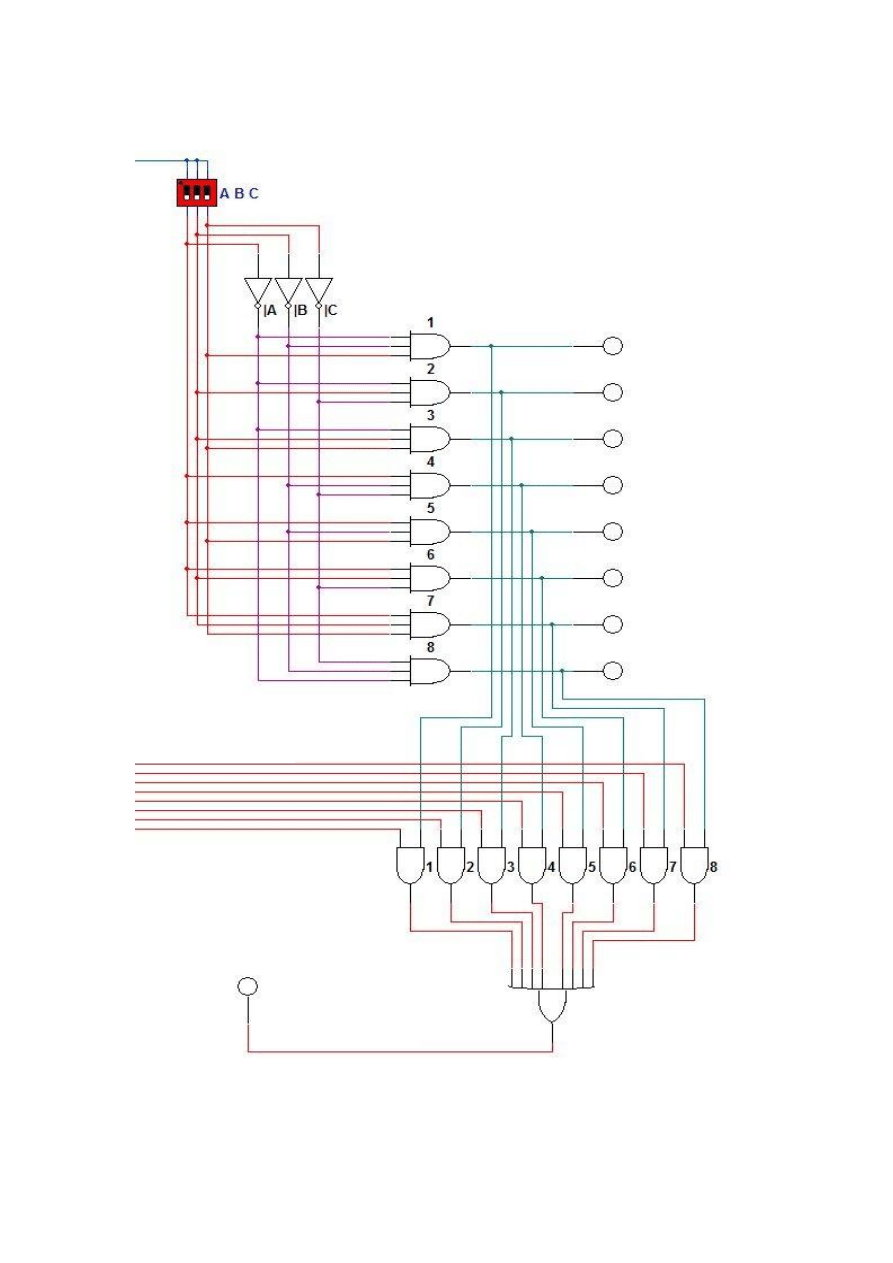

2.7 Układ wybierający wejście:

Tablica prawdy:

1

2

3

4

5

6

7

8

A

B

C

1

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

1

0

1

0

0

0

0

0

1

0

0

1

1

0

0

0

0

0

0

0

1

0

1

1

1

0

0

0

0

0

0

0

1

0

0

0

Na włączniku trzybitowym wybieramy pożądany współczynnik dzielenia zgodnie z kodem

binarnym (wyjątek – 000 odpowiada 8).

Układ bramek odpowiednio załącza wyjście wybranego dzielnika.

Sygnały z dzielników

Wyjście

Wyszukiwarka

Podobne podstrony:

programowalny dzielnik częśtotliwości, Studia, Informatyka, Semestr III, Teoria Układów Cyfrowych, L

PSL Programowalny dzielnik częstotliwości projekt 6

Dzielnik częstotliwości

projekt podstawy programowania, Politechnika Częstochowska- Wydział Budownictwa, Podstawy Programowa

Ciekawy dzielnik częstotliwośći

Ciekawy dzielnik częstotliwośći

Częstotliwości programów radiowych

prąd zmienny malej czestotliwosci (2)

Nowy Prezentacja programu Microsoft PowerPoint 5

Charakterystyka programu

1 treści programoweid 8801 ppt

Programowanie rehabilitacji 2

Rola rynku i instytucji finansowych INowy Prezentacja programu Microsoft PowerPoint

W13 Pomiary częstotliwości i czasu ppt

więcej podobnych podstron