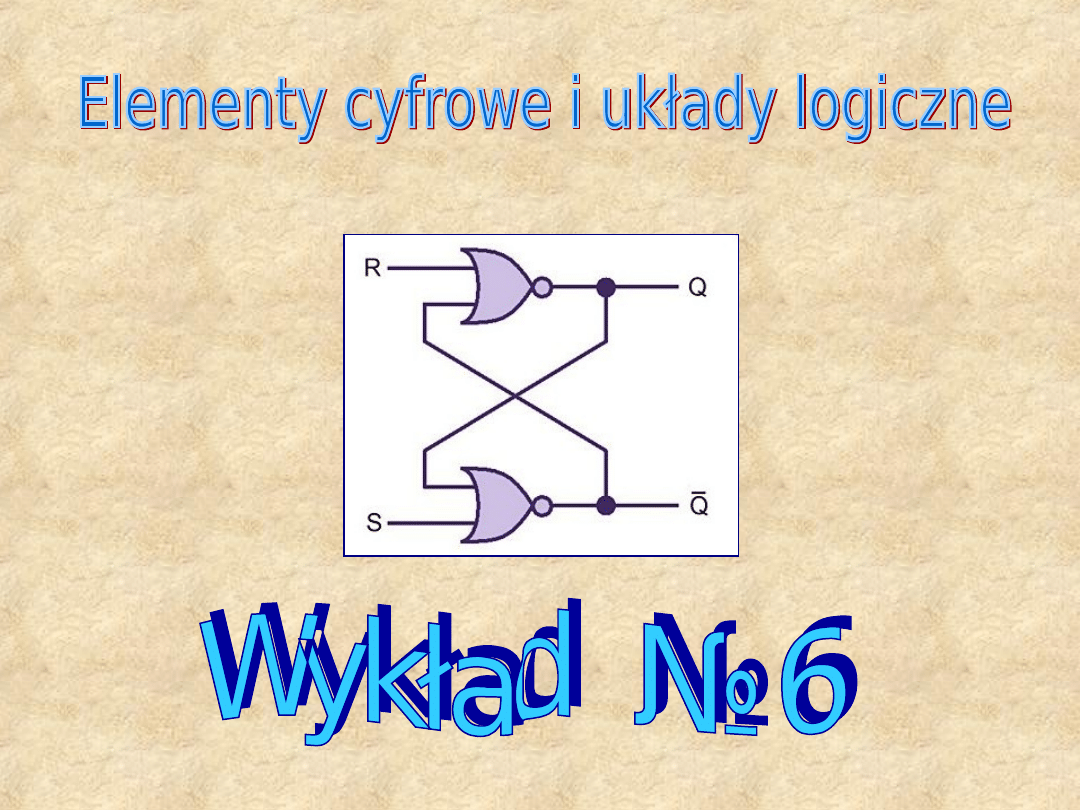

1

Dr Galina

Cariowa

2

Legenda

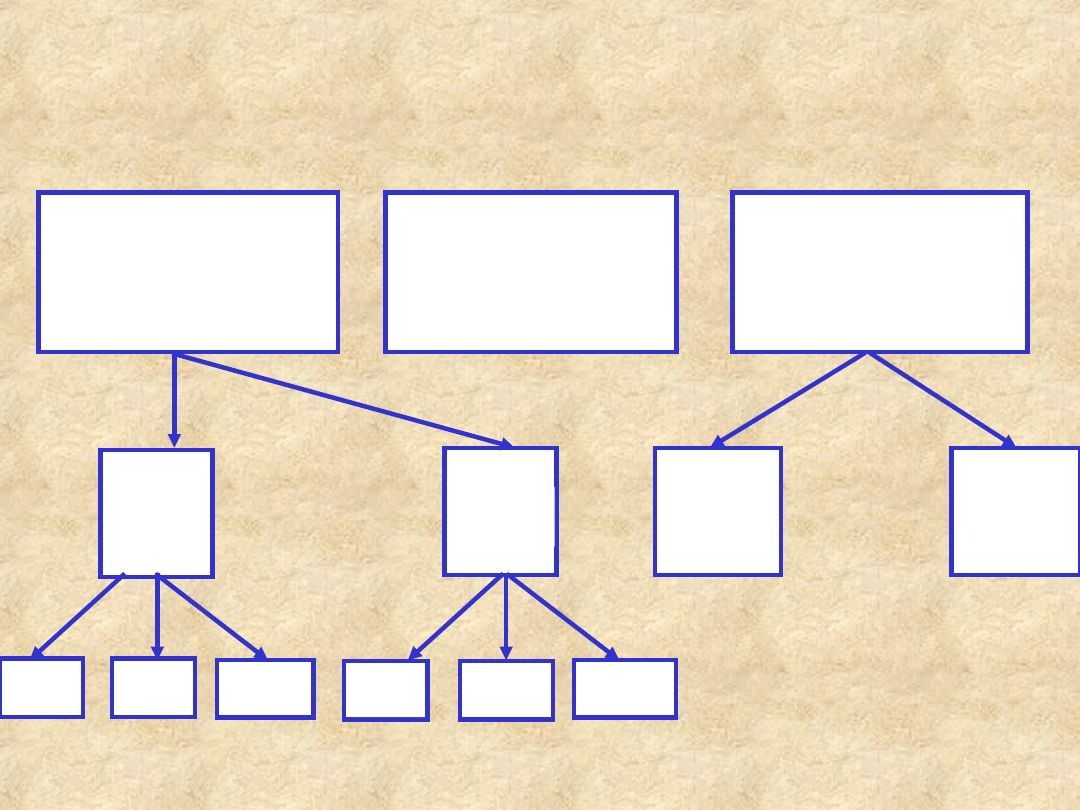

Procedura projektowania

układów kombinacyjnych.

Podział układów VLSI.

3

Procedura

projektowania

Specyfikacja

Napisz, jeśli jeszcze nie

istnieje, specyfikację

układu

Opracowanie opisu formalnego

Wygeneruj tablicę

prawdy lub początkowy zestaw równań

boolowskich, które definiują wymagane

zależności między wejściami a

wyjściami układu

Optymalizacja

Wykonaj dwupoziomową lub wielopoziomową

optymalizację. Narysuj schemat lub dostarcz listę

połączeń układu z wykorzystaniem bramek AND, OR i

NOT.

Wybór i realizacja w

technologii

Przekształć schemat logiczny lub listę

połączeń w nowy schemat lub w nową listę

połączeń zgodnie z wymaganiami

dostępnej technologii implementacji

układu

Weryfikacja

Sprawdź

poprawność

końcowego projektu

4

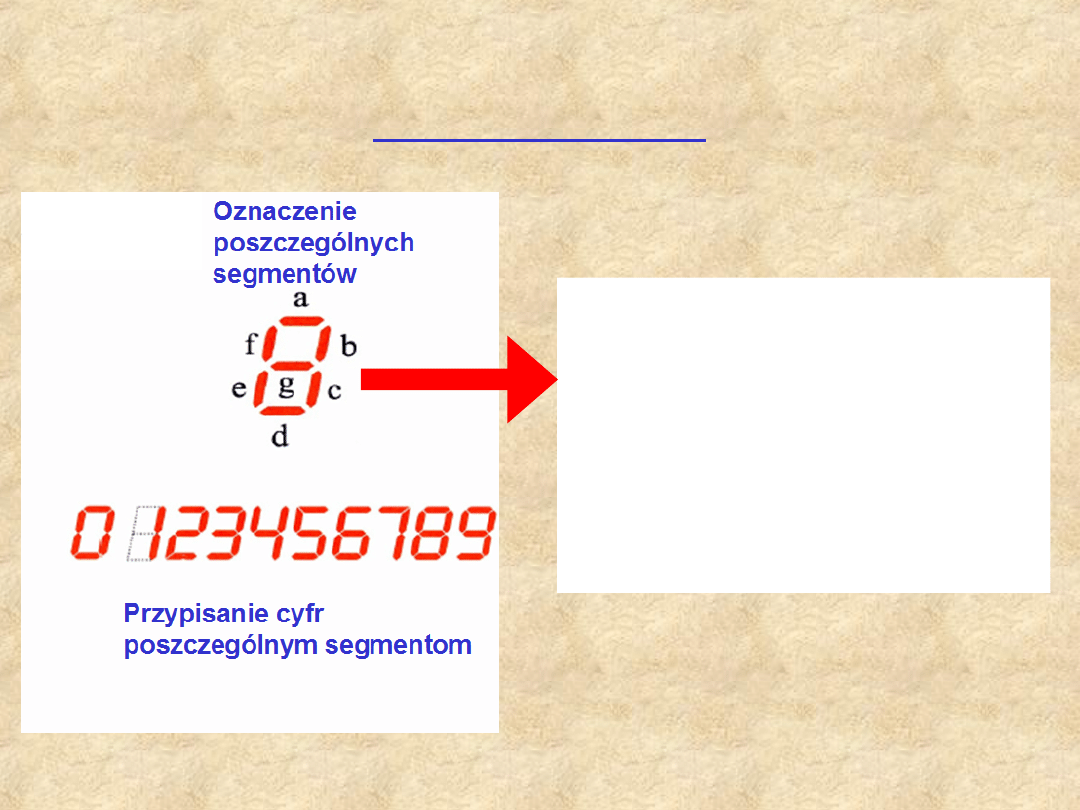

Wyświetlacz

segmentowy

(specyfikacja)

Przykład

. Projekt dekodera kodu BCD na

kod

wyświetlacza 7 –

segmentowego.

Każda cyfra wyświetlacza diodowego jest

zbudowana z 7 segmentów LED (dioda

elektroluminescencyjna

).

Każdy segment może zostać podświetlony za

pomocą sygnału cyfrowego.

Dekoder BCD na podstawie cyfry dziesiętnej w

kodzie BCD generuje sygnały wyjściowe dla

poszczególnych segmentów wyświetlacza, aby

wyświetlił on tę cyfrę

.

5

Wyświetlacz segmentowy

(specyfikacja)

Siedem wyjść dekodera

(a, b, c, d, e, f, g)

odpowiada określonym

segmentom

wyświetlacza.

6

Wyświetlacz segmentowy

(specyfikacja)

Dekoder kodu BCD ma

cztery wejścia

oznaczone symbolami

A, B, C, D,

które

odpowiadają cyfrze kodu BCD,

i

siedem wyjść

,

a, b, c, d, e, f, g

, które

sterują poszczególnymi segmentami

wyświetlacza.

7

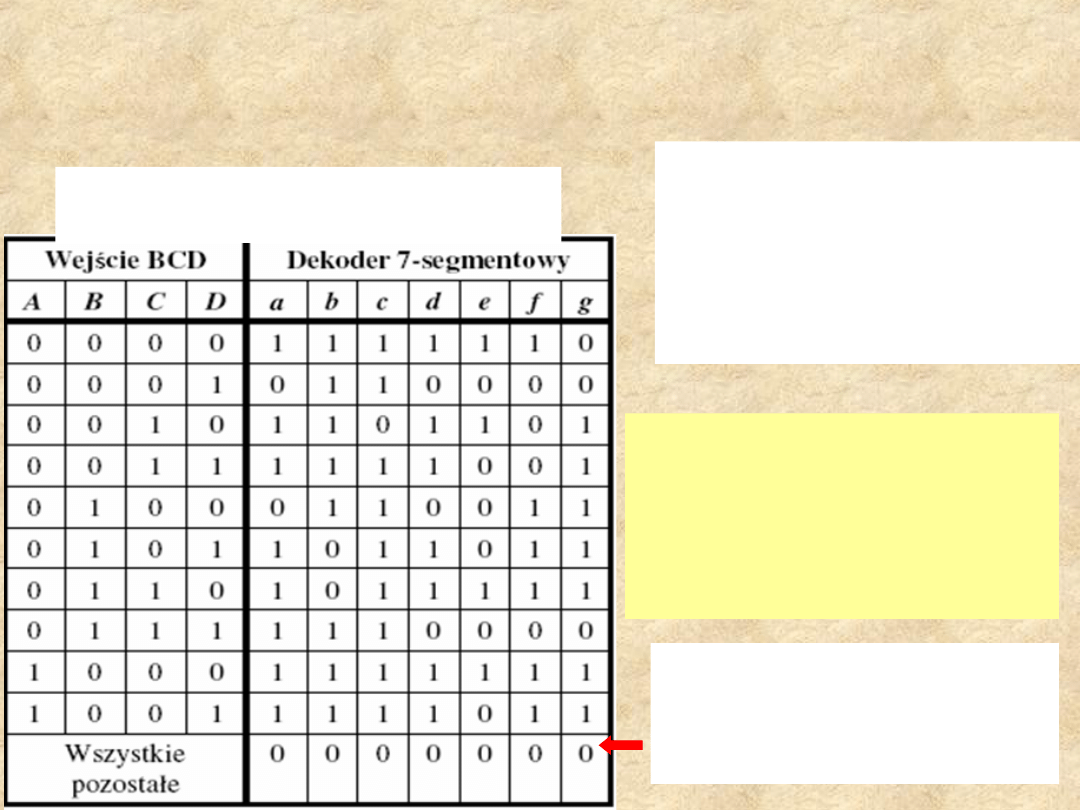

Wyświetlacz

segmentowy

(opracowanie opisu formalnego)

Każda cyfra BCD powoduje

zapalenie odpowiednich

segmentów wyświetlacza.

(np.

0101

odpowiada 5, która

jest wyświetlana za pomocą

segmentów a, c, d, f oraz g).

Tablica prawdy układu

kombinacyjnego:

Tablica prawdy zakłada, że

sygnał odpowiadający

logicznej

1włącza

dany

segment, a sygnał

odpowiadający logicznemu

0

go

wyłącza

.

Nieużywanym kombinacjom

binarnym przypisujemy

stan

wyłączenia

wszystkich

segmentów.

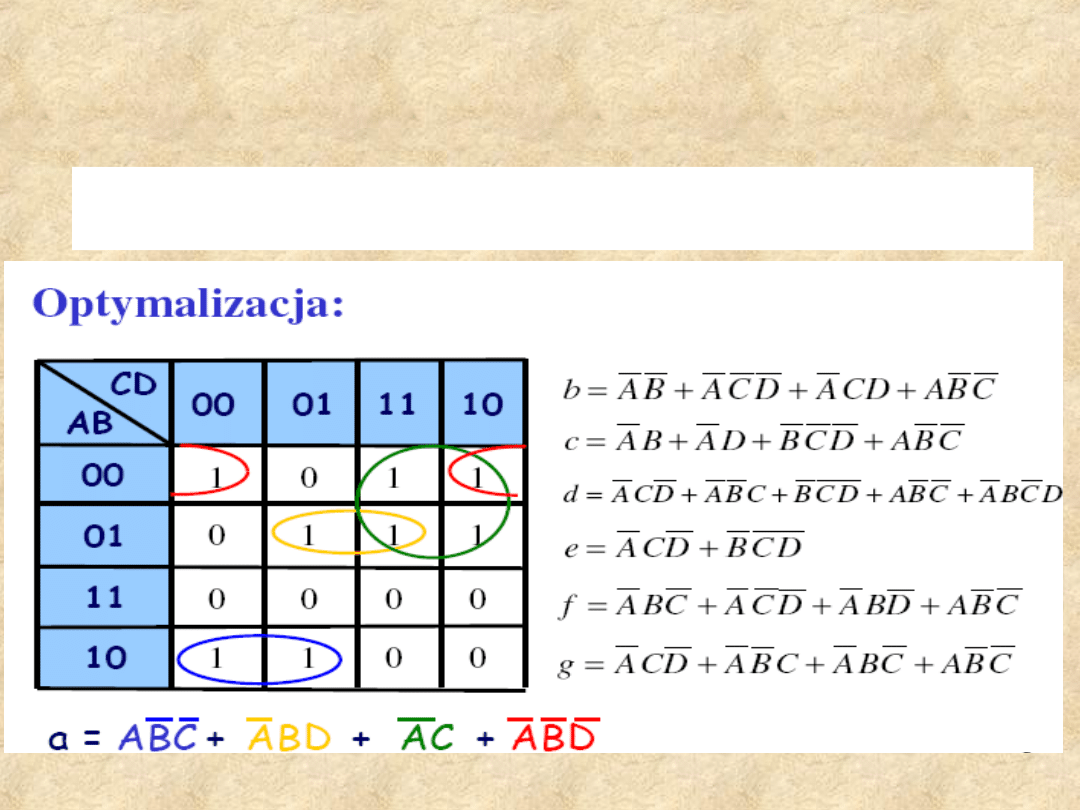

8

Wyświetlacz

segmentowy

(Optymalizacja)

Informację z tablicy prawdy przenosimy do siedmiu tablic

Karnaugha.

9

Wyświetlacz

segmentowy

Niezależna implementacja:

AND – 27

,

OR – 7

. Wspólne iloczyny –

14

.

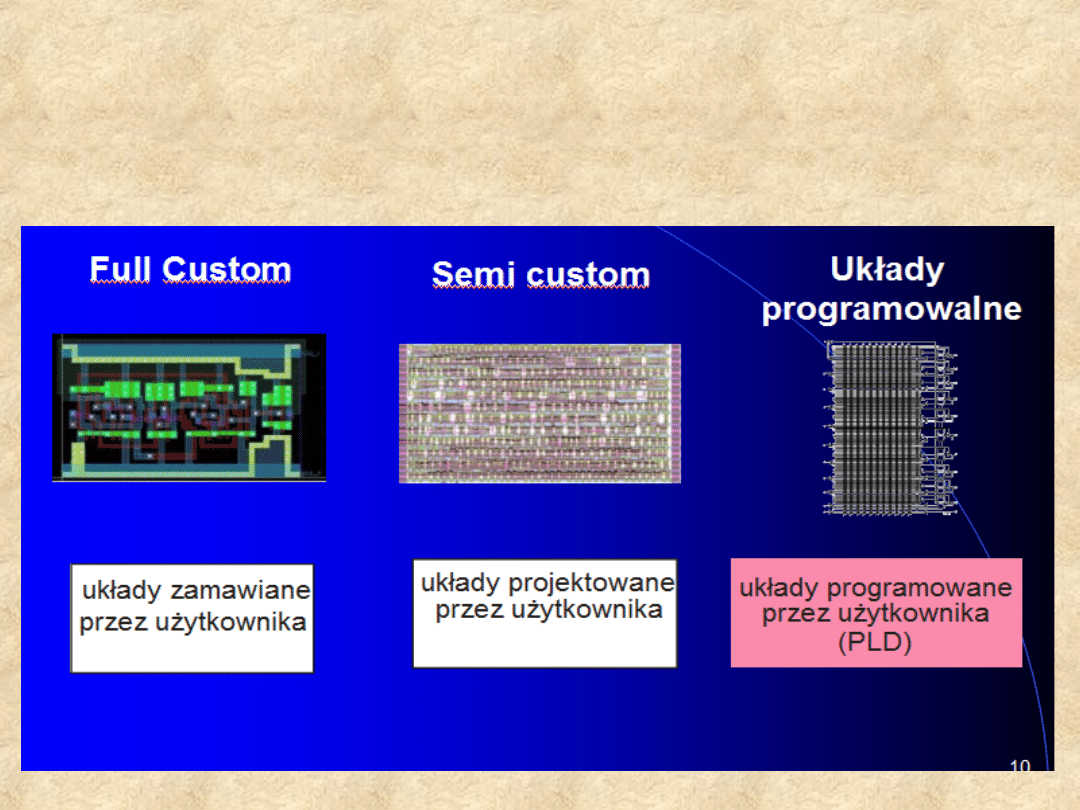

10

Wybór

i realizacja

w technologii

11

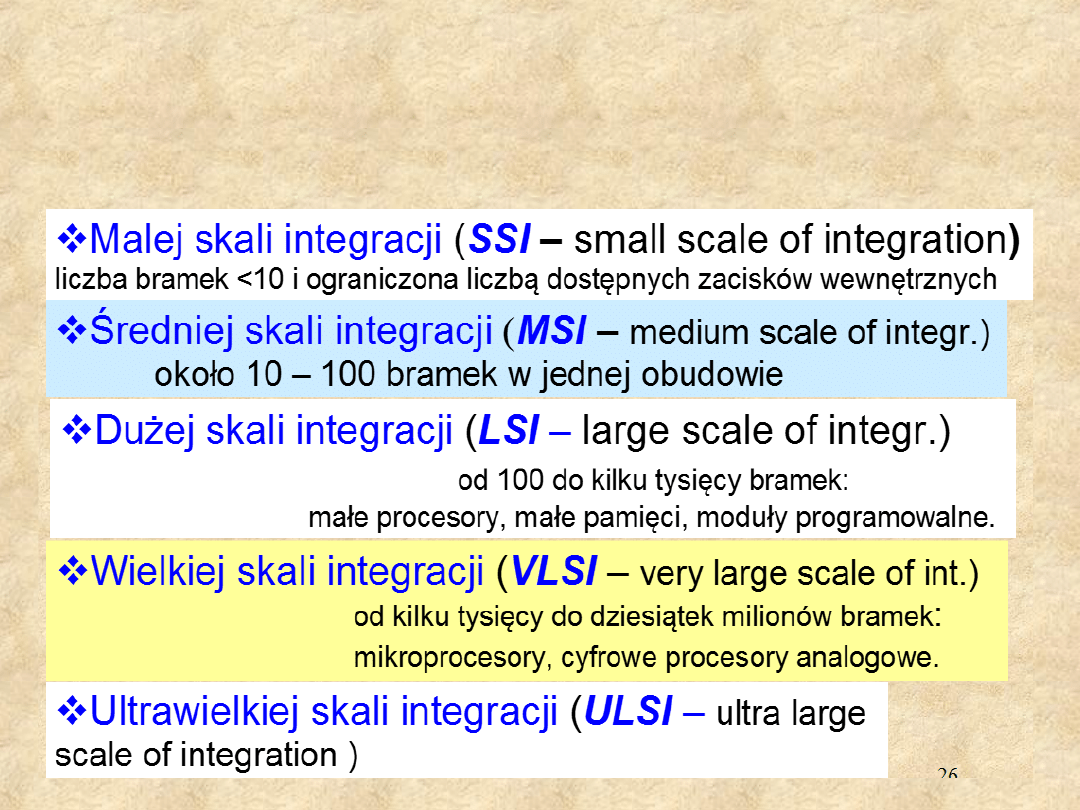

Podział układów ze

względu

na stopień

scalenia

12

Podstawowe metody

projektowania układów

VLSI

13

Podstawowe metody

projektowania układów

VLSI

układy

projektowane

przez

użytkownika

(

semi-custom

)

układy

programowane

przez

użytkownika

układy

zamawiane

przez

użytkownika

(

full-custom

)

Standar

d

Cell

Design

Gate

Arra

y

PLD

FPGA

PL

A

PAL

MUX

TLU

MAX

Gates

14

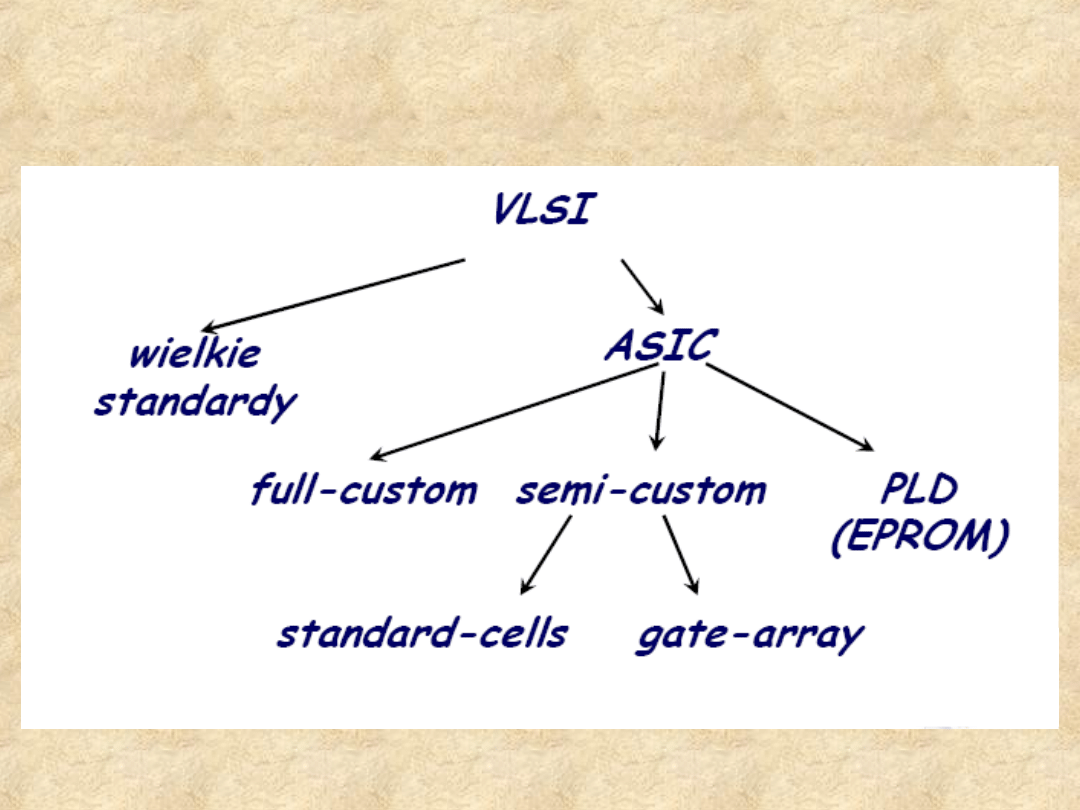

Podział układów

VLSI

Wielkie standardy

– układy produkowane

głównie z inicjatywy

producenta.

ASIC

– (application specific inegrated

circuits) -

to układy

na zamówienie klienta.

15

Wielkie standardy

Standardowe

układy

–

uniwersalne elementy

o strukturze

niemodyfikowalnej po

wyprodukowaniu.

bramki i

układy

funkcjonalne

rodzin TTL,

ECL, MOS,

mikroproceso

ry, pamięci.

16

Podział układów

ASIC

Układy na zamówienie z

ograniczonym

(niepełnym) cyklem

projektowania

(

semi-

custom

);

Układy programowane przez

użytkownika

(

PLD

).

Układy na zamówienie z pełnym

cyklem

projektowania (

full-

custom

);

W zależności od technologii i techniki

projektowania specjalizowane układy

scalone klasyfikujemy w następujących

kategoriach:

17

Układy

ASIC

18

Układy na zamówienie z

pełnym cyklem

projektowania (full-

custom):

W tej metodzie wykonuje się cały projekt

układu, wykonuje się „ręcznie” projektowanie

każdego elementu układu, wzajemnego

rozmieszczenia elementów i połączeń między

nimi.

Ze względu na wysokie koszty, metoda ta

jest uzasadniona dla układów gęsto

upakowanych, szybkich i sprzedawanych

w wielkich ilościach.

19

Zalety metody full-

custom:

1.Największa

uniwersalność.

2.Możliwość minimalizacji powierzchni

układu.

Wady metody full-

custom:

1. Wysoki

koszty.

3.Skomplikowan

a.

3. Pełna swoboda

projektanta.

2.Czasochłonna

.

4. Raz wyprodukowany układ nie może zmienić swojej

funkcji.

20

Układy

semi-custom

a)układy wykorzystujące komórki

standardowe

(standard cell design);

b) układy na płytkach wstępnie

przygotowanych

jak matryce bramek

AND (

gate arrays

).

W grupie układów

projektowanych przez

użytkownika wyróżnić można:

21

Metoda semi-

custom

Cechą charakterystyczną

układów Semi - custom jest

wielokrotne

wykorzystywanie raz

zaprojektowanych bloków

funkcjonalnych

, które są

przechowywane w bibliotece.

Bloki takie są zwane

komórkami

bibliotecznymi

.

Wielkości struktur

scalonych oraz ich

parametry elektryczne są z

góry narzucone.

22

Metoda standard-

cells

Projektant ma do dyspozycji

bibliotekę gotowych

już wcześniej

zaprojektowanych

bramek

logicznych

, z których składa układ.

Te części projektu są łączone ze sobą

tworząc projekt układu scalonego.

23

Układy standard - cells

Projektowanie matryc komórek polega

na

składaniu układu z gotowych bramek,

multiplekserów, liczników, itp.,

a następnie przesłaniu tak

zaprojektowanego układu do

producenta, który korzystając z

biblioteki masek wytwarza zamówione

układy

24

Zalety metody standard -

cells:

Mniejsze nakłady

finansowe

1.Mniejsza gęstość

upakowania.

Wady:

2.Układy standard cells są

wolniejsze

od układów full-

custom.

25

Metoda Gate

arrays

Projektant ma

gotowe płytki

dla

każdego nowego projektu i wykonuje

jedynie połączenia

pomiędzy

elementami logicznymi znajdującymi

na gotowej matrycy bramek o

określonych rozmiarach.

Wiele czynności

składających się na proces

wytwarzania jest

wspólnych, więc mogą być

wykonany w wielu

projektach.

26

Zalety metody gate

arrays (semi-custom):

2.Mniejszy czas projektowania

układu od

rozpoczęcia projektu do otrzymania

gotowego ukladu.

3.

Najtańsza

metoda

.

Wad

a:

Marnotrawstwo powierzchni

układu –wiele

komórek zwykle pozostaje niewykorzystanych

.

1.Możliwość

wcześniejszego wyprodukowania

płytek

zawierających matryce komórek bez

połączeń.

27

Układy FPLD

Czas potrzebny do

otrzymania prototypów

nowo zaprojektowanego

układu w stylu

Full-

custom

lub

Semi-

custom

jest rzędu co

najmniej

kilku tygodni

.

W przypadku

małych

serii układów

specjalizowanych

(do

kilku tysięcy) najbardziej

opłacalne jest

zastosowanie przez

użytkownika układów

programowanych

FPLD

-

Field Programmable

Logic Devices

,

(programowalne moduły

logiczne).

28

Układy programowane

przez użytkownika (PLD):

Układy programowalne

to układy typu

matrycowego lub komórkowego, jednak z

możliwością programowania połączeń

elektrycznych.

Producent dostarcza „prefabrykaty”

projektantowi, który może je zaprogramować

u siebie „na biurku”.

29

Układy programowane

przez użytkownika (PLD):

Najważniejsza cecha układów PLD

:

Możliwość nadawania układom przez

programowanie określonych przez

użytkownika cech funkcjonalnych.

Układy PLD

- gotowe wyprodukowane

układy scalone, których

właściwości

funkcjonalne są definiowane

nie przez

producenta, lecz

przez końcowego

użytkownika.

30

Zalety metody PLD:

1.Krótki czas opracowania

prototypu;

2.Łatwość jego

modyfikacji;

3.Dostępne są „z

półki”;

4.Szybkość

działania;

5.Doskonałe parametry

pojemności.

Wady metody

PLD:

Duży koszt

jednostkowy

.

6. Jedyne rozwiązanie dla urządzeń

unikatowych.

31

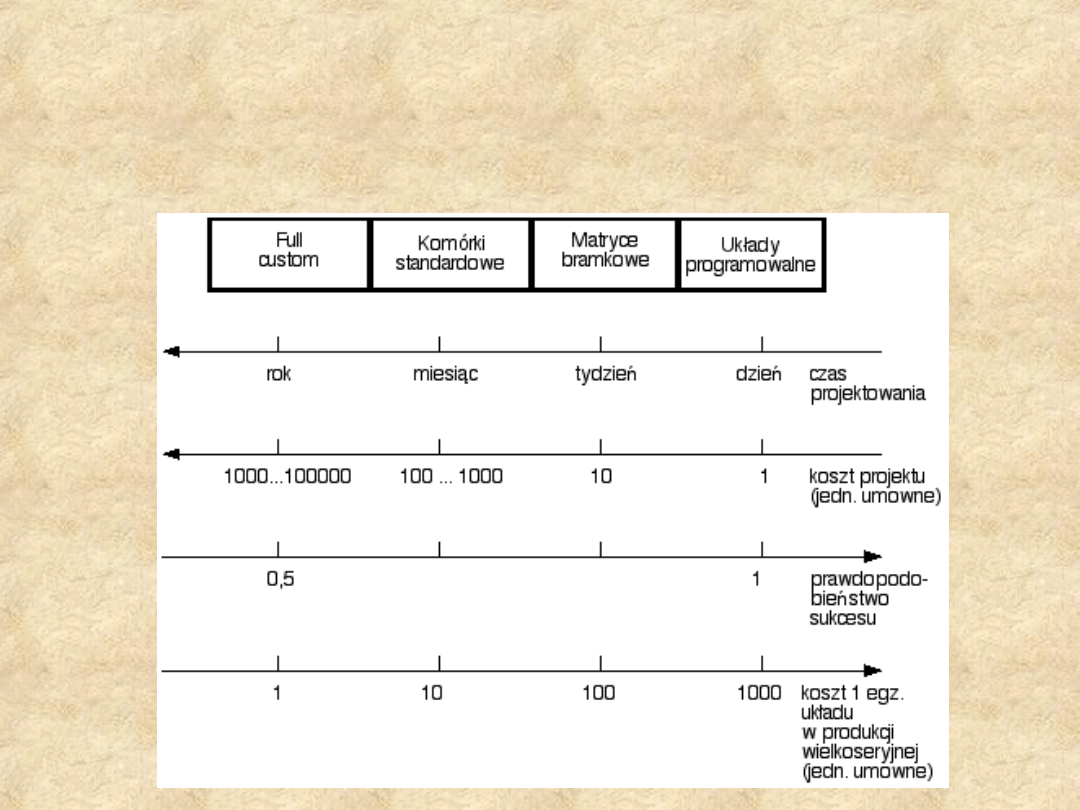

Wykres zależności

pomiędzy metodami projektowania, a czasem projektowania,

kosztem i prawdopodobieństwem sukcesu (tj. poprawnego

działania pierwszej zaprojektowanej wersji układu bez przeróbek

i poprawek)

32

Ukłądy ASIC

charakteryzuje:

1. Wyższa

niezawodność

2.Mniejsza

pracochłonność

3. Mniejszy

koszt

4. Nowe

funkcje

5. Lepsze parametry

6. Ochrona myśli

technicznej

33

Komórki

W przypadku

technologii z niepełnym

cyklem projektowania i

technologii opartych na

matrycach

bramkowych układy są

konstruowane przez

połączenie komórek.

Biblioteka komórek

– zbiór komórek

dostępnych dla danej

technologii

implementacji. Każda

komórka jest

dokładnie opisana.

Biblioteka opisanych

komórek stanowi

fundament procesu

wyboru i realizacji

układów w określonej

technologii (ang.

technology –

mapping)

34

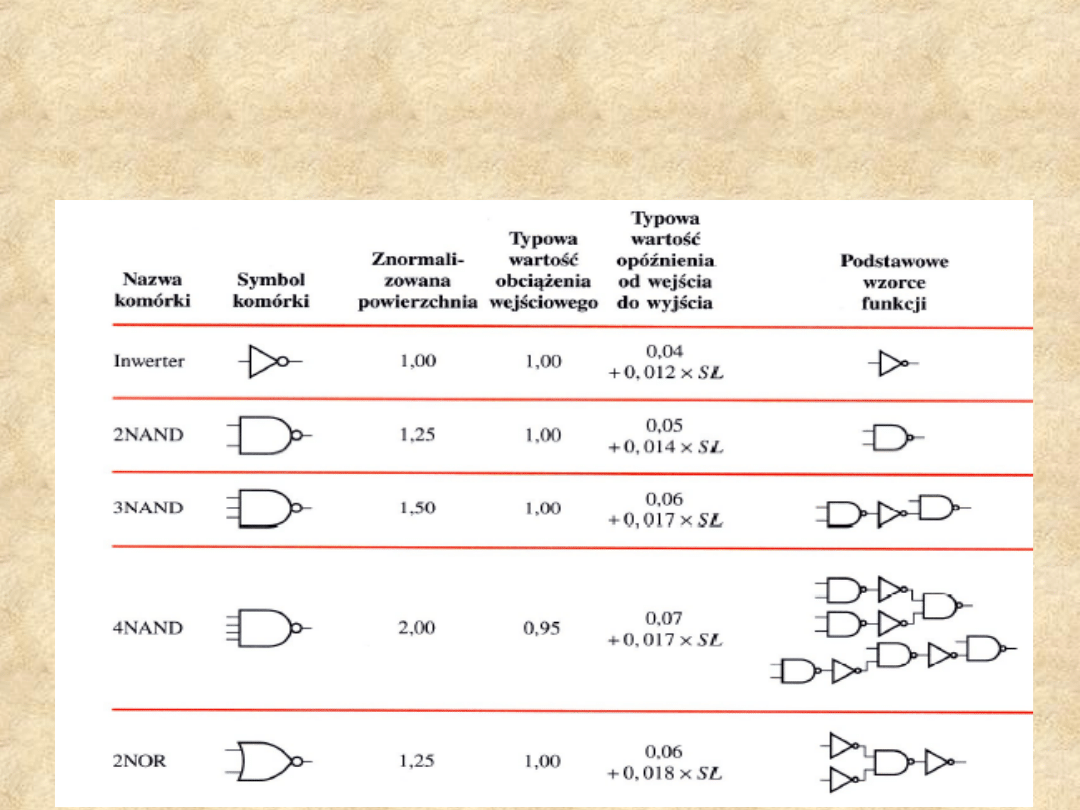

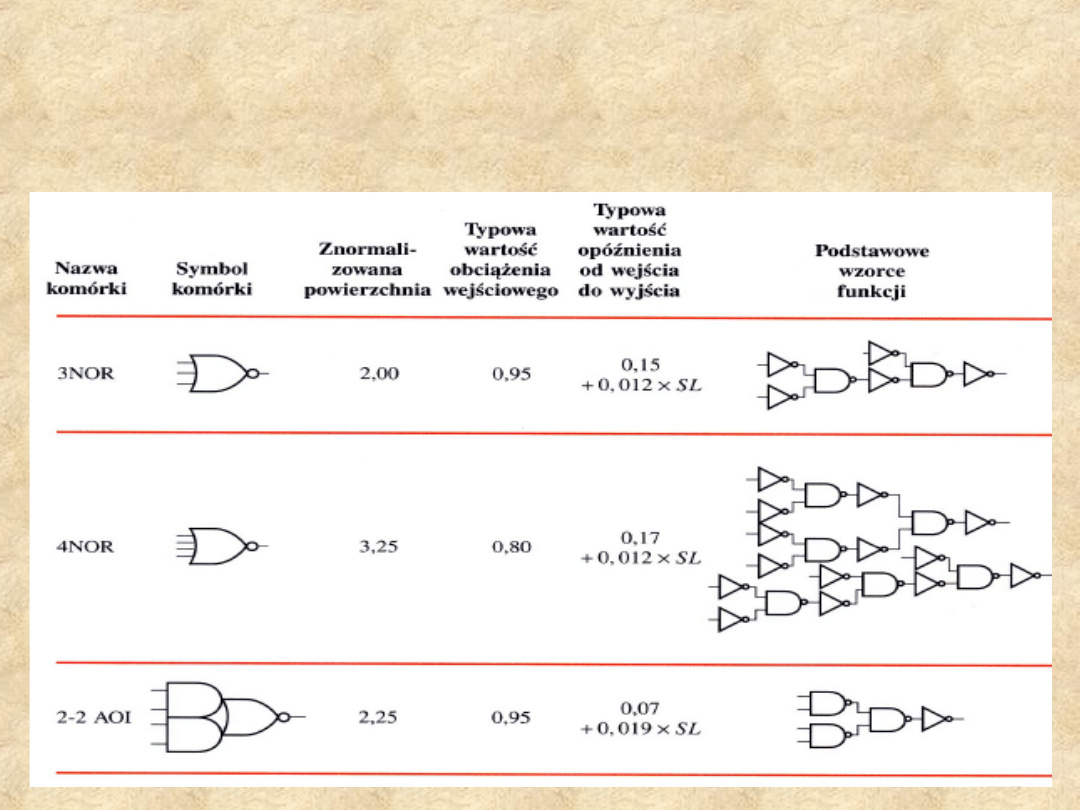

Biblioteka komórek

Biblioteki komórek mogą składać się:

1)

z

bramek jednego typu

, takich jak bramki

typu NAND;

2)

z

bramek wielu typów

.

Komórki w określonej technologii

projektowania są zorganizowane w postaci

jednej lub kilku bibliotek.

35

Biblioteka komórek

Układ, który początkowo składa się z bramek

AND, OR i NOT,

w trakcie etapu wyboru

technologii jest przekształcany w taki układ, w

którym występują

tylko komórki z zastosowanej biblioteki

.

36

Specyfikacja komórek

Schemat logiczny funkcji

realizowanej

przez komórkę

.

Obciążenie wejściowe,

wyrażone w

obciążeniach standardowych.

Opóźnienia sygnału

z każdego wejścia

komórki do każdego wyjścia komórki.

Jeden lub wiele

przykładowych

zastosowań

komórki w implementacjach.

Jeden lub wiele

modeli komórki

w postaci

opisów w HDL.

Wymagania dotyczące powierzchni

zajmowanej przez komórkę, często

znormalizowanej względem powierzchni

małej komórki (np. inwertera).

37

Specyfikacja komórek c.d.

A także (opcjonalnie, jeśli narzędzie

automatycznie generuje rozmieszczenie

elementów układu):

Rozmieszczenie elementów układu

scalonego dla komórki

.

Plan rozmieszczenia wejść, wyjść

oraz połączeń zasilania i masy komórki.

38

Przykład biblioteki komórek,

wykorzystywanej w procesie

wyboru technologii

39

Przykład biblioteki

komórek c.d.

40

Obliczanie opóźnienia

komórki

(wpływ obciążenia

na opóźnienie komórki)

Wyjście komórki 2NAND steruje

komórkami:

inwerterem,

4NAND, 4NOR.

Suma obciążeń standartowych

wejściowych:

75

,

2

80

,

0

95

,

0

00

,

1

SL

Opóźnienie komórki 2NAND, sterującej komórkami

inwerter, 4NAND, 4NOR:

ns

t

p

089

,

0

75

,

2

014

,

0

05

,

0

41

Techniki wyboru i

realizacji w określonej

technolocii

Przekształcenie projektu układu

z użyciem bramek typu AND,

OR oraz inwerterów w projekty

oparte na stosowaniu komórek

dostępnych w technologiach

realizacji układu

.

42

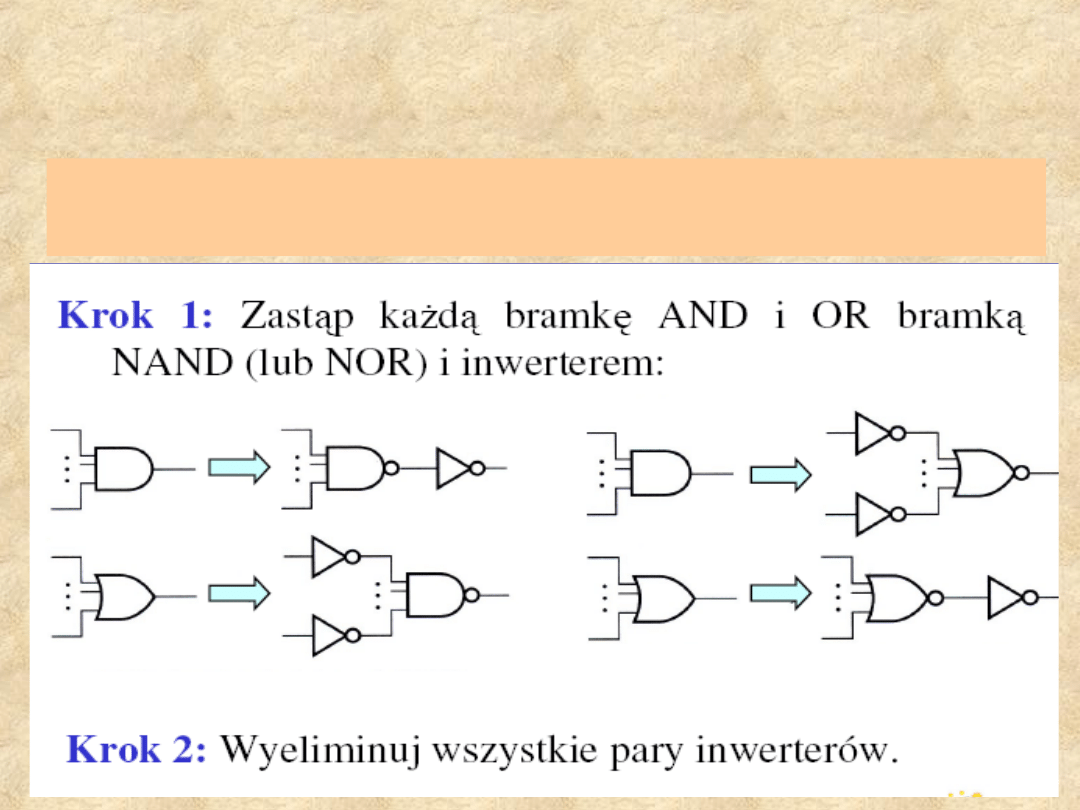

Procedura konwersji AND

(OR)

do NAND (NOR)

Generacja układu zbudowanego z bramek NAND (lub

NOR)

o nieograniczonej liczbie wejść.

43

Procedura konwersji

AND(OR)

do NAND (NOR)

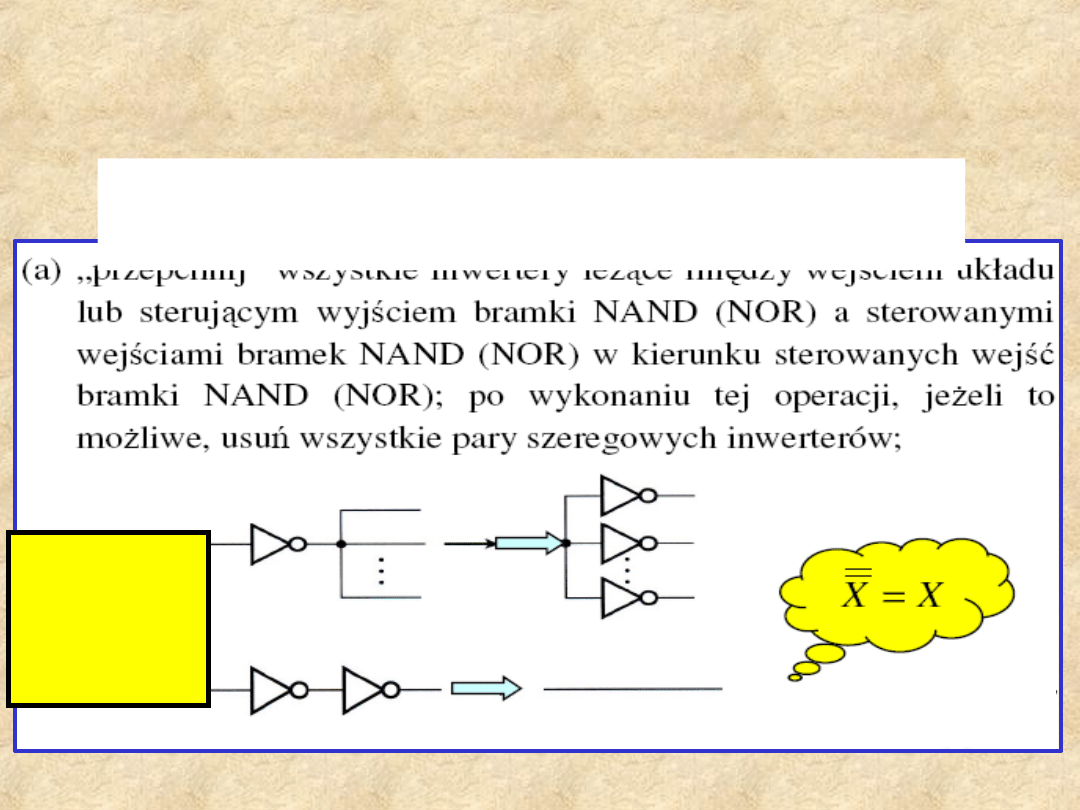

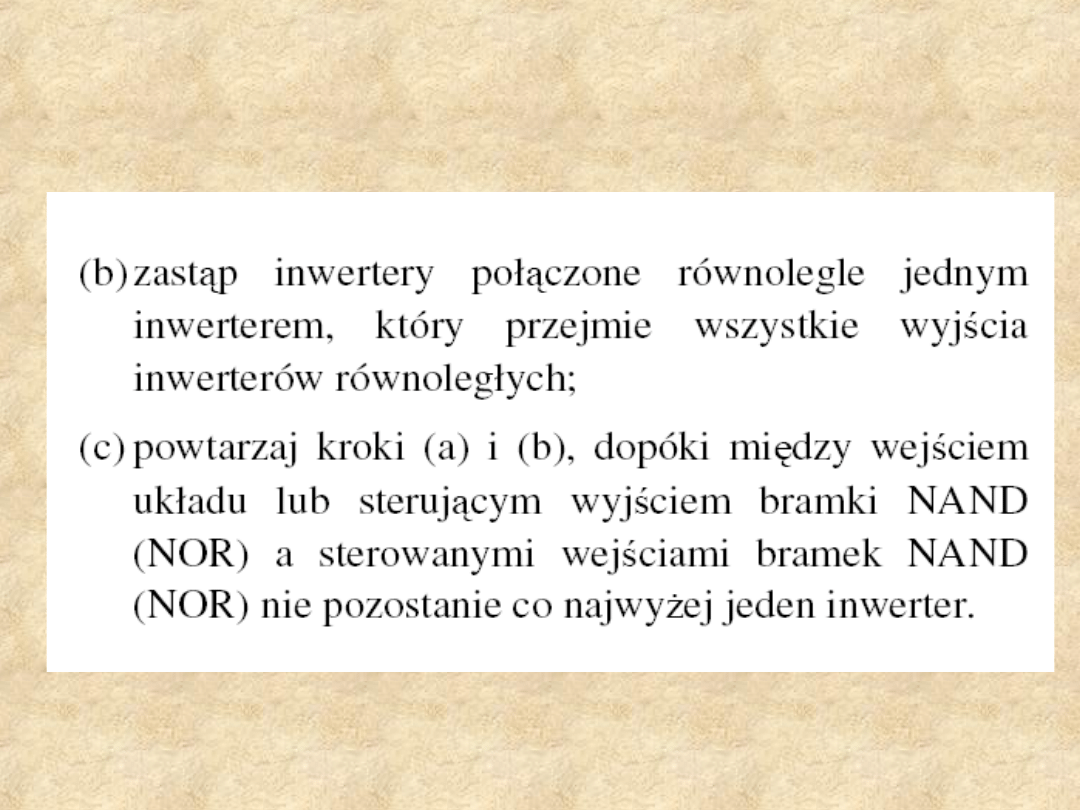

Krok 3: Nie zmieniając funkcji

logicznej:

Reguła

przepychani

a inwertera

przez węzeł

układu

44

Procedura konwersji AND-

OR

do NAND (NOR)

45

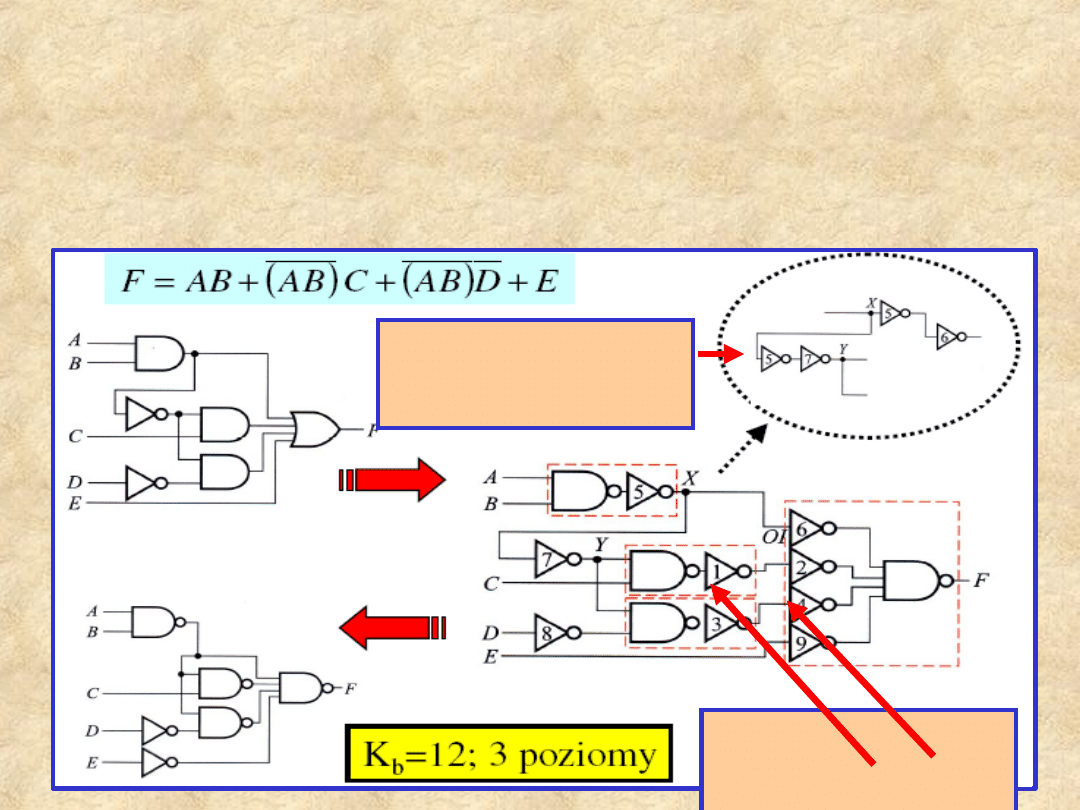

Przykład 1.

Zrealizować funkcję za pomocą

układu zawierającego tylko

bramki NAND.

Usuwamy pary

inwerterów (1,2) i

(3,4)

Inwerter 5 zostaje

przepchnięty za

węzeł x

46

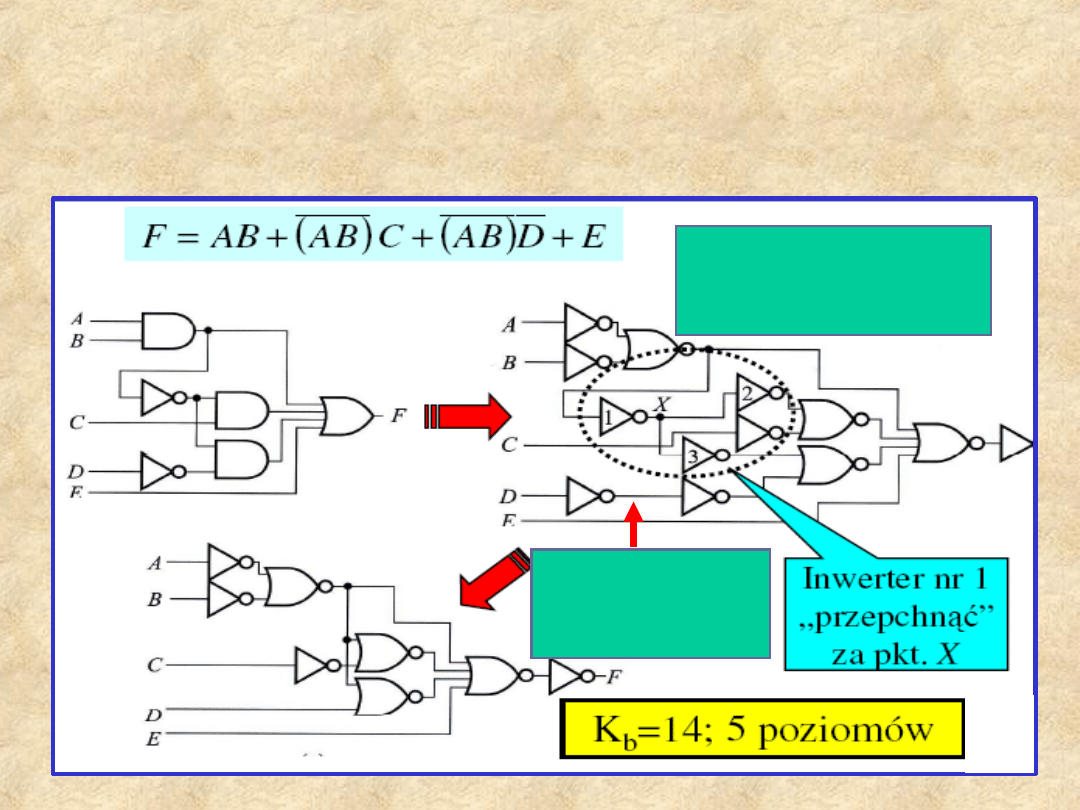

Przykład 2.

Zrealizować funkcję za pomocą

układu zawierającego tylko

bramki NOR.

Usuwamy pary

inwerterów (1,2) i

(1,3).

Usuwamy pary

inwerterów na

wejściu D

47

Procedura konwersji AND

(OR)

do NAND (NOR)

1. W

pierwszym

przykładzie

koszt wejść

bramkowych

zaimplemento

wanego układu

wynosi

12

, a w

drugim -14.

2. W pierwszym przykładzie

maksymalna liczba

szeregowo połączonych

bramek wynosi

3 bramki

,

natomiast w drugim- aż 5.

Z tego wynika że maksymalne

opóźnienie

między zmianą sygnału

na wejściu a zmianą na wyjściu jest

najprawdopodobniej

większe

.

implementacja z użyciem

bramek NAND jest mniej

kosztowna

48

Procedura projektowania

układu

Ręczna analiza

układu

logicznego

Symulacja

komputerowa

Weryfikacja funkcjonalna

układu

Weryfikacja ma wykazać, czy końcowy układ jest

zgodny z początkowej specyfikacją.

Weryfikacja ma za zadanie zapobiegać wytwarzaniu i

praktycznemu stosowaniu błędnie zaprojektowanych

układów.

49

Dziękuję

za uwagę

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

Wyszukiwarka

Podobne podstrony:

Wyk ECiUL#1 2013

Wyk ECiUL#5 2013

Wyk ECiUL#3 2013

Wyk ECiUL#1 2013

Wyk ECiUL#9S 2013

Wyk ECiUL#9S 2013

TEMATY NA ZAL WYK Z MASZYN 2013, Mazynoznastwo

de Rosset, wyk inauguracyjny 2013 14

4 Wyk PNOP 2013 14 innowacje dz Nieznany (2)

TEMATY NA ZAL WYK MASZYNOZN 2013 14, STUDIA PŁ, TECHNOLOGIA ŻYWNOŚCI I ŻYWIENIA CZŁOWIEKA, ROK II, S

TEMATY NA ZAL WYK Z MASZYN 2013, Mazynoznastwo

fizjo - wyk+éady, Leśnictwo UP POZNAŃ 2013, Fizjologia roślin drzewiastych

Genetyka wyk éad 2( 02 2013

genetyka wyk éad 1 ! 02 2013 MAM

MiBM Reg. i wyk. ćw. Lab 2013 stacjonarne

Wyk. syllabus 2010 analiza ekonomiczna SSE I, Ekonomia UWr WPAIE 2010-2013, Semestr II, Analiza Ekon

materia éy z wyk é VIII ch fiz 2013

więcej podobnych podstron