Pamięci RAM i ROM

R. J. Baker, "CMOS Circuit Design, Layout, and Simulation",

Wiley-IEEE Press, 2 wyd. 2007

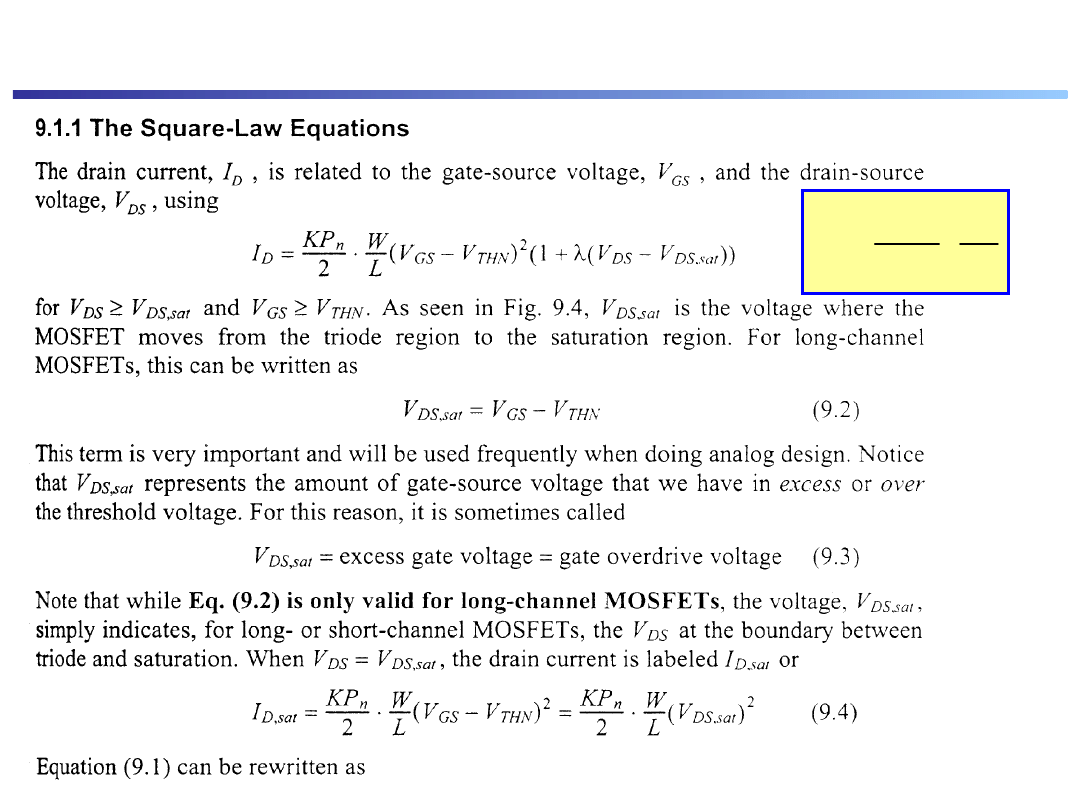

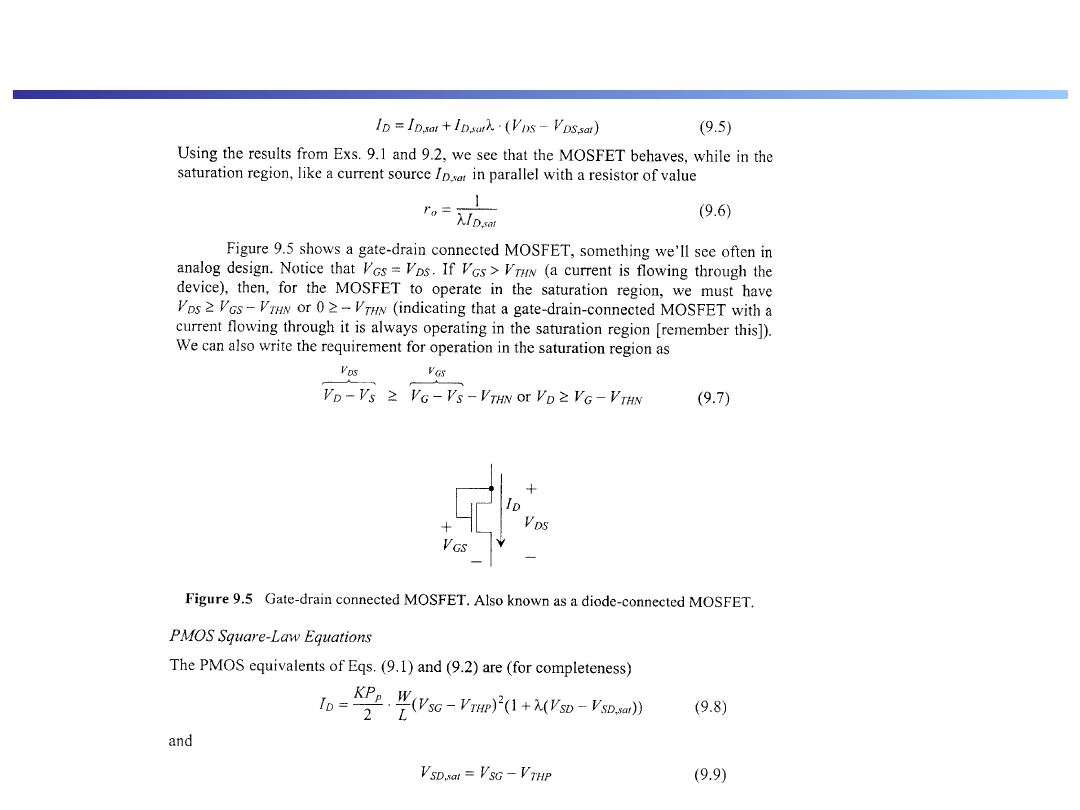

Tranzystor MOS z długim kanałem – kwadratowa aproksymacja charakterystyk

MOSFET_square_law_eq_1

L

W

KP

n

2

MOSFET_square_law_eq_2

Tranzystor MOS z długim kanałem – kwadratowa aproksymacja charakterystyk

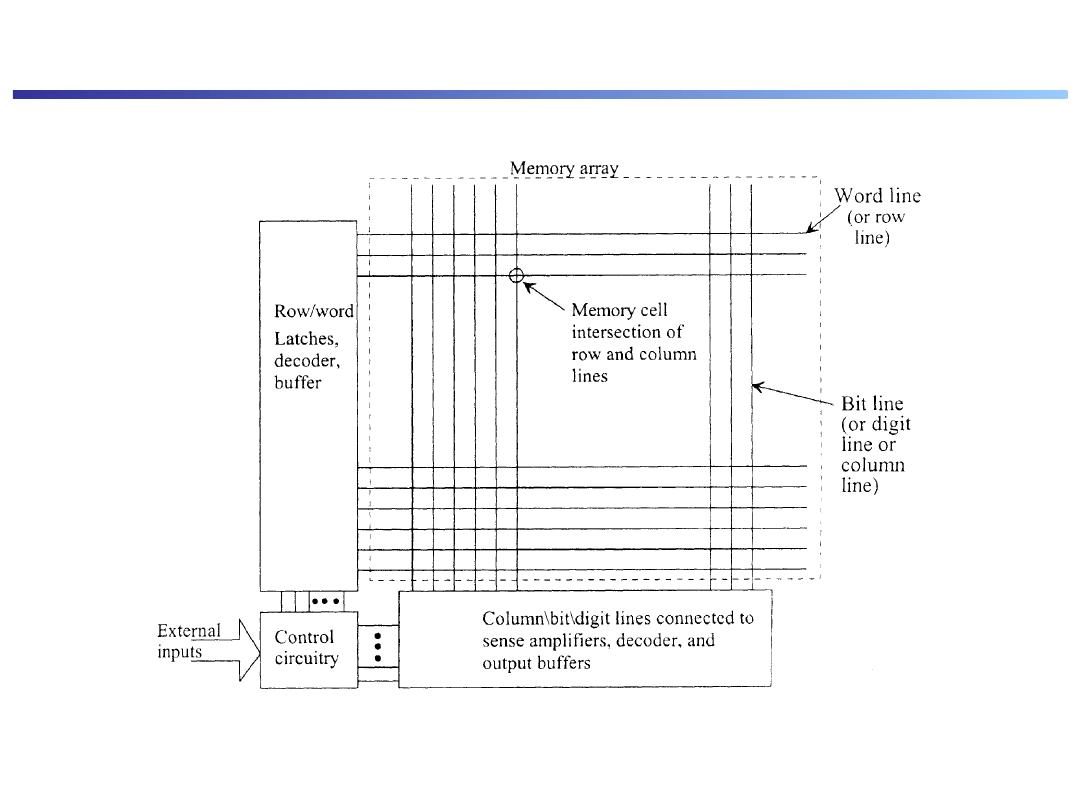

Pamięć RAM – schemat blokowy

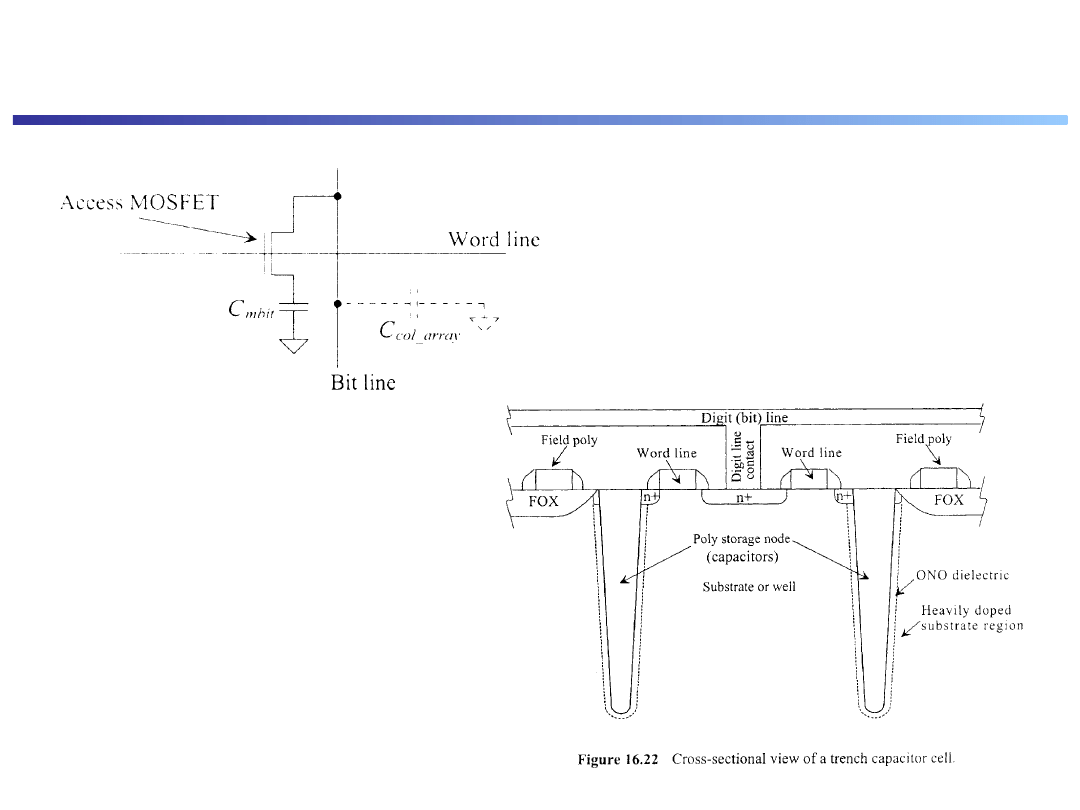

Komórka dynamicznej pamięci (DRAM)

z jednym tranzystorem i jednym kondensatorem

Schemat

Przekrój komórki z kondensatorem

wykonanym na ścianach wgłębienia

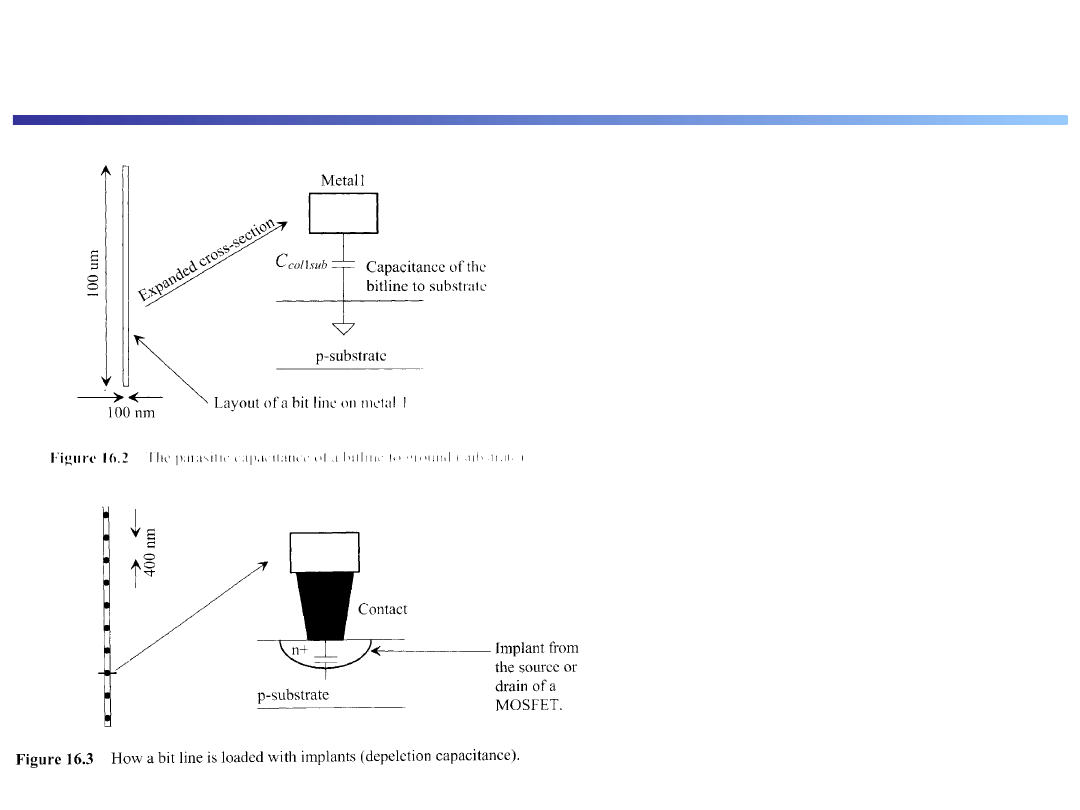

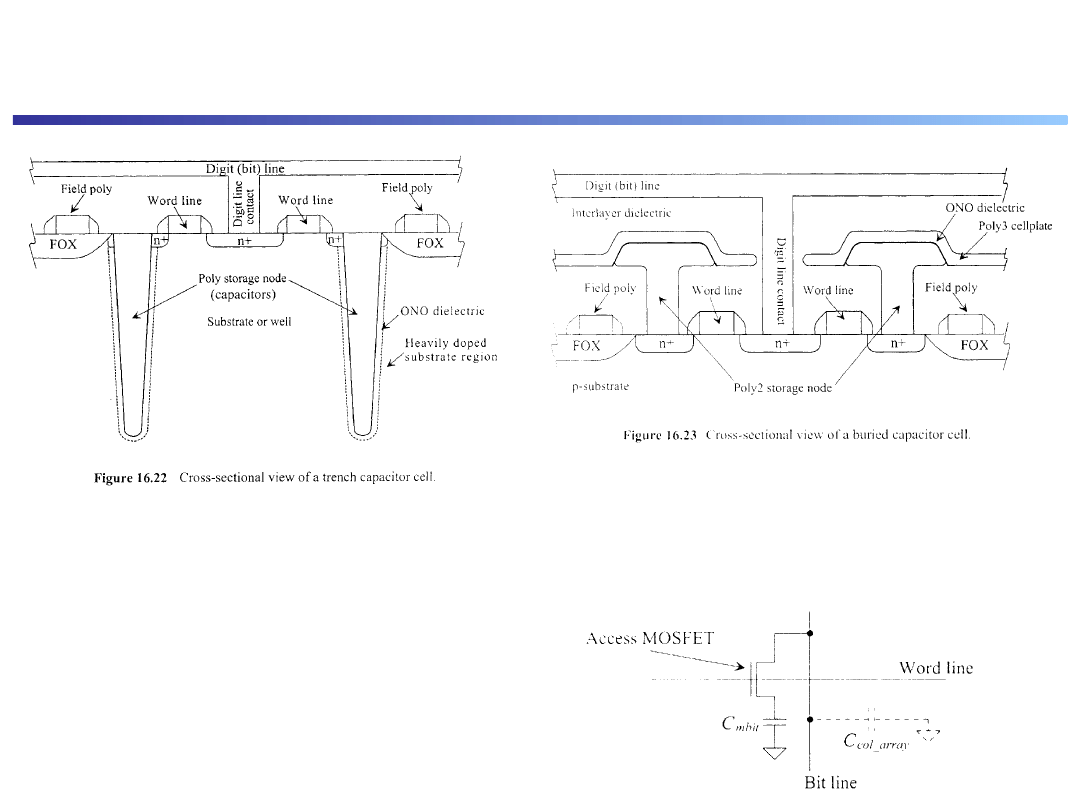

Pasożytnicze pojemności

linii bitu w DRAM

Metalowa ścieżka linii bitu położona na SiO

2

tworzy pasożytniczą pojemność do podłoża.

Pojemność ta łączy się równolegle do

kondensatora komórki pamięci, kiedy

tranzystor dostępu do komórki

przewodzi, np. w trakcie odczytu. Niech

pojemność jednostkowa będzie:

C

1sub

=100 aF/µm

2

.

C

col1sub

= Powierzchnia · C

1sub

C

col1sub

= (0,1)(100)(100 aF) = 1 fF

To niedużo, ale mamy jeszcze pojemności

złączowe związane z implantowanymi drenami

rozmieszczonymi co 400 nm:

Przykład dla technologii 50 nm:

C

col

= liczba_linii_słowa ·

pojemność_drenu + C

col1sub

C

col

= 100 fF

- pojemność pasożytnicza jest

-WIĘKSZA od pojemności

kondensatora komórki pamięci C

mbit

= 20 fF.

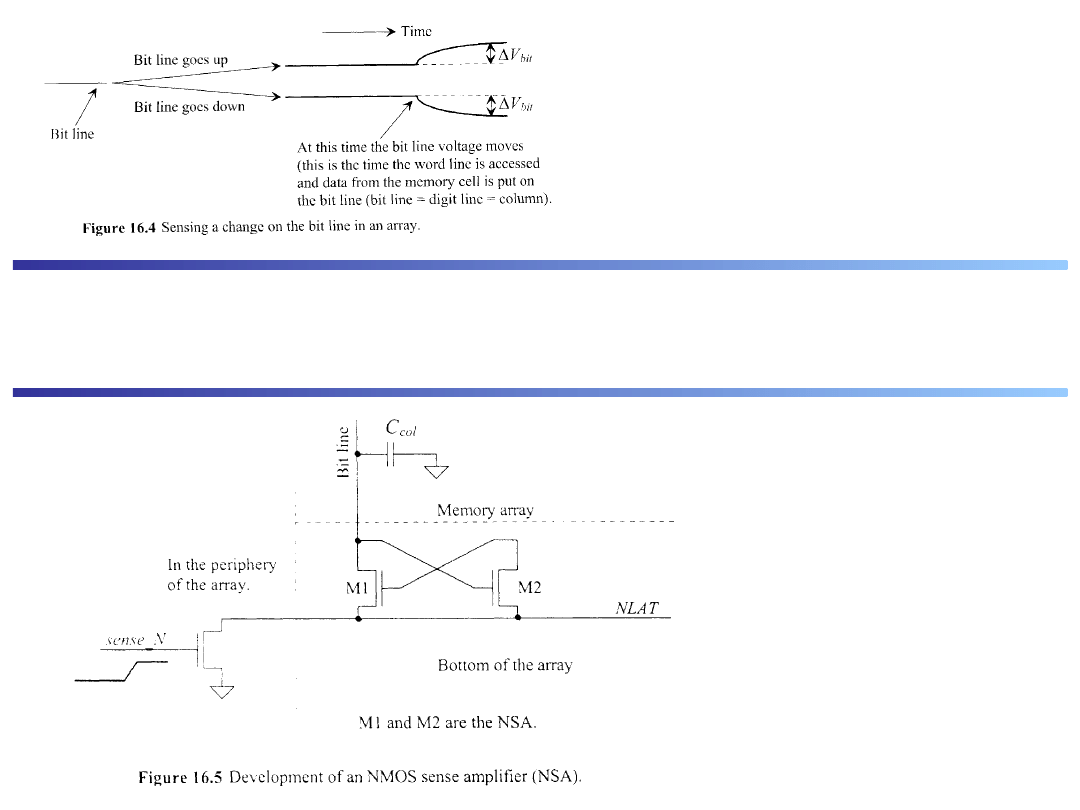

Konieczny wzmacniacz odczytu stanu naładowania

kondensatora komórki pamięci dynamicznej!

W tym momencie wybierana jest linia słowa

i ładunek kondensatora komórki pamięci

(zapamiętana dana) jest umieszczana na linii bitu.

Duża wartość pojemności pasożytniczej linii bitu

powoduje, że skok napięcia jest niewielki.

Układ z dodatnim sprzężeniem zwrotnym

(„latch” – zatrzask) użyty jako wzmacniacz

odczytu w linii bitu.

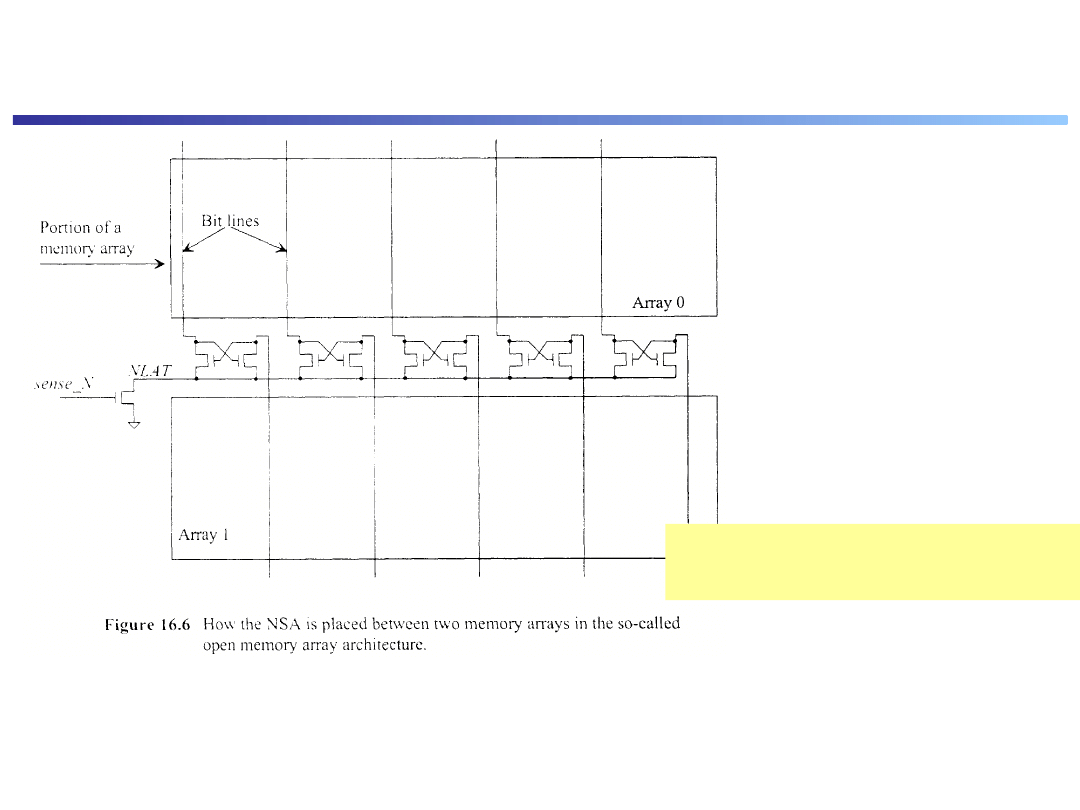

W celu niezawodnego odczytu stanu komórki DRAM

wygodnie jest użyć „architektury otwartej tablicy”

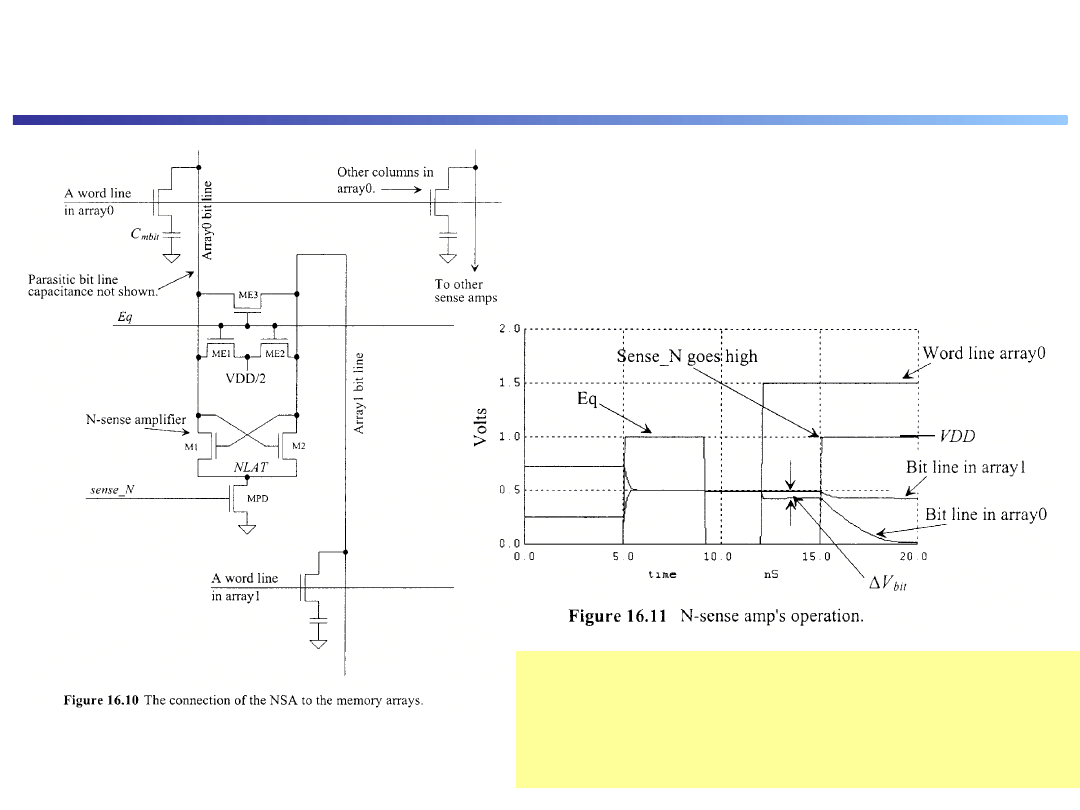

NSA – nMOS Sense Amplifier

- wzmacniacz odczytu z nMOS

Stan jednej linii bitu podłączonej do NSA jest wzmacniany,

a stan drugiej linii bitu jest wykorzystywany jako stan odniesienia.

Aby tak mogło być układ trzeba rozbudować o blok wyrównywacza stanów.

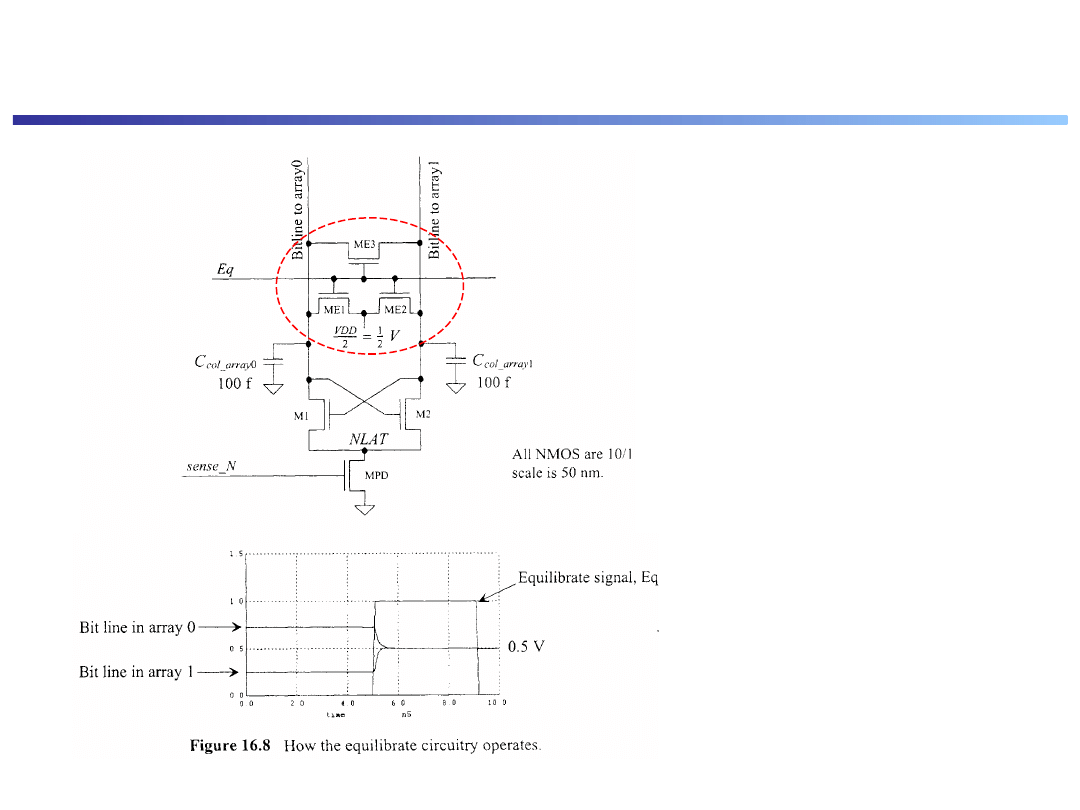

Wyrównywanie stanów przed operacją odczytu

ze wzmacniaczem odczytu nMOS

Przed uaktywnieniem linii słowa napięcia linii bitów

tablicy 0 i tablicy 1 są wyrównywane do wartości VDD/2,

przez uaktywnienie linii Eq.

Wszystkie tranzystory w technologii 50 nm,

10/1 (to jest W = 10·50 nm / L = 1·50 nm)

Napięcie zasilania VDD = 1 V.

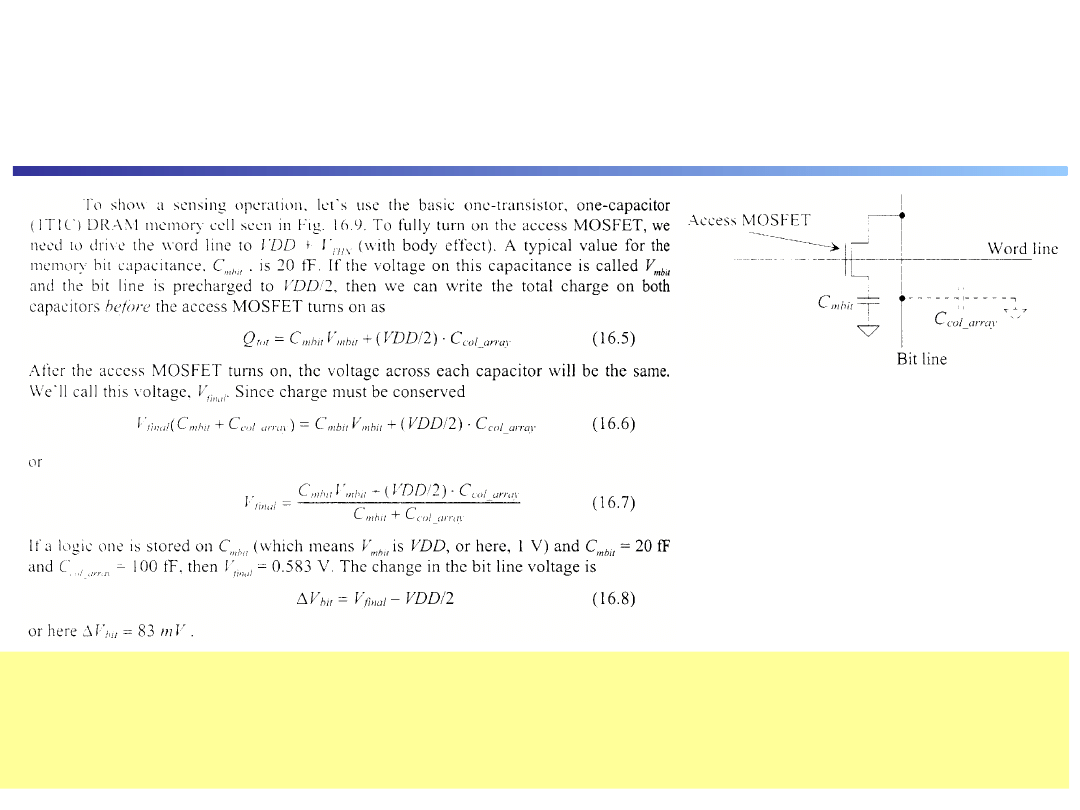

Odczyt - po wyrównaniu stanów linii bitów i po

uaktywnieniu linii słowa, to jest po wprowadzeniu w

stan przewodzenia tranzystora dostępu komórki.

Po wyrównaniu stanów linii bitów uaktywniana jest linia słowa, to jest tranzystor dostępu komórki jest

wprowadzny w stan przewodzenia. Wskutek dołączenia pasożytniczej pojemności linii bitów różnica

napięć pomiędzy linią odczytywaną, a linią odniesienia jest niewielka - tylko 83 mV

w naszym przykładzie technologii 50 nm.

Sytuacja ulega radykalnej zmianie po uaktywnieniu linii sense_N.

Odczyt - wzmocnienie po uaktywnieniu linii

sense_N

Odczyt „0” z komórki w tablicy 0:

Po uaktywnieniu linii sense_N wzmacniacz

z dodatnim sprzężeniem zwrotnym powoduje,

że różnica napięć wzrasta niemal do wartości VDD/2.

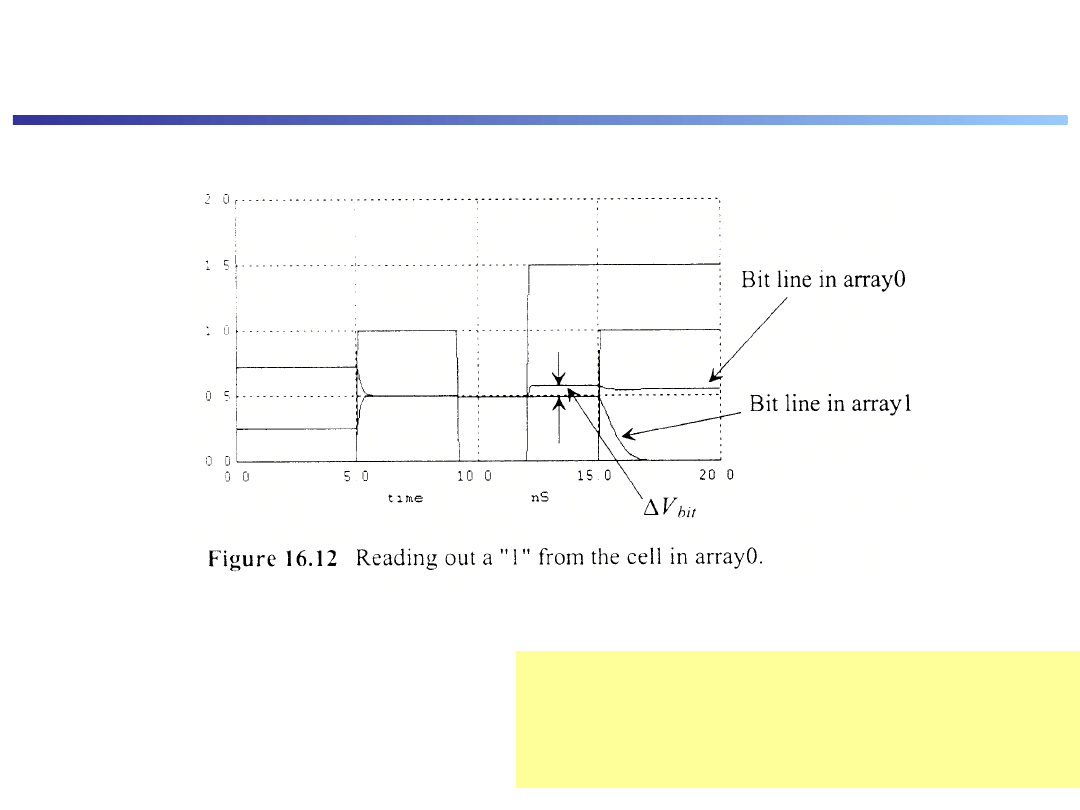

Odczyt „1” z komórki w tablicy 0

Odczyt „1” z komórki w tablicy 0:

Po uaktywnieniu linii sense_N wzmacniacz

z dodatnim sprzężeniem zwrotnym powoduje,

że różnica napięć wzrasta niemal do wartości VDD/2.

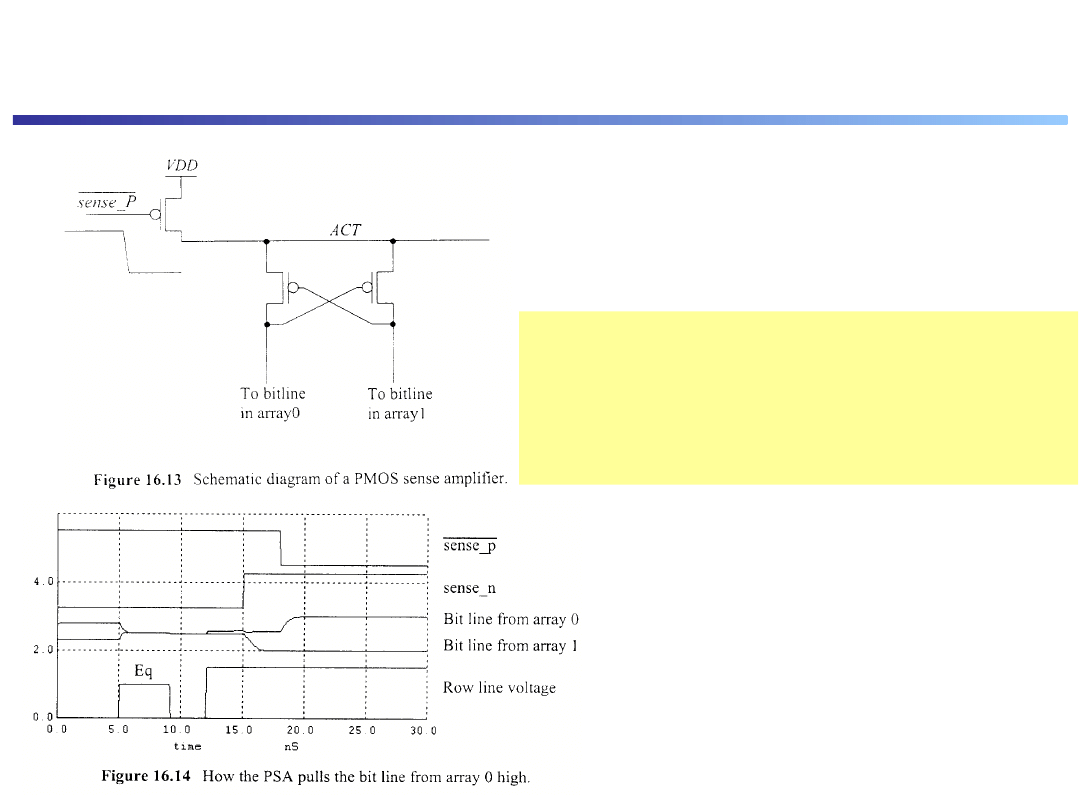

Dwa wzmacniacze odczytu : NSA – z tranzystorami

nMOS oraz PSA – z tranzystorami pMOS.

Różnicę napięć pomiędzy odczytywaną

linią bitów a linią odniesienia można

wzmocnić do wartości niemal VDD

przez zastosowanie dodatkowego

wzmacniacza – z tranzystorami pMOS.

Odświeżanie zawartości komórki DRAM

Odświeżanie zawartości komórki DRAM odbywa się przez

uaktywnienie

sense_n oraz sense_p

przy przewodzącym tranzystorze dostępu.

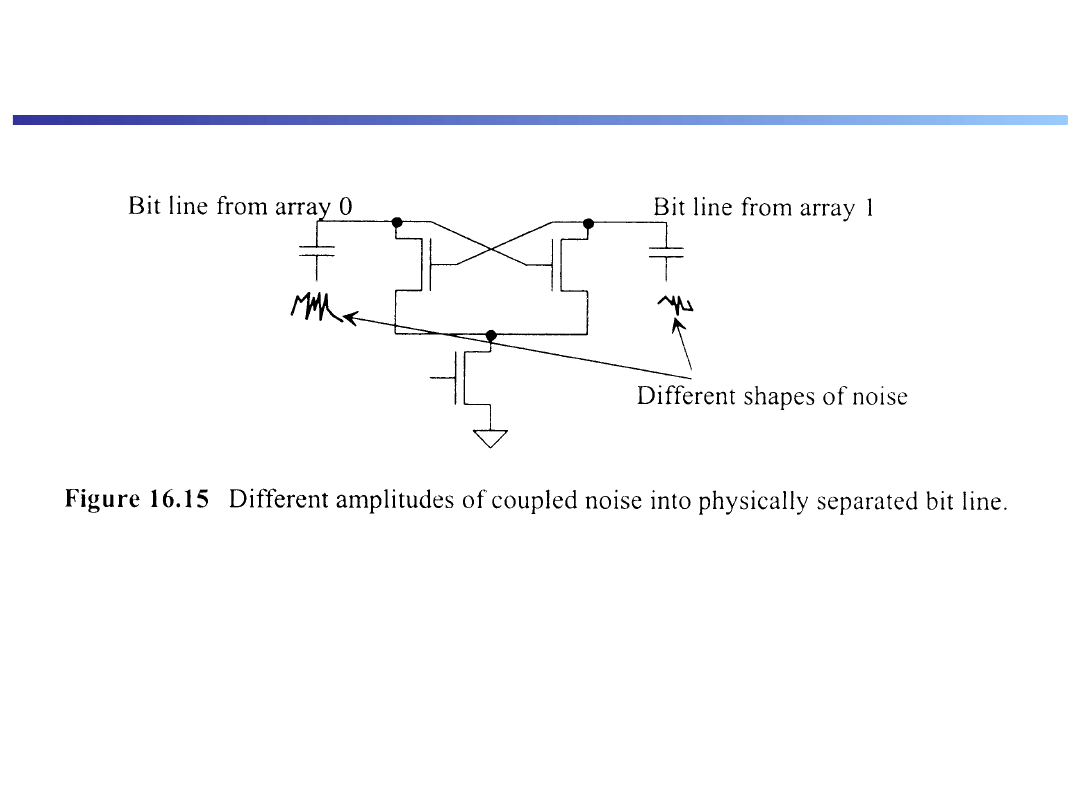

W architekturze „otwartej tablicy” porównywane w trakcie odczytu linie bitów

są fizycznie oddalone od siebie – jedna w tablicy 0, druga w tablicy 1.

Jest prawdopodobne, że w liniach bitów zaindukują się różne szumy,

co doprowadzi do błędów odczytu.

Szumy w „architekturze otwartej tablicy”

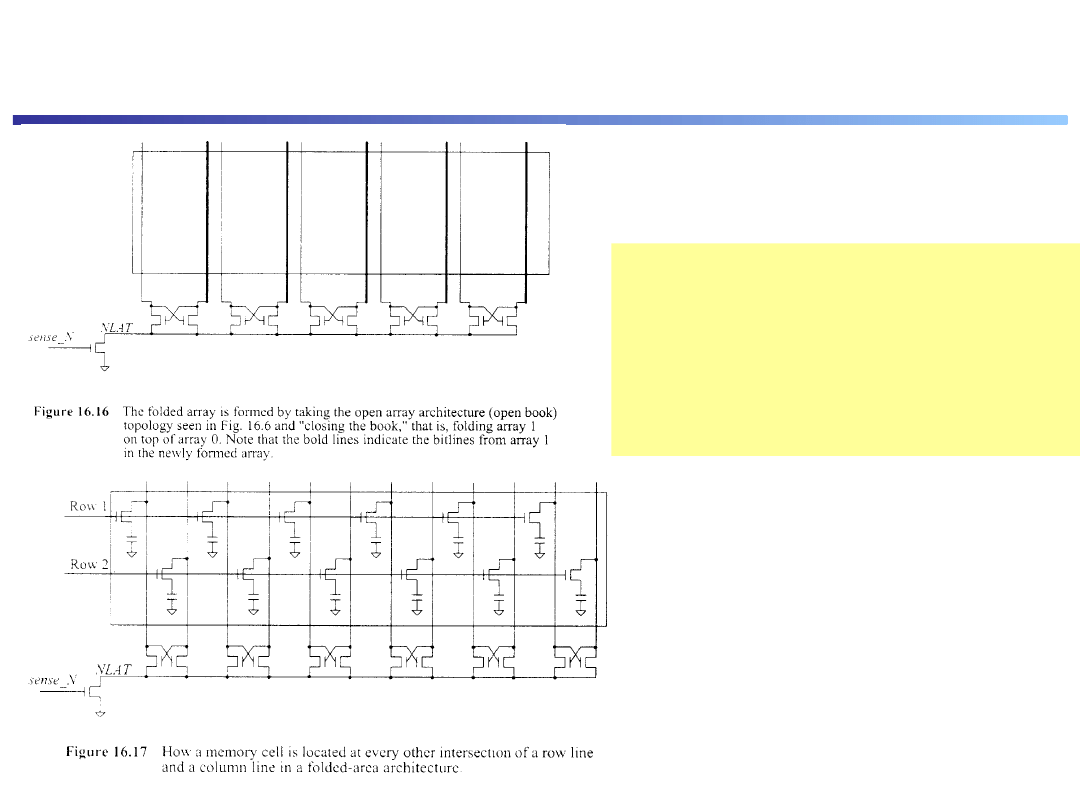

Zmniejszenie szumów odczytu przez zastosowanie

„architektury tablicy złożonej”

W architekturze „ tablicy złożonej”

porównywane w trakcie odczytu linie bitów

są fizycznie zbliżone do siebie

– tablica 0 i w tablica 1 przeplatają się.

Jest prawdopodobne, że w liniach bitów

zaindukują się podobne szumy,

co zmniejszy prawdopodobieństwo

błędu odczytu.

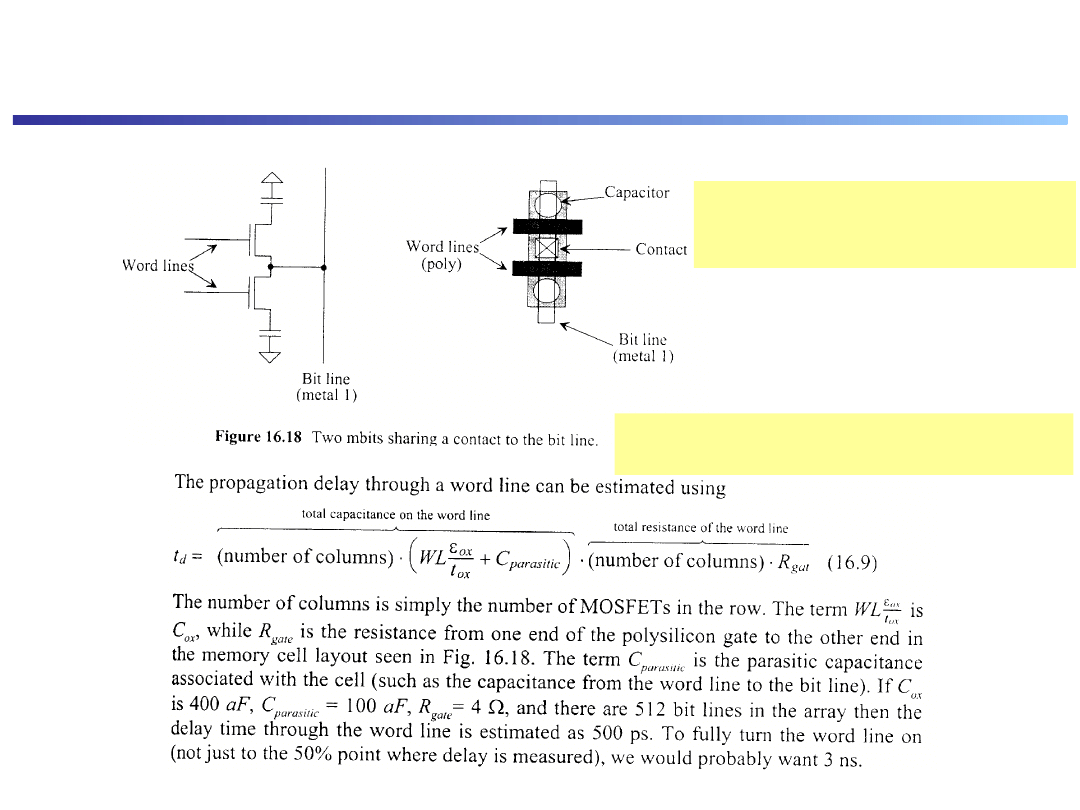

Rozkład elementów komórki DRAM

Oszczędzamy miejsce przez

użycie wspólnego kontaktu drenu

dla dwóch komórek.

Opóźnienie związane z propagacją

sygnału wzdłuż polikrzemowej linii słowa.

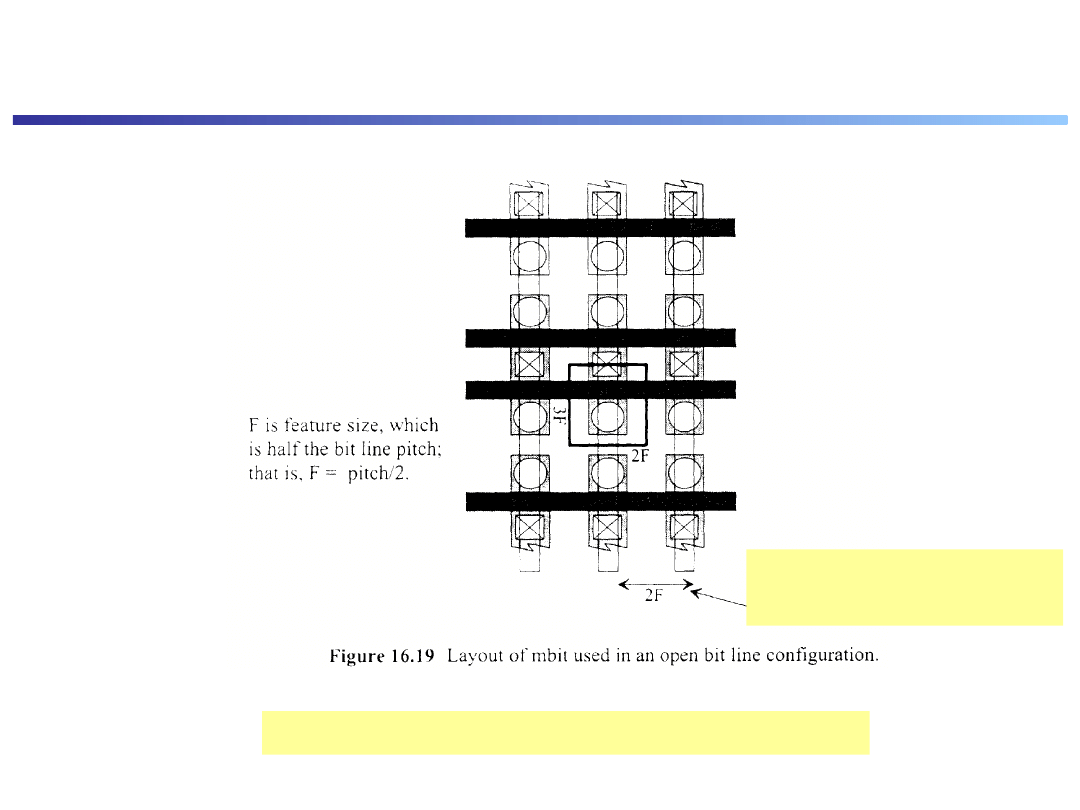

Rozkład elementów komórki DRAM w „architekturze

otwartej tablicy”

2F – odstęp pomiędzy

liniami bitu

Komórka pamięci zajmuje powierzchnię 6F

2

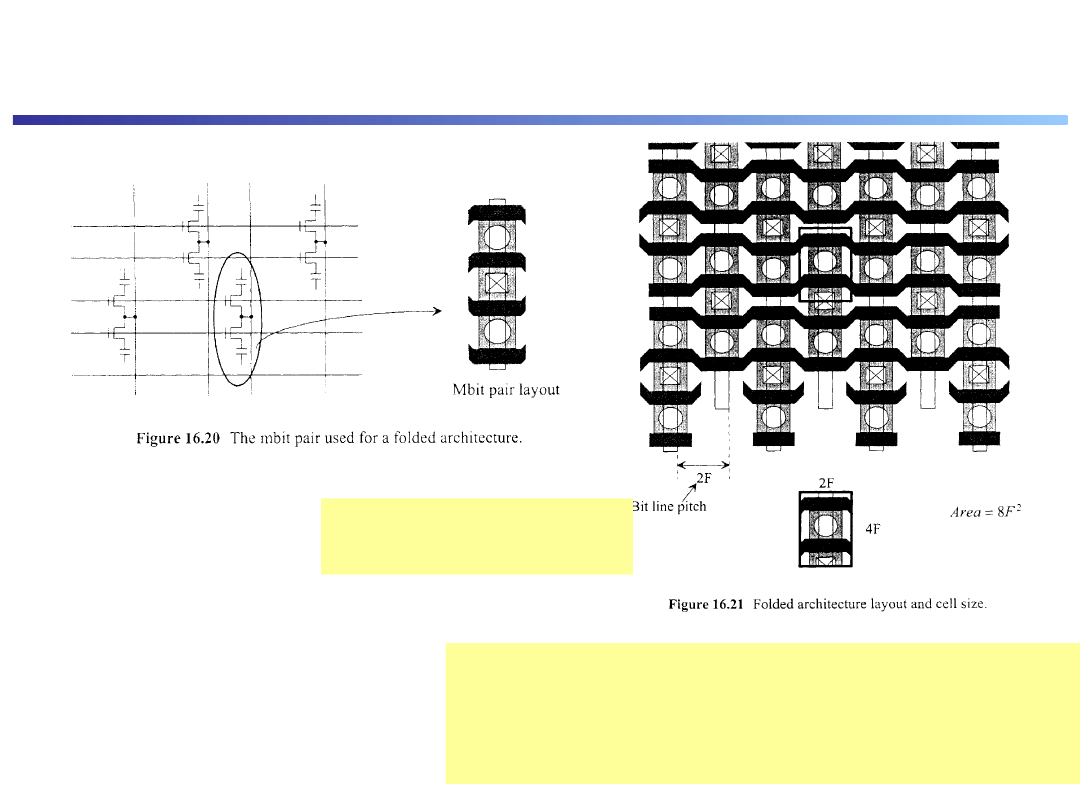

Rozkład elementów komórki DRAM w „architekturze

złożonej tablicy”

2F – odstęp pomiędzy

liniami bitu

Komórka pamięci zajmuje powierzchnię 8F

2

-więcej niż w „architekturze otwartej tablicy

- w konsekwencji większe też jest opóźnienie

propagacji sygnału wzdłuż linii słowa

Konstrukcje kondensatorów w komórkach DRAM

Przekrój komórki z kondensatorem

wykonanym w jednej z warstw metalizacji

Schemat

Przekrój komórki z kondensatorem

wykonanym na ścianach wgłębienia

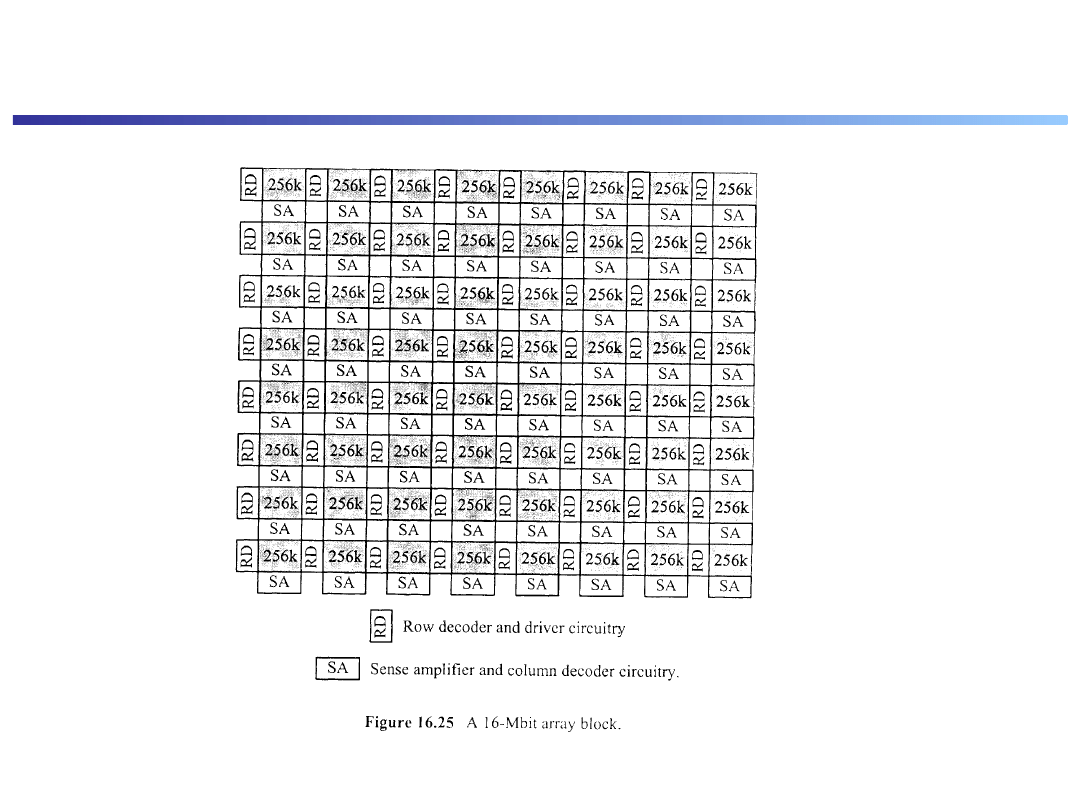

Rozkład bloków pamięci DRAM w układzie scalonym

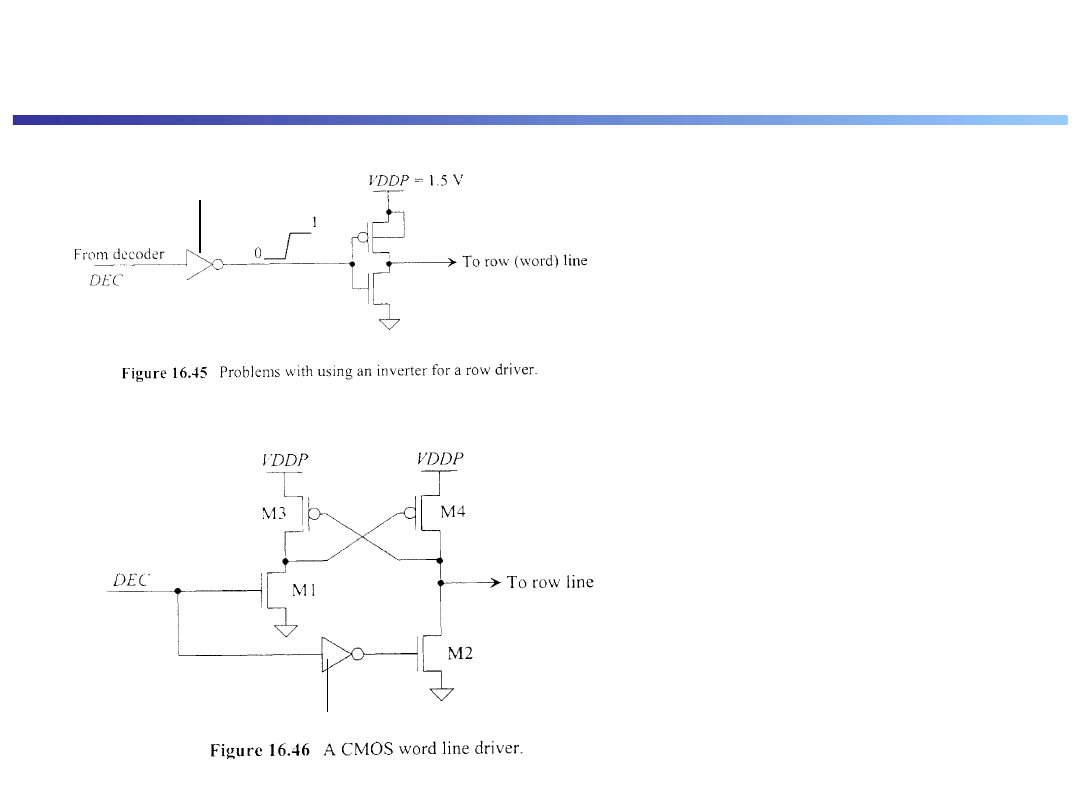

Pamięci DRAM – współpraca układów o różnych

napięciach zasilania

VDD = 1V

VDD = 1V

Przy różnych napięciach zasilania,

VDDP > VDD

stan wysoki na wyjściu pierwszego

inwertera nie zamknie tranzystora

pMOS drugiego inwertera

Rozwiązaniem jest stosowanie

wzmacniacza z dodatnim

sprzężeniem zwrotnym

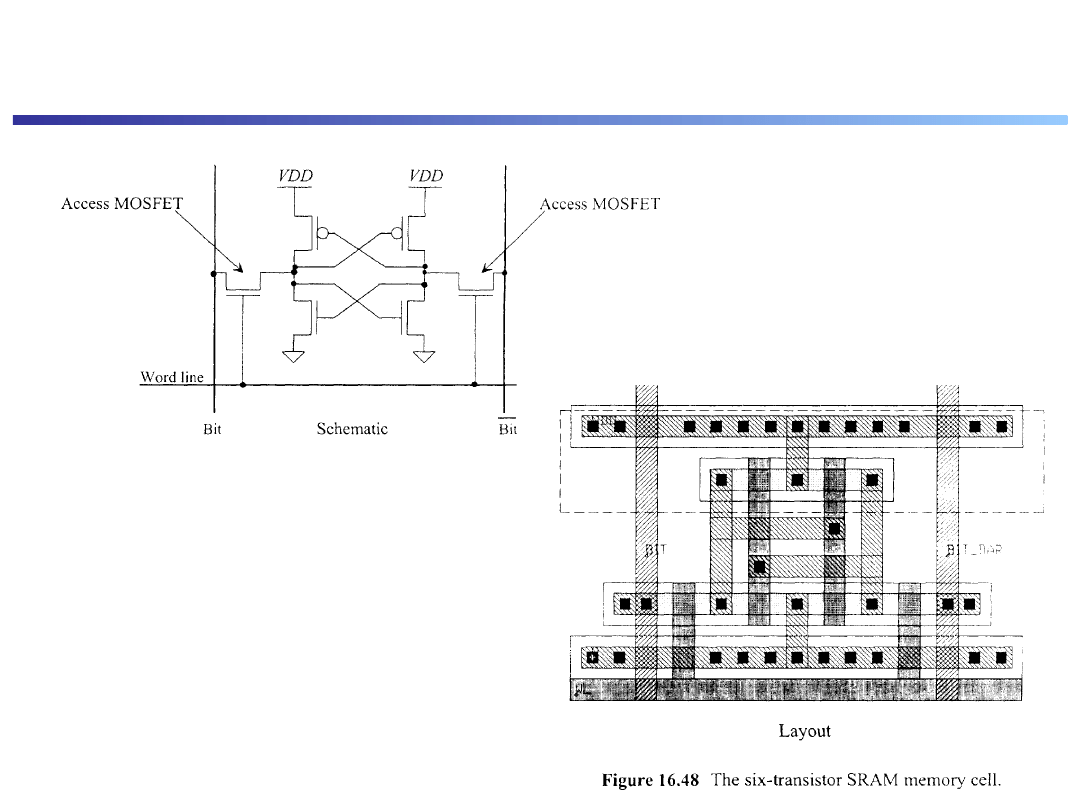

Komórka pamięci statycznej (SRAM) – z 6

tranzystorami

Zajmuje dużo miejsca

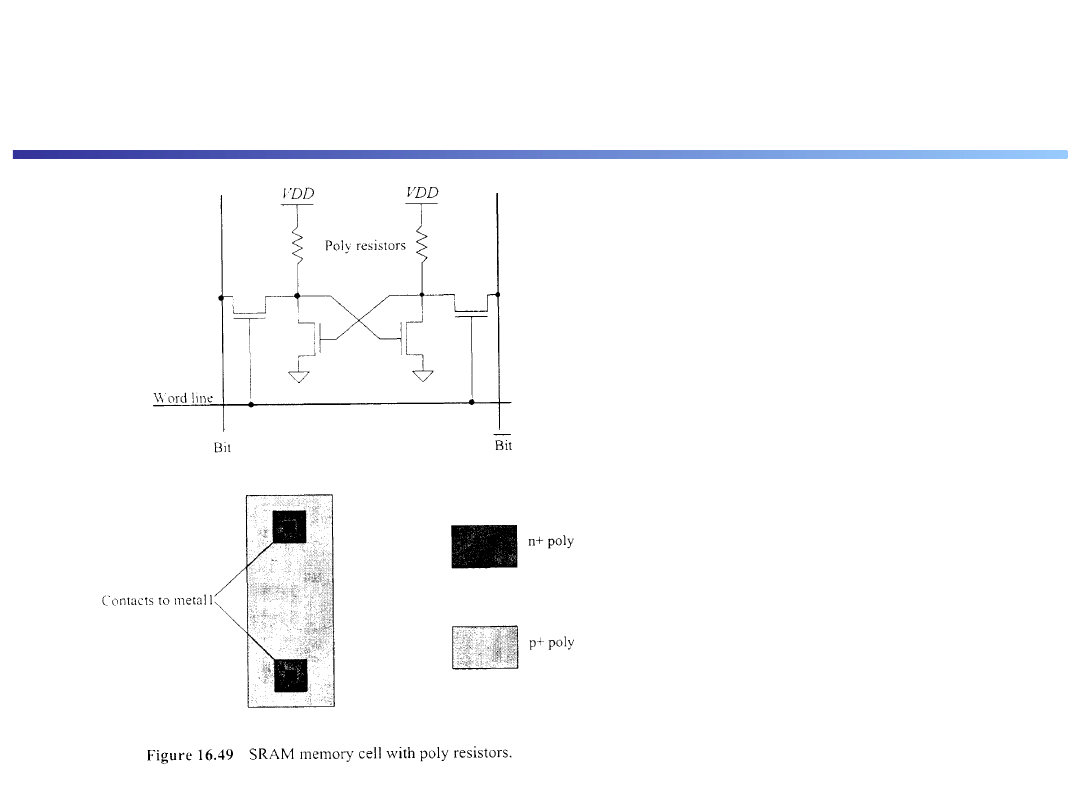

Komórka pamięci statycznej (SRAM) – z 2

tranzystorami i 2 rezystorami

Rezystory wykonywane w warstwie

krzemu polikrystalicznego

(typowo 10 MOhm).

Komórka mniejsza niż SRAM z 6 MOS.

Komórka pobiera statycznie moc.

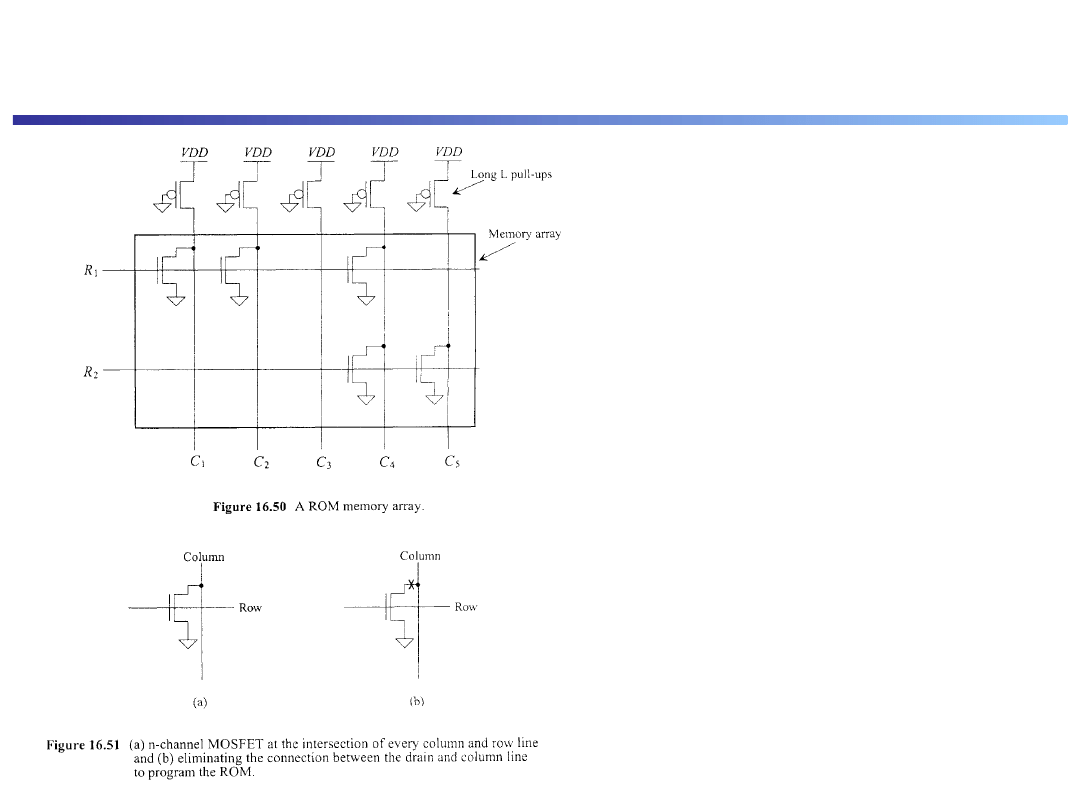

Pamięci tylko do odczytu (ROM)

Chip ROM zaprogramowany

przy pomocy maski.

Programowalny chip ROM

– przepalane połączenia.

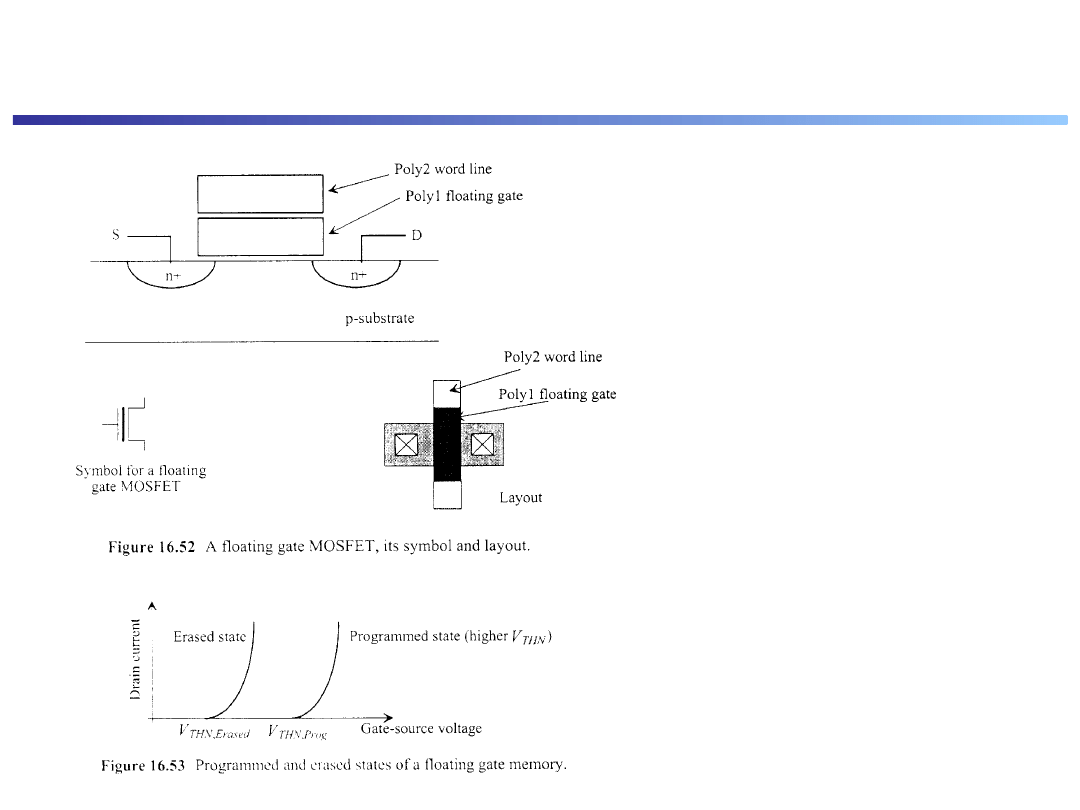

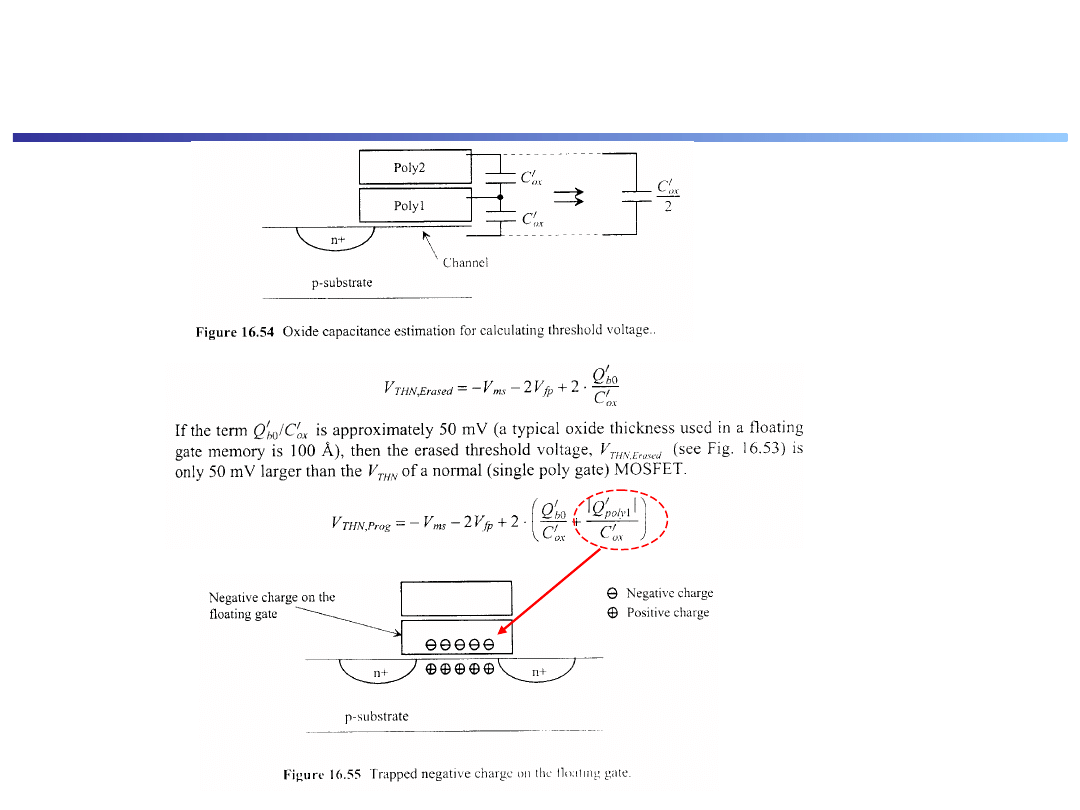

Pamięć nieulotna z pływającą bramką

Umieszczenie ładunku

w pływającej bramce

prowadzi do zmiany napięcia

progowego

– przesunięcia charakterystyk

Pamięć nieulotna z pływającą

bramką – napięcie progowe

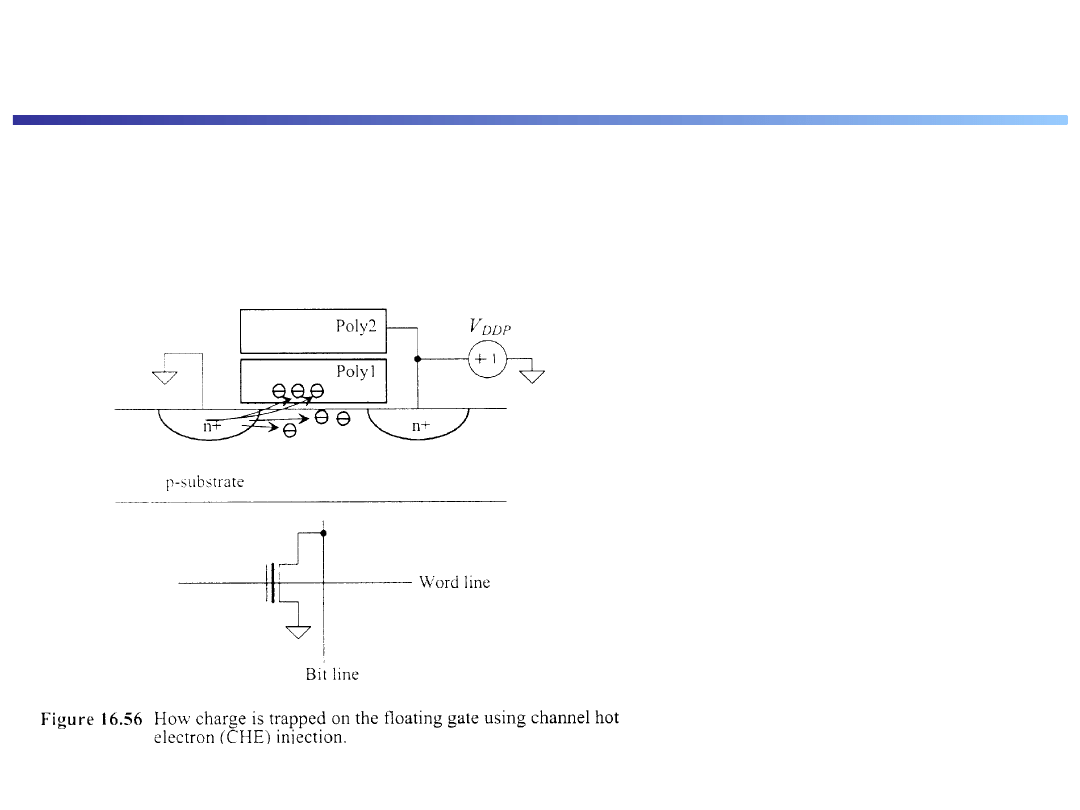

Reprogramowalne pamięci ROM (erasable

programable – EPROM)

Zapis – przez umieszczenie ładunku elektronów w pływającej bramce.

Bramka i dren polaryzowane są wysokim napięciem. Elektrony uzyskują

w polu elektrycznym wysoką energię. Stają się „gorące”. Elektrony o

dostatecznie wysokiej energii pokonują barierę energetyczną tlenku bramki i

są wstrzykiwane do polikrzemu pływającej bramki.

Kasowanie – elektronom z pływającej bramki

dostarczana jest energia przez oświetlenie

ultrafioletem. Uzyskawszy odpowiednią energię

elektrony mogą opuścić polikrzem pływającej bramki.

Proces kasowania niewygodny – przyrządy zastąpione

zostały przez „flash”.

flash_1

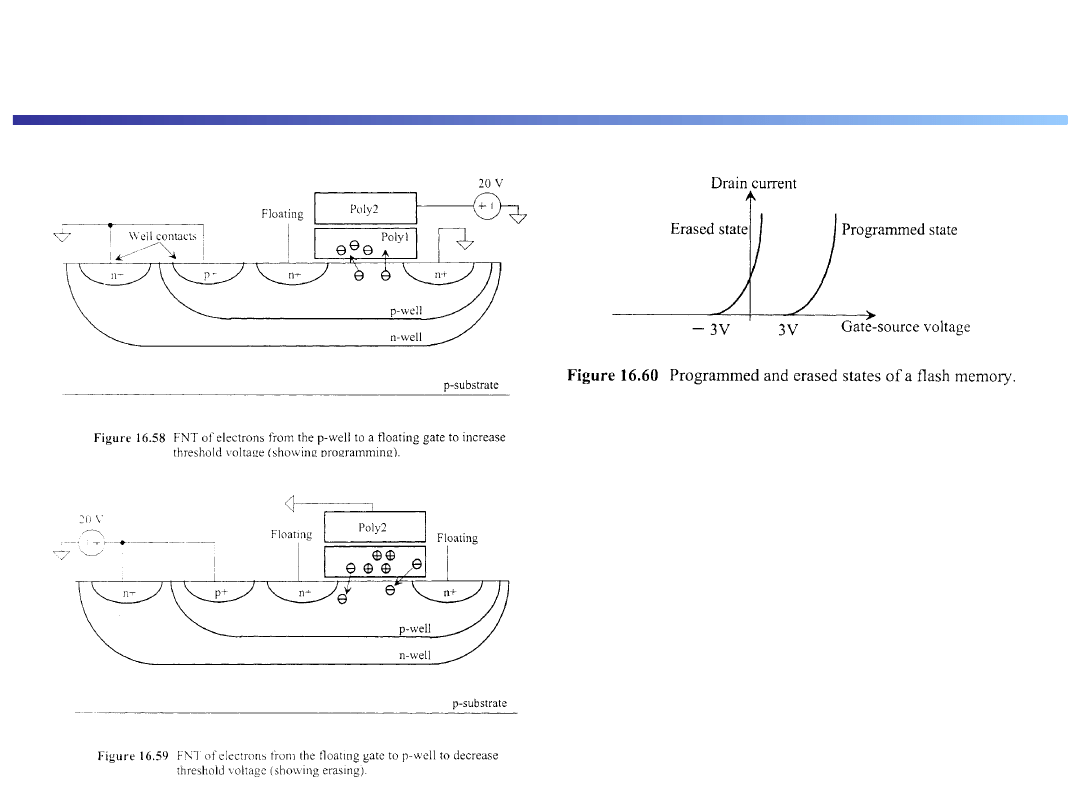

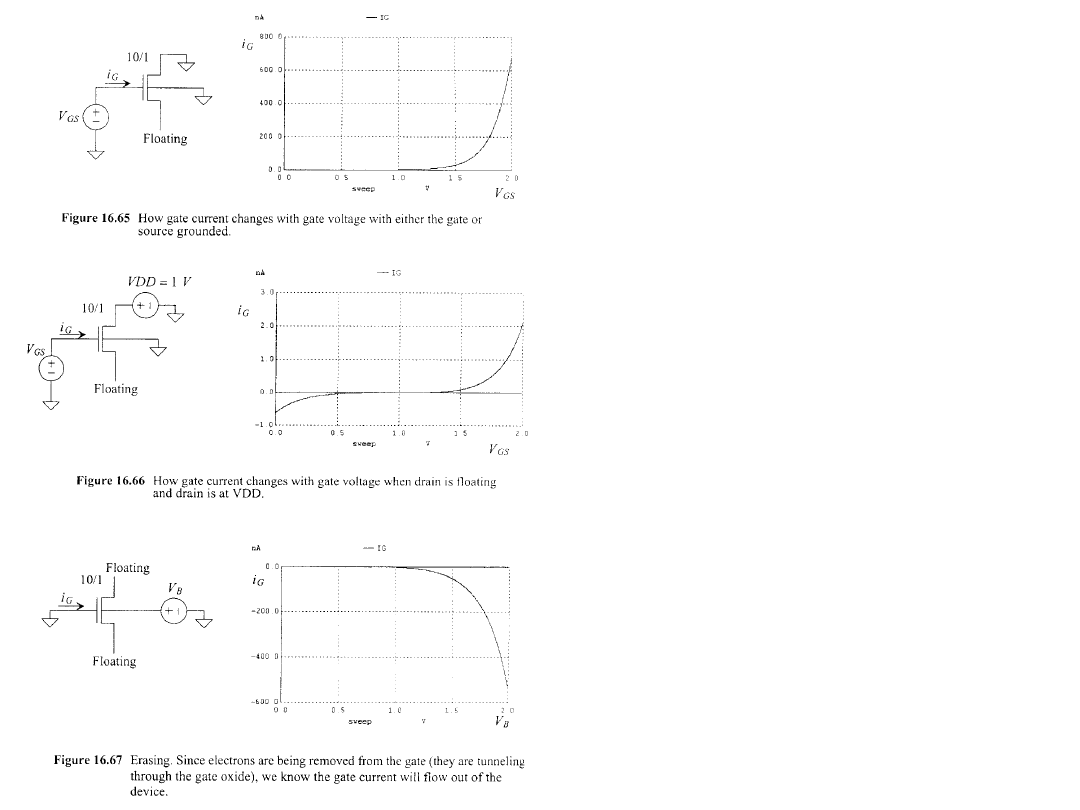

Pamięci nieulotne „flash”

Zapis i kasowanie, to jest umieszczanie i usuwanie

elektronów w polikrzemie pływającej bramki,

w wyniku tunelowania Fowlera-Nordheima.

flash_2

Pamięci nieulotne „flash”

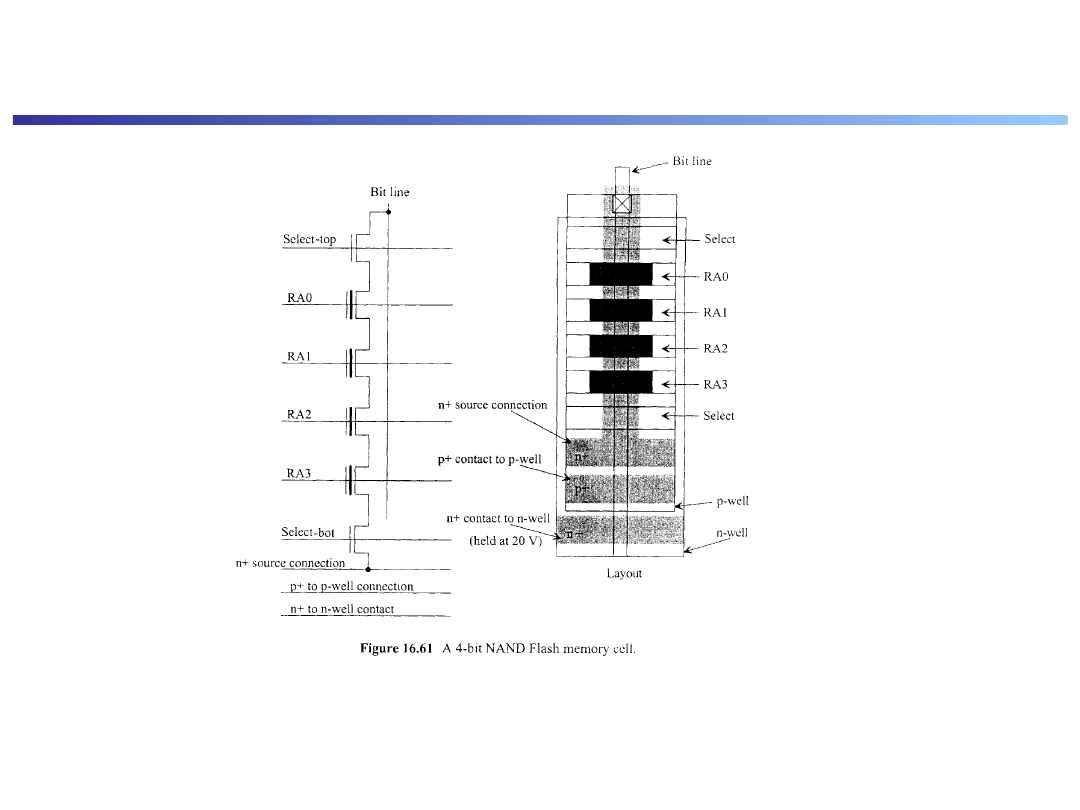

4-bitowa komórka NAND pamięci „flash”

Pamięci nieulotne „flash”

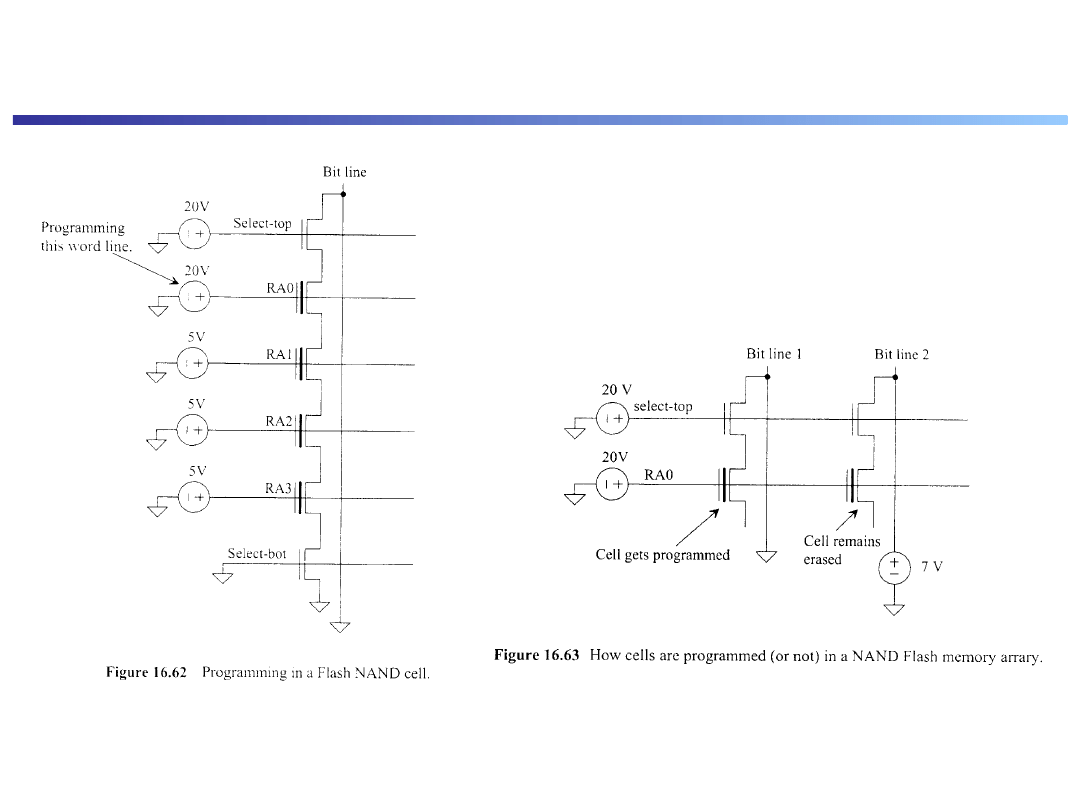

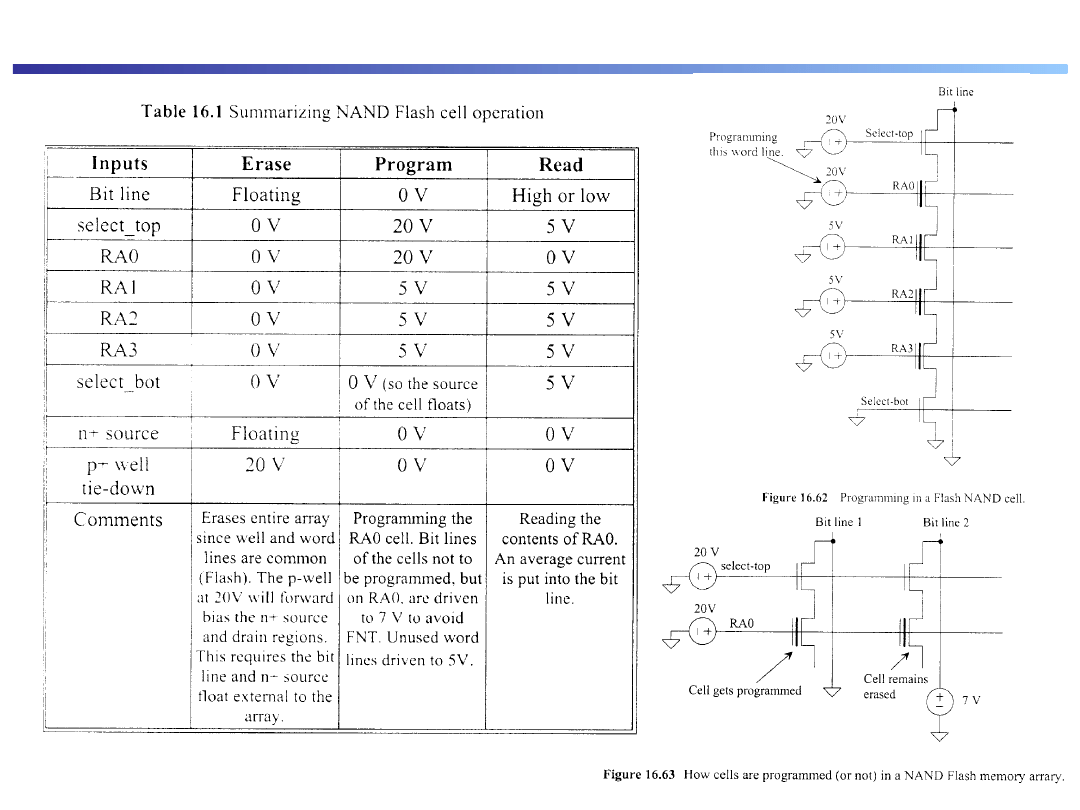

flash_3

Programowanie

Pamięci nieulotne „flash”

flash_4

Pamięci nieulotne „flash”

– charakterystyki tranzystorów

Document Outline

- Pamięci RAM i ROM

- MOSFET_square_law_eq_1

- MOSFET_square_law_eq_2

- Pamięć RAM – schemat blokowy

- Komórka dynamicznej pamięci (DRAM) z jednym tranzystorem i jednym kondensatorem

- Pasożytnicze pojemności linii bitu w DRAM

- Konieczny wzmacniacz odczytu stanu naładowania kondensatora komórki pamięci dynamicznej!

- W celu niezawodnego odczytu stanu komórki DRAM wygodnie jest użyć „architektury otwartej tablicy”

- Wyrównywanie stanów przed operacją odczytu ze wzmacniaczem odczytu nMOS

- Odczyt - po wyrównaniu stanów linii bitów i po uaktywnieniu linii słowa, to jest po wprowadzeniu w stan przewodzenia tranzystora dostępu komórki.

- Odczyt - wzmocnienie po uaktywnieniu linii sense_N

- Odczyt „1” z komórki w tablicy 0

- Dwa wzmacniacze odczytu : NSA – z tranzystorami nMOS oraz PSA – z tranzystorami pMOS.

- Odświeżanie zawartości komórki DRAM

- Szumy w „architekturze otwartej tablicy”

- Zmniejszenie szumów odczytu przez zastosowanie „architektury tablicy złożonej”

- Rozkład elementów komórki DRAM

- Rozkład elementów komórki DRAM w „architekturze otwartej tablicy”

- Rozkład elementów komórki DRAM w „architekturze złożonej tablicy”

- Konstrukcje kondensatorów w komórkach DRAM

- Rozkład bloków pamięci DRAM w układzie scalonym

- Pamięci DRAM – współpraca układów o różnych napięciach zasilania

- Komórka pamięci statycznej (SRAM) – z 6 tranzystorami

- Komórka pamięci statycznej (SRAM) – z 2 tranzystorami i 2 rezystorami

- Pamięci tylko do odczytu (ROM)

- Pamięć nieulotna z pływającą bramką

- Pamięć nieulotna z pływającą bramką – napięcie progowe

- Reprogramowalne pamięci ROM (erasable programable – EPROM)

- flash_1

- flash_2

- flash_3

- flash_4

- Pamięci nieulotne „flash” – charakterystyki tranzystorów

- Slide 34

- Slide 35

Wyszukiwarka

Podobne podstrony:

pamiec CMOS Baker 2007 plotka

pamiec CMOS Baker 2007 plotka

03 Odświeżanie pamięci DRAMid 4244 ppt

wykład 12 pamięć

8 Dzięki za Pamięć

06 pamięć proceduralna schematy, skrypty, ramyid 6150 ppt

Pamięć

PAMIĘĆ 3

Architektura i organizacja komuterów W5 Pamięć wewnętrzna

Test Pamięci Wzrokowej Bentona2 3

Pamięć robocza i modele umysłowed

uwaga i pamięć

więcej podobnych podstron