PODSTAWY TEORII

UKŁADÓW CYFROWYCH

Opracował: A.

Nowak

UKŁADY

KODUJĄCE

Kodery

Kodery

Kodery służą do przedstawienia informacji z

tylko jednego aktywnego wejścia na postać

binarną.

Ponieważ istnieje fizyczna możliwość

jednoczesnej aktywacji więcej niż jednego

wejścia informacyjnego musi istnieć

możliwość "uznania" tylko jednego.

Tak powstał enkoder priorytetowy, uznający

zawsze najstarsze w hierarchii wejście

(ignoruje akcje na pozostałych).

Znajduje on zastosowanie np. do

wprowadzania informacji z prostej

klawiatury i tłumaczenie jej na kod

zrozumiały dla układu cyfrowego.

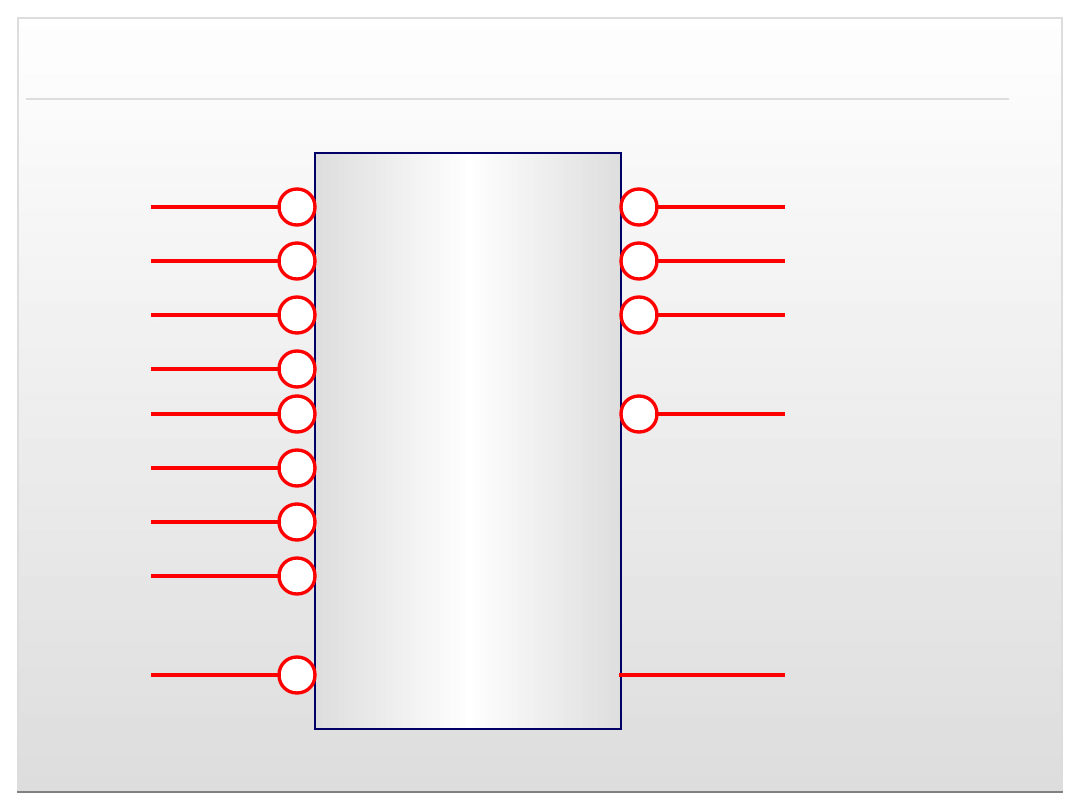

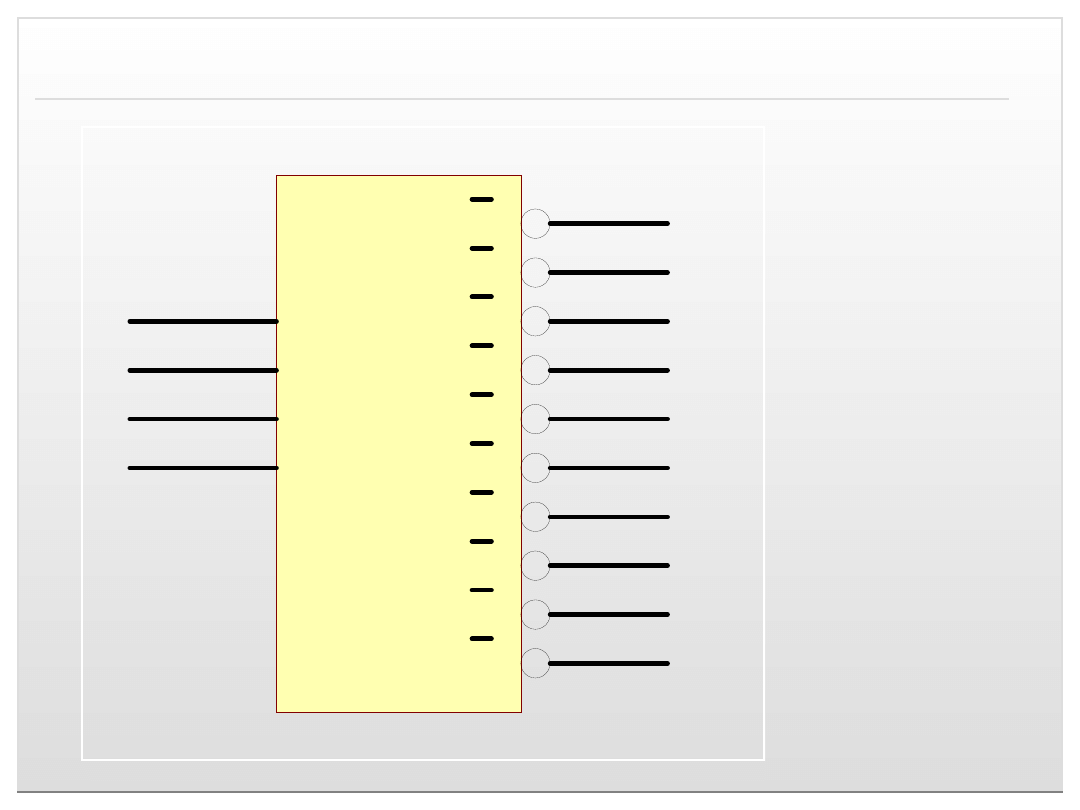

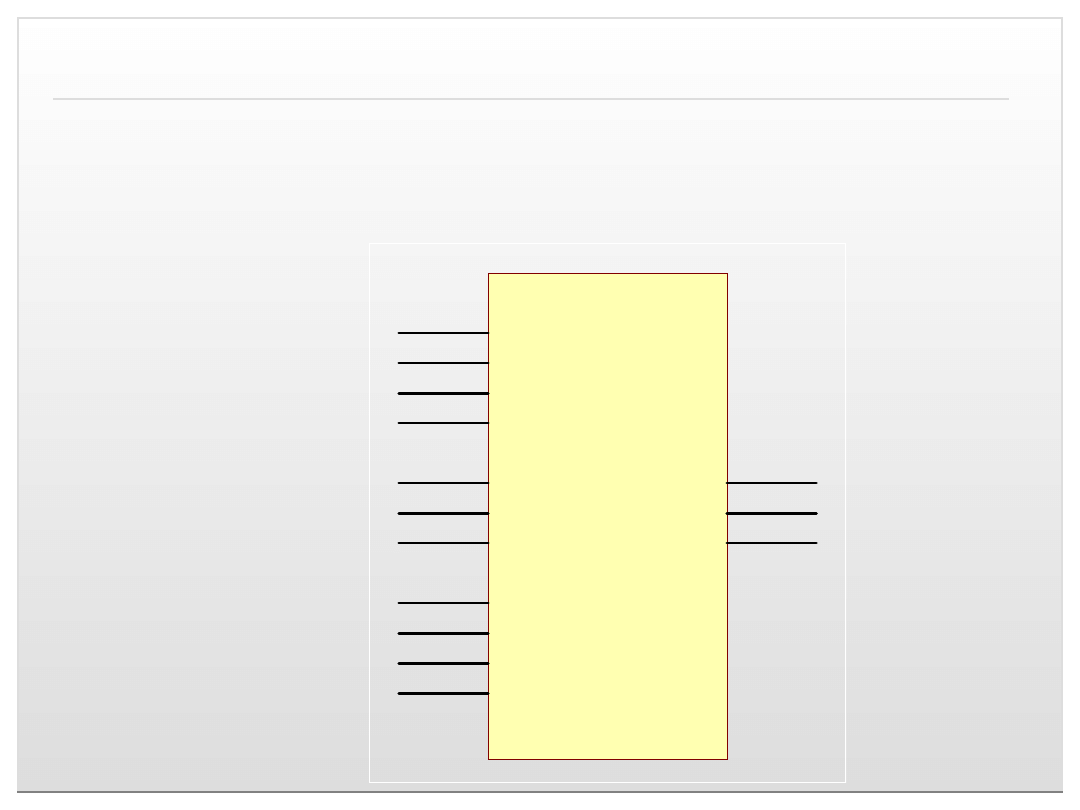

Koder – UCY 74148

1

1

1

0

1

2

1

3

1

4

1

5

1

2

3

4

5

9

7

6

0

1

2

3

4

5

6

7

EI

A

B

C

GS

EO

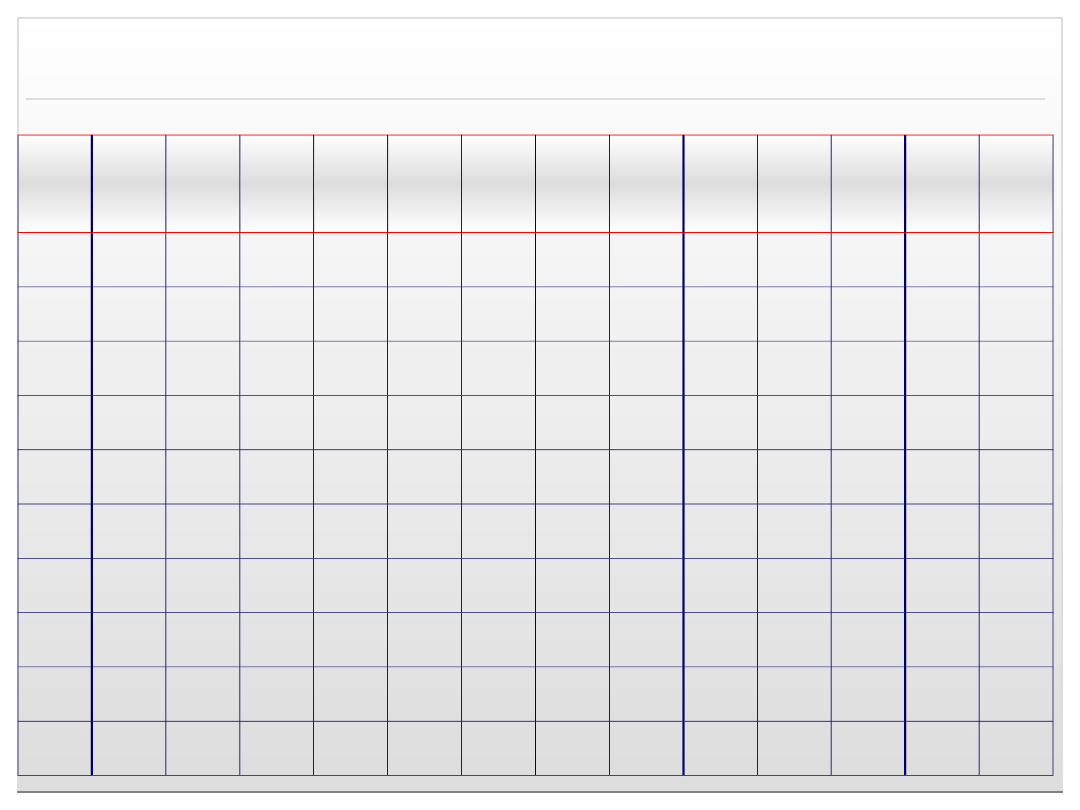

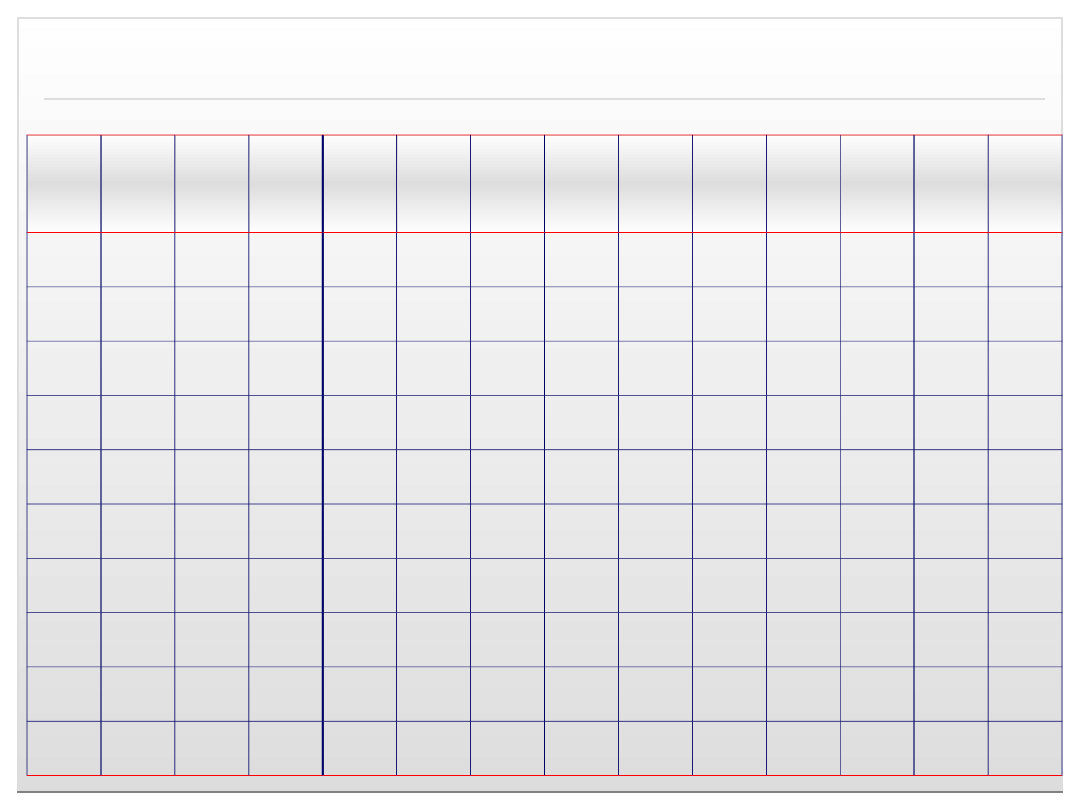

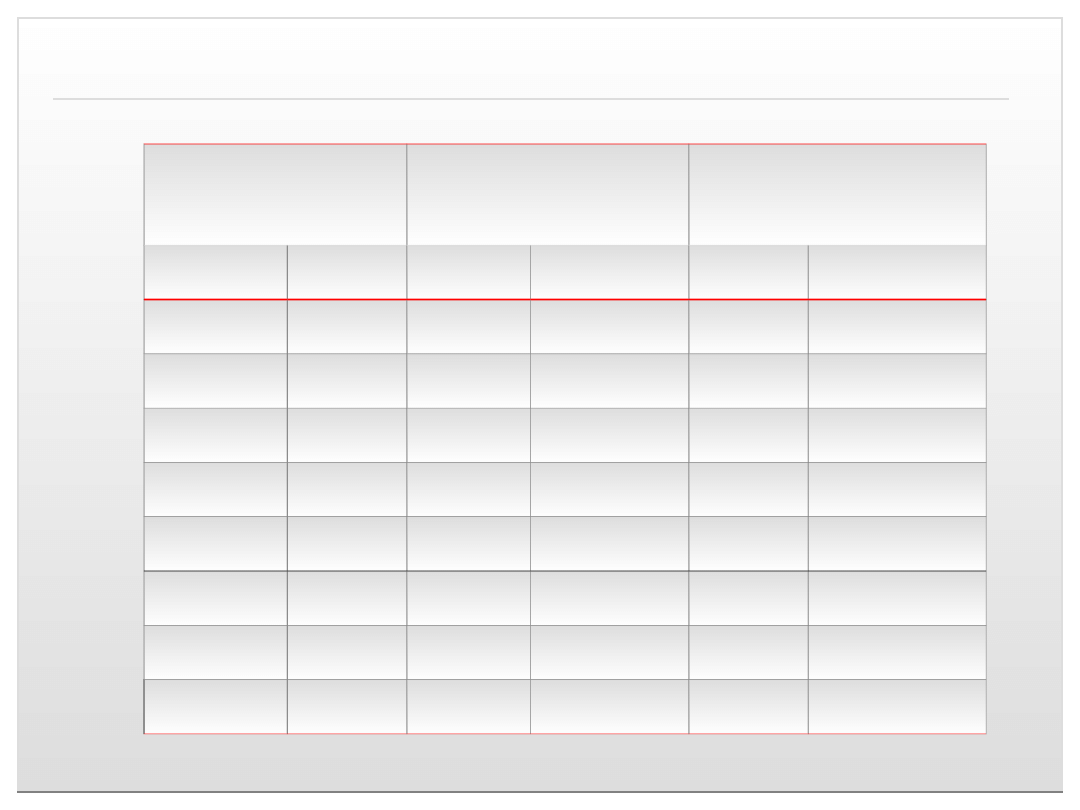

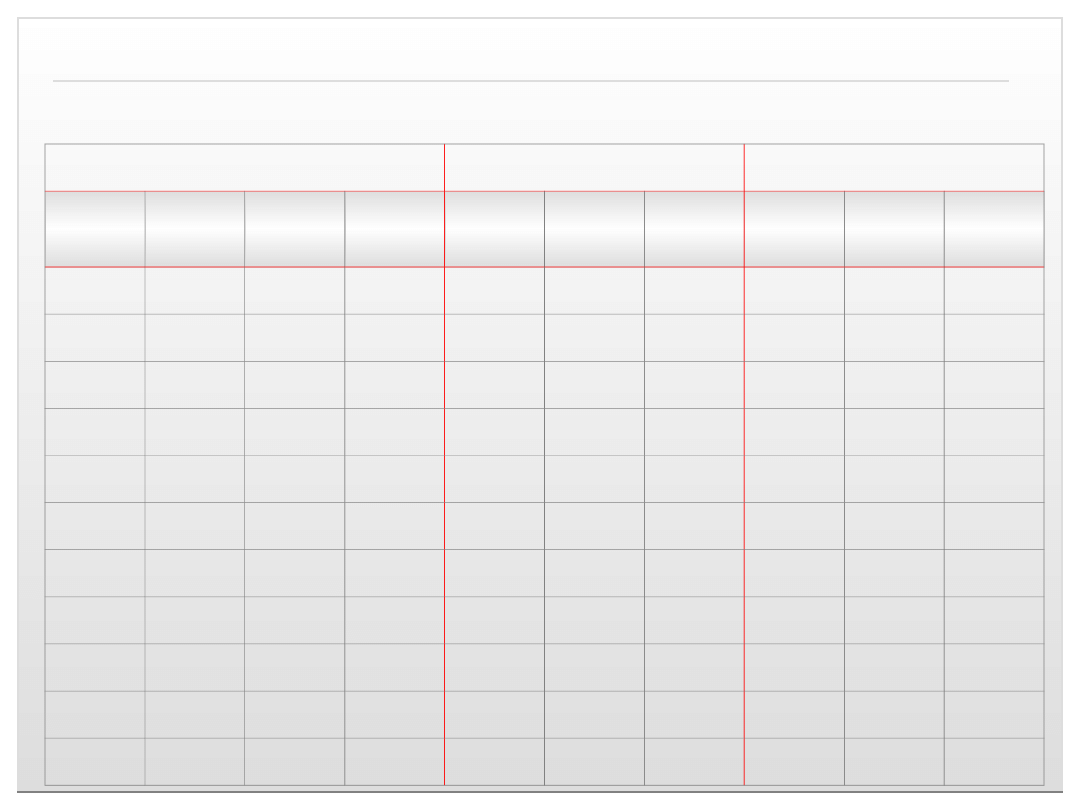

Koder – UCY 74148 - tabela

kodowania

EI

0

1

2

3

4

5

6

7

A

B

C

G

S

E

O

1

X

X

X

X

X

X

X

X

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

X

X

X

X

X

X

X

0

0

0

0

0

1

0

X

X

X

X

X

X

0

1

0

0

1

0

1

0

X

X

X

X

X

0

1

1

0

1

0

0

1

0

X

X

X

X

0

1

1

1

0

1

1

0

1

0

X

X

X

0

1

1

1

1

1

0

0

0

1

0

X

X

0

1

1

1

1

1

1

0

1

0

1

0

X

0

1

1

1

1

1

1

1

1

0

0

1

0

0

1

1

1

1

1

1

1

1

1

1

0

1

Kodery

X

- oznacza wartość nieistotną - tzn. dla

wybranego wejścia np. 5 (aktywne 0),

niezależnie od stanów na wejściach

młodszych i tak zostanie zakodowana 5.

Należy zauważyć, że kod wybranego

wejścia został przedstawiony w postaci

zanegowanego naturalnego kodu

dwójkowego.

Dekodery

Dekodery

Dekoder zamienia kod binarny na jego

reprezentację w postaci wybranego tylko

jednego wyjścia (aktywne 0).

W zależności od ilości wyjść (n) nazywa się

dekoderem 1 z N.

Dekoder – UCY 7442

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

9

8

10

9

11

A3

12

A2

13

A1

14

A0

15

7442

Dekoder

A

0

A

1

A

2

A

3

0

1

2

3

4

5

6

7

8

9

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

1

0

1

1

1

1

1

1

1

1

0

1

0

0

1

1

0

1

1

1

1

1

1

1

1

1

0

0

1

1

1

0

1

1

1

1

1

1

0

0

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

0

1

1

1

1

0

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

1

1

0

0

0

1

1

1

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

Gr 1i2 1 it

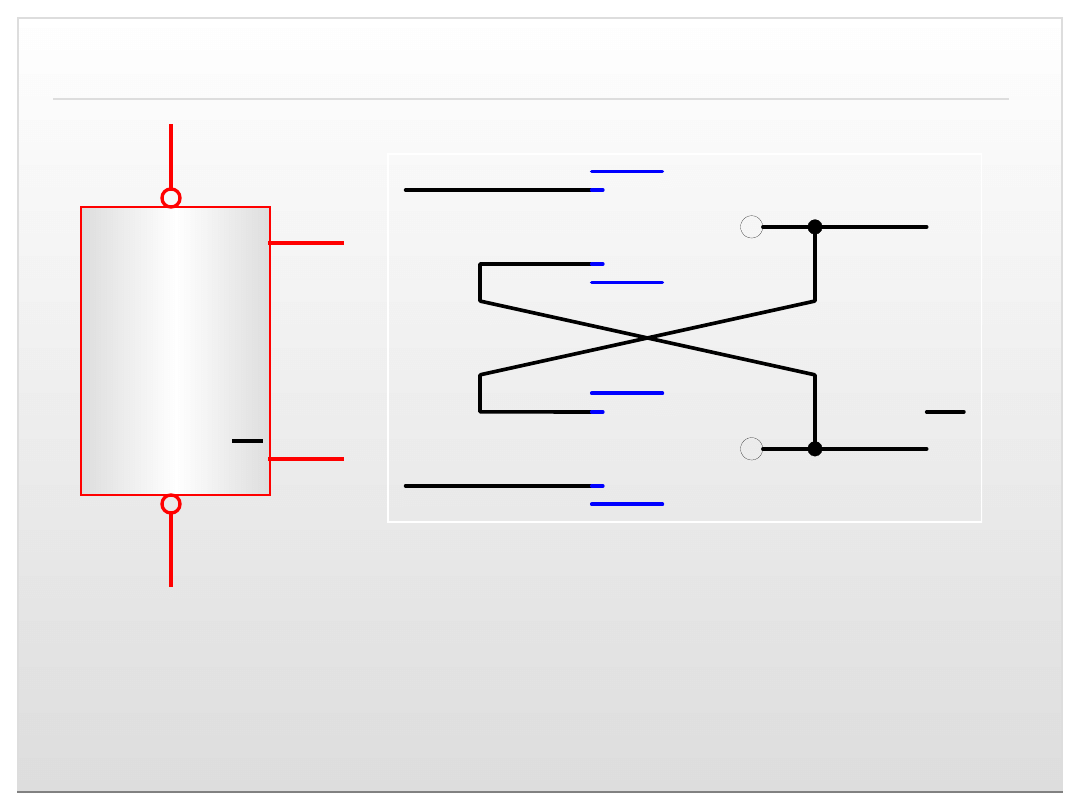

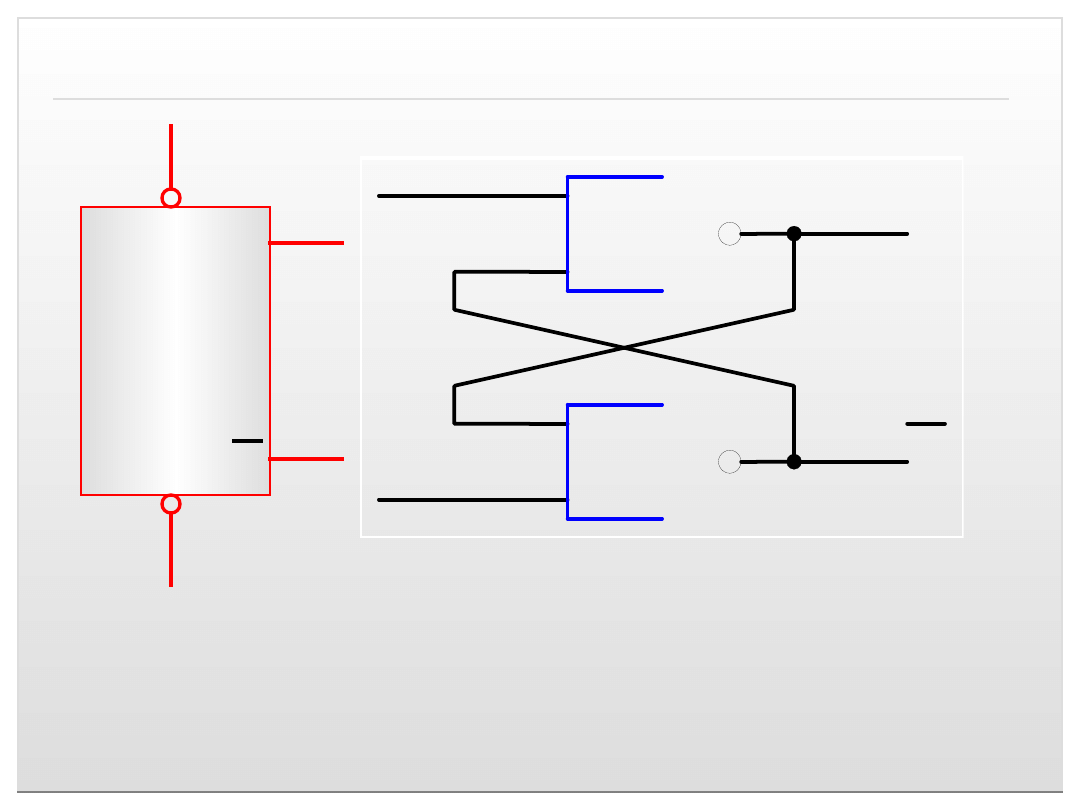

Multipleksery

i

demultipleksery

Multipleksery i demultipleksery

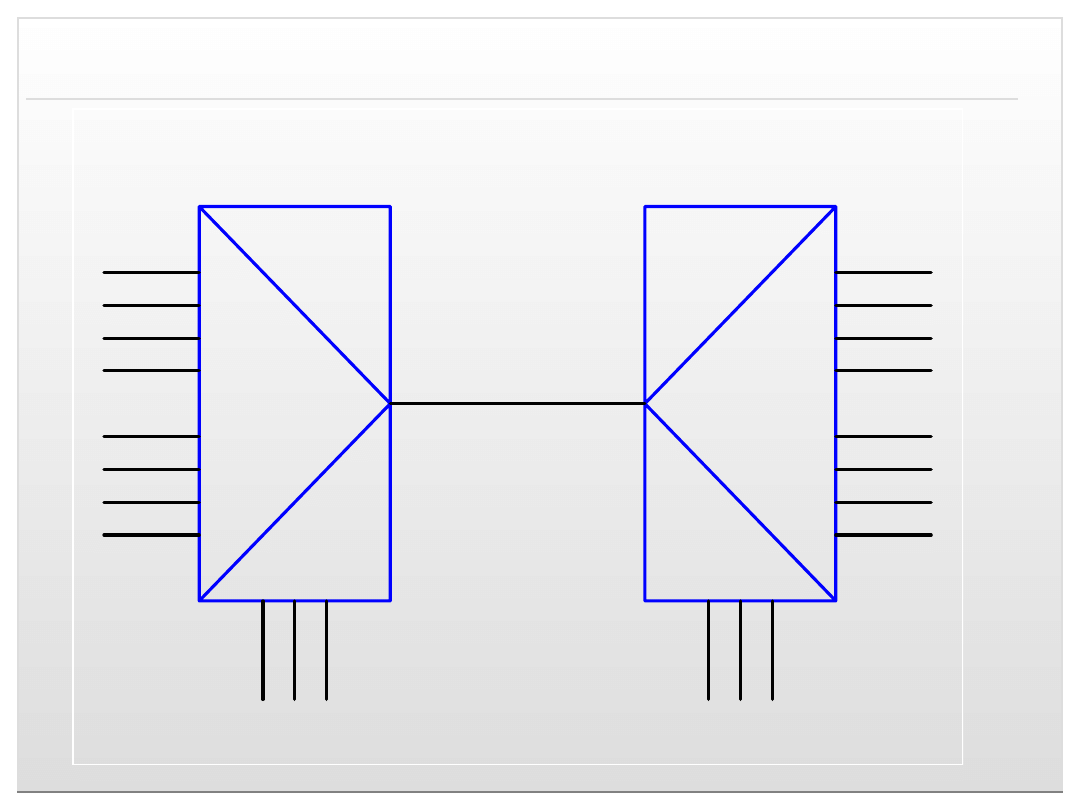

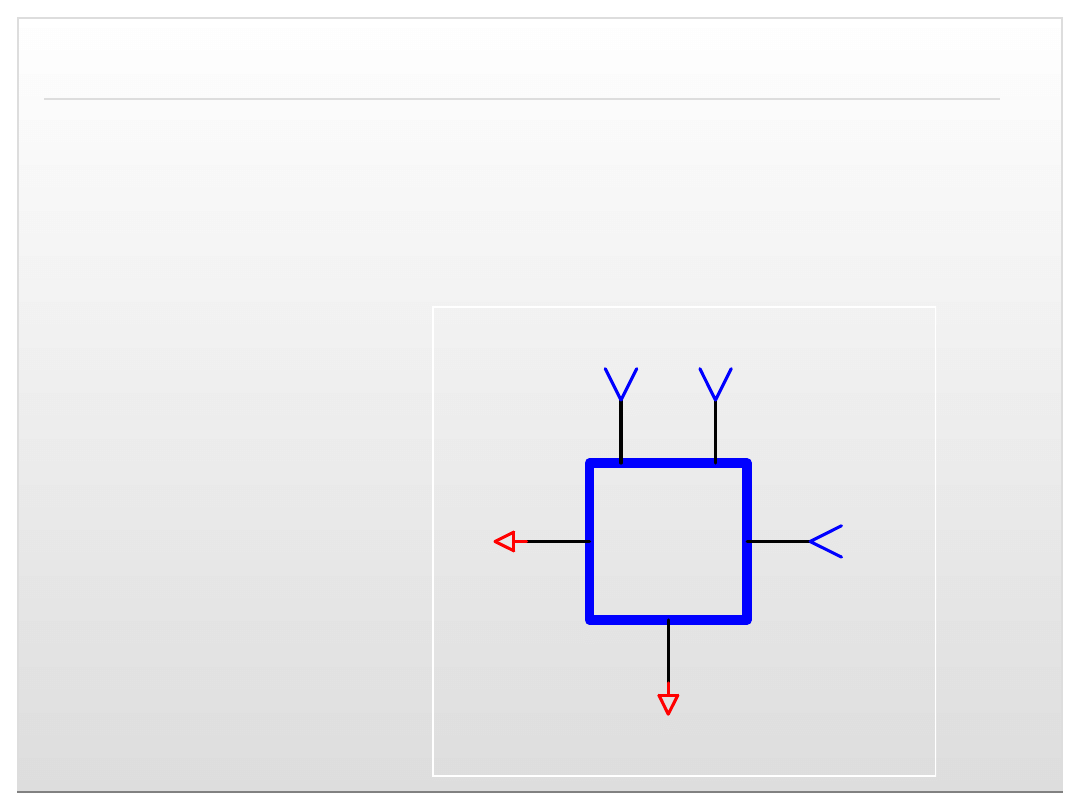

Multiplekser

(MPX) ma zadanie, w

zależności od kodu wejścia (kod

binarny) połączyć ten numer

wejścia ze wspólnym wyjściem.

Demultiplekser

(DMPX) działa na

odwrót.

Multipleksery i demultipleksery

Multipleksery i demultipleksery właściwie

należy rozpatrywać łącznie.

Oprócz funkcji specjalnych, umożliwiających

syntezę układów kombinacyjnych,

właściwym ich zastosowaniem jest

stworzenie np. toru transmisji danych

udostępnianego naprzemiennie informacji na

różnych wejściach i kierowanie jej do

odpowiednich wyjść.

Wymaga to jednak pełnej synchronizacji kodów

na wejściach A, B, C. Można jednak przekierować

informację na dowolne wyjście demultipleksera.

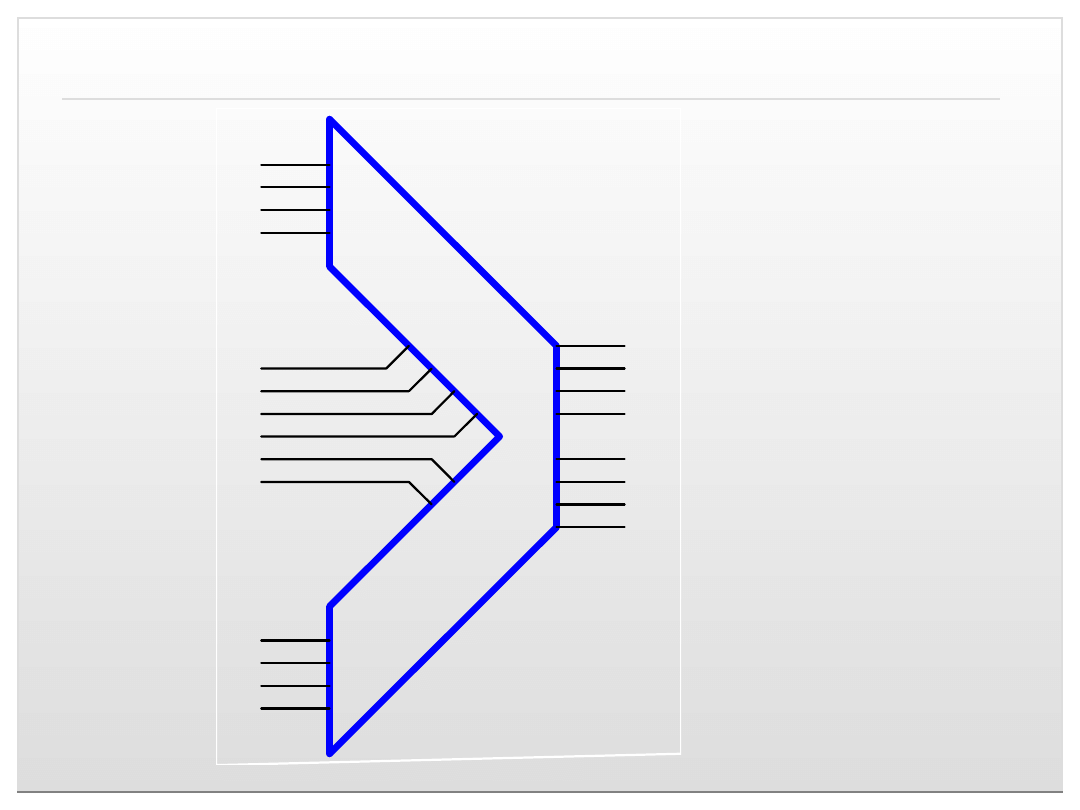

Multiplekser

(MPX) i

demultiplekser

(DMPX)

0

1

2

3

4

5

6

7

A B C

0

1

2

3

4

5

6

7

A B C

MPX

DMPX

Multiplekser i demultiplekser z zastosowaniem rzeczywistych

układów scalonych

D0

8

D1

7

D2

6

D3

5

D4

4

D5

3

D6

2

D7

1

D8

23

D9

22

D10

21

D11

20

D12

19

D13

18

D14

17

D15

16

A

15

B

14

C

13

D

11

G

9

Q

10

74150

A

23

B

22

C

21

D

20

G1

18

G2

19

0

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

13

12

14

13

15

14

16

15

17

74154

KOD WEJ�CIA

KOD WYJ�CIA

TOR TRANSMIS JI

0

1

0

1

0

0

1

0

Krzyżykami zaznaczono wejścia /

wyjścia informacyjne (uwaga na

kody binarne) między którymi

następuje wymiana danych.

UKŁADY

SEKWENCYJNE

Ogólna definicja

Układem sekwencyjnym nazywamy

układ cyfrowy, w którym

stan wyjść

zależy

od

stanu wejść

oraz od

poprzednich

stanów układu.

Składa się z bramek i

przerzutników.

Przerzutniki

Przerzutniki

Przerzutnik - układ cyfrowy umożliwiający

przechowywanie najmniejszej porcji

informacji – jednego bitu.

Zmienia swój stan bądź to przez

wymuszenie stanu na wejściu

(asynchroniczne) lub zaistnienie sygnału

zegarowego (synchroniczne).

•

Asynchroniczne - (RS);

•

Synchroniczne (RS, JK, T, D flip-flop, D

latch).

Przerzutniki

Należy zauważyć, że przerzutnik RS może być

asynchroniczny (nie posiada wejścia zegarowego)

lub synchroniczny (posiada wejście zegarowe),

lecz zawsze posiada tzw. stan zabroniony

(kombinacja, która zaprzecza działaniu

przerzutnika).

Pozostałe przerzutniki pozbawione są tej wady, gdyż

są przerzutnikami dwutaktowymi (tzw. master-

slave M-S).

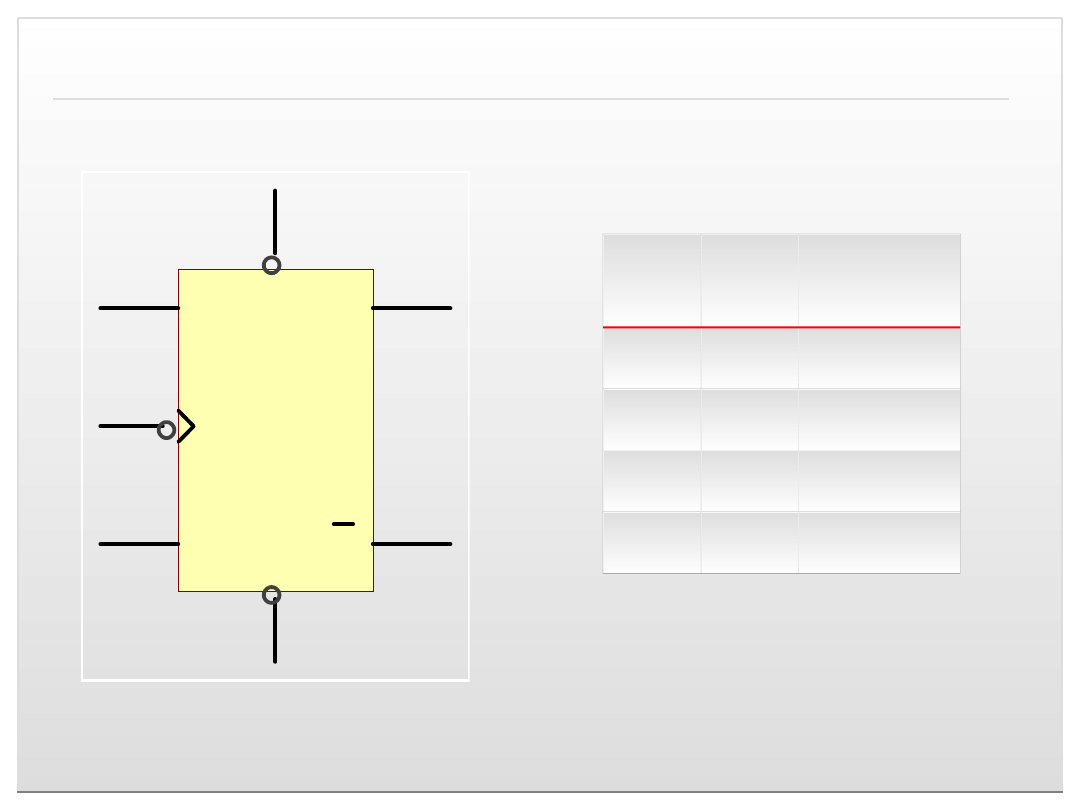

Przerzutniki

Wszystkie przerzutniki powinny posiadać

charakterystyczne wejścia i wyjścia (gwiazdką

zaznaczono nie wymagane - w zależności od

typu):

•

wejścia informacyjne synchroniczne (RS, JK, T, D)

,

•

wejścia asynchroniczne zerujące (R) i

ustawiające (S) *,

•

wejście zegarowe synchronizujące (C) *,

•

wyjście proste (Q),

•

wyjście zanegowane (NOT(Q)).

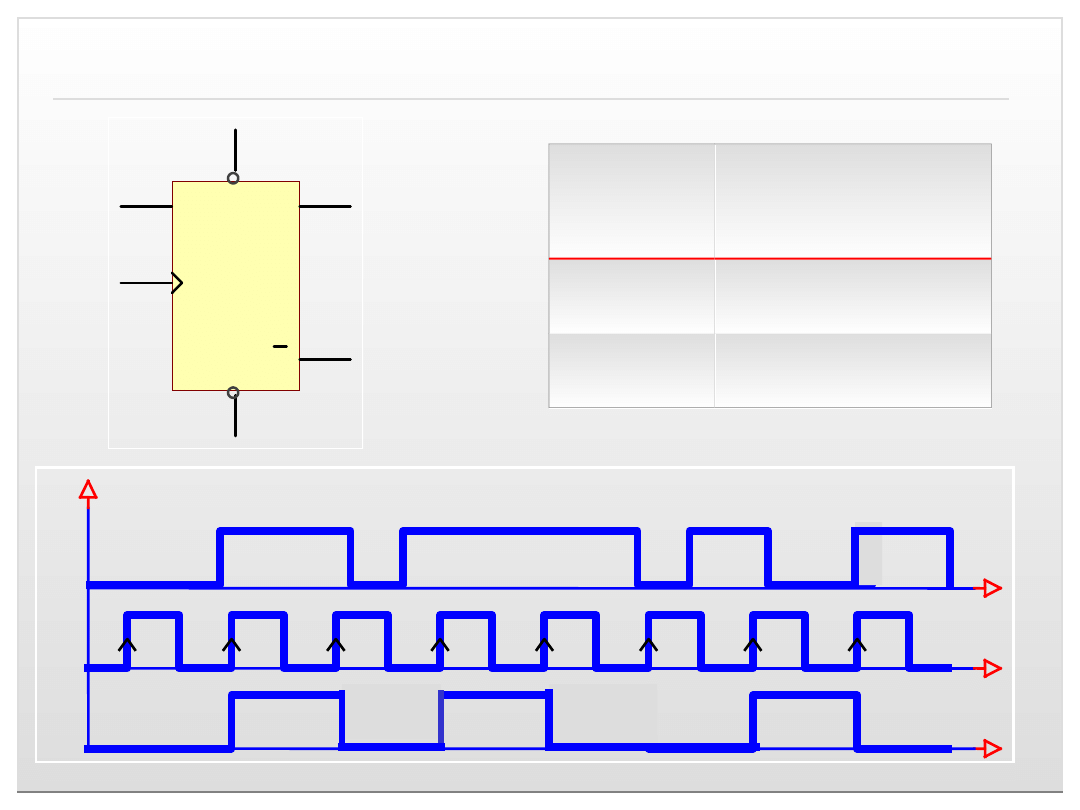

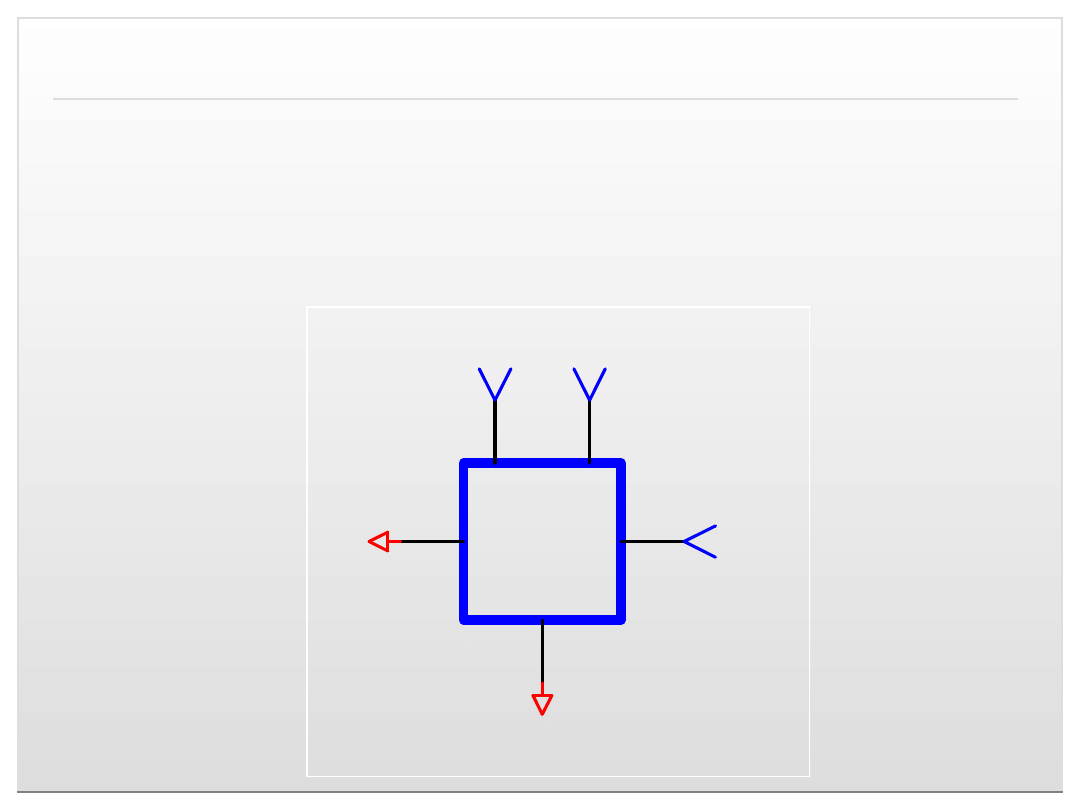

Przerzutnik -

JK

J

K

C

Q

Q

R

S

J

K Qn+1

0

0

Qn

0

1

0

1

0

1

1

1

/Qn

Przerzutnik -

T

(powstaje z połączenia wejść J+K)

T

C

Q

Q

R

S

t

t

t

T

C

Q

T

Qn+1

0

Qn

1

/Qn

gr1

Przerzutnik -

D flip-flop

D

C

Q

Q

R

S

D

Qn+1

0

0

1

1

t

t

t

D f

C

Q

Przerzutnik -

D

latch

D

C

Q

Q

R

S

D

Qn+1

0

0

1

1

D

latch

C

Q

t

t

t

Gr 2

gr1

Przerzutnik -

RS

asynchroniczny

R

S

Q

Q

schemat wykonanego z bramek

NOR

asynchronicznego

przerzutnika

RS

R

S

Q

Q

Przerzutnik -

RS

asynchroniczny

schemat wykonanego z bramek

NAND

asynchronicznego

przerzutnika

RS

R

S

Q

Q

R

S

Q

Q

Przerzutnik -

RS

asynchroniczny

NOR

NAND

R

S

Qn

Qn+1

Qn

Qn+1

0

0

0

0

0

*

0

0

1

1

1

*

0

1

0

1

0

1

0

1

1

1

1

1

1

0

0

0

0

0

1

0

1

0

1

0

1

1

0

*

0

0

1

1

1

*

1

1

Rejestry

Rejestry

Rejestrem

nazywamy układ

cyfrowy przeznaczony do

krótkoterminowego

przechowywania ilości

informacji lub do zamiany

postaci informacji z

równoległej na szeregową

albo odwrotnie.

Rejestry

Rejestry to układy zbudowane z

przerzutników D i z tego względu

(zasada działania przerzutnika)

służą do przechowywania danych.

Znajdują zastosowania w

konstrukcjach pamięci oraz

nadajnikach - odbiornikach

transmisji szeregowej

.

.

Rejestry - typy

•

Rejestry z wejściem i wyjściem

równoległym – PIPO (ang. parallel input,

parallel output). -

rejestry zatrzaskowe

(ang. latch)

/

buforowe/

•

Rejestry z wejściem i wyjściem

szeregowym – SISO (ang. serial input,

serial output) –

rejestry przesuwające

Rejestry - typy

•

Rejestry z wejściem szeregowym i

wyjściem równoległym – SIPO (ang.

serial input, parallel output)

•

Rejestry z wejściem równoległym i

wyjściem szeregowym – PISO (ang.

parallel input, serial output)

Rejestry

Wejściem cyfrowym szeregowym

nazywamy takie wejście, które umożliwia

wprowadzanie informacji do układu bit

po bicie.

Do wprowadzenia słowa n-bitowego

potrzeba n taktów zegara.

Informacja jest wpisywana szeregowo do

rejestru (bit po bicie) i szeregowo

wyprowadzana.

Rozróżniamy dwa typy rejestrów szeregowych:

•

FIFO - pierwszy bit "wchodzi", pierwszy

"wychodzi",

•

FILO - pierwszy bit "wchodzi", ostatni

"wychodzi".

Rejestry z

wejściem cyfrowym

równoległym

Wejściem cyfrowym równoległym

nazywamy takie wejście, które umożliwia

wprowadzenie do układu cyfrowego

wszystkich bitów słowa w jednym takcie

zegarowym.

D

C

Q

R

D

C

Q

R

D

C

Q

R

D

C

Q

R

CLK

RES ET

D0

D1

D2

D3

Q0

Q1

Q2

Q3

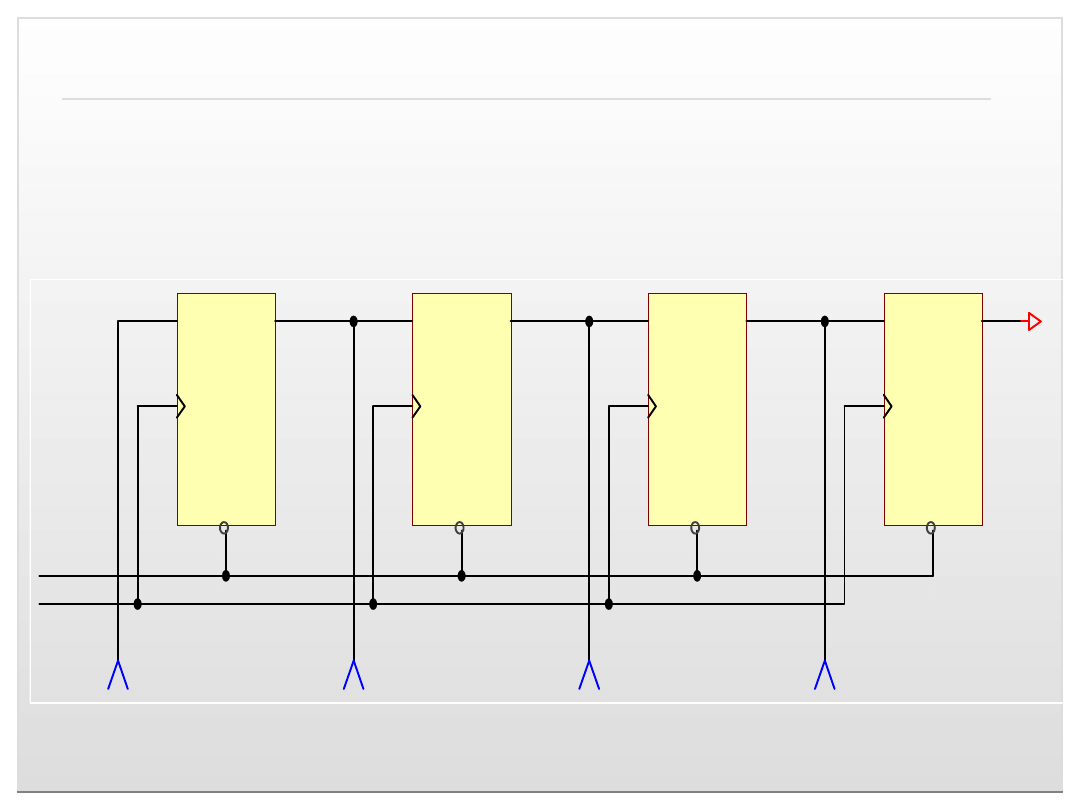

Rejestr – równoległo - szeregowy

Informacja jest wpisywana równolegle a

wyprowadzana szeregowo

D

C

Q

R

D

C

Q

R

D

C

Q

R

D

C

Q

R

CLK

RESET

D0

D1

D2

D3

Q

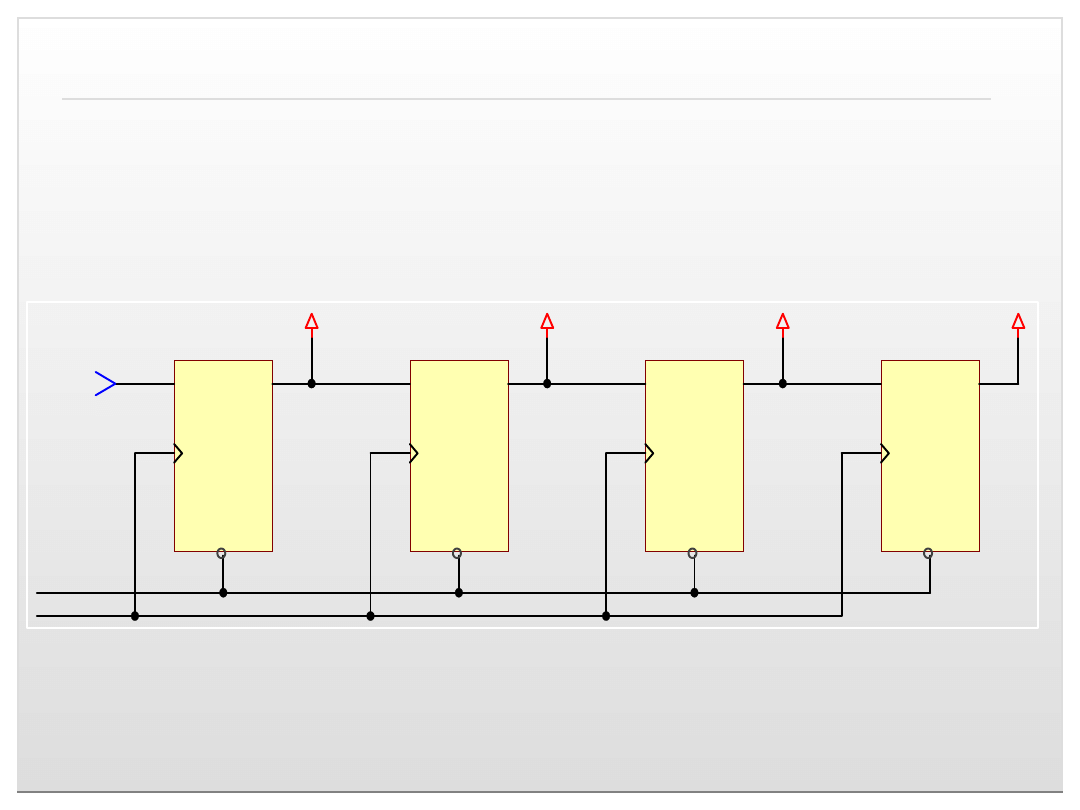

Rejestr – szeregowo - równoległy

Informacja jest wpisywana szeregowo a

wyprowadzana równolegle.

D

C

Q

R

D

C

Q

R

D

C

Q

R

D

C

Q

R

CLK

RESET

Q0

Q1

Q2

Q3

Gr

2

Liczniki

Liczniki

Liczniki są to układy sekwencyjne

zbudowane z przerzutników, najczęściej

JK lub T.

Ich zadaniem jest zliczanie impulsów

zegarowych i przedstawianie stanu na

wyjściach.

Można dokonać podziału liczników pod

wieloma względami:

Liczniki

Ze względu na s wyróżnialnych stanów (pod

względem sposobu powtarzania cyklu):

•

modulo s (dzielniki liczby impulsów

zegarowych - częstotliwości - przez s),

•

do s,

Pod względem sposobu oddziaływania impulsów

zliczanych na stan przerzutników licznika:

•

o stałej długości cyklu,

•

o programowanej długości cyklu.

Liczniki

Pod względem kierunku zliczania:

•

jednokierunkowe liczące w przód,

•

jednokierunkowe liczące wstecz,

•

dwukierunkowe (rewersyjne).

Pod względem sposobu oddziaływania impulsów

zliczanych na stan przerzutników licznika:

•

asynchroniczne,

•

synchroniczne,

•

asynchroniczno - synchroniczne

.

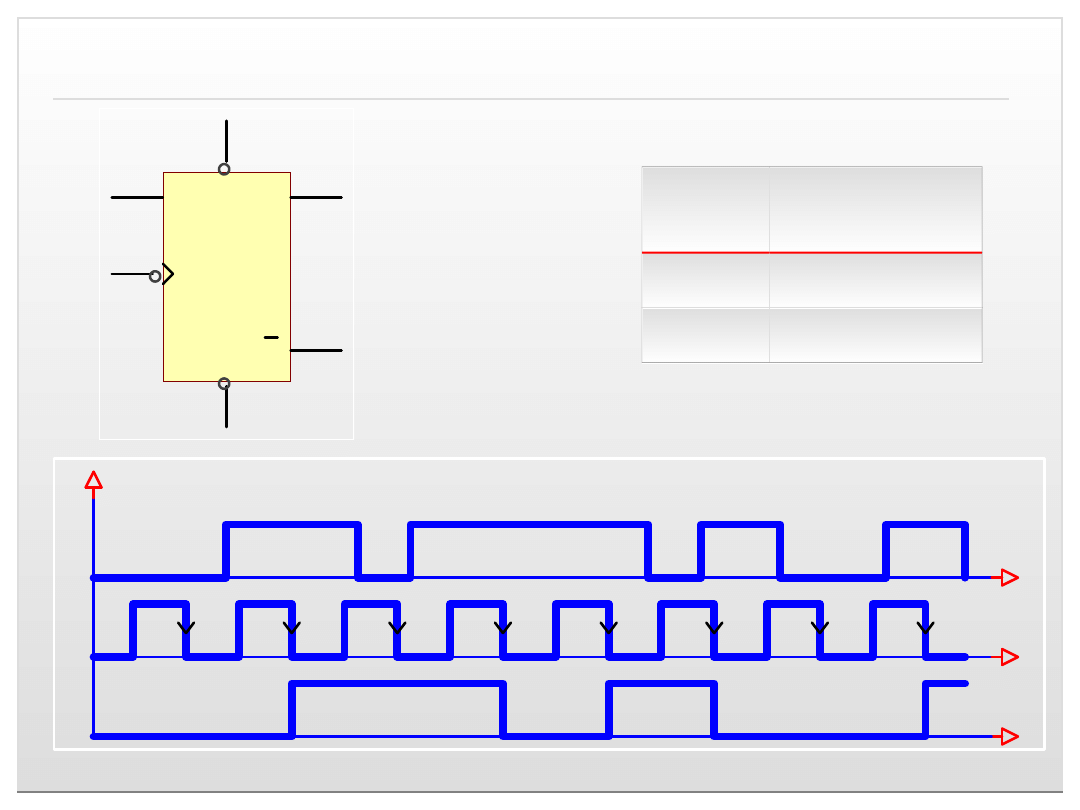

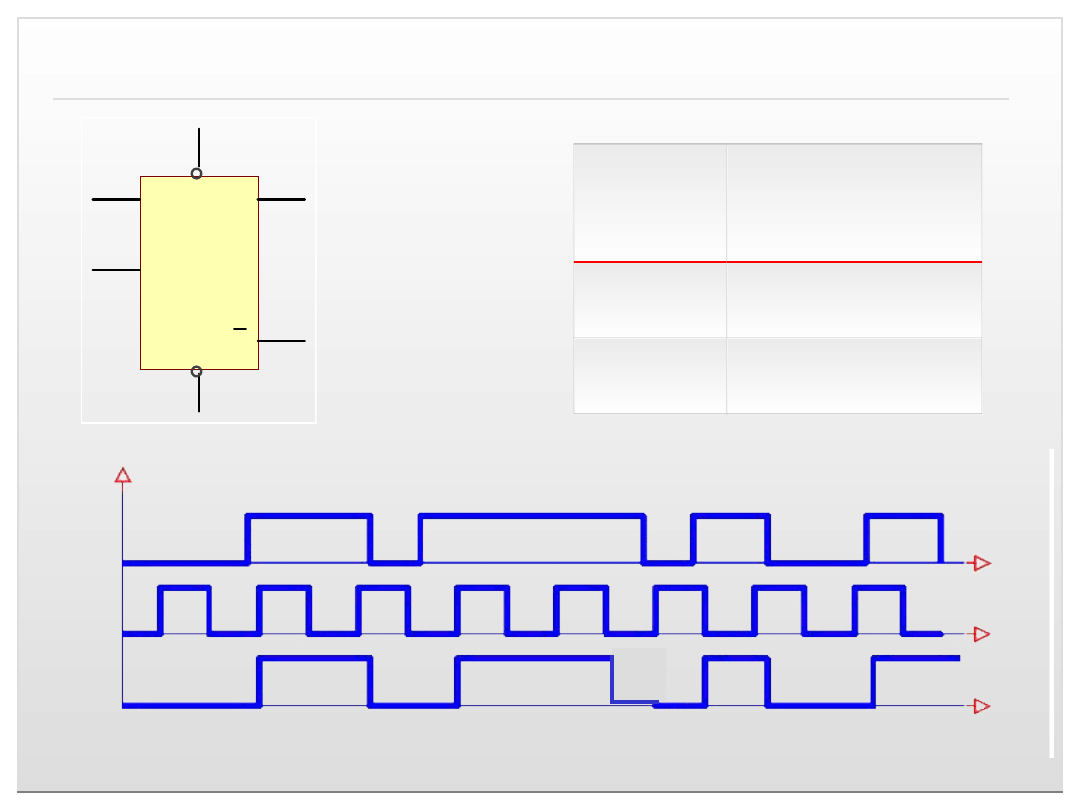

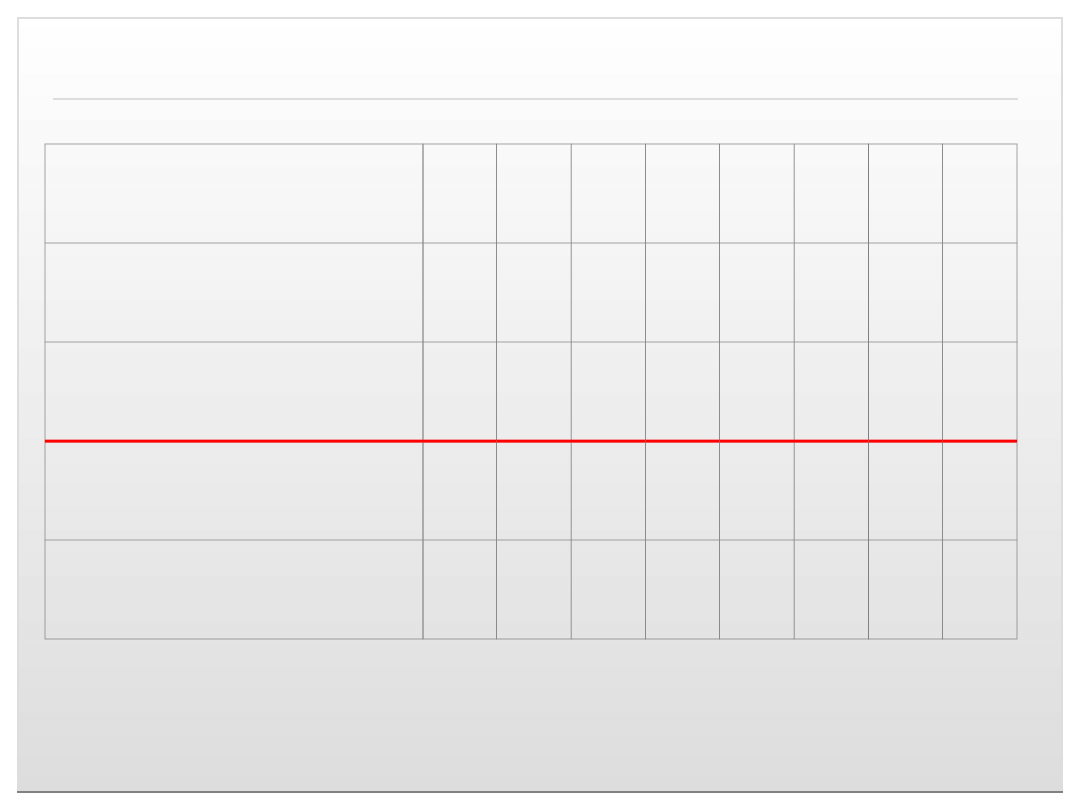

Liczniki

Najprostszą formą licznika jest przerzutnik T z

podpiętym na stałe wejściem T do logicznej

"jedynki".

Taki przerzutnik nazywa się "dwójką liczącą".

Porównując tabelę prawdy dochodzimy do

wniosku, że po każdym impulsie zegarowym

przerzutnik zmieni stan na przeciwny.

W oparciu o niego można zbudować

asynchroniczny licznik liczący np. do 8.

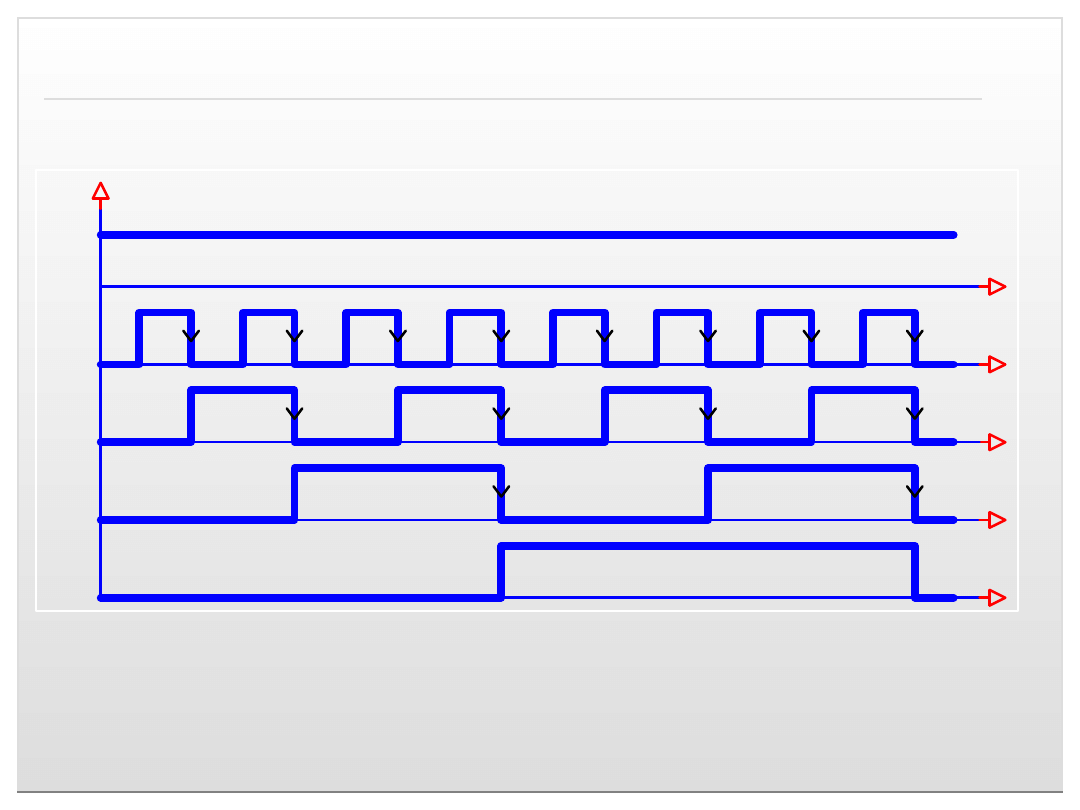

Poniżej przedstawiono na wykresie czasowym

kolejne stany licznika.

Analizując je można stwierdzić że układają się w

naturalny kod dwójkowy.

Liczniki

Można również zauważyć, że każdy moduł licznika

dzieli częstotliwość zegarową przez dwa. Ilość

możliwych stanów tak zbudowanego licznika

wyraża się wzorem:

n

2

S

gdzie n - ilość przerzutników

Istnieje możliwość wprowadzania danych

początkowych (programowanie) licznika oraz

zmiana kierunku zliczania

Liczniki

t

t

t

T

C

Q1

Q2

Q3

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

t

t

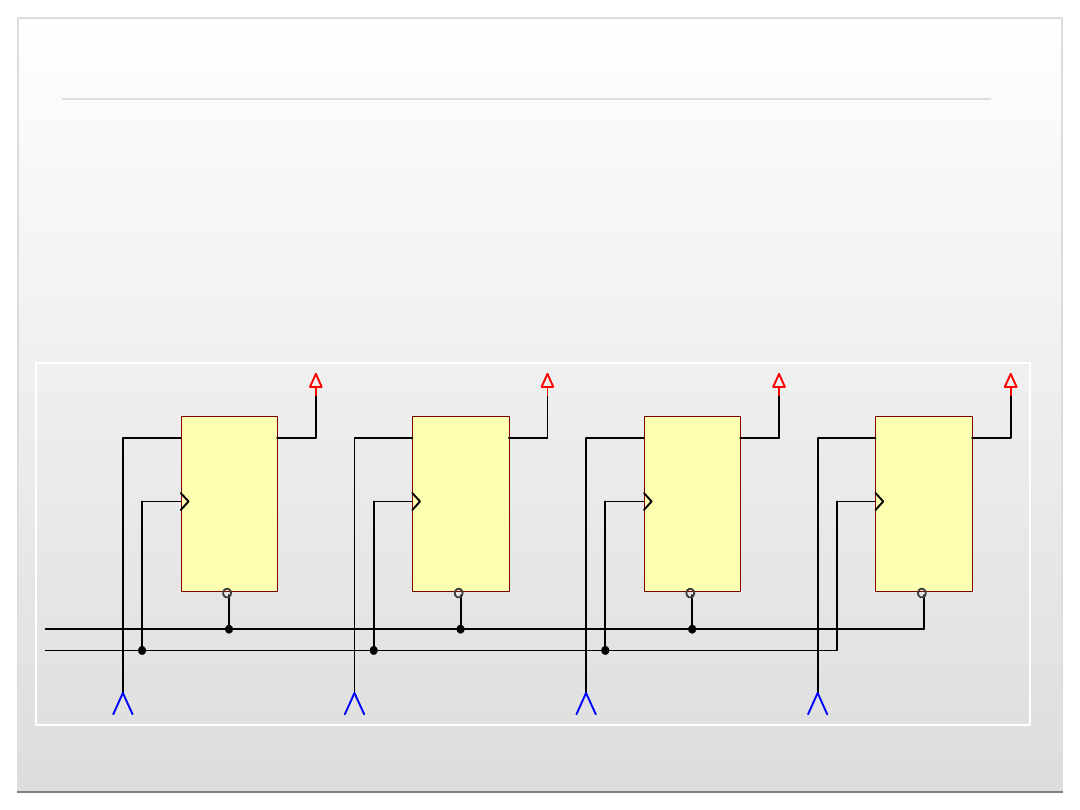

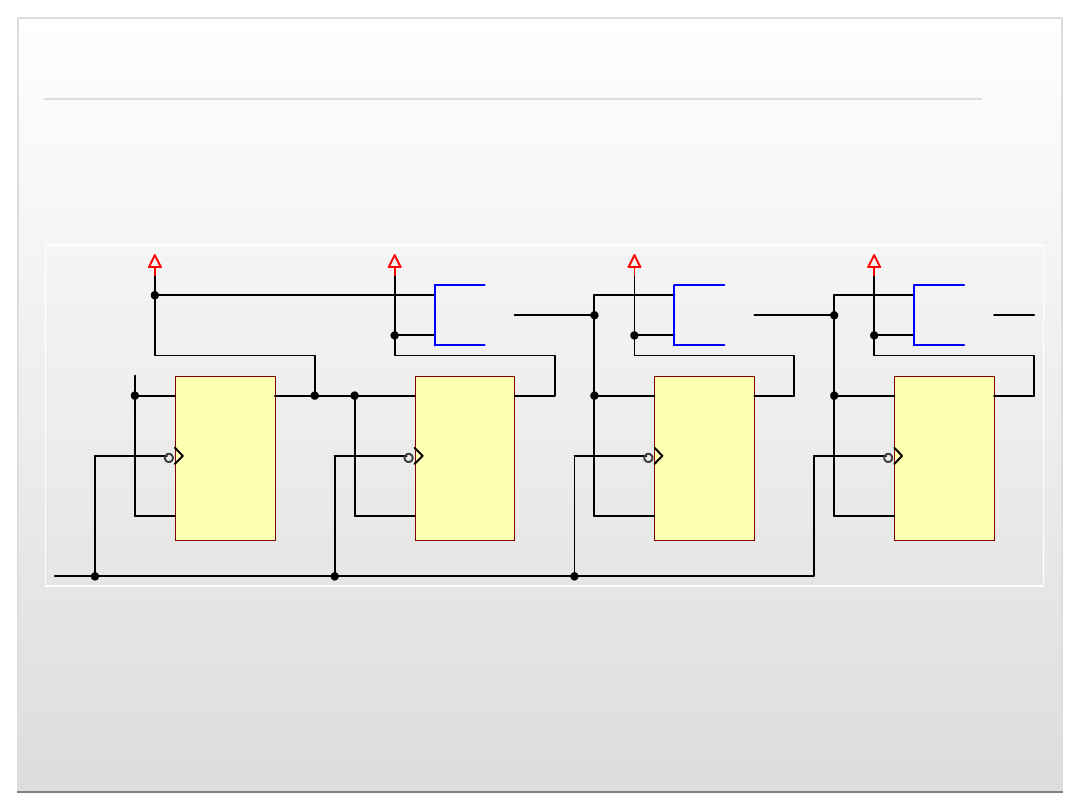

LICZNIK Z PRZENIESIENIEM SZEREGOWYM (ang. Ripple Carry)

J

K

C

Q

"1"

J

K

C

Q

J

K

C

Q

C

A

B

C

J

K

C

Q

D

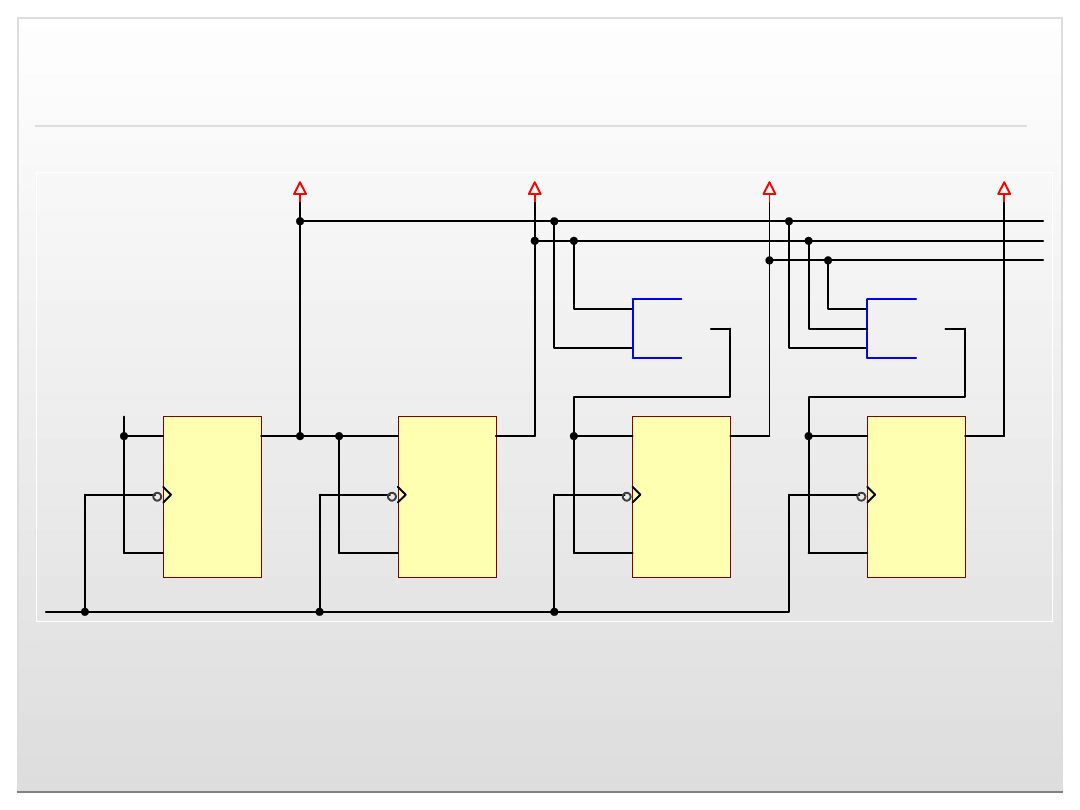

LICZNIK Z PRZENIESIENIEM RÓWNOLEGŁYM

(ang. Look Ahead)

J

K

C

Q

"1"

J

K

C

Q

J

K

C

Q

C

J

K

C

Q

A

B

C

D

UKŁADY

ARYTMETYCZNE

Sumator

Sumator

SUMATOR

realizuje operację

dodawania

, możliwe

jest łączenie ich kaskadowo (sumowanie

liczb wielobitowych).

Ai

Bi

S i

Ci

Ci-1

Sumator - tabela działania

Dodajna

Ai

0

0

0

0

1

1

1

1

Dodajnik

Bi

0

0

1

1

0

0

1

1

Przeniesienie

Ci-1

0

1

0

1

0

1

0

1

Suma

Si

0

1

1

0

1

0

0

1

Przeniesienie

Ci

0

0

0

1

0

1

1

1

Subtraktor

Subtraktor

SUBTRAKTOR

realizuje operację

odejmowania

,

również możliwe jest łączenie ich

kaskadowo.

Ai

Bi

Di

Vi

Vi-1

Subtraktor - tabela działania

Odjemna

Ai

0

0

0

0

1

1

1

1

Odjemnik

Bi

0

0

1

1

0

0

1

1

Pożyczka

Vi-1

0

1

0

1

0

1

0

1

Różnica

Di

0

1

1

0

1

0

0

1

Pożyczka

Vi

0

1

1

1

0

0

0

1

Multiplikator

Multiplikator

MULTIPLIKATOR

realizuje operację

mnożenia

, łączy się je

kaskadowo. Jest to dość skomplikowany układ,

więc rysunek zostanie pominięty.

Komparator

Komparator

KOMPARATOR

realizuje operację

porównania

, łączy

się je kaskadowo

A0

A1

A2

A3

B0

B1

B2

B3

A>B

A=B

A<B

A>B

A=B

A<B

Komparator

- znak X w tabeli oznacza stan nieistotny.

relacje

wejścia

wyjścia

A3,B

3

A2,B

2

A1,B

1

A0,B

0

A>B A<B A=B A>B A<B A=B

>

X

X

X

X

X

X

1

0

0

<

X

X

X

X

X

X

0

1

0

=

>

X

X

X

X

X

1

0

0

=

<

X

X

X

X

X

0

1

0

=

=

>

X

X

X

X

1

0

0

=

=

<

X

X

X

X

0

1

0

=

=

=

>

X

X

X

1

0

0

=

=

=

<

X

X

X

0

1

0

=

=

=

=

1

0

0

1

0

0

=

=

=

=

0

1

0

0

1

0

=

=

=

=

0

0

1

0

0

1

ALU

ALU

Uniwersalna Jednostka Arytmetyczno -

Logiczna

-realizuje wszystkie wcześniejsze

operacje

plus

operacje logiczne

.

ALU

jest

podstawowym

elementem

("sercem") każdego mikroprocesora i od

jego konstrukcji, skomplikowania, szybkości

zależy w znacznej mierze wydajność

każdego procesora, a przez to i całego

komputera.

ALU – schemat ideowy

A0

A1

A2

A3

B0

B1

B2

B3

F0

F1

F2

F3

S 0

S 1

S 2

S 3

M

C0

C4

A=B

P

G

ALU – uproszczona zasada

działania

W zależności od stanu wejść sterujących

S0 - S3 układ wykonuje różne funkcje

(dodawanie , odejmowanie, mnożenie

itp.) na liczbach An i Bn, podając wynik

na wyjściach Fn.

Wejście M przełącza rodzaj funkcji -

logiczne / arytmetyczne.

Wejścia / wyjścia C0 i C4 wraz z A=B, P i

G sygnalizują relacje pomiędzy liczbami

An i Bn oraz umożliwiają przeniesienie

danych do następnych ALU, gdyż

możliwe jest również łączenie tych

układów kaskadowo.

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

- Slide 50

- Slide 51

- Slide 52

- Slide 53

- Slide 54

- Slide 55

- Slide 56

- Slide 57

- Slide 58

- Slide 59

- Slide 60

- Slide 61

- Slide 62

- Slide 63

Wyszukiwarka

Podobne podstrony:

Ogrzewanie dodatkowe (PTC)

Egzamin z PTC podst kombinacyjne, elektro, 1, Podstawy Techniki Mikroprocesorowej

Egzamin z PTC Nisko, elektro, 1, Podstawy Techniki Mikroprocesorowej

Wniosek do PTC Era (windykacja), Wzory Dokumentów

Przekaźnik PTC typu MS(R) 220KA

10 TRIHAL HV LV TRANSFOR PTC PROTECTION

Przekaźnik PTC typu MS(R) 220KA

instrukcja PTC cw1 kombinacyjne Nieznany

doogrzewacze PTC

MATEUSZ DYBCIAK PTC sprawozdanie 1

DSI technik informatyk ptc 1

ptc 3

Daclab, Instrukcja çwiczenia lab. PTC

instrukcja PTC cw2 hdl wprowadz Nieznany

instrukcja PTC cw3 sekwencyjne synch

Ogrzewanie dodatkowe (PTC)

ptc 2

więcej podobnych podstron