Sprawozdanie z Laboratorium Technik Cyfrowych nr 4

Wstęp

Układy sekwencyjne są to takie układy w których wartość na wyjściu zależy nie tylko od wartości na wejściu ale i wartości poprzedniej wartości wyjściowej. Układy kombinacyjne w odróżnieniu od sekwencyjnych zmieniają wartość na wyjściu niemal natychmiast po pojawianiu się sygnału na wejściu, opóźnienie wiąże się z czasem propagacji bramek, układów logicznych, elementów elektronicznych. Przerzutniki zapamiętują pojedynczy bit i ich wyjście tak długo jest w stanie 1 lub 0 jak długo nie zostanie zmieniony sygnałem zegarowym. Są one podstawowymi elementami z których buduje się złożone układy sekwencyjne. Jest kilka rodzajów przerzutników: RS, JK, T, D.

Ze względu na tryb pracy układy sekwencyjne dzielimy na:

Układy asynchroniczne - nie mają wejścia sterującego ich pracą (synchronizującego, zegarowego), zatem stany wyjść zmieniają się wraz ze zmianą wejść układu.

Układy synchroniczne - reakcja takiego układu na wartości wejść jest determinowana, w dyskretnych chwilach czasowych, przez zewnętrzny sygnał sterujący C (zegarowy, synchronizujący, taktujący).

Układ, w którym występują jedynie synchroniczne przerzutniki bistabilne nazywamy synchronicznym układem sekwencyjnym. Natomiast jeśli choć jeden przerzutnik jest asynchroniczny, to układ sekwencyjny jest asynchroniczny. Znacznie częściej w systemach cyfrowych spotykamy układy synchroniczne. Układy asynchroniczne mogą być układowo prostsze niż synchroniczne. W obu przypadkach dochodzi jednak do występowania zjawisk niepożądanych - określanych jako wyścigi i hazardy. Przyczyną występowania takich zjawisk, które są przejściowe i stabilne jednak niepożądane, są niejednakowe opóźnienia elementów układów i różne drogi sygnałowe układu.

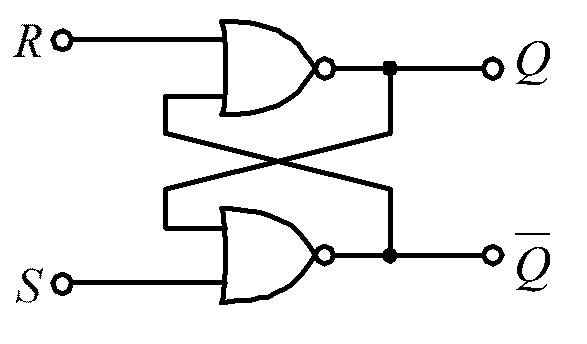

Przerzutnik RS (Set-Reset): ma dwa wejścia S oraz R, wejście S nazywamy ustawiającym, a R resetującym. Gdy na wejście S podawany jest sygnał o wartości 1 to na wyjściu jest 1, gdy będzie podawany sygnał 1 na wejście R to na wyjściu pojawi się 0, jeżeli wartość 1 nie pojawia się ani na wejściu R ani na S to utrzymywana jest wartość poprzednia na wyjściu. Niejednokrotnie dołącza się wejście synchronizujące (zegarowe), wtedy stan na wyjściu zmienia się wraz z stanem zegara.

Tablica wartości dla przerzutnika RS:

|

R |

Qn |

|

0 |

0 |

Qn-1 |

Qn-1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

X |

X |

Wartość X oznacza stan zabroniony, Qn jest sygnałem na wyjściu, a ~Qn jest sygnałem na wyjściu zanegowanym. Przerzutnik można zbudować zarówno na bramkach NAND jak i dla bramek NOR.

Dekoder służy jako układ „kluczujący”, który określa który bit ma zostać odczytany przez multiplekser i wysłany na wyjście adresowe, a w przypadku demultipleksera, który bit z szyny adresowej jest aktualnie odczytywany i na które wyjście ma zostać wysłany.

Multiplekser jest układem posiadającym wejścia danych i wejścia adresowe oraz jedno wyjście. Wejścia adresowe są sterowane przez dekoder i określają, która dana - z wejścia danych, ma zostać w danym momencie odczytana i przesłana na wyjście.

Demultiplekser posiada, tak samo jak multiplekser, wejścia adresowe, jedno wejście danych oraz wyjścia danych. Odpowiada on za przesłanie danej pobranej z wejścia, na odpowiednie wyjście zależne od wejścia adresowego.

Multiplekser i demultiplekser muszą posiadać tyle samo wejść adresowych co dekoder, który de facto nimi steruje. Ilość wejść danych w multiplekserze oraz ilość wyjść w demultiplekserze jest równa liczbie wejść adresowych - zazwyczaj jest to n-ta potęga 2.

Licznik jest to układ cyfrowy, służący do zliczania i pamiętania liczby impulsów podawanych na jego wejście zliczające. Oprócz wejścia dla impulsów zliczanych, licznik ma zazwyczaj wejście ustawiające jego stan początkowy. Ustawienie wszystkich przerzutników, z których jest zbudowany licznik, w stan 0 nazywa się zerowaniem licznika.

Jeżeli licznik przechodzi przez wszystkie stany cyklicznie (tzn. po przejściu N stanów cykl jest powtarzany), to licznik taki nazywamy licznikiem modulo N (w skrócie mod N). Po podaniu na jego wejście zliczające K impulsów, licznik taki wskaże zliczenie L impulsów, gdzie L=KmodN jest resztą z dzielenia całkowitego liczby K przez N. Jeżeli licznik przechodzi przez wszystkie stany jednokrotnie (i po osiągnięciu ostatniego pozostaje w nim). To taki licznik nazywamy licznikiem do N. Ponowne użycie takiego licznika wymaga wcześniejszego ustawienia go w stan początkowy (wyzerowania).

(lab 4.4) Zbudować i sprawdzić działanie przerzutnika RS wyzwalanego zboczem.

Do budowy powyższego układu użyłem dwóch przerzutników D wyzwalanych zboczem. Wyjście zanegowane ~Q1 pierwszego z nich zostało połączone z wejściem D (ang. data) drugiego, natomiast wyjście proste Q2 drugiego połączyłem z wejściem D przerzutnika pierwszego. W związku z tym, że podczas sprawdzania poprawności układu na początku stany wyjściowe są nieznane (nieokreślone) musiałem wprowadzić dodatkowy węzeł (za wejściem D pierwszego przerzutnika), który zmienia wartość sygnału na niską („Force LO”). Najpierw ustawiany jest stan pierwszego przerzutnika D wyzwalanego zboczem, a dopiero później dzięki ustalonej już wartości ~Q1 ustawiany jest drugi przerzutnik. Przerzutnik nr 2 wysyłając wartość Q2 zmienia stany wewnętrzne przerzutnika pierwszego na przeciwne, która to zmiana powoduje zanegowanie stanów przerzutnika drugiego w następnym cyklu. Występuje zatem pętla, która w odpowiednich cyklach przełącza przerzutniki D. Wyjścia ~Q1 oraz Q2 połączone są dodatkowo bramką ExNOR, która w przypadku jednakowych wartości ustawia wyjście przerzutnika RS wyzwalanego zboczem ( Y=1 ), natomiast dla sygnałów przeciwnych stan przerzutnika RS jest zerowany.

(lab 5.1) Zbudować tor transmisji szeregowej (multiplekser, demultiplekser) słowa 4-bitowego przy wykorzystaniu układu dekodera, multipleksera i demultipleksera zbudowanych na bramkach prostych.

Zamiast pokazanych powyżej układów multipleksera i demultipleksera użyłem układy, które moim zdaniem są czytelniejsze.

(lab 5.3) Zbudować, zaobserwować działanie i sprawdzić tabelę prawdy:

Przerzutnik RS kluczowy

D typu zatrzask

RS master-slave

JK master-slave na bramkach NANDD wyzwalany zboczem

Przerzutnik T

(lab 6.1) Liczniki (sprawdzić działanie):

Asynchroniczny modulo 16 - zaobserwować asynchroniczność (np. budując układ zatrzaskujący niepożądany krótkotrwały wynik)

Synchroniczny modulo 16 - spróbować zaobserwować efekt asynchroniczności jak w podpunkcie a.

Dwójkowy z przełączanym kierunkiem zliczania

Asynchroniczny BCD (sprawdzić przejście z liczby 9 na 0)

Synchroniczny BCD

Wnioski:

Układy sekwencyjne mogą przyjmować na wyjściach stany niedozwolone (występuje tzw. Efekt wyścigów i hazardu).

Przerzutniki mogą być wykorzystane jako „komórki pamięci”.

Przerzutnik RS wyzwalany zboczem jest przykładem synchronicznego przerzutnika, w którym nie występują stany niedozwolone.

Budując układy sekwencyjne należy sprawdzać czy podczas działania nie występują stany niedozwolone lub czy wartość sygnału jest określona.

Multiplekser i demultiplekser muszą być zsynchronizowane takim samym dekoderem by móc poprawnie przenosić dane.

Przerzutnik RS kluczowany odczytuje wartości wejść R i S tylko wtedy gdy „klucz” przyjmuje wartość 1 - możemy zatem decydować kiedy przerzutnik RS będzie działać sterując kluczem (Wciąż jednak możliwy jest stan niedozwolony).

Przerzutnik D typu zatrzask przenosi wartość D na wyjście tylko wtedy gdy sygnał sterujący C przyjmuje wartość 1 (stan wysoki). W przeciwnym wypadku zapamiętana zostanie ostatnio ustawiona wartość.

Przerzutnik RS master - slave dla C=1 odczytuje wejścia R i S (nie zmieniając stanu wyjść), natomiast dla C=0 zmiany wejść układu są ignorowane - ustawiane są stany wyjść przerzutnika, które zależą od „zatrzaśniętej” wartości R i S (wartości, która była ostatnio odczytana dla C=1) - nadal może pojawić się stan niedozwolony dla układu.

Przerzutnik JK master - slave (na bramkach NAND) działa podobnie jak RS master - slave (J=R, K=S) jednak w przypadku gdy K=1 i S=1, nie występuje już stan niedozwolony, w takiej sytuacji układ neguje ostatnią wartość wyjścia.

Przerzutnik D wyzwalany zboczem działa podobnie jak D typu zatrzask, jedyną różnicą jest to, że wejście D (data) odczytywane jest gdy sygnał taktujący C ma stan niski (C=0), a gdy sygnał C zmieni stan na wysoki, zatrzaskiwana jest wartość D i przenoszona na wyjście układu. Układ ten w przeciwieństwie do D typu zatrzask zachowuje się przez pewien czas stabilnie, niezależnie czy stand D jest stabilny czy nie.

Przerzutnik T jest zbudowany z przerzutnika D wyzwalanego zboczem. Jedynie wejście D (data) zostało zmodyfikowane dzięki czemu wyjście Q zmienia się jedynie gdy T=1 - wtedy też następuje negacja Q. Przerzutnik D wyzwalanym zboczem w takiej sytuacji przenosił ma wyjście wartość D.

Liczniki synchroniczne są często bardziej skomplikowane od asynchronicznych, jednak dzięki bezpośredniemu połączeniu z urządzeniem taktującym są bardziej dokładne, w skutek czego nie są zwracane krótkotrwałe, niepożądane wartości.

Liczniki asynchroniczne (binarne, modulo 16) łatwiej rozbudowywać (np. modulo 16 do modulo 32) niż liczniki synchroniczne. Rozbudowa wymaga mniejszej ilości bramek (w tym bramek z wieloma wejściami), co za tym idzie jest tańsza i zajmuje mniej miejsca.

Licznik dwójkowy wykonany przeze mnie nie jest w pełni optymalny, gdyż w każdym momencie zarówno dodaje (wynik na wyjściach Q) oraz odejmuje (wynik na wyjściach ~Q). Dzięki temu faktowi jednak można skonstruować układ, który wyświetla zarówno wynik dodawania jak i odejmowania w tym samym momencie (przy 2 kompletach diod podpinając jeden komplet tylko do wyjść Q, a drugi tylko do ~Q), lub przy pomocy dodatkowego wejścia i układu bramek (Dodawanie / Odejmowanie) odpowiednio wysyłać sygnał do diod z tylko wyjść Q lub tylko ~Q (jak w układzie przedstawionym powyżej).

R |

S |

C |

Q |

~Q |

0 |

0 |

0 |

Q-1 |

~Q-1 |

0 |

1 |

0 |

Q-1 |

~Q-1 |

1 |

0 |

0 |

Q-1 |

~Q-1 |

1 |

1 |

0 |

Q-1 |

~Q-1 |

0 |

0 |

1 |

Q-1 |

~Q-1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

X |

X |

D |

C |

Q |

~Q |

0 |

0 |

Q-1 |

~Q-1 |

1 |

0 |

Q-1 |

~Q-1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

R |

S |

C |

Q |

~Q |

Q1 |

~Q1 |

0 |

0 |

0 |

Q1 |

~Q1 |

Q1-1 |

|

0 |

1 |

0 |

Q1 |

~Q1 |

Q1-1 |

~Q1-1 |

1 |

0 |

0 |

Q1 |

~Q1 |

Q1-1 |

~Q1-1 |

1 |

1 |

0 |

Q1 |

~Q1 |

Q1-1 |

~Q1-1 |

0 |

0 |

1 |

Q-1 |

~Q-1 |

Q1-1 |

~Q1-1 |

0 |

1 |

1 |

Q-1 |

~Q-1 |

1 |

0 |

1 |

0 |

1 |

Q-1 |

~Q-1 |

0 |

1 |

1 |

1 |

1 |

Q-1 |

~Q-1 |

X |

X |

J |

K |

Q |

~Q |

0 |

0 |

Q-1 |

~Q-1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

~Q-1 |

Q-1 |

D |

C |

Q |

~Q |

0 |

0 |

Q-1 |

~Q-1 |

1 |

0 |

Q-1 |

~Q-1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

T |

C |

Q |

0 |

0 |

Q-1 |

1 |

0 |

Q-1 |

0 |

1 |

Q-1 |

1 |

1 |

~Q-1 |

Damian Pawlik

WFMiIS

grupa 21

Wyszukiwarka

Podobne podstrony:

L05 Malec Marcola Ławniczek Mikronapedy Lab4 spr(1)

Nap Lab4 spr

lab4 spr

spr lab4

Lab4

Spr[1] adm i uznanie adm

08 03 KPGO Spr z realizacji

17 Rozp Min Zdr w spr szk czyn Nieznany

Lab4

przetworka spr ostatnie

as spr 5 id 69978 Nieznany (2)

metr spr 5

belka spr podl

lab4 8

078c rozp zm rozp min gosp w spr szkolenia w dziedzinie bhp

więcej podobnych podstron