III.2. Tranzystory bipolarne

Wstęp

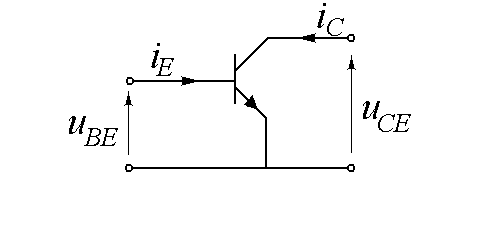

Tranzystor bipolarny - element półprzewodnikowy o trzech końcówkach: emiter (E), baza (B), kolektor (C). Struktura wewnętrzna: warstwy n-p-n lub p-n-p, stanowiące obszary E, B, C.

Domieszkowanie: NC = 1014 1015cm-3, NB= 1016 1018cm-3, NE= 1019 1020cm-3. Grubość bazy - poniżej 1 m

Złącza: E - B; C - B.

Obszary (zakresy) pracy:

Aktywny normalny: E-B -przewodząco, C-B - zaporowo.

Aktywny inwersyjny: E-B - zaporowo, C-B - przewodząco.

Odcięcie: oba złącza zaporowo. Nasycenie: oba złącza przewodząco.

Konfiguracje: WB (CB); WE (CE).

W obszarze AN: Prąd emitera (wejściowy): głównie elektrony z E do B. Oporność wejściowa reb mała (złącze przewodzące). Elektrony wprowadzane do bazy w większości docierają do kolektora. Prąd kolektora (wyjściowy) bliski prądowi emitera. Oporność wyjściowa rcb duża (złącze C-B polaryzowane zaporowo). Sygnał napięciowy na wyjściu większy od sygnału wejściowego.

Modele tranzystora idealnego

Założenia: złącza idealne; powierzchnie E-B i C-B równoległe: przepływ jednowymiarowy (z wyjątkiem ruchu nośników większościowych w bazie); szerokości WE, WB, WC - stałe.

Stałoprądowy model Ebersa - Molla

npn

Obszar A.N., Konfiguracja W.B., ICW pomijalny

Charakterystyki wyjściowe

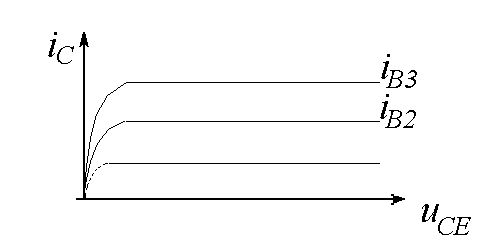

Konfiguracja W.E.

Charakterystyki wyjściowe

Modele wielkosygnałowe dynamiczne

Model Ebersa-Molla uzupełniamy o nieliniowe pojemności złącz E-B i C-B

Złącze E-B. Pojemność dyfuzyjna:

Pojemność złączowa:

Złącze C - B: Pojemność dyfuzyjna:

Pojemność złączowa:

Modele małosygnałowe - obszar A.N.

Konfiguracja W.B.

Konfiguracja W.E.:

Wzmocnienia prądowe i częstotliwości graniczne.

Dla

2.3. Właściwości tranzystorów rzeczywistych

Rezystancje szeregowe

Efekt Early'ego - modulacja szerokości bazy

Zjawiska przebić. Złącze C - B: powielanie lawinowe.

W.B.

W.E.

W.E.: przebicie przy mniejszych napięciach niż w W.B.

Złącze E - B: małe napięcie przebicia.

Procesy generacyjno rekombinacyjne w warstwach ładunku przestrzennego.

Obszar A.N. ICB0 - głównie prąd generacyjny.

Złącze E - B: prąd rekombinacyjny obok „zwykłego” prądu dyfuzyjnego; różne zależności od uBE; im mniejszy prąd całkowity tym większy udział składowej rekombinacyjnej. Prąd kolektora: tylko składnik idealny. Skutek: efektywne współczynniki wzmocnienia prądowego mniejsze przy mniejszych prądach.

Efekty wysokoprądowe: Prądowa modulacja szerokości bazy (efekt Kirk'a), Zjawisko quasi-nasycenia, Zagęszczenie prądu przy brzegach złącza E-B (current crowding), Wysoki poziom wprowadzenia w bazie. Skutek: zmniejszanie wartości parametrów użytkowych (np. , fT) w zakresie dużych prądów.

Najlepsze parametry użytkowe przy umiarkowanych gęstościach prądu. Pogarszanie parametrów przy dużych i małych prądach.

2.4 Tranzystor bipolarny jako przełącznik

I)

II), III)

II)

III)

I)

III)

II)

Praca impulsowa: najdłuższa faza przełączania to przejście z nasycenia do obszaru aktywnego.

2.5. Tranzystor jako wzmacniacz

Model małosygnałowy

m.cz.

3. Tranzystory polowe

3.1. Wstęp

Tranzystor polowy (Field - Effect Transistor - FET) element półprzewodnikowy trójkońcówkowy:

Źródło - S (Source); Dren - D (Drain); Bramka - G (Gate)

Prąd między S i D płynie przez kanał. Bramka, odizolowana od kanału oddziaływuje na przepływ prądu w kanale za pośrednictwem pola elektrycznego.

Dwie grupy: MOSFET i JFET. Różnica: sposób odizolowania bramki od kanału.

MOSFET - warstwa izolatora; JFET - złącze spolaryzowane zaporowo (p-n lub M-S)

3.2 Tranzystory MOSFET

Wykorzystują struktury Metal - Dielektryk - Półprzewodnik

Kanał n; Kanał p.

Kanał wbudowany (normalnie załączony; pracujący ze zubożaniem)

Kanał indukowany (normalnie wyłączony; pracujący ze wzbogaceniem)

Kanał n (Si: n = 3p)

Obszary pracy (dla uBS = 0)

Normalny (uDS>0) i odwrotny (uDS<0)

Normalny:

Odcięcie uGS < UP

Nienasycenie uGS - UP > uDS > 0

Nasycenie 0 < uGS - UP < uDS uGS - UP = uDS

punktowe zamknięcie kanału.

Modele idealnego tranzystora MOSFET

Założenia:

NB = const

b) n = const

c) IG = 0

Długość kanału L = const

Tylko prąd unoszenia

Nie ma przebić

rS (G, D, S) = 0

Model stałoprądowy (wielkosygnałowy)

Odcięcie: iDS = 0

Nienasycenie:

Nasycenie:

Normalnie:

pomijalne;

UP - napięcie progowe;

Obszar nasycenia: możliwości wzmacniające tym lepsze im większe B.

Model wielkosygnałowy dynamiczny

Pojemności CGS, CGD i CDB

Modele małosygnałowe (W.S)

nasycenie

b) nienasycenie (tylko m.cz.)

Szczegółowy przypadek - tzw. obszar liniowy

Regulowany rezystor:

Rzeczywiste tranzystory MOSFET

Ruchliwość

Długość kanału

W obszarze nasycenia:

Duże prądy: zależność gm od UGS słabsza niż według modelu idealnego.

Składowa dyfuzyjna: istotny udział w prądzie drenu w zakresie słabej inwersji (inaczej: zakres podprogowy - subthreshold region), co odpowiada małym prądom.

Zjawiska przebić: przebicie złącza D - B (lawinowe) w obszarze nasycenia; przebicie izolatora bramka - kanał (niszczące). Zabezpieczenia, np.:

Rezystancje szeregowe - istotne przy dużych częstotliwościach lub dużych szybkościach przełączania.

3.3 Tranzystory polowe złączowe

JFET (junction field effect transistors); dwie grupy: PNFET i MESFET.

Skrót JFET odnosi się zazwyczaj do pierwszej grupy.

Tranzystory JFET ze złączem p-n (Si)

Kanał (wbudowany) n lub p. Normalnie załączone.

Kanał n

Napięcie uGS < 0 (złącze bramka-kanał spolaryzowane zaporowo).

Zmiany uGS

zmiany szerokości warstw ładunku przestrzennego

zmiany grubości kanału

zmiany rezystancji kanału

zmiany prądu drenu przy danym uDS.

Przy uGS = UP (<0) grubość kanału staje się równa zeru.

uGS = UP - odcięcie.

Dla uGS - UP = uDS - punktowe zamknięcie kanału

Obszary pracy - jak dla MOSFET-a.

Modele - podobne do modeli MOSFET-a.

Prąd drenu w nasyceniu:

użyteczny zakres zmian uGS: (UP, 0)

Tranzystory MESFET (GaAs)

Większe

większe B (większe gm) przy tym samym COX.

Dobre właściwości wzmacniające w zakresie w.cz. (powyżej 1 GHz).

Można wytwarzać półizolacyjne warstwy podłożowe (bo bardzo małe ni).

Trudności z dyfuzją domieszek i wytwarzaniem złącz p-n. Łatwiej wykonać złącze Schottky'ego.

Materiał bramki inny niż elektrod S i D (struktury wielowarstwowe)

Kosztowna technologia.

Zastosowania: układy mikrofalowe, szybkie układy cyfrowe.

3.4 Tranzystory polowe jako elementy przełącznikowe i wzmacniające

Układ NMOS z opornikiem obciążającym

Przykład: UP=1V, B = 0.5mA/V2, UDD = 5V, R = 4kΩ.

Nachylenie charakterystyki;

Np. dla uWE =2V; Ku= - 2

Układy NMOS z obciążeniem aktywnym

a) b)

Charakterystyka elementu obciążającego (rys. a)

Rezystancja różniczkowa:

Nachylenie charakterystyki przenoszenia inwertera (a):

Inwerter CMOS

Charakterystyka przenoszenia symetryczna. Nachylenie Ku w punkcie środkowym wynika z nieidealności tranzystorów.

4. Diody i tranzystory w układach cyfrowych

Podstawowe operacje logiczne: NOT, OR, AND.

Negacja (NOT):

Suma (OR) i negacja sumy (NOR)

Iloczyn (AND) i negacja iloczynu (NAND)

Układ realizujący funkcje logiczne można przedstawić w postaci:

Pewnym przedziałom napięć przypisujemy „0” lub „1”

Charakterystyka przenoszenia: uY = f(uX) - jedno z wejść aktywne, pozostałe połączone do + lub - zasilania.

Punkty pracy: A, B. Punkty jednostkowego wzmocnienia: C, D. Punkt przejściowy TP.

Amplituda logiczna:

UA = uY(A) - uY(B)

Zakres przełączania:

UZ = uX(D) - uX(C)

Marginesy zakłóceń:

M1 = uX(C) - uX(A) M2 = uX(B) - uX(D)

Marginesy zakłóceń powinny być duże w stosunku do UA, a to wymaga, aby UZ było małe.

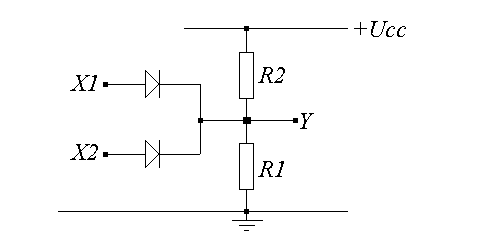

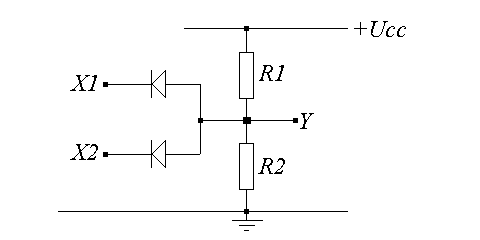

Funkcje logiczne OR i AND można realizować w sposób prymitywny w układach złożonych z diod i oporników.

Przykłady.

Np. R2=5kΩ,

R1 = 0.5kΩ,

UCC = 5V

1) OR;

2) AND;

Ograniczone możliwości: przy połączeniu kilku bramek - za mała amplituda logiczna, a nawet niemożność odróżnienia „0” i „1”. Brak funkcji NOT.

Użycie tranzystorów - realne bramki.

3) NAND - modyfikacja układu 2)

Może być więcej wejść - np. X3, X4...

uX1 |

X1 |

uX2 |

X2 |

uY |

Y |

0,5 |

0 |

0,5 |

0 |

5 |

1 |

0,5 |

0 |

4,5 |

1 |

5 |

1 |

4,5 |

1 |

0,5 |

0 |

5 |

1 |

4,5 |

1 |

4,5 |

1 |

0,2 |

0 |

Przewaga 3) nad 2): lepszy kształt charakterystyki przenoszenia; oporność wejściowa większa od wyjściowej

możliwość łączenia wielu bramek. AND = N(NAND).

Bramki podobne do układu 3) produkowano w latach 60 - tych (DTL - diode transistor logic). Potem opracowano TTL.

Standardowa bramka TTL NAND - przykład 4).

Lepszy kształt charakterystyki, mniejszy pobór mocy niż w bramce 3).

Kolejne wymaganie - szybkość pracy

Podstawowe modyfikacje układów TTL - układy TTL-S. Każdy tranzystor z dodatkową diodą Schottky'ego.

„Płytsze” nasycenie - krótszy czas wyłączania (wyjście z obszaru nasycenia).

Odmiany TTL: S, LS, AS, ALS, FAST i in.

Układy ECL - oparte na idei wzmacniacza różnicowego.

Y1 - NOR

Y2 - OR

Bramki MOS

Bramki statyczne NMOS - modyfikacje inwertera.

Statyczne CMOS

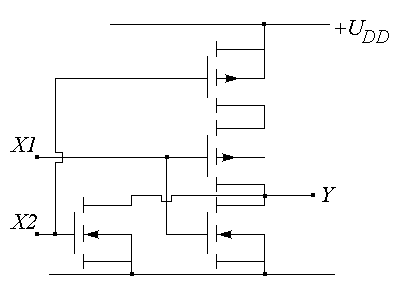

NOR

X1 |

X2 |

Y |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

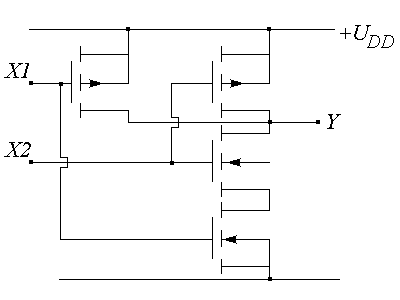

NAND

Bramki dynamiczne MOS - ogólna idea:

Ciągi impulsów zegarowych 1, 2 - w przeciwfazie. Mały pobór mocy. Dobra synchronizacja pracy różnych bloków.

|

Y |

0 |

1 |

1 |

0 |

X1 |

X2 |

Y |

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

X1 |

X2 |

Y |

Y |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

uX1 |

X1 |

uX2 |

X2 |

uY |

Y |

0,5 |

0 |

0,5 |

0 |

0,5 |

0 |

4,5 |

1 |

0,5 |

0 |

3,9 |

1 |

0,5 |

0 |

4,5 |

1 |

3,9 |

1 |

4,5 |

1 |

4,5 |

1 |

3,92 |

1 |

uX1 |

X1 |

uX2 |

X2 |

uY |

Y |

0,5 |

0 |

0,5 |

0 |

1,1 |

0 |

0,5 |

0 |

4,5 |

1 |

1,1 |

0 |

4,5 |

1 |

0,5 |

0 |

1,1 |

0 |

4,5 |

1 |

4,5 |

1 |

4,5 |

1 |

X1 |

X2 |

Y |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

Wyszukiwarka

Podobne podstrony:

Materiały do kolokwium III

POBIERANIE I PRZECHOWYWANIE MATERIAŁÓW DO BADAŃ wiRUSOLOGICZNYCH prezentacja

Materialy do seminarium inz mat 09 10 czesc III

Enzymologia materiały do ćwiczeń

materiały do egazaminu CHIR

Materiały do wykładu 4 (27 10 2011)

Materiały do izolacji termicznych

Materiały do ćwiczeń z geologii

BHP materiały do lekcji

MATERIALY DO WYKLADU CZ IV id Nieznany

Zadanie z kompensacji, Elektrotechnika-materiały do szkoły, Gospodarka Sowiński

zestawienie materiału do matury, in italiano, LICEUM

wersja bez badan pol, materiały do pracy z autyzmem, Pomoce naukowe, gotowość szkolna

socjologia ludności - materialy do zajęć 9, socjologia, Socjologia Ludności

Fizjologia zagadnienia, Fizjologia, Materiały do egzaminu

1z21, materiały do egzaminu

Podpowiedzi do mądrości przyrody, Ekologia - materiały do zajęć

test 1 - 2010, Elektrotechnika-materiały do szkoły, Zakłócenia w układach elektroenergetycznych

więcej podobnych podstron